Interesting Points of the SPARC Processor Saunders Roesser

- Slides: 16

Interesting Points of the SPARC Processor Saunders Roesser Summer 2002 CS-585 -2

Outline • • • Quick History Register Windowing Processor Traps Memory Model Conclusion

Quick History • Processor Design based off of the RISC I and II designs as the University of California, Berkeley • First SPARC Processor appeared in 1987 in a SUN MS SUN-4 Computer • 1989 – SPARC International Organization Setup

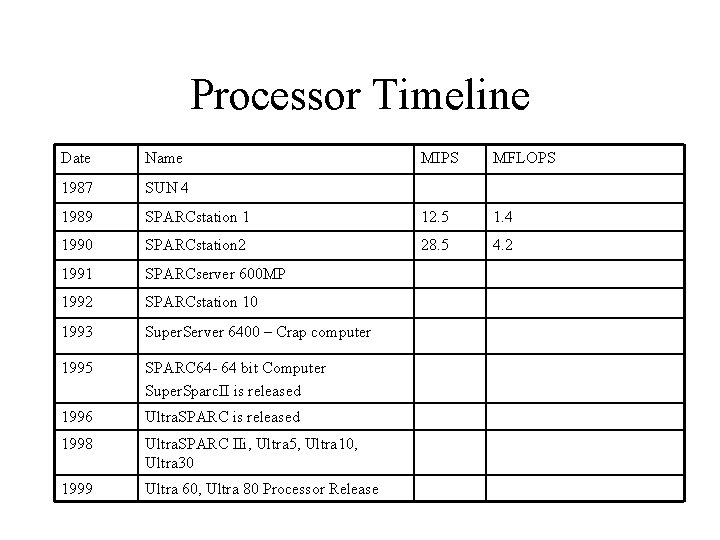

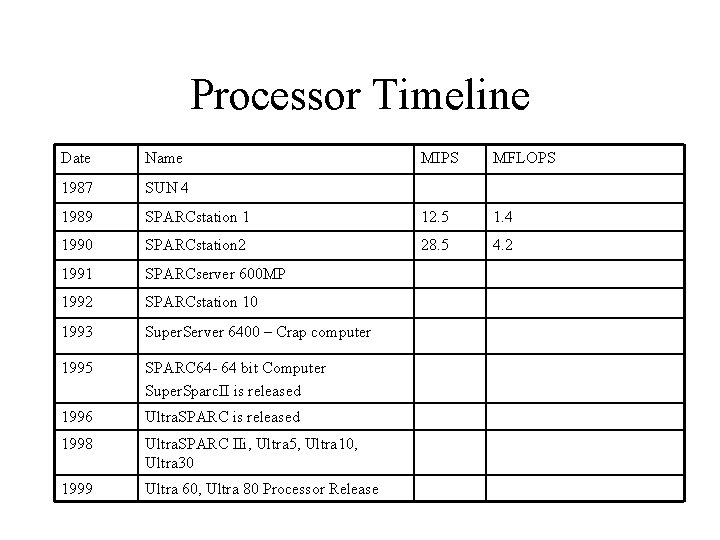

Processor Timeline Date Name MIPS MFLOPS 1987 SUN 4 1989 SPARCstation 1 12. 5 1. 4 1990 SPARCstation 2 28. 5 4. 2 1991 SPARCserver 600 MP 1992 SPARCstation 10 1993 Super. Server 6400 – Crap computer 1995 SPARC 64 - 64 bit Computer Super. Sparc. II is released 1996 Ultra. SPARC is released 1998 Ultra. SPARC IIi, Ultra 5, Ultra 10, Ultra 30 1999 Ultra 60, Ultra 80 Processor Release

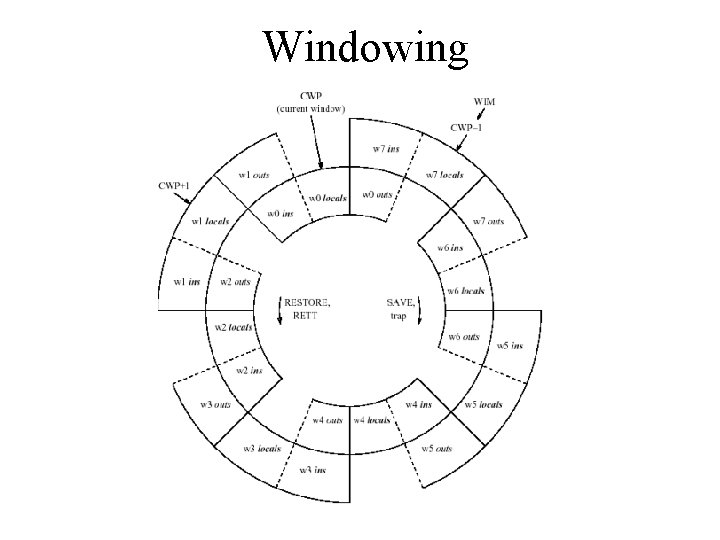

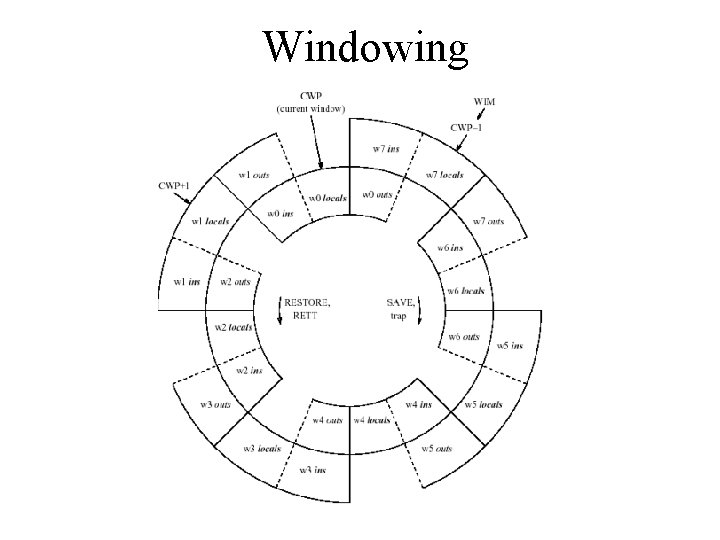

Register Windowing • Technique for handling register management • Only a small amount of the total physical register are available at any one time. • Virtual Window slides up and down the register stack to show groups of registers.

Register Windowing • Two types of registers – General Purpose Registers – Control/Status Registers • Each Processor Part has it’s own set of registers: – Instruction Unit (IU) – Co-Processor (CP) – Floating Point Unit (FPU)

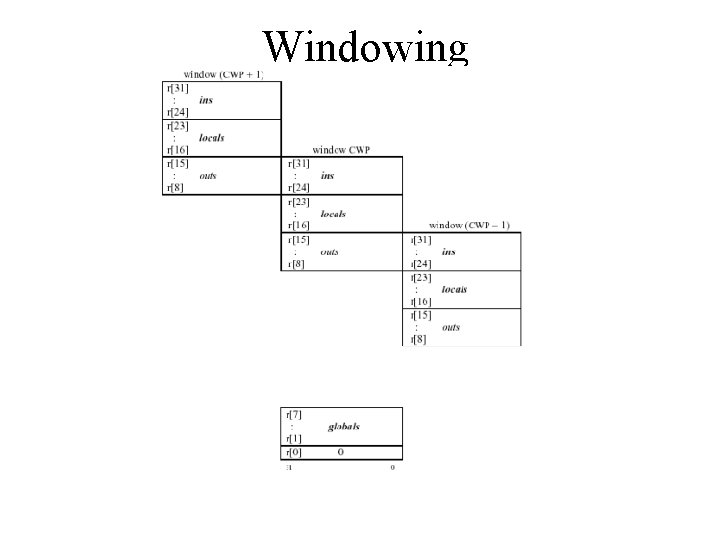

Instruction Unit • • May have between 40 -520 Registers 8 Global registers Divide the rest into Sets Set contains: – 8 local registers – 8 in registers • Window Contains: – 1 Set (8 local and 8 in) – Plus 8 Out Registers which equal the 8 In Registers of the Next Window

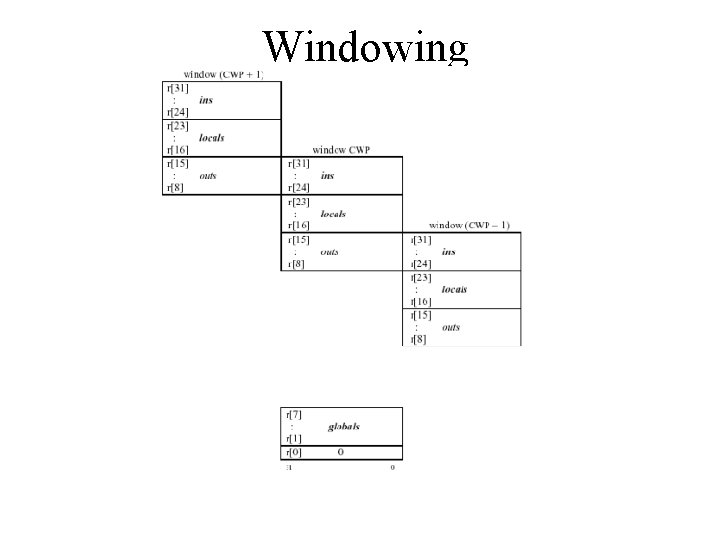

Windowing

Windowing

Traps • Error Handling Mechanism in the SPARC architecture • Handle errors, such as overflow, I/O, and instruction errors.

Handling Traps • Current Window Point is decremented • Information on the trap is stored in the local registers of the window.

Types of Traps • Precise trap – Error occurs before the instruction is executed • Deferred Trap – Error occurs after the instruction has executed – Can occur after several more instruction have occurred • Interrupting Traps – Error occurred from an event, such as I/O

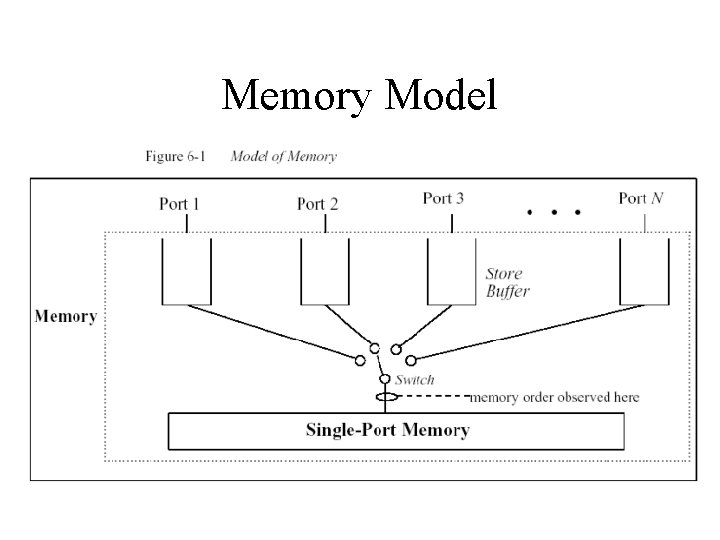

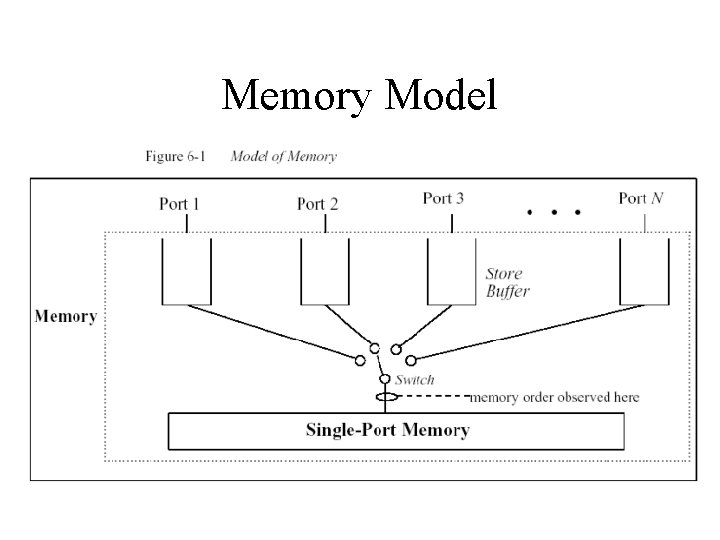

Memory Model • Total Store Ordering – Store, Flush, and Load happen in order they were issued • Partial Store Ordering – Issuing order can happen out of order to increase speed. • Hardware Implementation dependent • As long as it appears correct to software • Same model for one processor or mutiprocessor

Memory • Memory is stored in: – Half Word – 2 byte boundaries – Word – 4 byte boundaries – Double Word – 8 byte boundaries – Big Endian Architecture

Memory Model

Conclusion • SPARC has been the most successful implementation of a RISC architecture • Closest competitors have 10 years less experience • Processor is hardwired • PC is read by the CALL or JMPL instructions, not by numbers.