INTEL 8251 A USART univerzalni sinhronoasinhroni risivertransmiter Dejan

- Slides: 47

INTEL 8251 A USART (univerzalni sinhrono/asinhroni risiver/transmiter) Dejan Stojnić, ds 13@beotel. net Tatjana Petrović, tanja@etf. bg. ac. yu Prof. Dr. Veljko Milutinović, vm@etf. bg. ac. yu

Osnovne karakteristike sinhroni i asinhroni mod rada n full-duplex, duplo baferovan transmiter i risiver n korekcija grešaka n svi ulazi i izlazi su TTL kompatibilni n 2

Osnovne karakteristike n n n uređaj prihvata od procesora podatke za slanje u paralelnom formatu, konvertuje ih u serijski format a zatim šalje na port/ka modemu, a istovremeno prihvata sa porta/modema serijski niz podataka, konvertuje ih u paralelni format, a zatim šalje ka procesoru 8251 A takođe briše ili ubacuje bite ili karaktere karakteristične za izabranu tehniku komunikacije (start, stop, parity bite. . . ) suština je da uređaj bude “transparentan” za procesor, tj. da se ponaša kao jednostavan ulaz/izlaz za 3 bajtovski orijentisane podatke koje prima/šalje

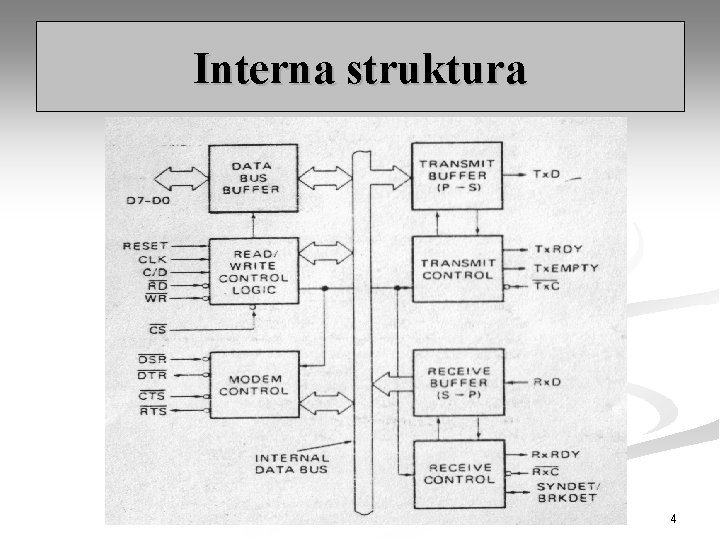

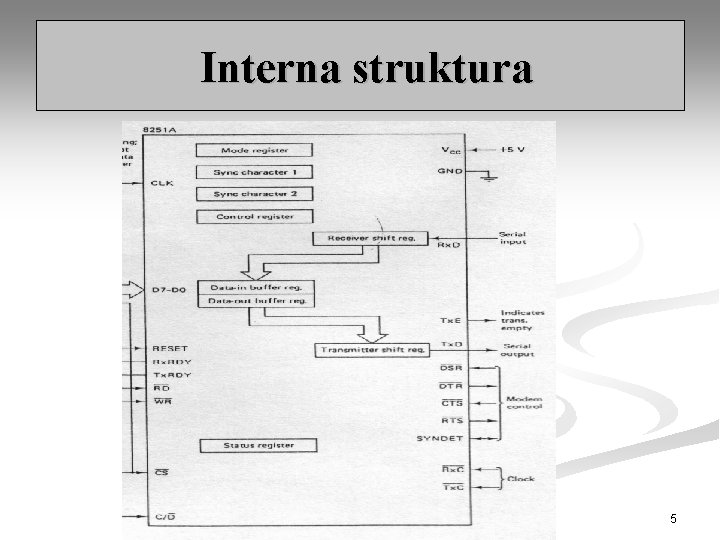

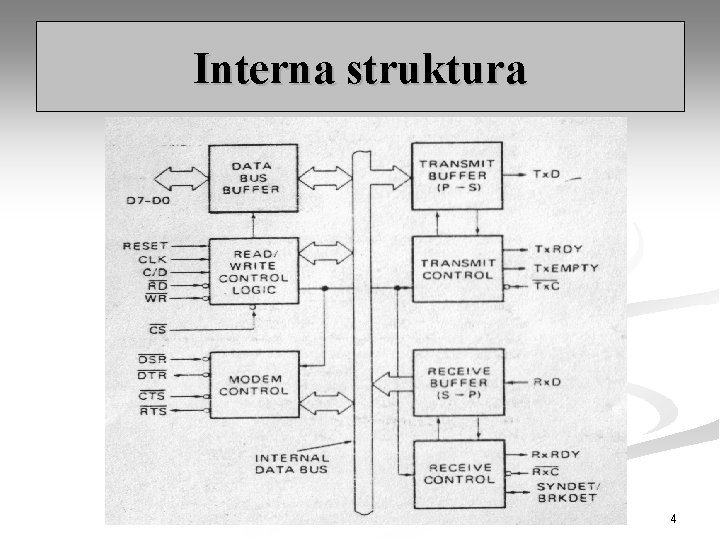

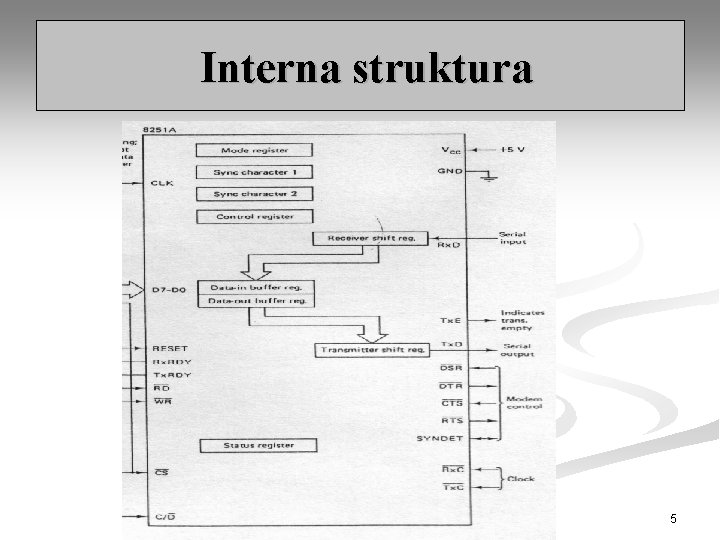

Interna struktura 4

Interna struktura 5

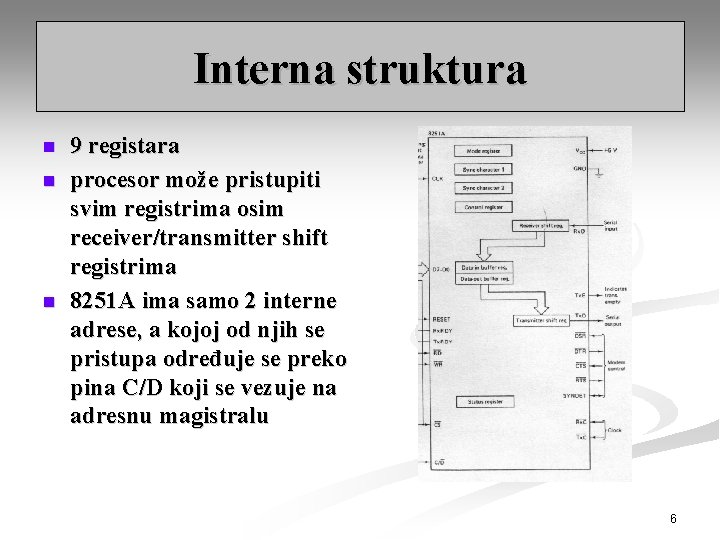

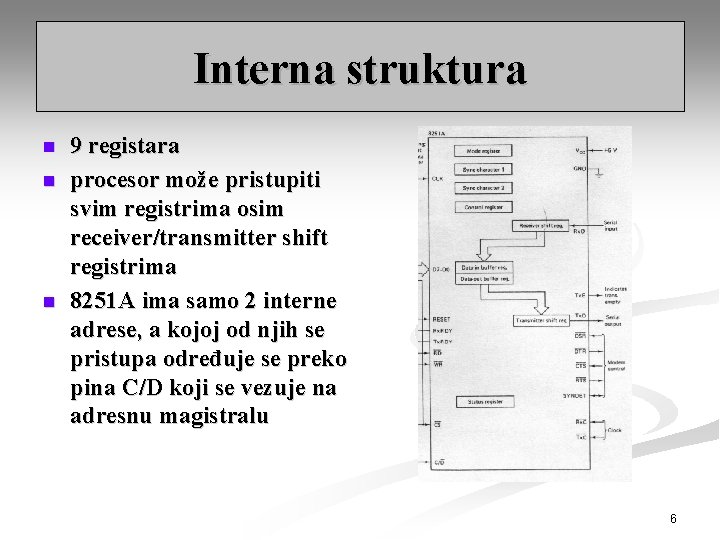

Interna struktura n n n 9 registara procesor može pristupiti svim registrima osim receiver/transmitter shift registrima 8251 A ima samo 2 interne adrese, a kojoj od njih se pristupa određuje se preko pina C/D koji se vezuje na adresnu magistralu 6

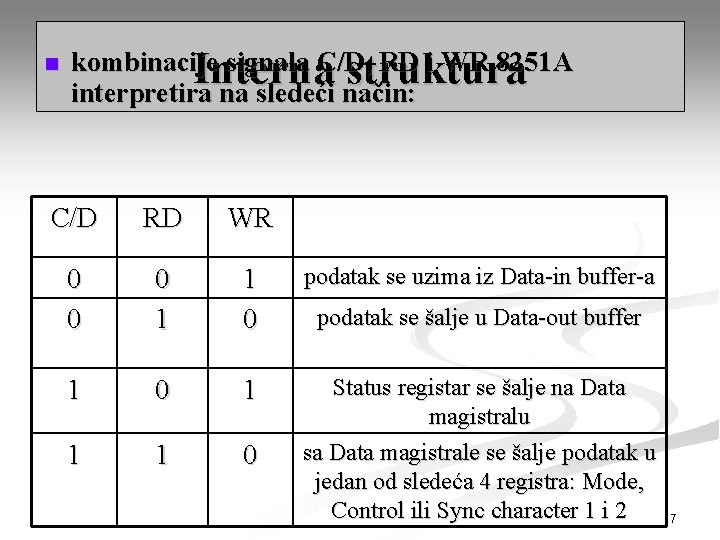

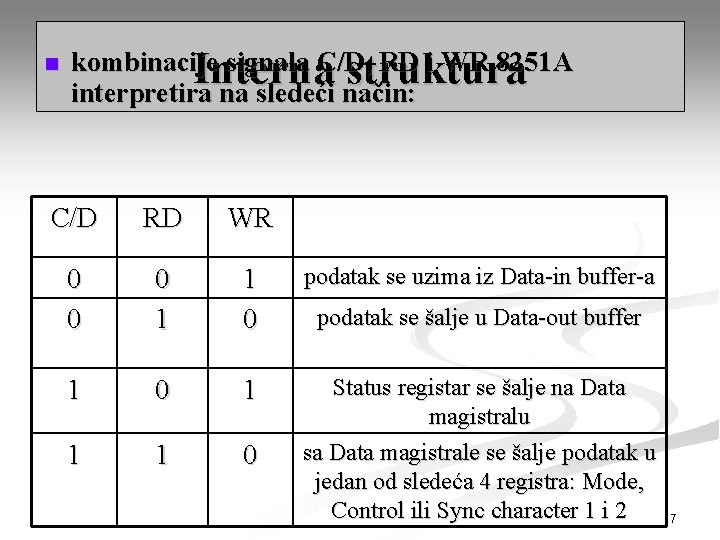

n kombinacije signala C/D, RD i WR 8251 A Interna struktura interpretira na sledeći način: C/D RD WR 0 0 0 1 1 0 podatak se uzima iz Data-in buffer-a 1 0 1 1 1 0 Status registar se šalje na Data magistralu sa Data magistrale se šalje podatak u jedan od sledeća 4 registra: Mode, Control ili Sync character 1 i 2 podatak se šalje u Data-out buffer 7

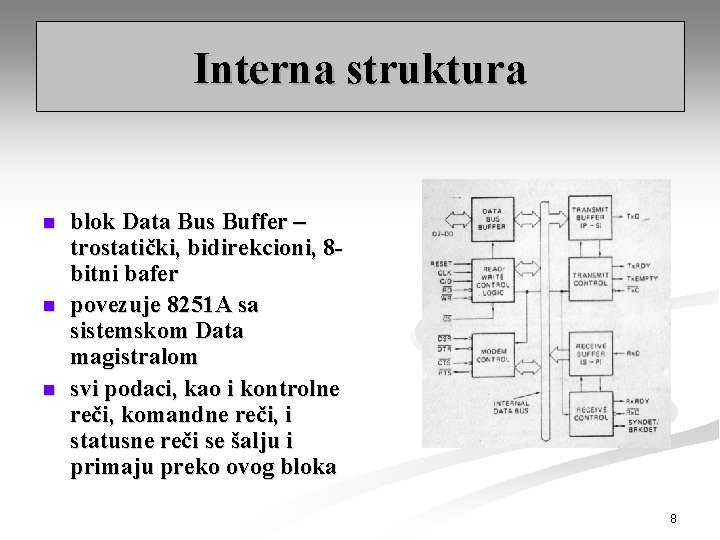

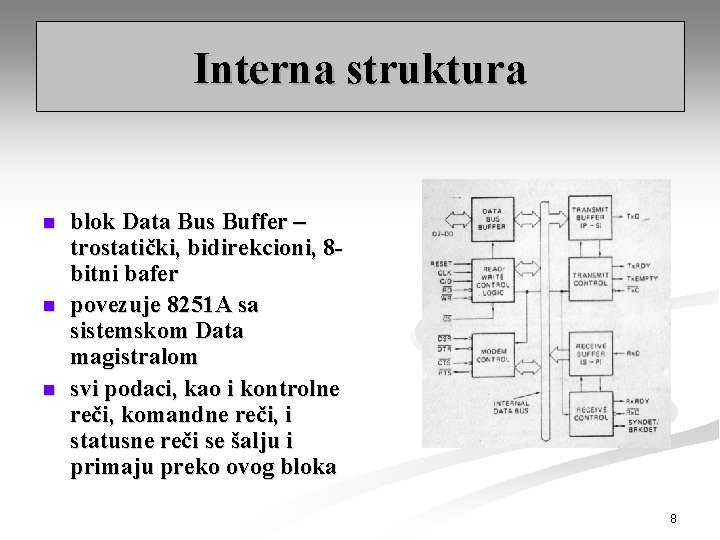

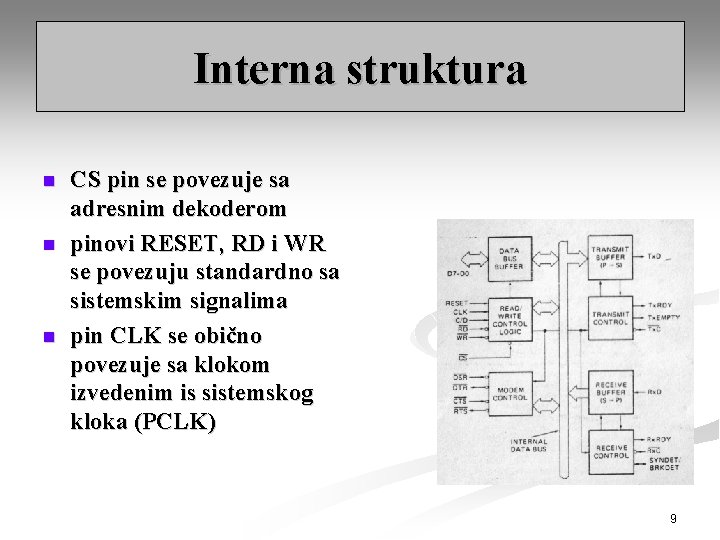

Interna struktura n n n blok Data Bus Buffer – trostatički, bidirekcioni, 8 bitni bafer povezuje 8251 A sa sistemskom Data magistralom svi podaci, kao i kontrolne reči, komandne reči, i statusne reči se šalju i primaju preko ovog bloka 8

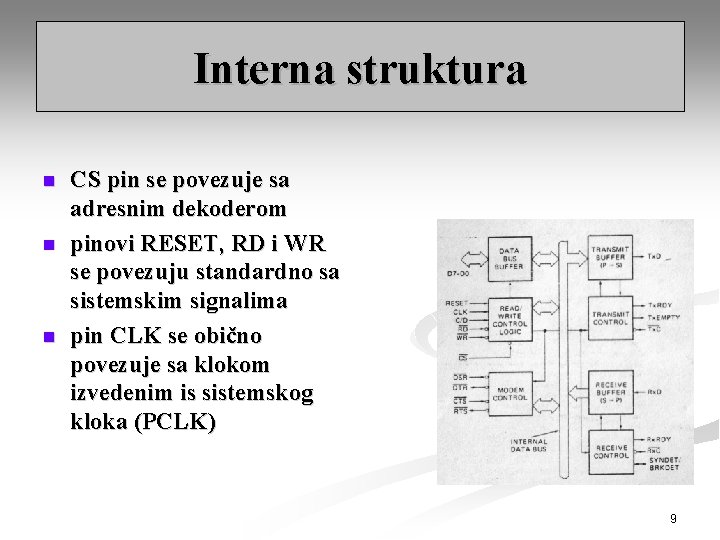

Interna struktura n n n CS pin se povezuje sa adresnim dekoderom pinovi RESET, RD i WR se povezuju standardno sa sistemskim signalima pin CLK se obično povezuje sa klokom izvedenim is sistemskog kloka (PCLK) 9

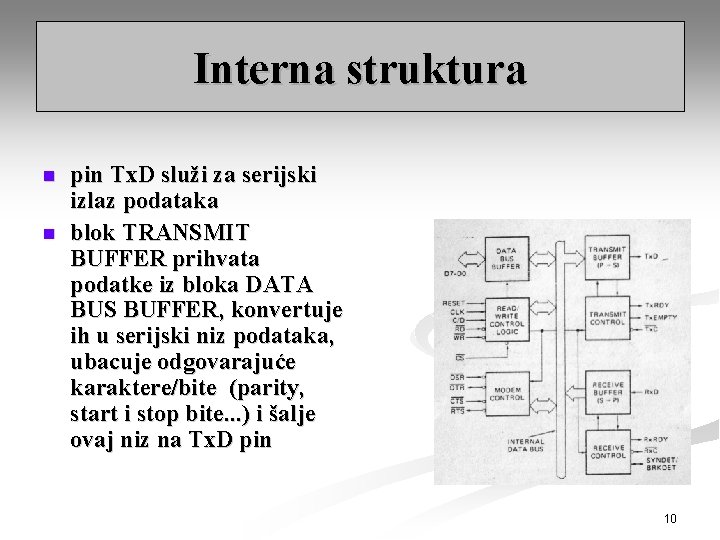

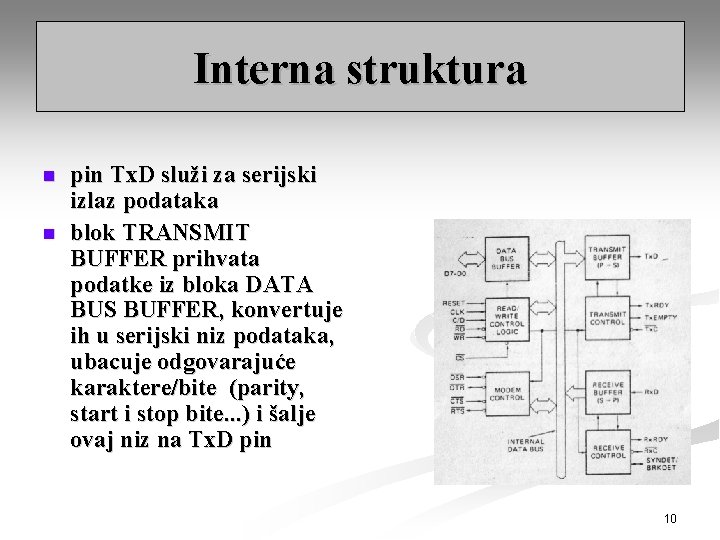

Interna struktura n n pin Tx. D služi za serijski izlaz podataka blok TRANSMIT BUFFER prihvata podatke iz bloka DATA BUS BUFFER, konvertuje ih u serijski niz podataka, ubacuje odgovarajuće karaktere/bite (parity, start i stop bite. . . ) i šalje ovaj niz na Tx. D pin 10

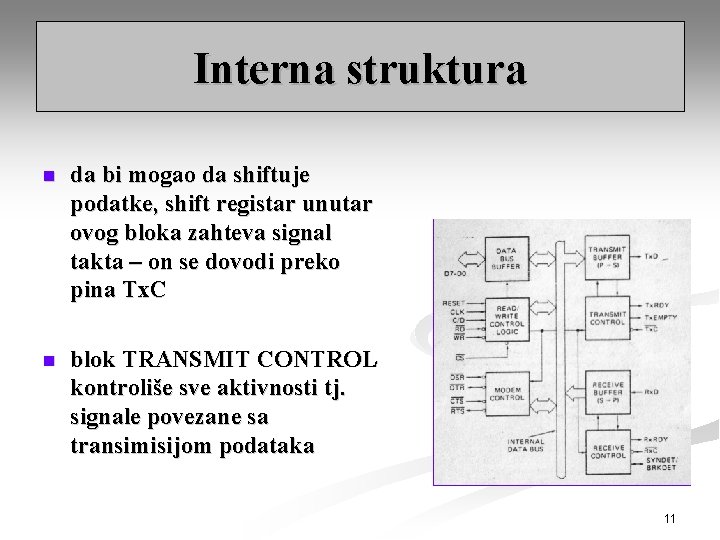

Interna struktura n da bi mogao da shiftuje podatke, shift registar unutar ovog bloka zahteva signal takta – on se dovodi preko pina Tx. C n blok TRANSMIT CONTROL kontroliše sve aktivnosti tj. signale povezane sa transimisijom podataka 11

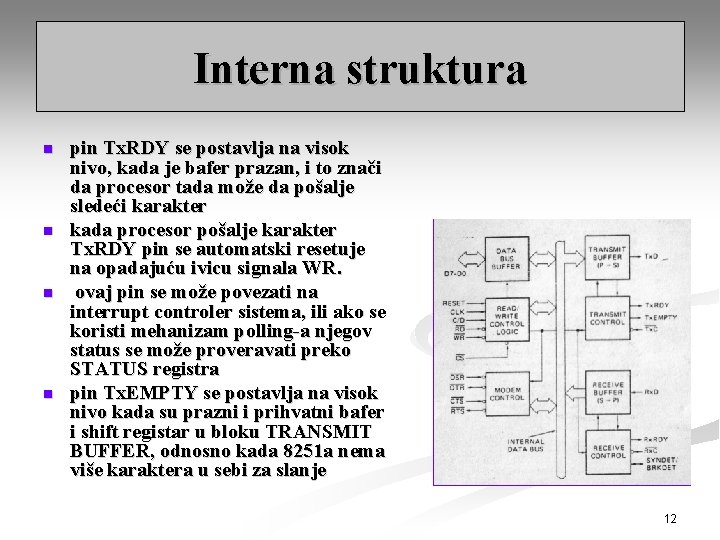

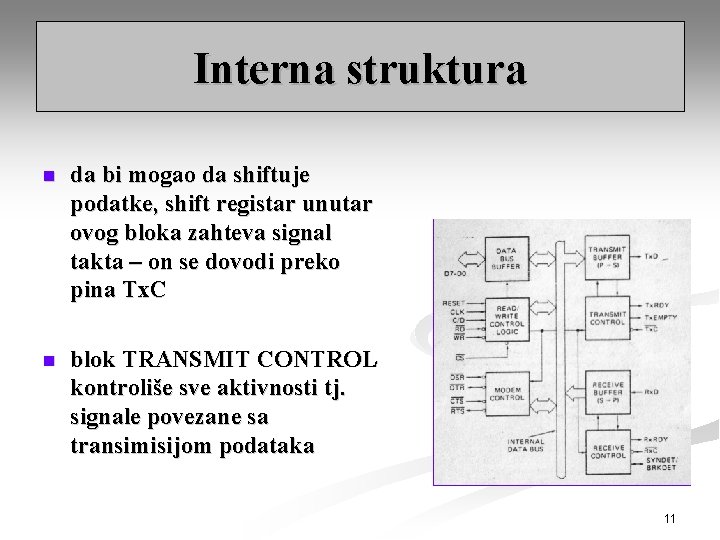

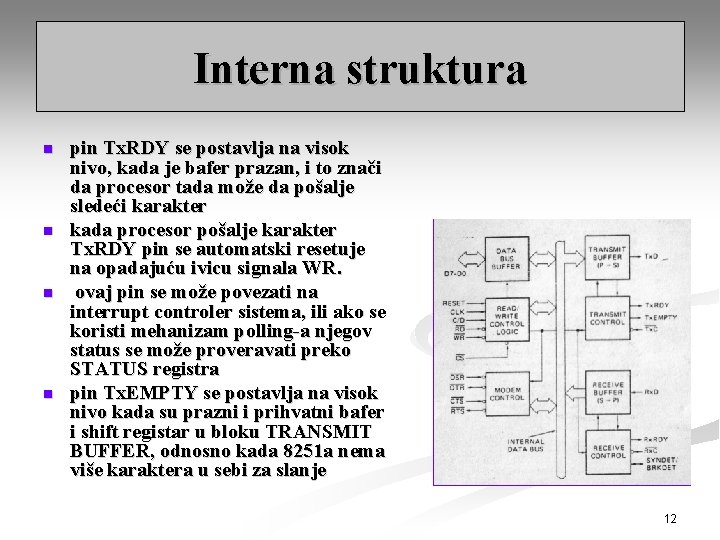

Interna struktura n n pin Tx. RDY se postavlja na visok nivo, kada je bafer prazan, i to znači da procesor tada može da pošalje sledeći karakter kada procesor pošalje karakter Tx. RDY pin se automatski resetuje na opadajuću ivicu signala WR. ovaj pin se može povezati na interrupt controler sistema, ili ako se koristi mehanizam polling-a njegov status se može proveravati preko STATUS registra pin Tx. EMPTY se postavlja na visok nivo kada su prazni i prihvatni bafer i shift registar u bloku TRANSMIT BUFFER, odnosno kada 8251 a nema više karaktera u sebi za slanje 12

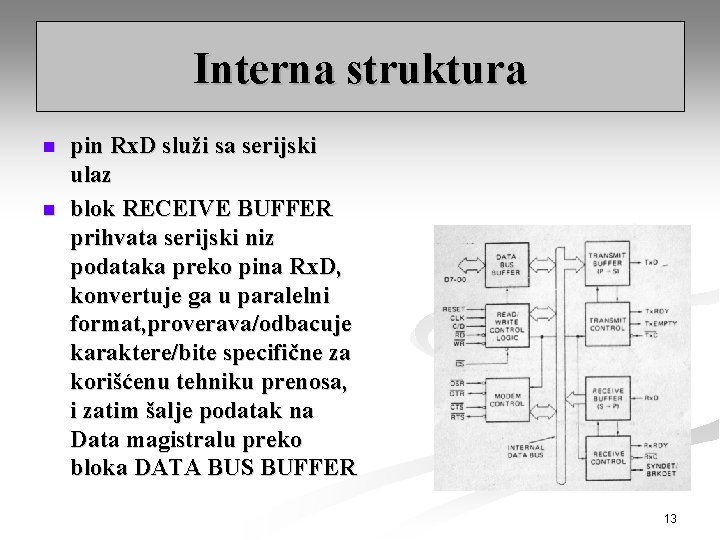

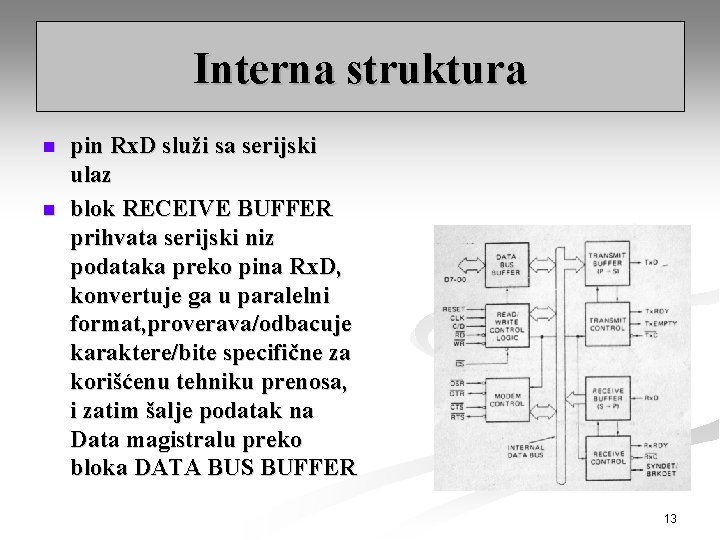

Interna struktura n n pin Rx. D služi sa serijski ulaz blok RECEIVE BUFFER prihvata serijski niz podataka preko pina Rx. D, konvertuje ga u paralelni format, proverava/odbacuje karaktere/bite specifične za korišćenu tehniku prenosa, i zatim šalje podatak na Data magistralu preko bloka DATA BUS BUFFER 13

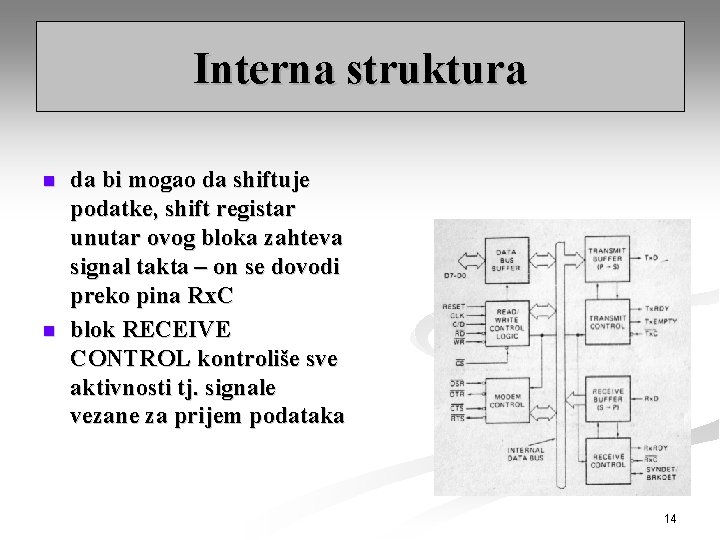

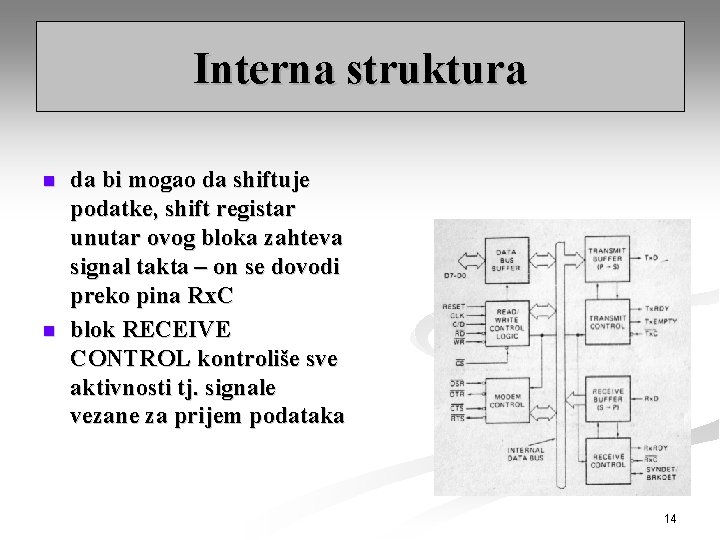

Interna struktura n n da bi mogao da shiftuje podatke, shift registar unutar ovog bloka zahteva signal takta – on se dovodi preko pina Rx. C blok RECEIVE CONTROL kontroliše sve aktivnosti tj. signale vezane za prijem podataka 14

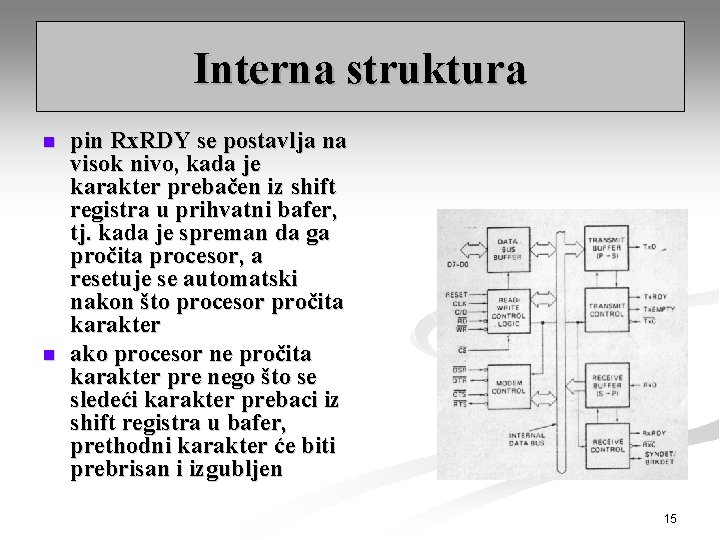

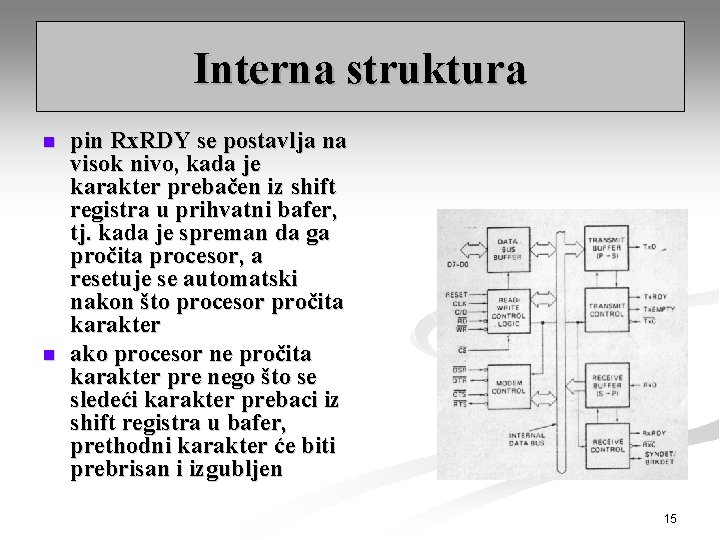

Interna struktura n n pin Rx. RDY se postavlja na visok nivo, kada je karakter prebačen iz shift registra u prihvatni bafer, tj. kada je spreman da ga pročita procesor, a resetuje se automatski nakon što procesor pročita karakter ako procesor ne pročita karakter pre nego što se sledeći karakter prebaci iz shift registra u bafer, prethodni karakter će biti prebrisan i izgubljen 15

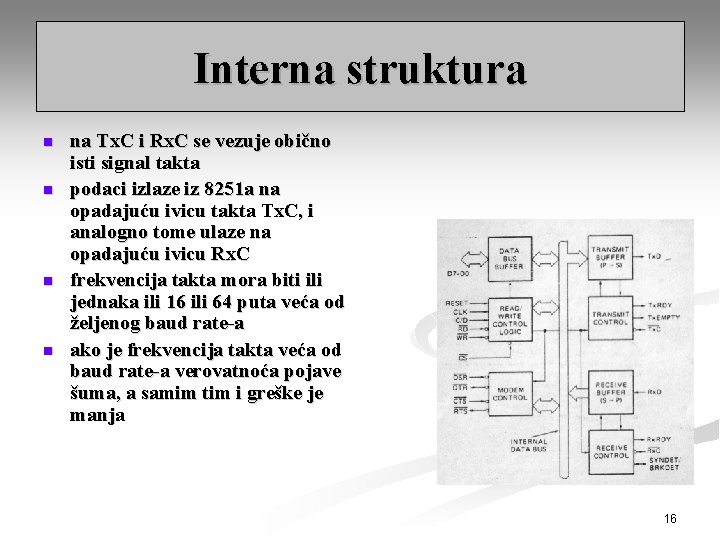

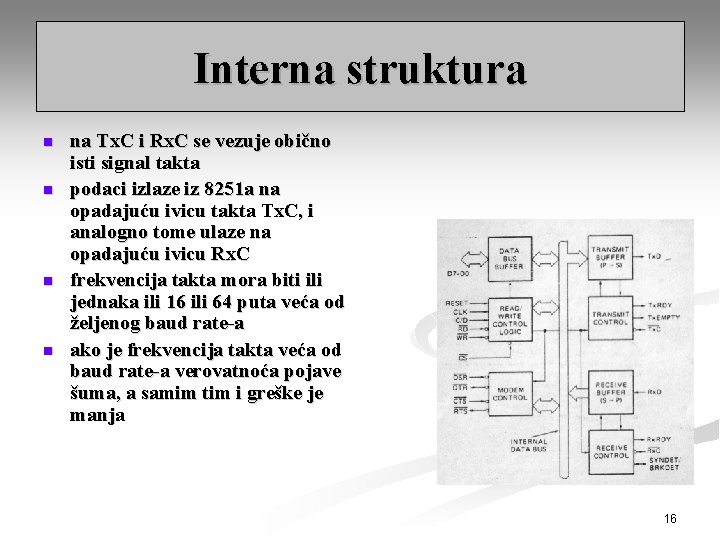

Interna struktura n n na Tx. C i Rx. C se vezuje obično isti signal takta podaci izlaze iz 8251 a na opadajuću ivicu takta Tx. C, i analogno tome ulaze na opadajuću ivicu Rx. C frekvencija takta mora biti ili jednaka ili 16 ili 64 puta veća od željenog baud rate-a ako je frekvencija takta veća od baud rate-a verovatnoća pojave šuma, a samim tim i greške je manja 16

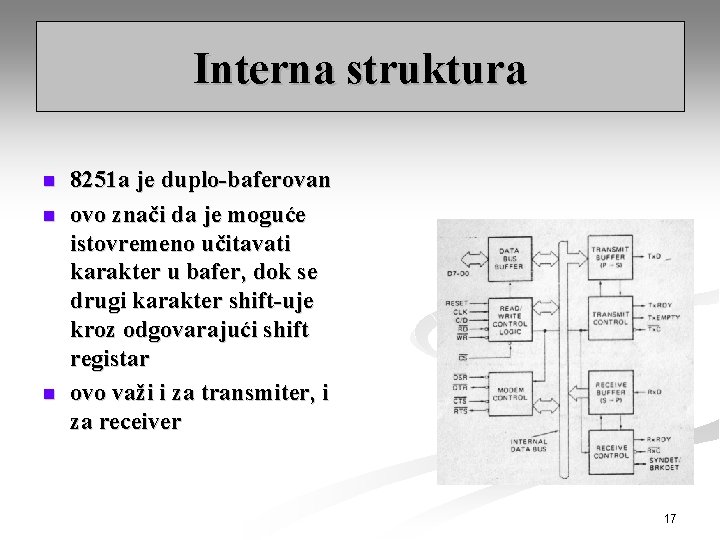

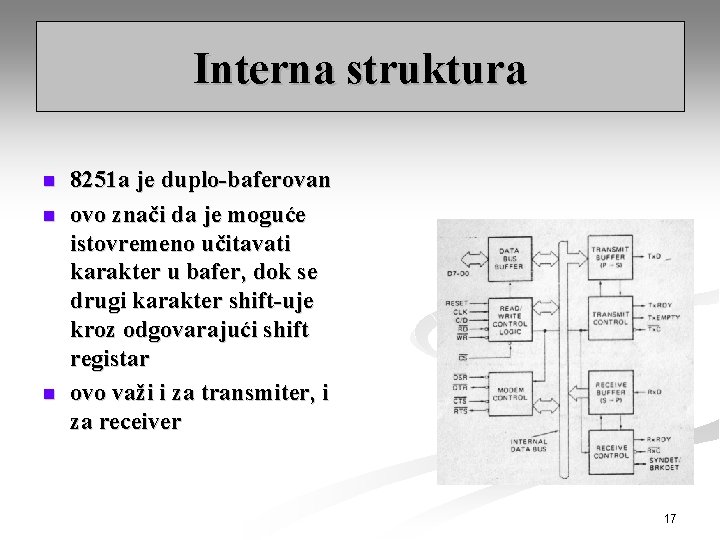

Interna struktura n n n 8251 a je duplo-baferovan ovo znači da je moguće istovremeno učitavati karakter u bafer, dok se drugi karakter shift-uje kroz odgovarajući shift registar ovo važi i za transmiter, i za receiver 17

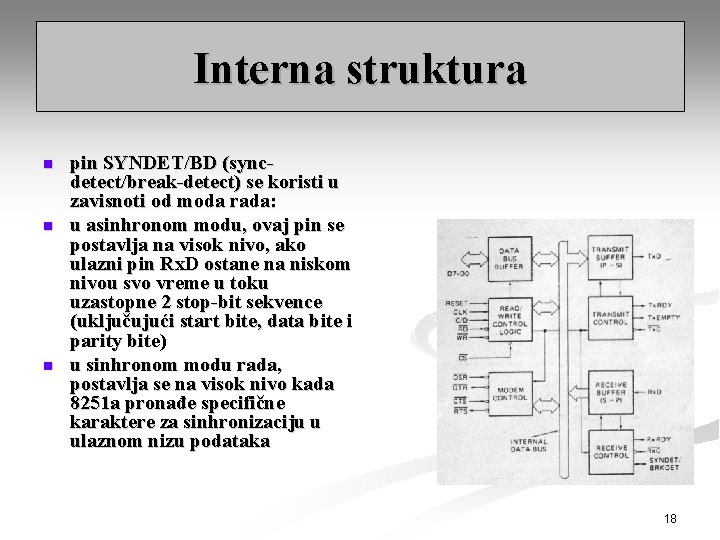

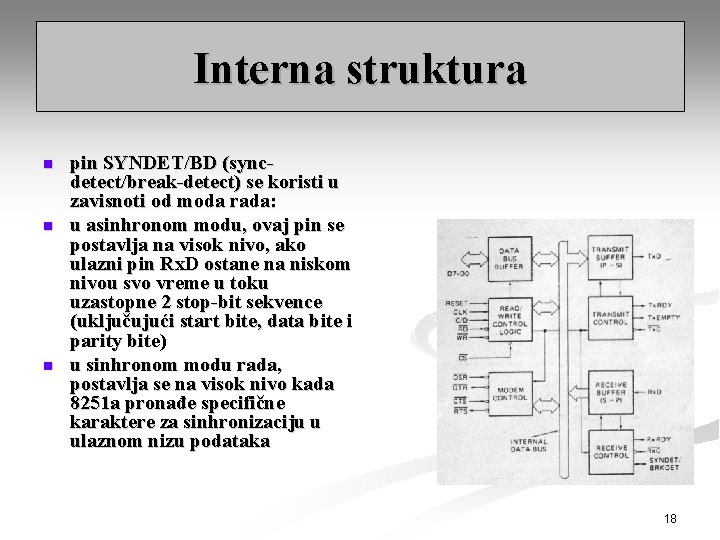

Interna struktura n n n pin SYNDET/BD (syncdetect/break-detect) se koristi u zavisnoti od moda rada: u asinhronom modu, ovaj pin se postavlja na visok nivo, ako ulazni pin Rx. D ostane na niskom nivou svo vreme u toku uzastopne 2 stop-bit sekvence (uključujući start bite, data bite i parity bite) u sinhronom modu rada, postavlja se na visok nivo kada 8251 a pronađe specifične karaktere za sinhronizaciju u ulaznom nizu podataka 18

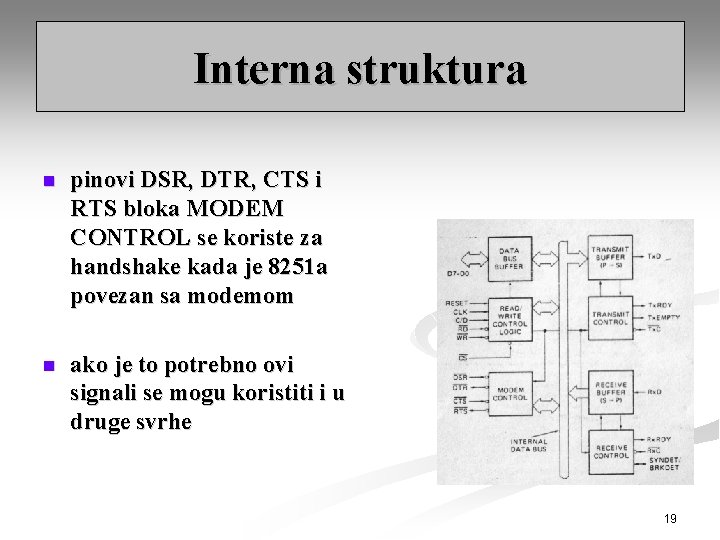

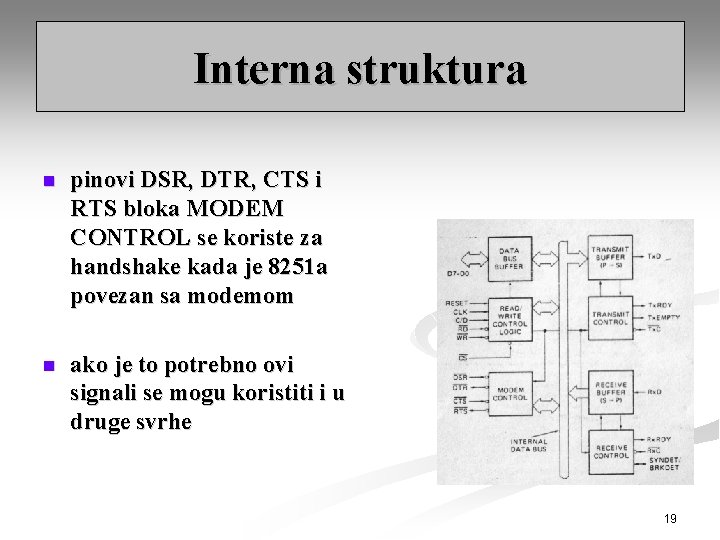

Interna struktura n pinovi DSR, DTR, CTS i RTS bloka MODEM CONTROL se koriste za handshake kada je 8251 a povezan sa modemom n ako je to potrebno ovi signali se mogu koristiti i u druge svrhe 19

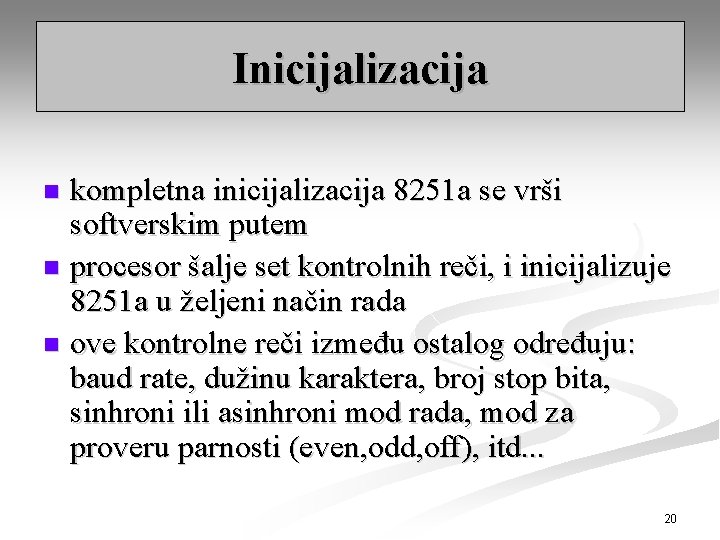

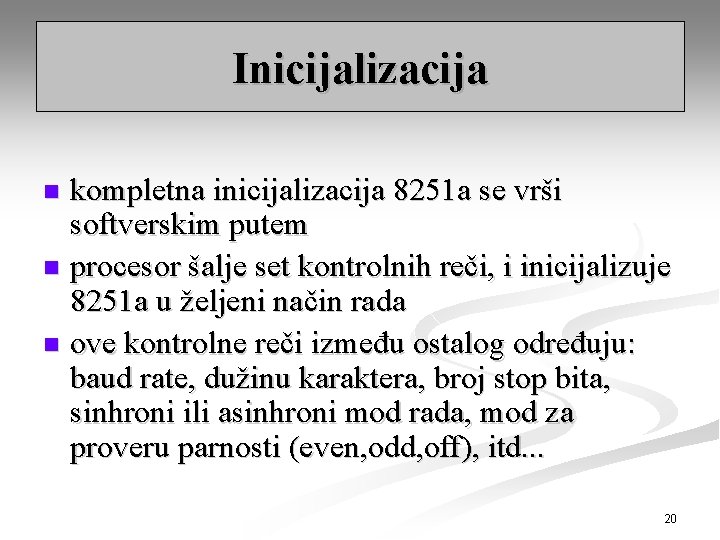

Inicijalizacija kompletna inicijalizacija 8251 a se vrši softverskim putem n procesor šalje set kontrolnih reči, i inicijalizuje 8251 a u željeni način rada n ove kontrolne reči između ostalog određuju: baud rate, dužinu karaktera, broj stop bita, sinhroni ili asinhroni mod rada, mod za proveru parnosti (even, odd, off), itd. . . n 20

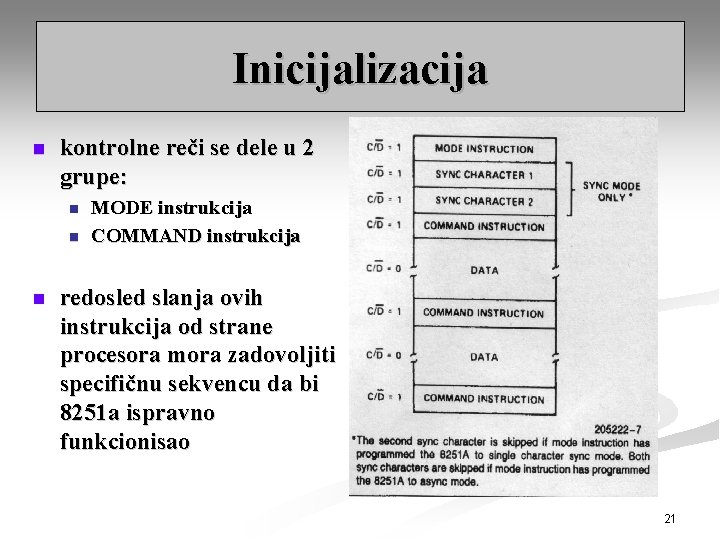

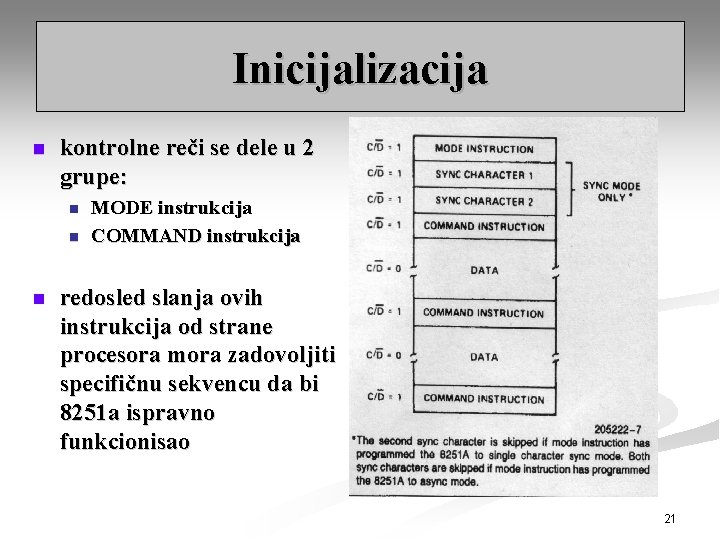

Inicijalizacija n kontrolne reči se dele u 2 grupe: n n n MODE instrukcija COMMAND instrukcija redosled slanja ovih instrukcija od strane procesora mora zadovoljiti specifičnu sekvencu da bi 8251 a ispravno funkcionisao 21

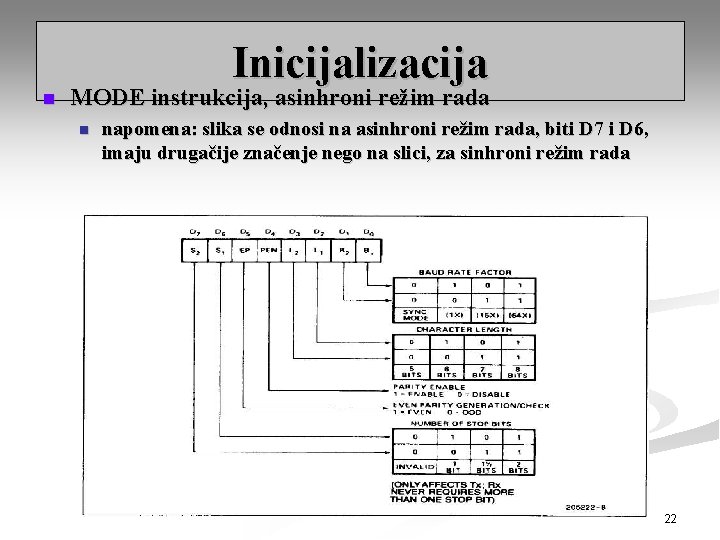

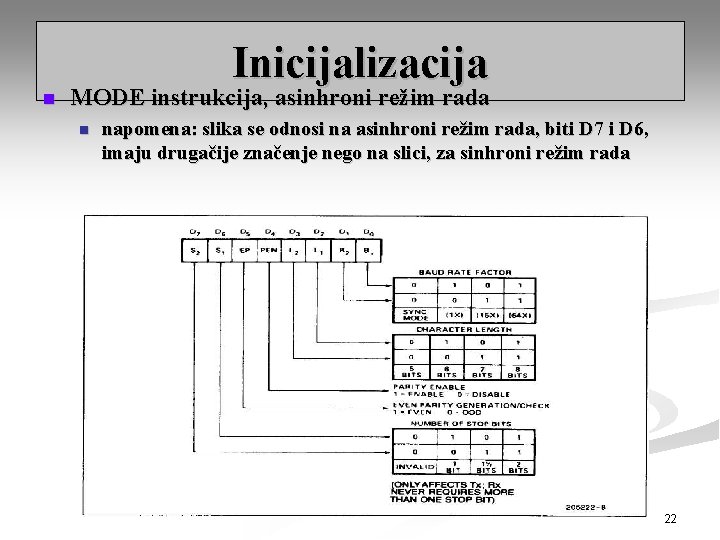

Inicijalizacija n MODE instrukcija, asinhroni režim rada n napomena: slika se odnosi na asinhroni režim rada, biti D 7 i D 6, imaju drugačije značenje nego na slici, za sinhroni režim rada 22

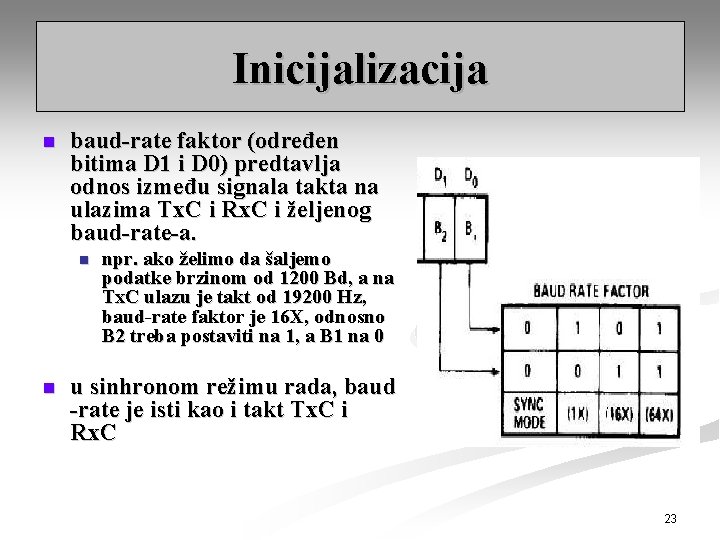

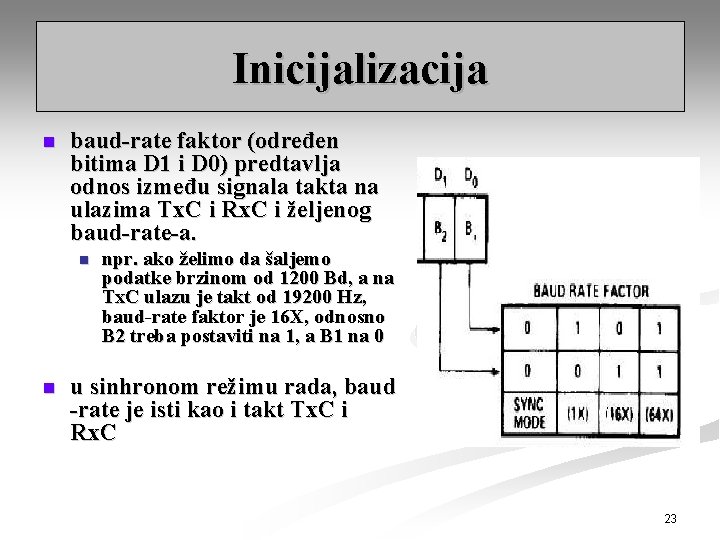

Inicijalizacija n baud-rate faktor (određen bitima D 1 i D 0) predtavlja odnos između signala takta na ulazima Tx. C i Rx. C i željenog baud-rate-a. n n npr. ako želimo da šaljemo podatke brzinom od 1200 Bd, a na Tx. C ulazu je takt od 19200 Hz, baud-rate faktor je 16 X, odnosno B 2 treba postaviti na 1, a B 1 na 0 u sinhronom režimu rada, baud -rate je isti kao i takt Tx. C i Rx. C 23

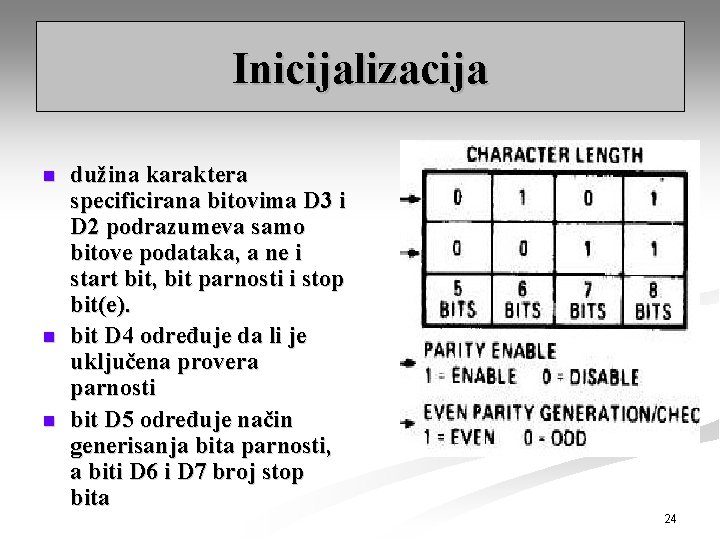

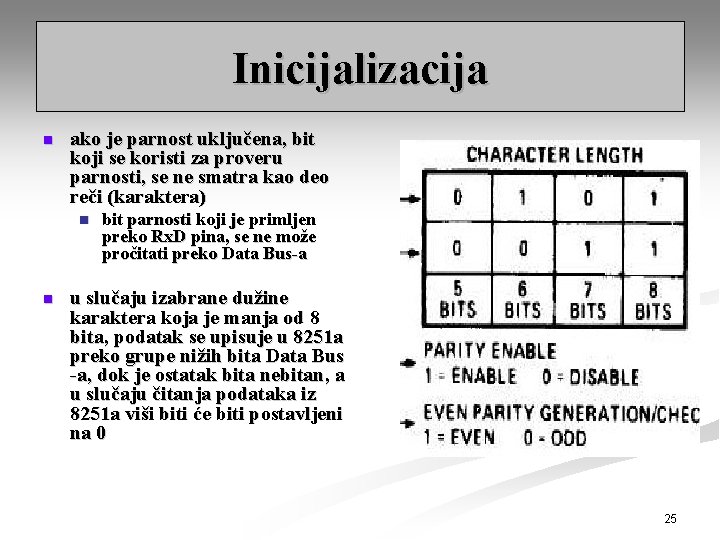

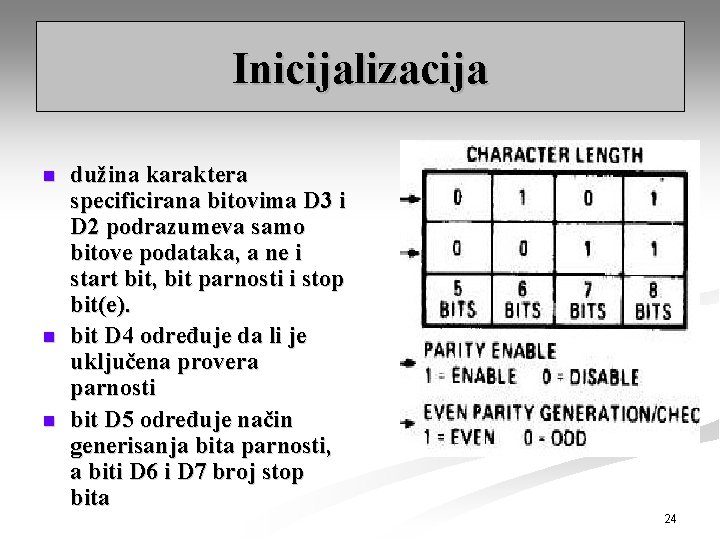

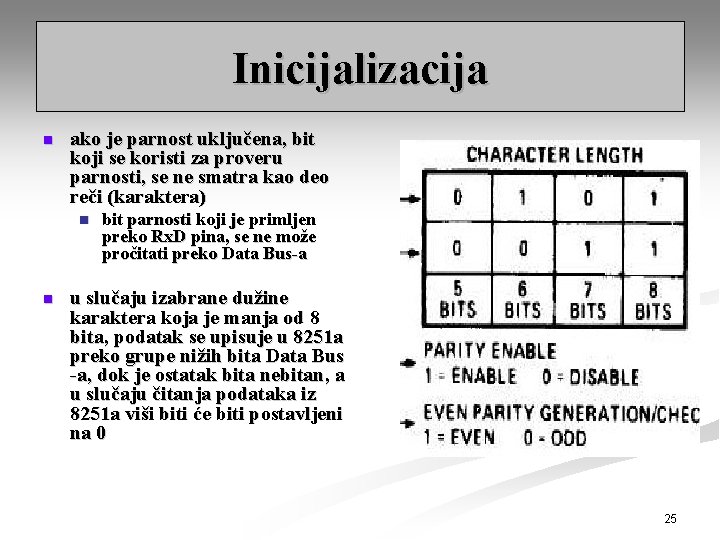

Inicijalizacija n n n dužina karaktera specificirana bitovima D 3 i D 2 podrazumeva samo bitove podataka, a ne i start bit, bit parnosti i stop bit(e). bit D 4 određuje da li je uključena provera parnosti bit D 5 određuje način generisanja bita parnosti, a biti D 6 i D 7 broj stop bita 24

Inicijalizacija n ako je parnost uključena, bit koji se koristi za proveru parnosti, se ne smatra kao deo reči (karaktera) n n bit parnosti koji je primljen preko Rx. D pina, se ne može pročitati preko Data Bus-a u slučaju izabrane dužine karaktera koja je manja od 8 bita, podatak se upisuje u 8251 a preko grupe nižih bita Data Bus -a, dok je ostatak bita nebitan, a u slučaju čitanja podataka iz 8251 a viši biti će biti postavljeni na 0 25

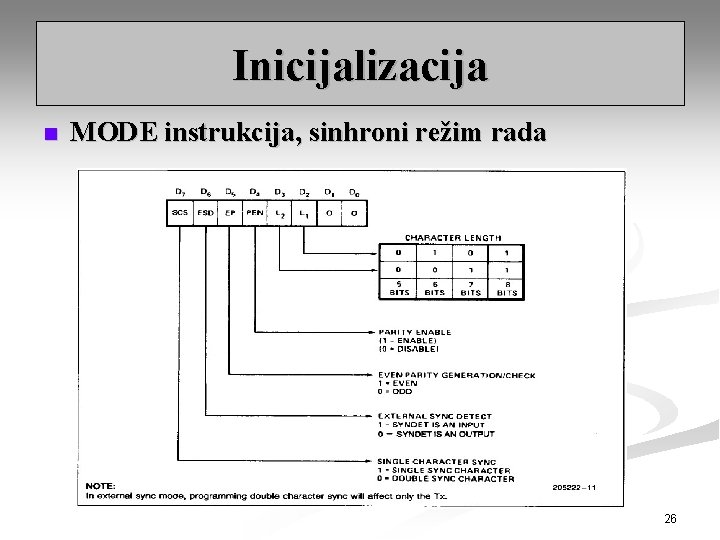

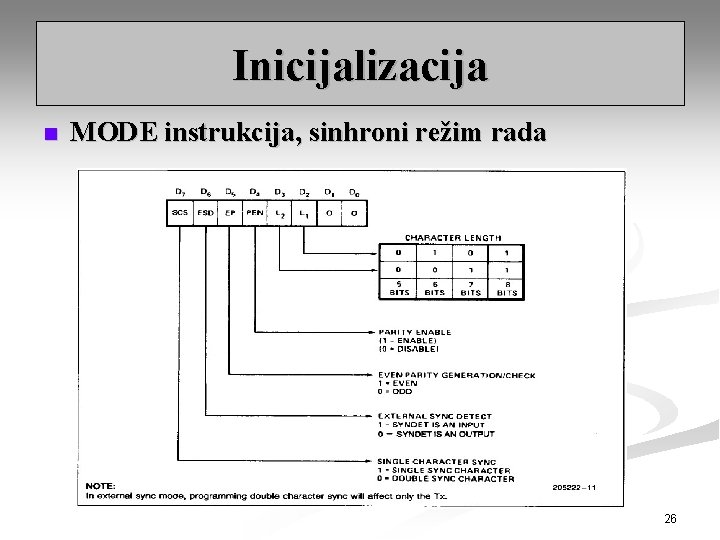

Inicijalizacija n MODE instrukcija, sinhroni režim rada 26

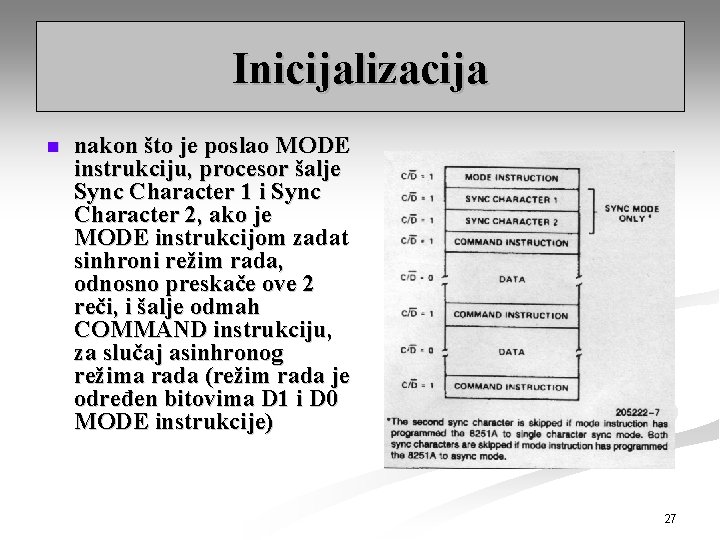

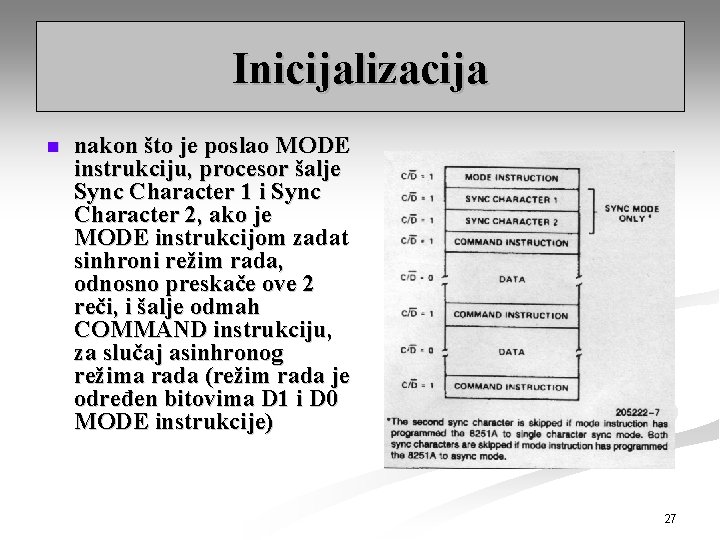

Inicijalizacija n nakon što je poslao MODE instrukciju, procesor šalje Sync Character 1 i Sync Character 2, ako je MODE instrukcijom zadat sinhroni režim rada, odnosno preskače ove 2 reči, i šalje odmah COMMAND instrukciju, za slučaj asinhronog režima rada (režim rada je određen bitovima D 1 i D 0 MODE instrukcije) 27

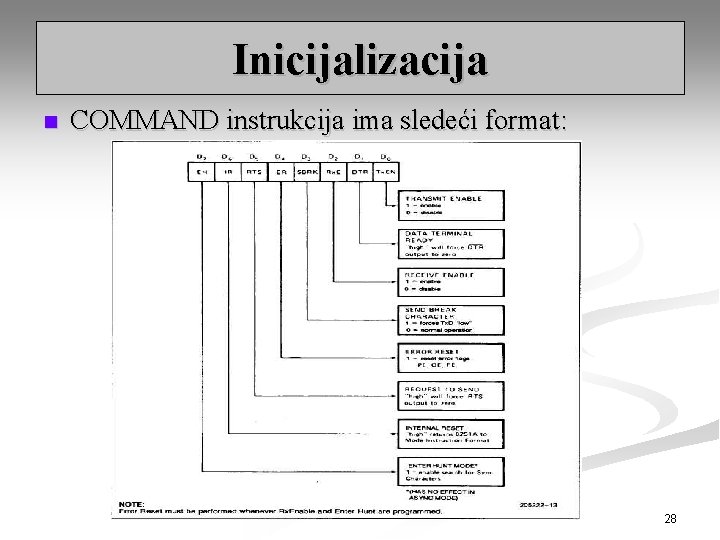

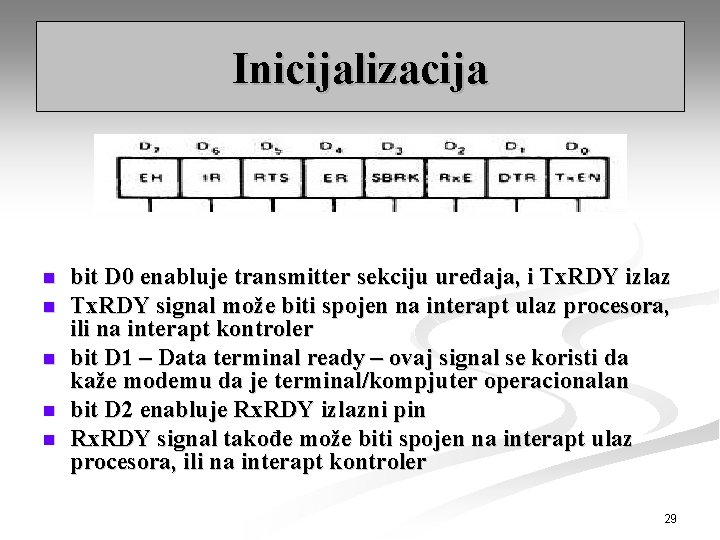

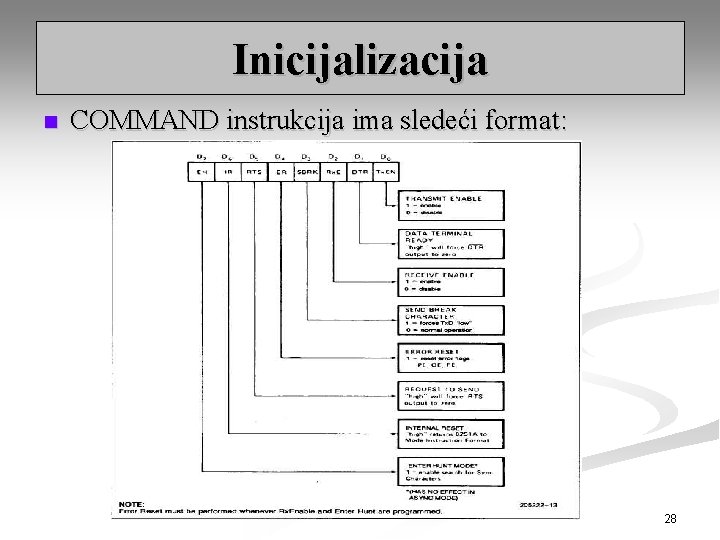

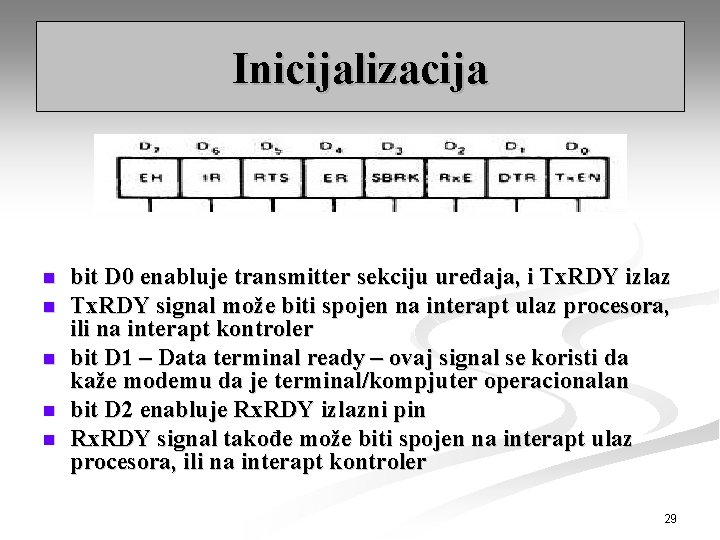

Inicijalizacija n COMMAND instrukcija ima sledeći format: 28

Inicijalizacija n n n bit D 0 enabluje transmitter sekciju uređaja, i Tx. RDY izlaz Tx. RDY signal može biti spojen na interapt ulaz procesora, ili na interapt kontroler bit D 1 – Data terminal ready – ovaj signal se koristi da kaže modemu da je terminal/kompjuter operacionalan bit D 2 enabluje Rx. RDY izlazni pin Rx. RDY signal takođe može biti spojen na interapt ulaz procesora, ili na interapt kontroler 29

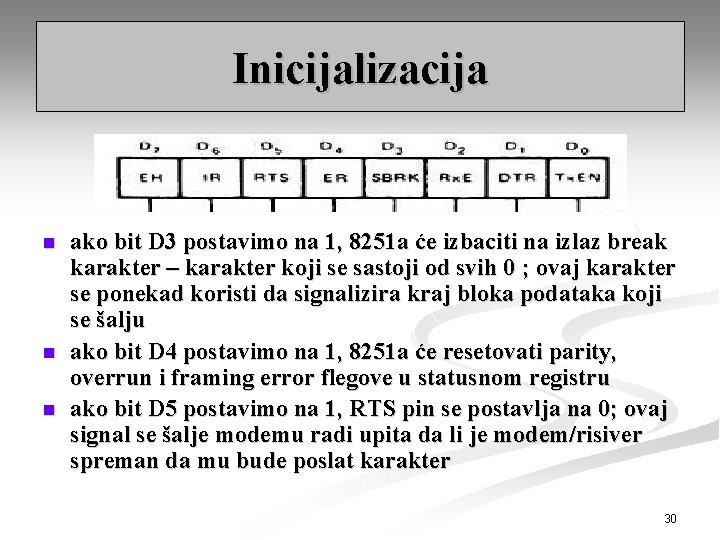

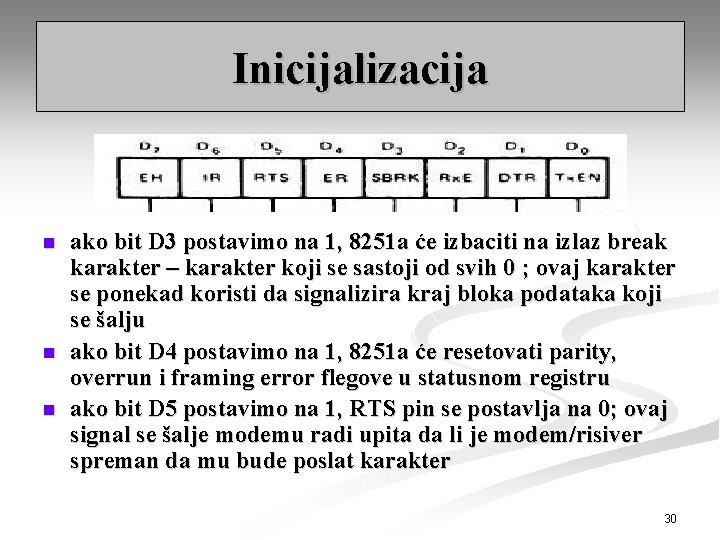

Inicijalizacija n n n ako bit D 3 postavimo na 1, 8251 a će izbaciti na izlaz break karakter – karakter koji se sastoji od svih 0 ; ovaj karakter se ponekad koristi da signalizira kraj bloka podataka koji se šalju ako bit D 4 postavimo na 1, 8251 a će resetovati parity, overrun i framing error flegove u statusnom registru ako bit D 5 postavimo na 1, RTS pin se postavlja na 0; ovaj signal se šalje modemu radi upita da li je modem/risiver spreman da mu bude poslat karakter 30

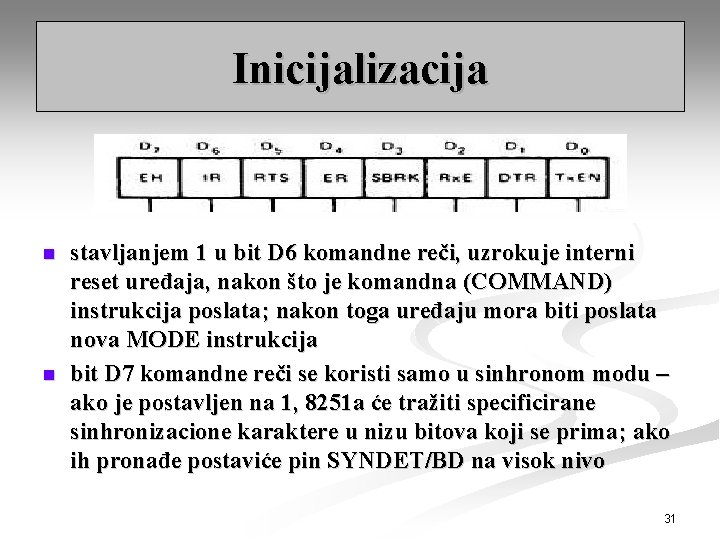

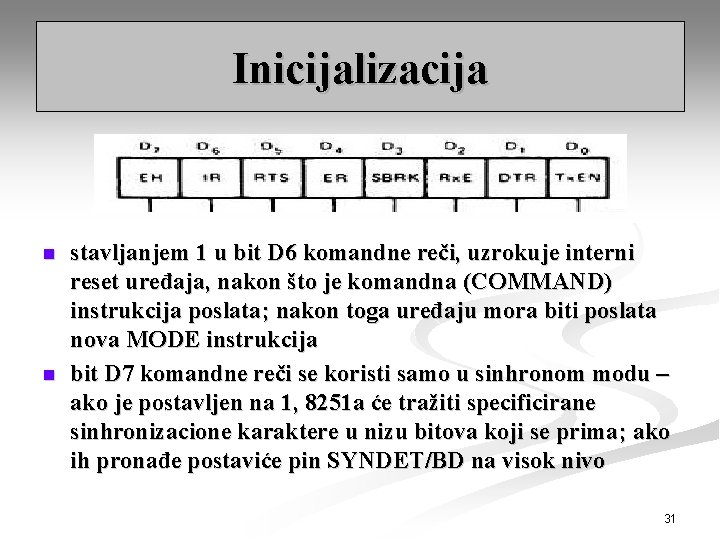

Inicijalizacija n n stavljanjem 1 u bit D 6 komandne reči, uzrokuje interni reset uređaja, nakon što je komandna (COMMAND) instrukcija poslata; nakon toga uređaju mora biti poslata nova MODE instrukcija bit D 7 komandne reči se koristi samo u sinhronom modu – ako je postavljen na 1, 8251 a će tražiti specificirane sinhronizacione karaktere u nizu bitova koji se prima; ako ih pronađe postaviće pin SYNDET/BD na visok nivo 31

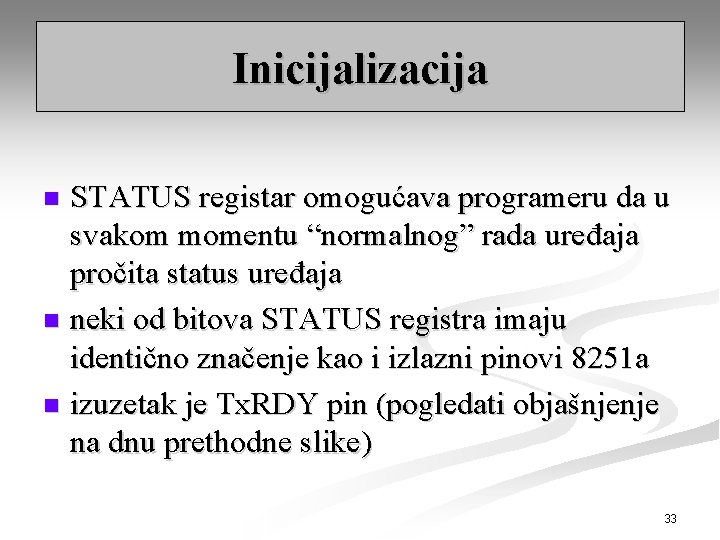

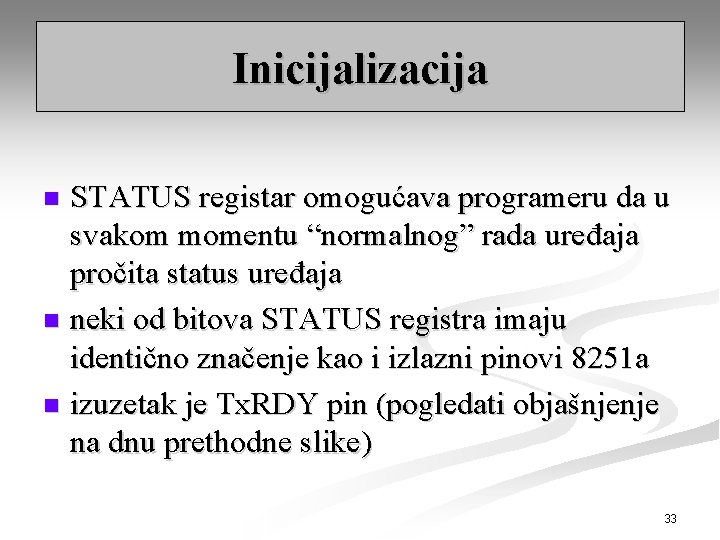

Inicijalizacija n izgled status registra 32

Inicijalizacija STATUS registar omogućava programeru da u svakom momentu “normalnog” rada uređaja pročita status uređaja n neki od bitova STATUS registra imaju identično značenje kao i izlazni pinovi 8251 a n izuzetak je Tx. RDY pin (pogledati objašnjenje na dnu prethodne slike) n 33

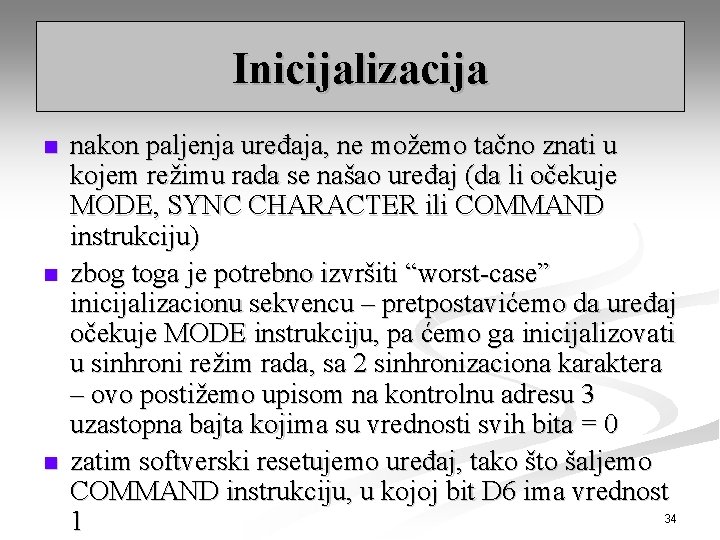

Inicijalizacija n nakon paljenja uređaja, ne možemo tačno znati u kojem režimu rada se našao uređaj (da li očekuje MODE, SYNC CHARACTER ili COMMAND instrukciju) zbog toga je potrebno izvršiti “worst-case” inicijalizacionu sekvencu – pretpostavićemo da uređaj očekuje MODE instrukciju, pa ćemo ga inicijalizovati u sinhroni režim rada, sa 2 sinhronizaciona karaktera – ovo postižemo upisom na kontrolnu adresu 3 uzastopna bajta kojima su vrednosti svih bita = 0 zatim softverski resetujemo uređaj, tako što šaljemo COMMAND instrukciju, u kojoj bit D 6 ima vrednost 34 1

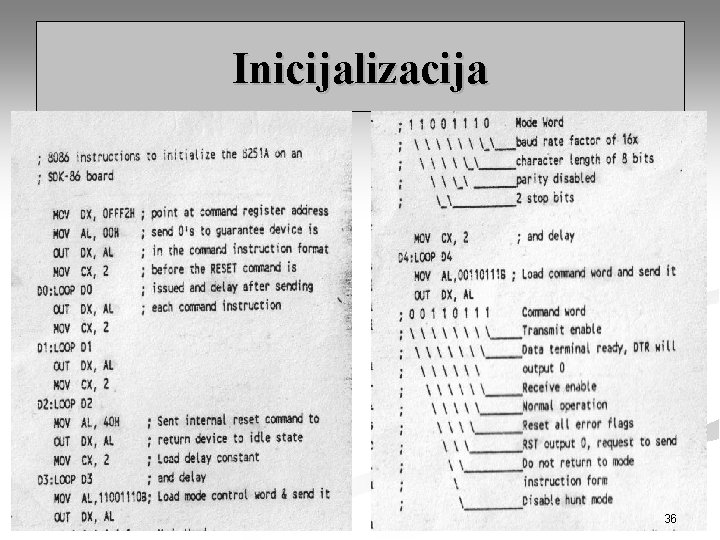

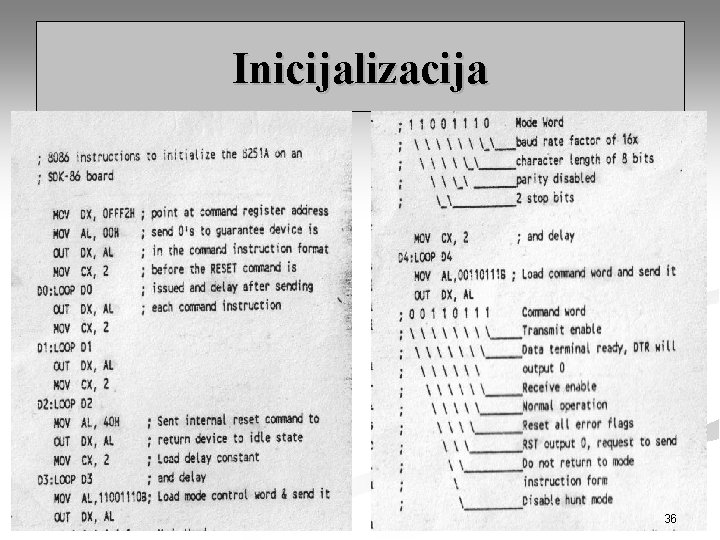

Inicijalizacija n n n prilikom inicijalizacije uređaja, treba obratiti pažnju i na “vreme oporavka” (write-recovery time)koje iznosi 16 taktova signala prikačenog na ulazni CLK pin prilikom upisivanja “običnih” podataka u 8251 a, ne treba voditi računa o ovome, pošto novi karakter ne može biti upisan, sve dok se prethodni shiftuje kroz shift registar, a ovo vreme je mnogo duže od vremena oporavka sledeća slika prikazuje kako treba inicijalizovati 8251 a 35

Inicijalizacija 36

Slanje i primanje karaktera n karaktere možemo slati i primati na 2 načina n mehanizmom interrupt-a n mehanizmom polling-a 37

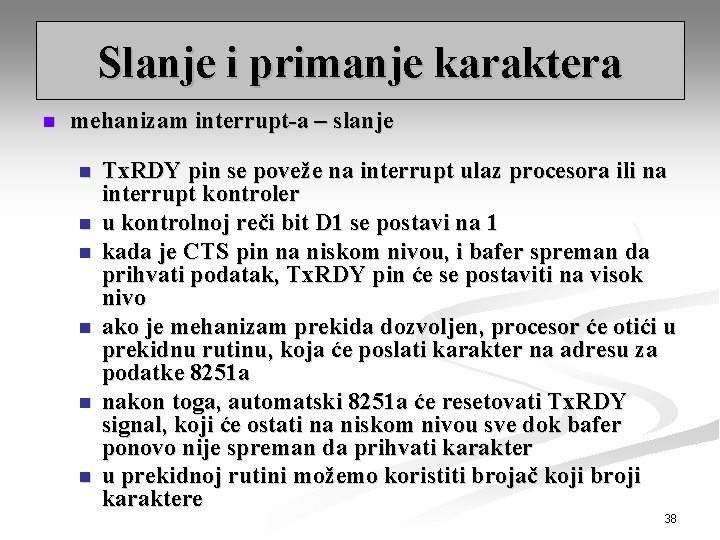

Slanje i primanje karaktera n mehanizam interrupt-a – slanje n n n Tx. RDY pin se poveže na interrupt ulaz procesora ili na interrupt kontroler u kontrolnoj reči bit D 1 se postavi na 1 kada je CTS pin na niskom nivou, i bafer spreman da prihvati podatak, Tx. RDY pin će se postaviti na visok nivo ako je mehanizam prekida dozvoljen, procesor će otići u prekidnu rutinu, koja će poslati karakter na adresu za podatke 8251 a nakon toga, automatski 8251 a će resetovati Tx. RDY signal, koji će ostati na niskom nivou sve dok bafer ponovo nije spreman da prihvati karakter u prekidnoj rutini možemo koristiti brojač koji broji karaktere 38

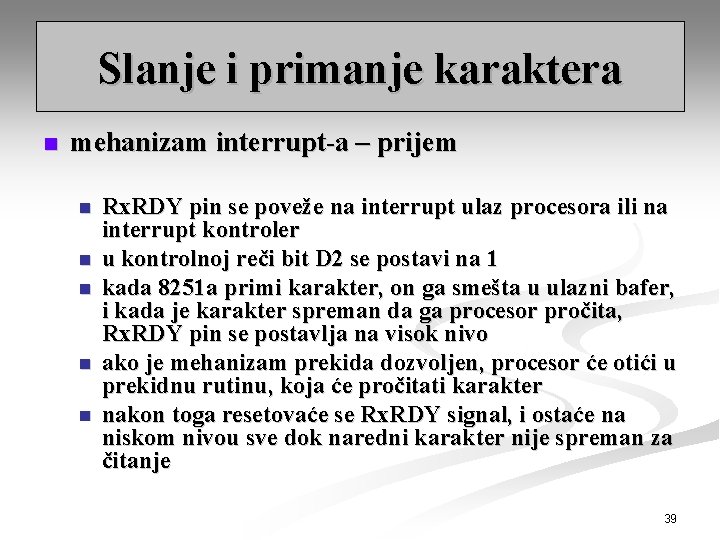

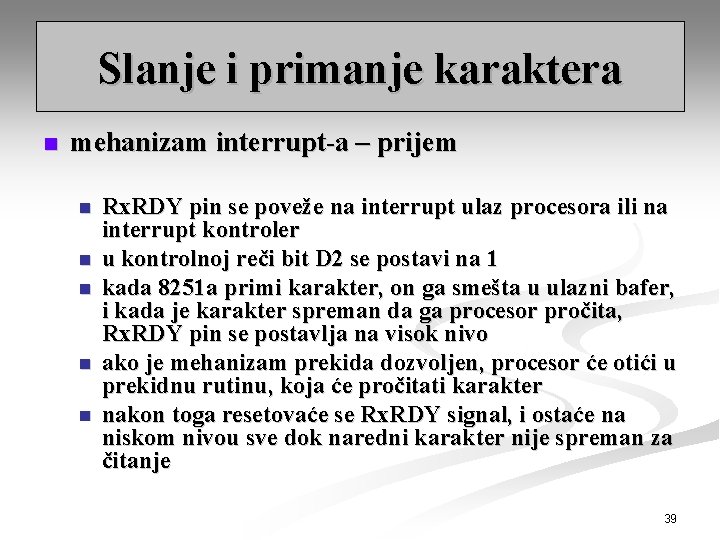

Slanje i primanje karaktera n mehanizam interrupt-a – prijem n n n Rx. RDY pin se poveže na interrupt ulaz procesora ili na interrupt kontroler u kontrolnoj reči bit D 2 se postavi na 1 kada 8251 a primi karakter, on ga smešta u ulazni bafer, i kada je karakter spreman da ga procesor pročita, Rx. RDY pin se postavlja na visok nivo ako je mehanizam prekida dozvoljen, procesor će otići u prekidnu rutinu, koja će pročitati karakter nakon toga resetovaće se Rx. RDY signal, i ostaće na niskom nivou sve dok naredni karakter nije spreman za čitanje 39

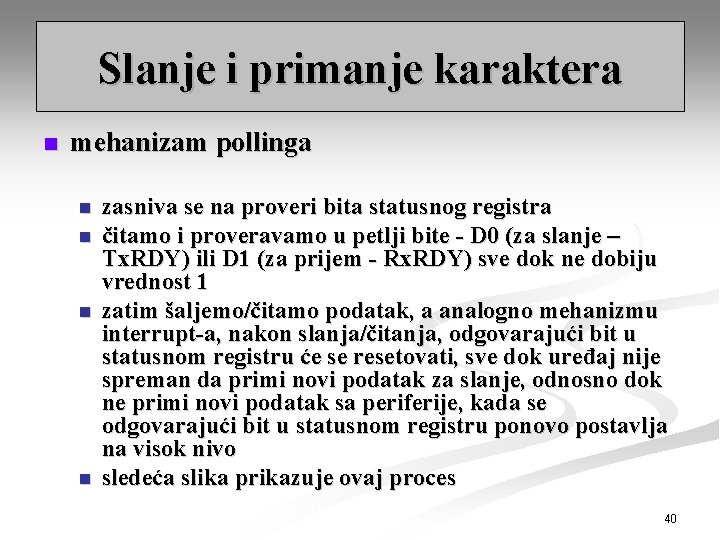

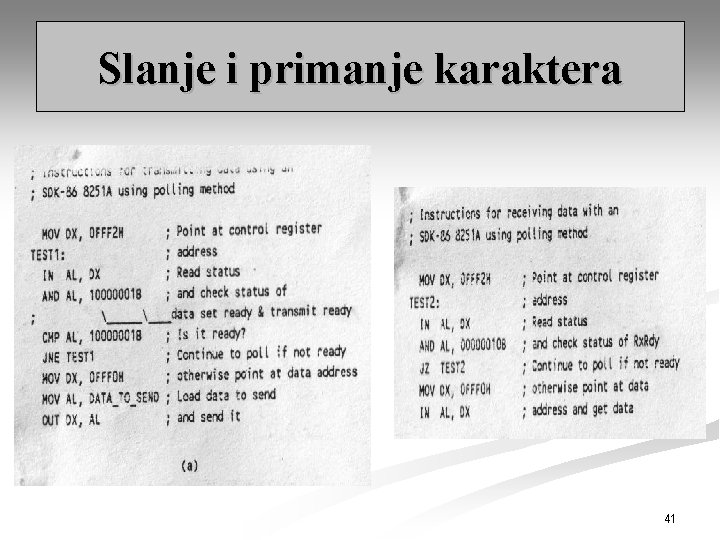

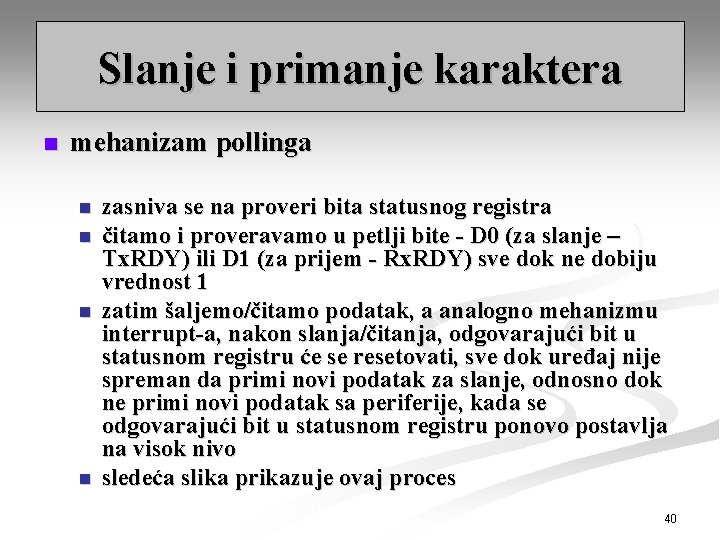

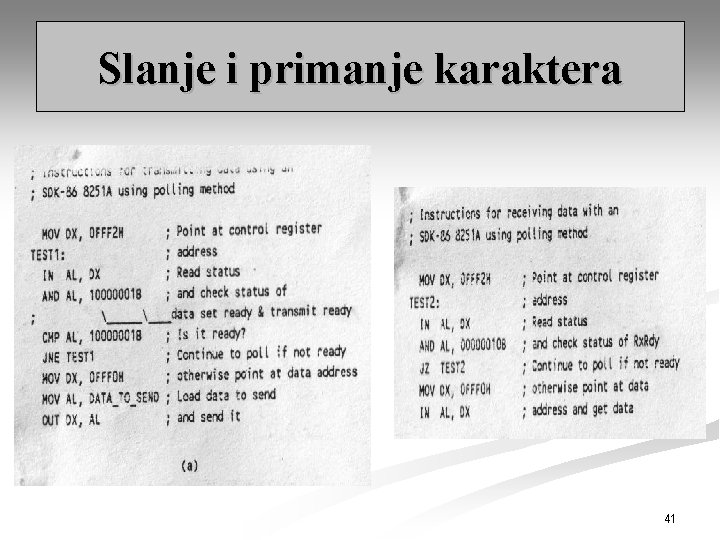

Slanje i primanje karaktera n mehanizam pollinga n n zasniva se na proveri bita statusnog registra čitamo i proveravamo u petlji bite - D 0 (za slanje – Tx. RDY) ili D 1 (za prijem - Rx. RDY) sve dok ne dobiju vrednost 1 zatim šaljemo/čitamo podatak, a analogno mehanizmu interrupt-a, nakon slanja/čitanja, odgovarajući bit u statusnom registru će se resetovati, sve dok uređaj nije spreman da primi novi podatak za slanje, odnosno dok ne primi novi podatak sa periferije, kada se odgovarajući bit u statusnom registru ponovo postavlja na visok nivo sledeća slika prikazuje ovaj proces 40

Slanje i primanje karaktera 41

RS-232 C standard n n n TTL nivoi signala (koje daje 8251 a na svojim izlazima) nisu pogodni za prenos na daljinu zato oni moraju biti konvertovani u drugi oblik – jedan od mogućih je i RS-232 C standard je razvijen 60 -ih godina kao rezultat potrebe da se povežu DTE i DCE uređaji n n DCE = Data Communication Equipment (modemi, i sl. . . ) DTE = Data Terminal Equipment (terminali, kompjuteri koji šalju i primaju podatke. . . ) 42

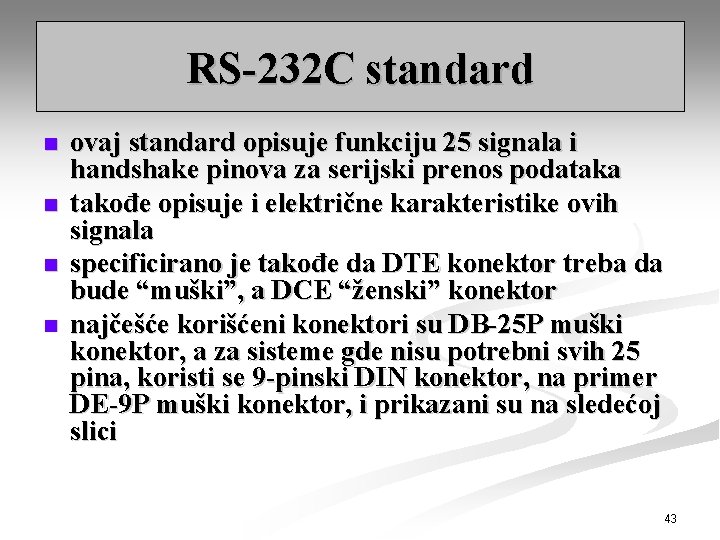

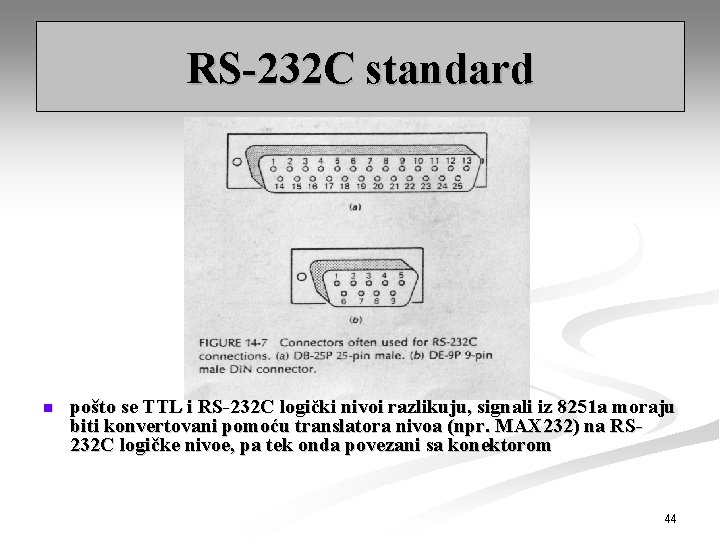

RS-232 C standard n n ovaj standard opisuje funkciju 25 signala i handshake pinova za serijski prenos podataka takođe opisuje i električne karakteristike ovih signala specificirano je takođe da DTE konektor treba da bude “muški”, a DCE “ženski” konektor najčešće korišćeni konektori su DB-25 P muški konektor, a za sisteme gde nisu potrebni svih 25 pina, koristi se 9 -pinski DIN konektor, na primer DE-9 P muški konektor, i prikazani su na sledećoj slici 43

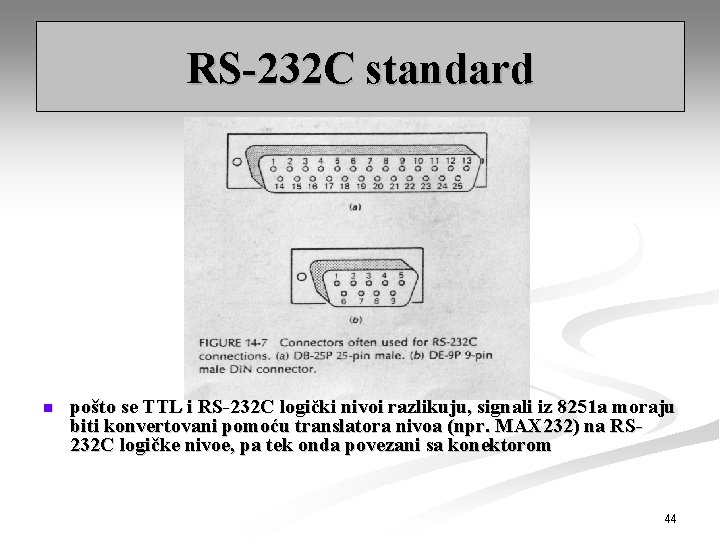

RS-232 C standard n pošto se TTL i RS-232 C logički nivoi razlikuju, signali iz 8251 a moraju biti konvertovani pomoću translatora nivoa (npr. MAX 232) na RS 232 C logičke nivoe, pa tek onda povezani sa konektorom 44

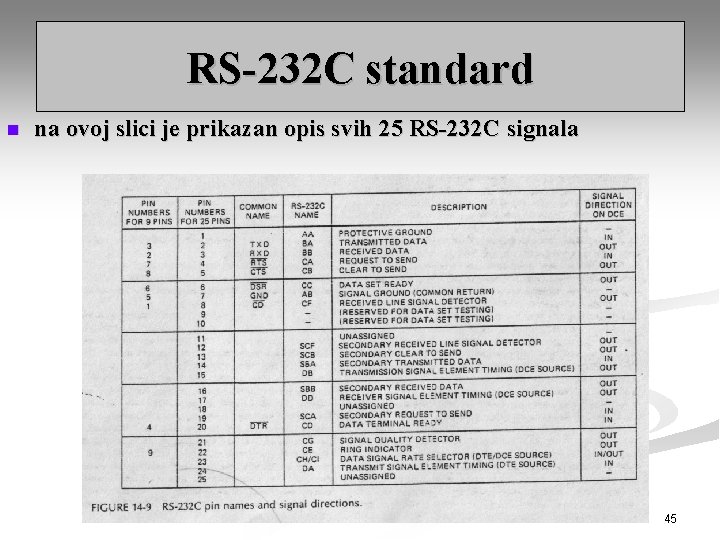

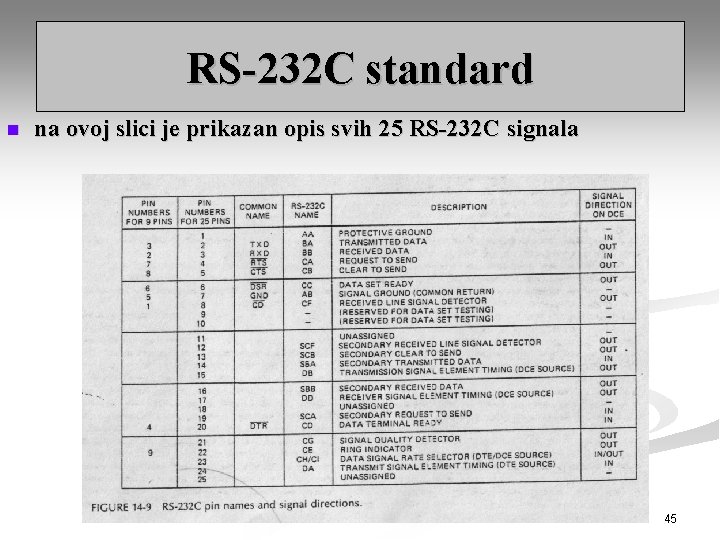

RS-232 C standard n na ovoj slici je prikazan opis svih 25 RS-232 C signala 45

Literatura n 1. Microprocessors and Interfacing – Douglas V. Hall n 2. Microcomputer Systems: The 8086/8088 Family – Yu Cheng Liu, Glenn A. Gibson 3. www. datasheetarchive. com n 46

Kraj prezentacije ; ). . . hvala na pažnji. . . prezentacija se može preuzeti sa: http: //galeb. etf. bg. ac. yu/~vm/os/osmips. html