Intel 8051 n Another family of microcontroller is

- Slides: 32

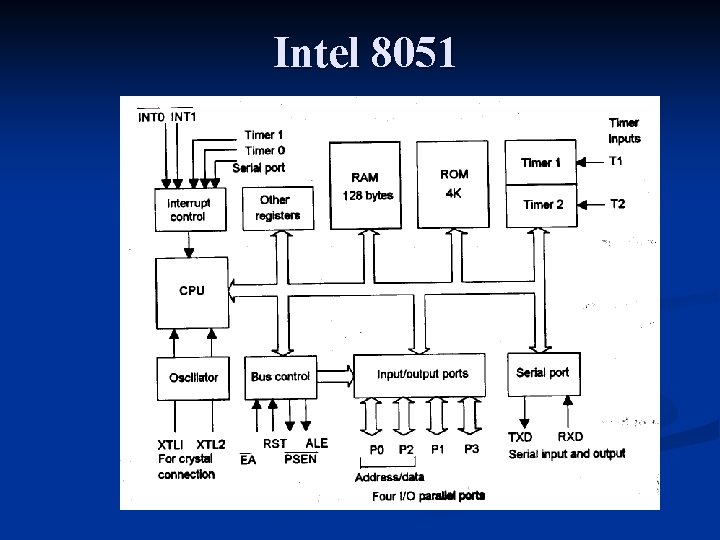

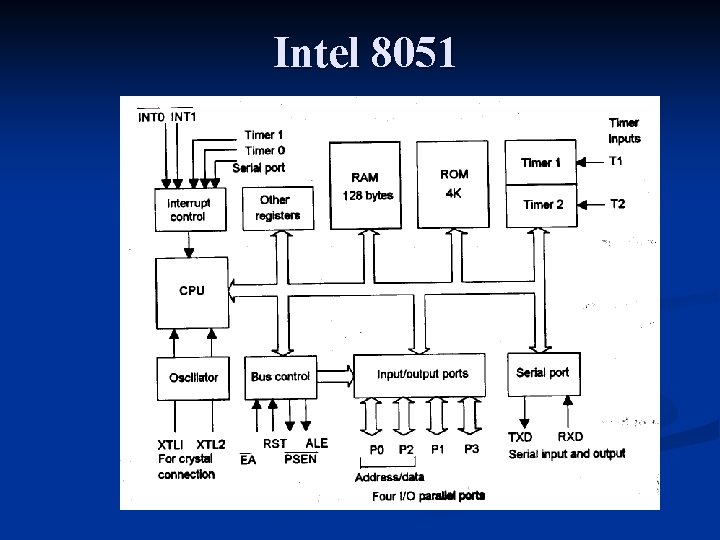

Intel 8051 n Another family of microcontroller is the Intel 8051 family. The basic 8051 microcontroller has four parallel input/output ports, port 0, 1, 2 and 3. The 8051 AH version has 4 K x 8 bytes ROM , 128 x 8 bytes RAM, two 16 -bit timers and interrupt control for five interrupt sources.

Intel 8051 The 8051 is a second-generation Intel 8 -bit microcontroller. The first Intel 8 -bit microcontroller was the 8048. n Later, Intel introduced the 8049, which double the amount of ROM and RAM. Its architecture is the same as the 8048 n A later introduction, the 8052, expands the size of ROM and RAM, but otherwise the architecture is the same as the 8051. n

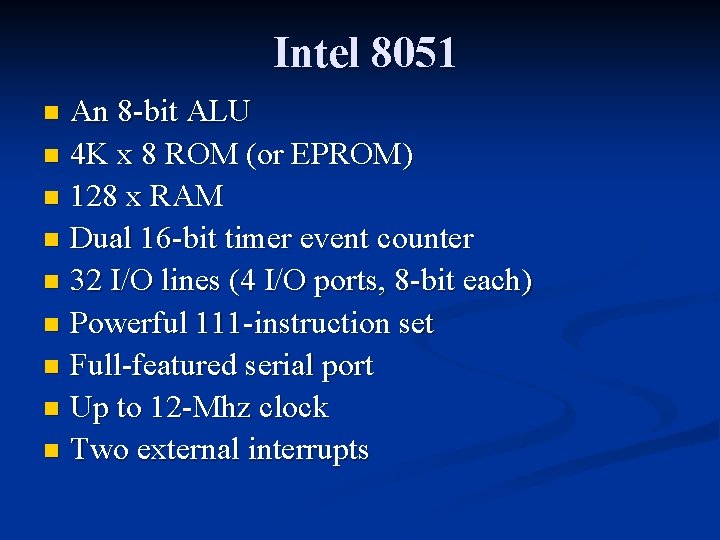

Intel 8051 An 8 -bit ALU n 4 K x 8 ROM (or EPROM) n 128 x RAM n Dual 16 -bit timer event counter n 32 I/O lines (4 I/O ports, 8 -bit each) n Powerful 111 -instruction set n Full-featured serial port n Up to 12 -Mhz clock n Two external interrupts n

Intel 8051 The 8051 can address external memory if there is not enough internal RAM and/or ROM. When used to address external memory, two ports provide the memory addressing. n The 8051 internal ROM is for program memory space. The program memory space is a readonly space. The processor cannot write data or read data from these memory locations. n

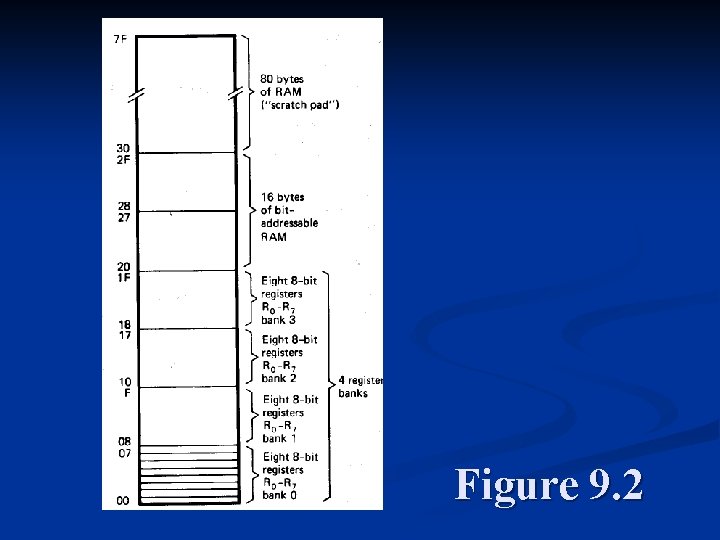

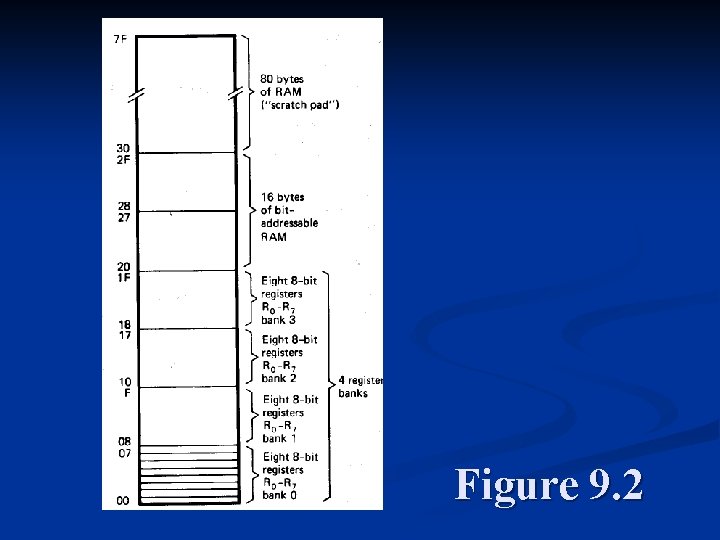

Intel 8051 The RAM is the data memory space. It is a read -write memory space. n The processor can read data from this memory space and can write data to this memory space. It cannot execute program instructions from this memory space. n The 128 bytes of internal RAM (00 H to 7 FH) provide general read-write data storage. Part of this memory space is often referred to as general purpose registers. n

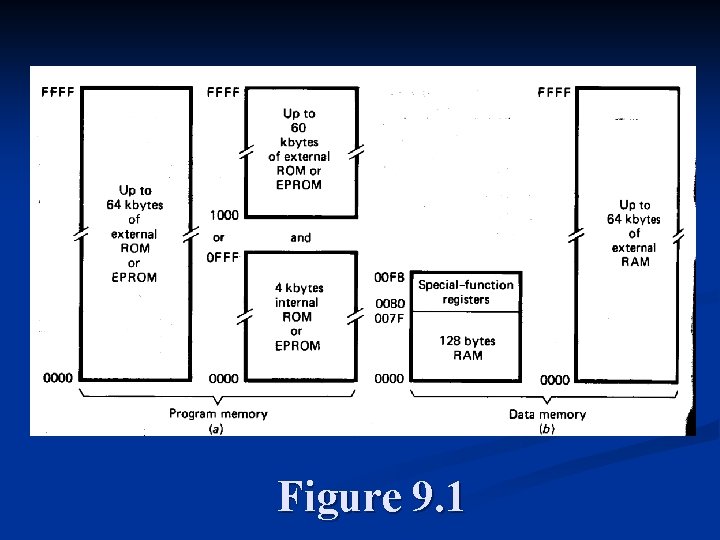

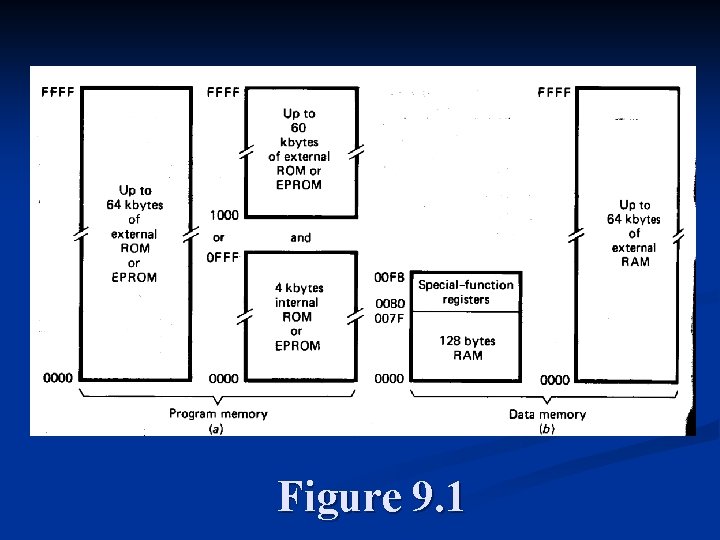

Intel 8051 The 8051 also has 22 special-function registers occupy data memory space from 80 H to F 8 H. Although addressable as memory locations, these registers must be used for their intended purpose. n If more program memory (ROM) is needed, the internal 4 -Kbyte memory can be expanded by additional 60 -Kbytes, giving the 8051 a full 64 kbytes program memory space. (see figure 9. 1) n

Intel 8051 n If the 8051 EA pin is connected to ground, it does not use the internal 4 K ROM. The external memory must start at memory location 0000 H and can be up to a full 64 kbytes. (8031 does not have internal ROM)

Figure 9. 1

Figure 9. 2

Intel 8051 n If you need more RAM, you can add external data memory. You always have full use of all 64 -kbytes of the external memory space. This memory is addressed separately from the internal 128 bytes of RAM.

Downloaded Program n Although the 8051 normally operates with separate program memory and data memory space, there applications where 8051 can input a block of data through its serial communications port, load that data into memory, and then execute that data as a program. It is a very common technique used to change the program operating in a remote microprocessor-based controller.

Intel 8051 Internal RAM The first 32 RAM locations are addressable as registers or as memory locations. By calling some memory locations registers, we can access them with single-byte instruction. n 16 bytes of 8051 RAM are both bit and byteaddressable. The general instructions can address a byte of data at these memory locations. Other special instructions can address any individual bit in these memory locations. Bit instructions are very powerful tools when you need to process data words from external hardware devices. n

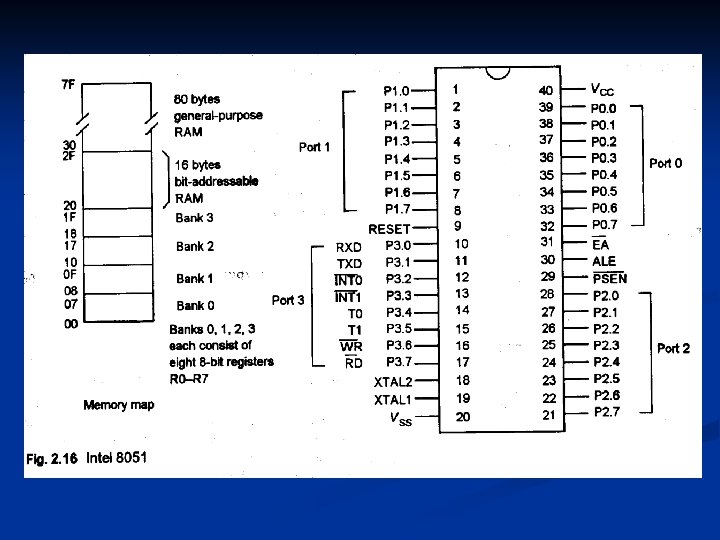

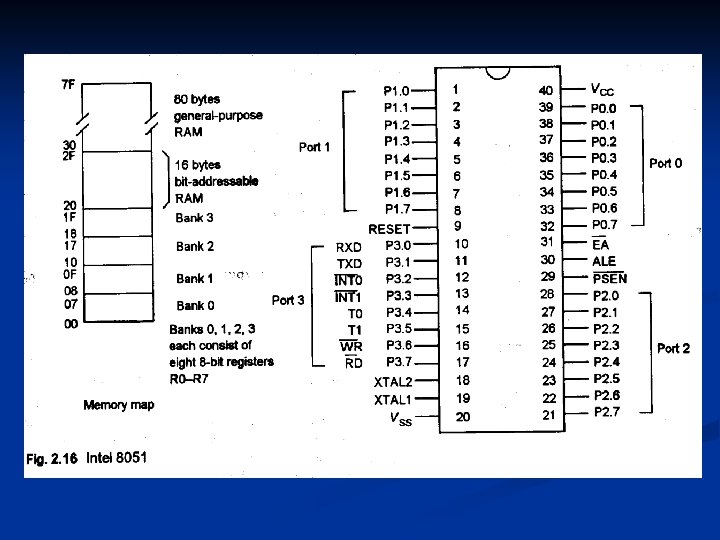

Intel 8051 Internal RAM. . n Figure 9. 2 is a memory map of the first 128 internal memory locations. The first 32 memory locations can be used as four register banks. There are eight registers in each bank. A register is an 8 -bit read-write memory location which is addressed in a single-byte instruction. Because these single-byte instructions have only 3 bits available to address the register, they address only one of eight registers.

Special Function Registers Special-function registers (SFRs). Each specialfunction register is dedicated to a single job. n The microprocessor’s SFRs are the accumulator (ACC E 0 H), the B register (B F 0 H), the program status word (PSW D 0 H), the stack pointer (SP 81 H), the data pointer (DPTR) which is a 2 bytes register (DPL 82 H and DPH 87 H), and the power control register (PCON 87 H). n

Special Function Registers Some of these SFRs are bit- and byteaddressable and others are only byteaddressable. n The accumulator is byte- or bit-addressable. It contains the operands or one of the operands of arithmetic or logical instruction and holds the result of that instruction. n The B register is used during multiply and divide operations as one 8 -bit source and to hold the high-order 8 bits. It also can be as a simple scratch-pad register. n

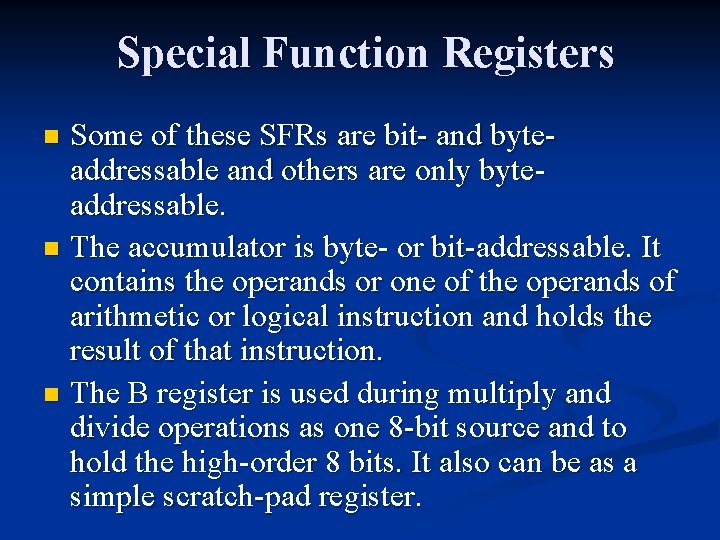

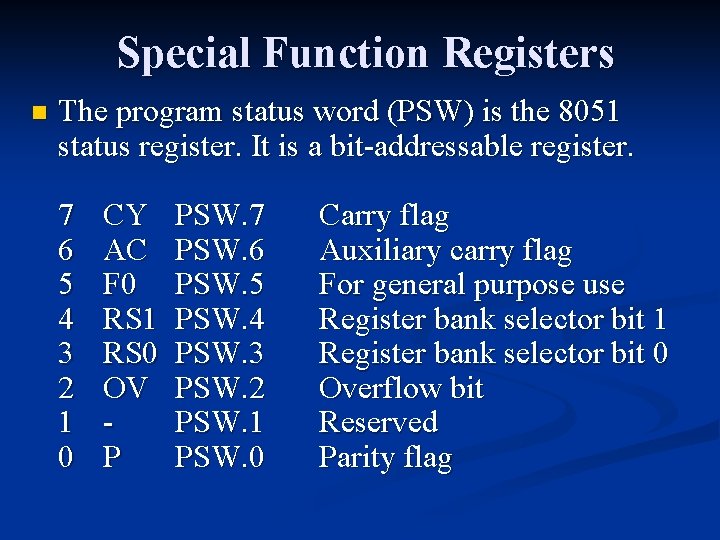

Special Function Registers n The program status word (PSW) is the 8051 status register. It is a bit-addressable register. 7 6 5 4 3 2 1 0 CY AC F 0 RS 1 RS 0 OV P PSW. 7 PSW. 6 PSW. 5 PSW. 4 PSW. 3 PSW. 2 PSW. 1 PSW. 0 Carry flag Auxiliary carry flag For general purpose use Register bank selector bit 1 Register bank selector bit 0 Overflow bit Reserved Parity flag

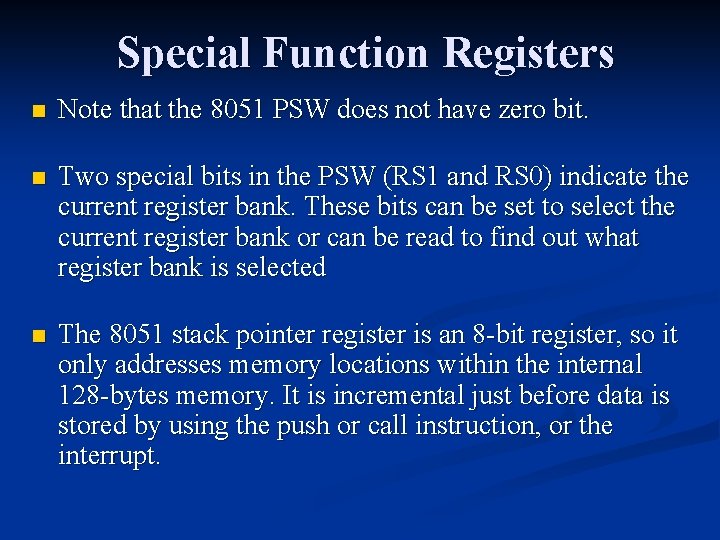

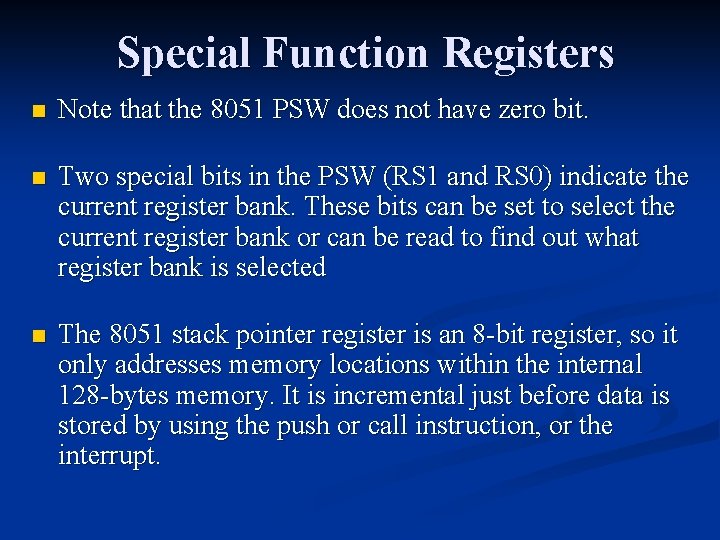

Special Function Registers n Note that the 8051 PSW does not have zero bit. n Two special bits in the PSW (RS 1 and RS 0) indicate the current register bank. These bits can be set to select the current register bank or can be read to find out what register bank is selected n The 8051 stack pointer register is an 8 -bit register, so it only addresses memory locations within the internal 128 -bytes memory. It is incremental just before data is stored by using the push or call instruction, or the interrupt.

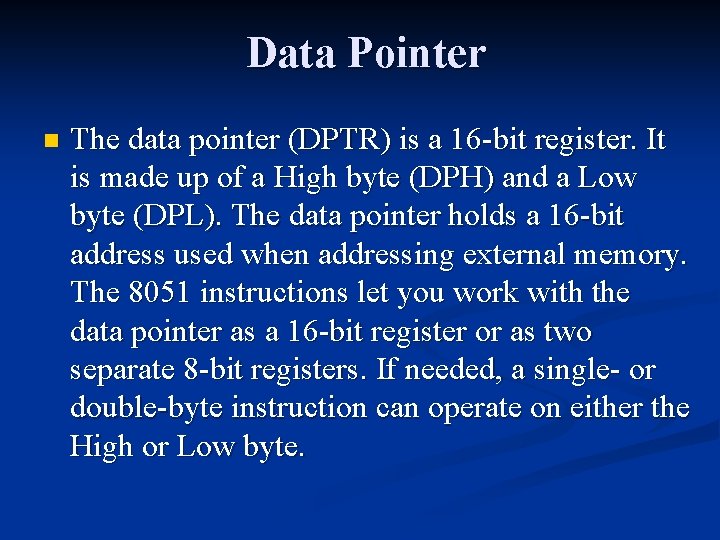

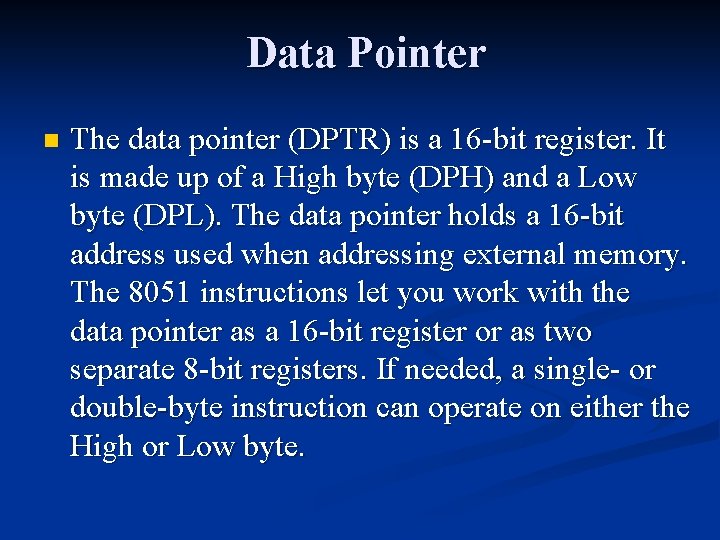

Data Pointer n The data pointer (DPTR) is a 16 -bit register. It is made up of a High byte (DPH) and a Low byte (DPL). The data pointer holds a 16 -bit address used when addressing external memory. The 8051 instructions let you work with the data pointer as a 16 -bit register or as two separate 8 -bit registers. If needed, a single- or double-byte instruction can operate on either the High or Low byte.

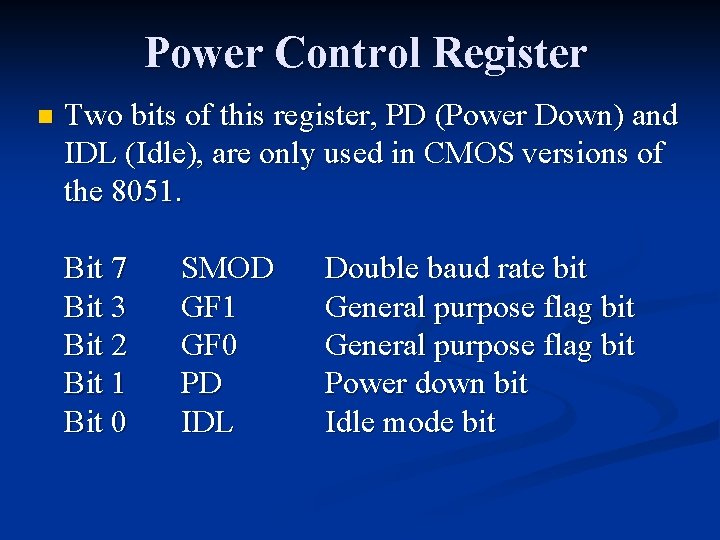

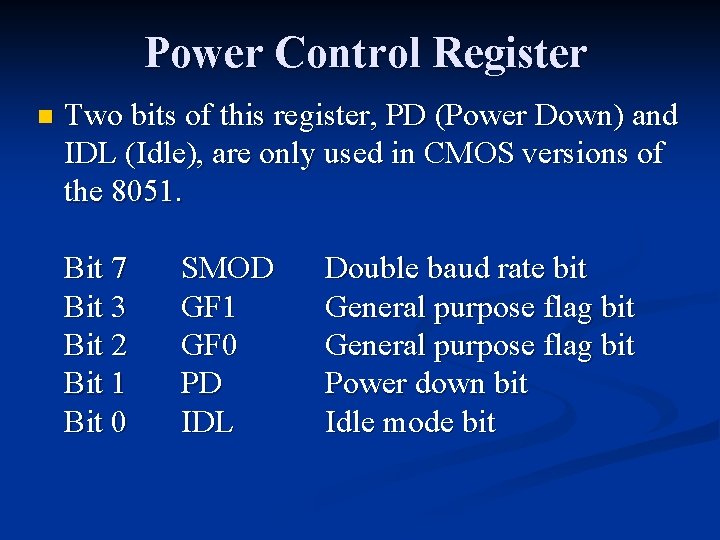

Power Control Register n Two bits of this register, PD (Power Down) and IDL (Idle), are only used in CMOS versions of the 8051. Bit 7 Bit 3 Bit 2 Bit 1 Bit 0 SMOD GF 1 GF 0 PD IDL Double baud rate bit General purpose flag bit Power down bit Idle mode bit

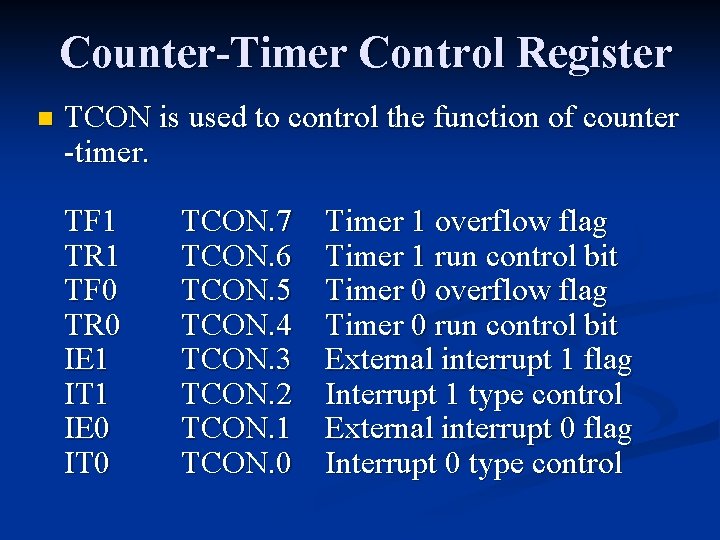

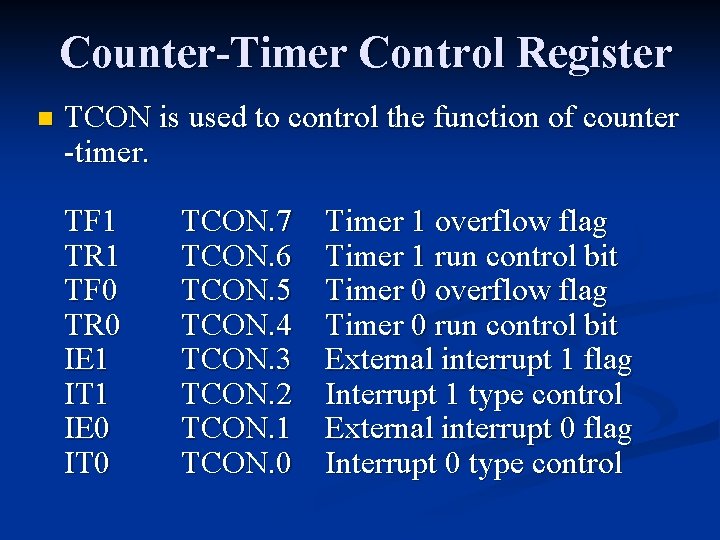

Counter-Timer Control Register n TCON is used to control the function of counter -timer. TF 1 TR 1 TF 0 TR 0 IE 1 IT 1 IE 0 IT 0 TCON. 7 TCON. 6 TCON. 5 TCON. 4 TCON. 3 TCON. 2 TCON. 1 TCON. 0 Timer 1 overflow flag Timer 1 run control bit Timer 0 overflow flag Timer 0 run control bit External interrupt 1 flag Interrupt 1 type control External interrupt 0 flag Interrupt 0 type control

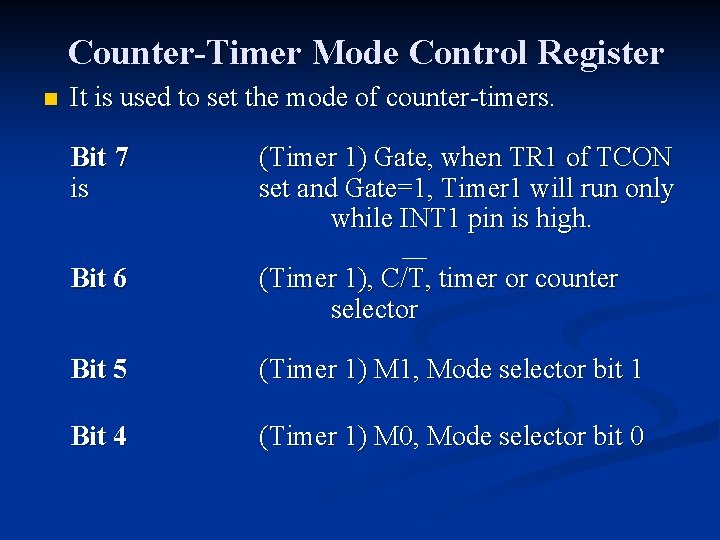

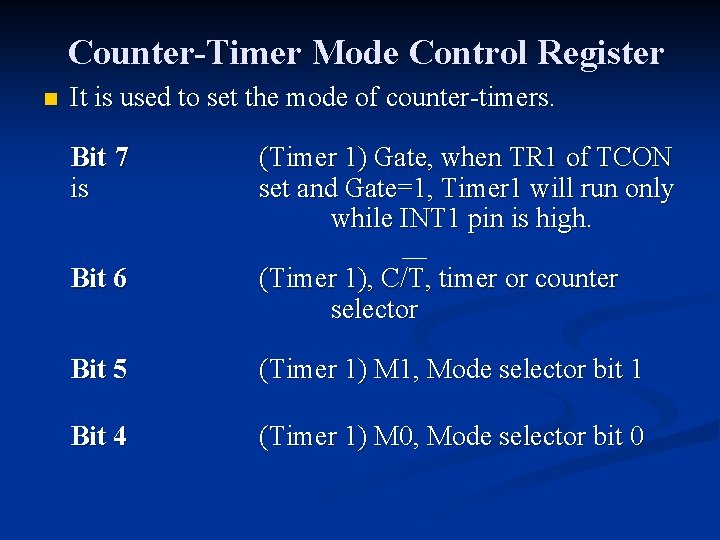

Counter-Timer Mode Control Register n It is used to set the mode of counter-timers. Bit 7 is (Timer 1) Gate, when TR 1 of TCON set and Gate=1, Timer 1 will run only while INT 1 pin is high. Bit 6 (Timer 1), C/T, timer or counter selector Bit 5 (Timer 1) M 1, Mode selector bit 1 Bit 4 (Timer 1) M 0, Mode selector bit 0

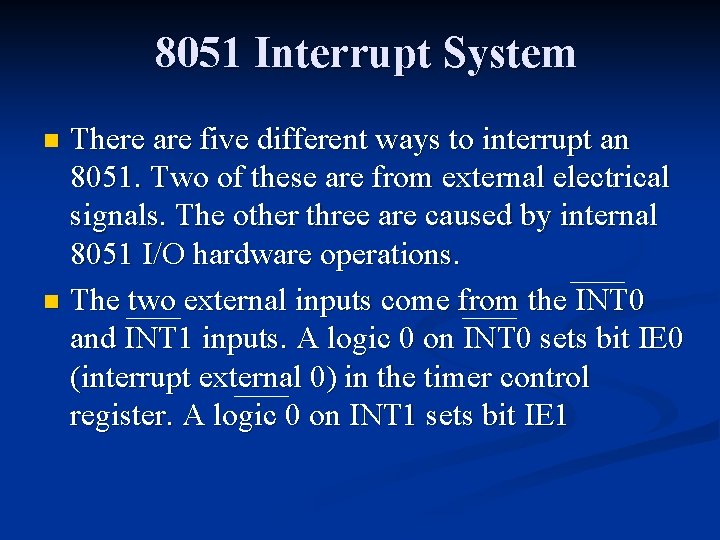

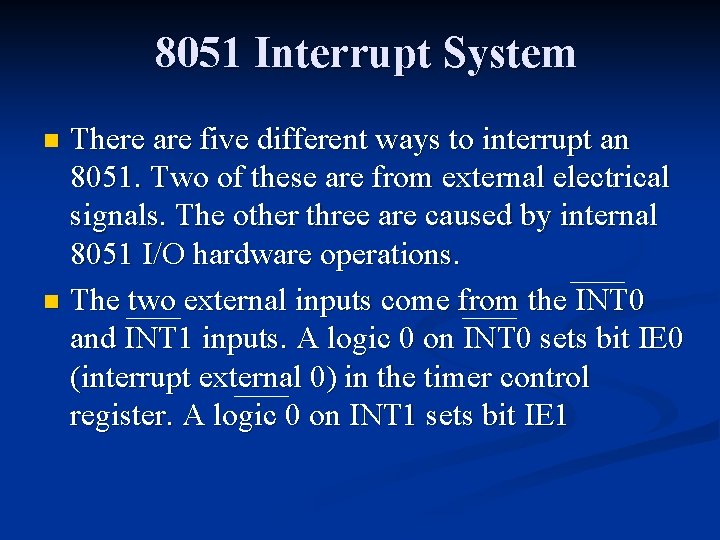

8051 Interrupt System There are five different ways to interrupt an 8051. Two of these are from external electrical signals. The other three are caused by internal 8051 I/O hardware operations. n The two external inputs come from the INT 0 and INT 1 inputs. A logic 0 on INT 0 sets bit IE 0 (interrupt external 0) in the timer control register. A logic 0 on INT 1 sets bit IE 1 n

Intel 8051

Intel 8051 n Port 0 is at address 80 H, port 1 at address 90 H, port 2 at address A 0 H and port 3 at address B 0 H. When a port is to be used as an output port the data is put into the corresponding special register. When a port is to be used as an input port, the value FFH must first be written to it.

Intel 8051 RXD is the serial input port n TXD is the serial output port n INT 0 is the external interrupt 0 n INT 1 is the external interrupt 1 n T 0 is the timer/counter 0 external input n T 1 is the timer/counter 1 external input n WR is the external memory write strobe n RD is the external memory read strobe n

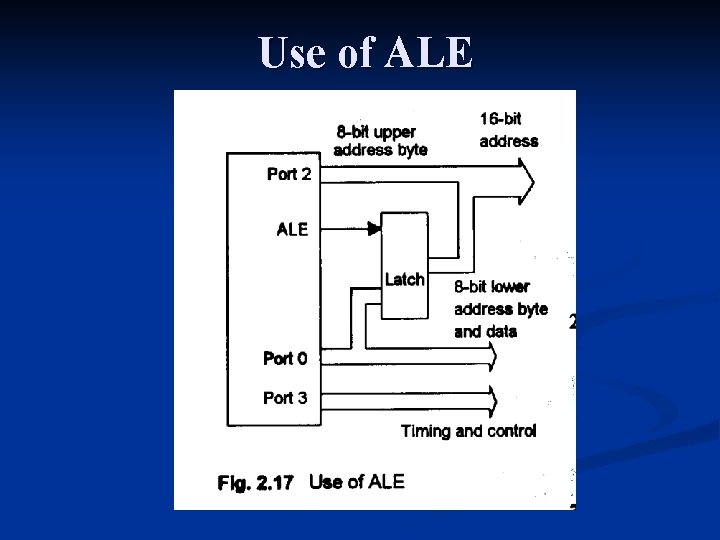

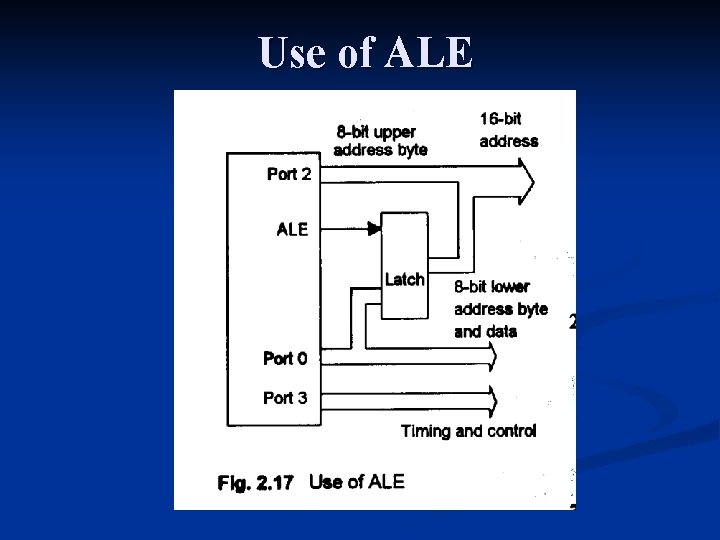

Intel 8051 n The term strobe describes a connection used to enable or disable a particular function. n ALE The address latch enable pin provides an output pulse for latching the low-order byte of the address during access to external memory. This allows 16 -bit addresses to be used. (see next slide)

Use of ALE

Intel 8051 n PSEN The program store enable pin is the read signal pin for external program memory and is active when low. It is connected to the output enable pin of external ROM or EPROM. n EA The external access pin is taken low for the microprocessor to access only external program code; when high it automatically accesses internal or external code, depending on the address. This pin also used on a microcontroller with EPROM to receive the programming supply voltage for programming the EPROM

Intel 8051 n XTAL 1, XTAL 2 These are the connecting pins for a crystal or external oscillator. n RESET A high signal for a minimum of two machine cycles on this pin resets the microcontroller.

Intel 8051 n Serial input/output Writing to the serial data buffer SBUF at address 99 H load data for transmission; reading SBUF accesses received data. n Timing The timer mode register TMOD at address 89 H is used to set the operating mode for timer 0 and timer 1. The timer control register TCON contains status and control bit for timer 0 and timer 1.

Intel 8051 n Interrupts force program to call a subroutine located at a specified address in memory; they are enable by writing to the interrupt enable register IE at address A 8 H. Bit 7 = EA (Global Enable/Disable) Bit 4 = ES (Enable serial port interrupt) Bit 3 = ET 1 (Enable Timer 1 interrupt) Bit 2 = EX 1 (Enable external 1 interrupt) Bit 1 = ET 0 (Enable timer 0 interrupt) Bit 0 = EX 0 (Enable external 0 interrupt)