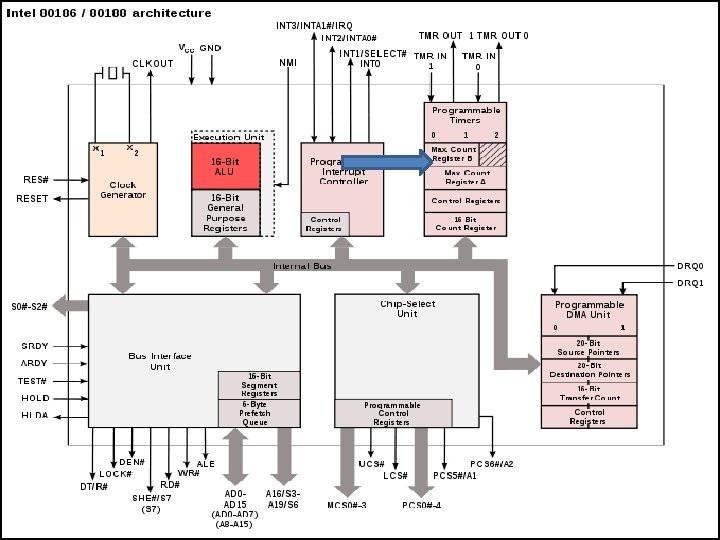

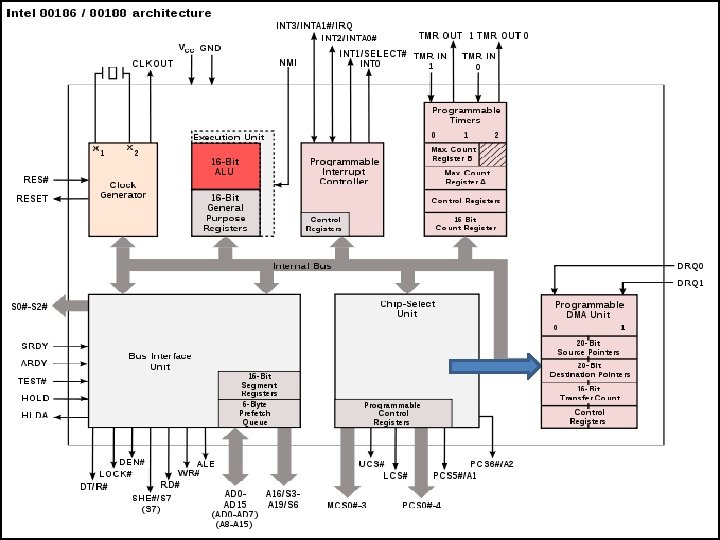

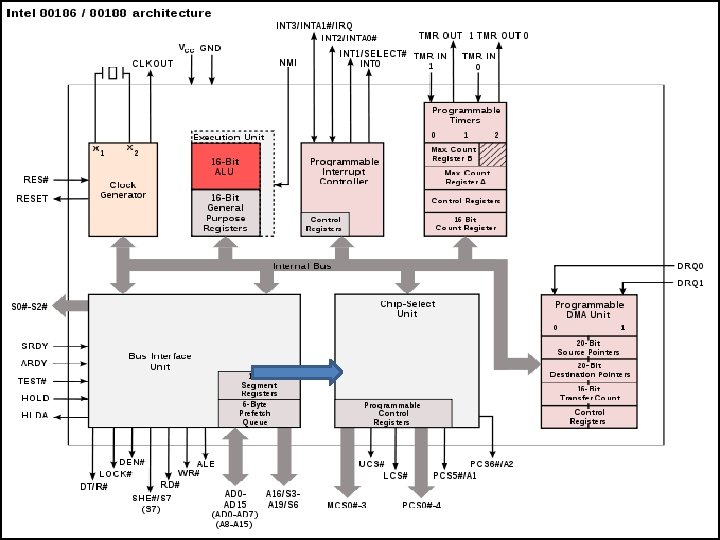

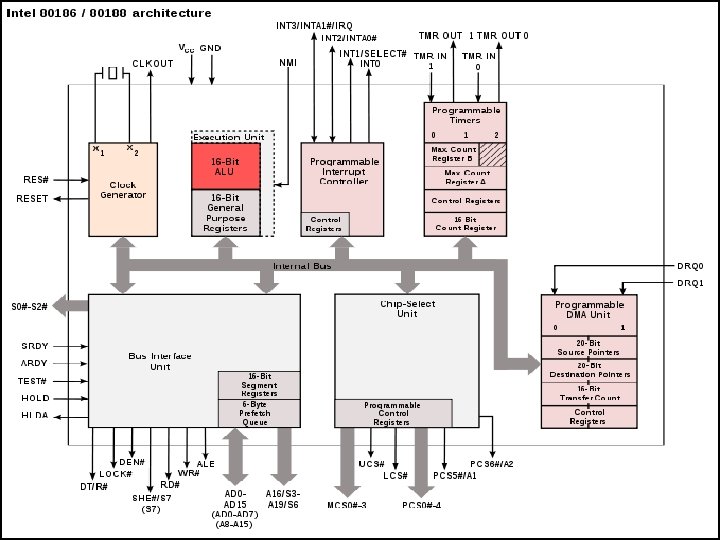

INTEL 80186 INTEL 80186 BASIC BLOCK DIAGRAM IN

INTEL 80186

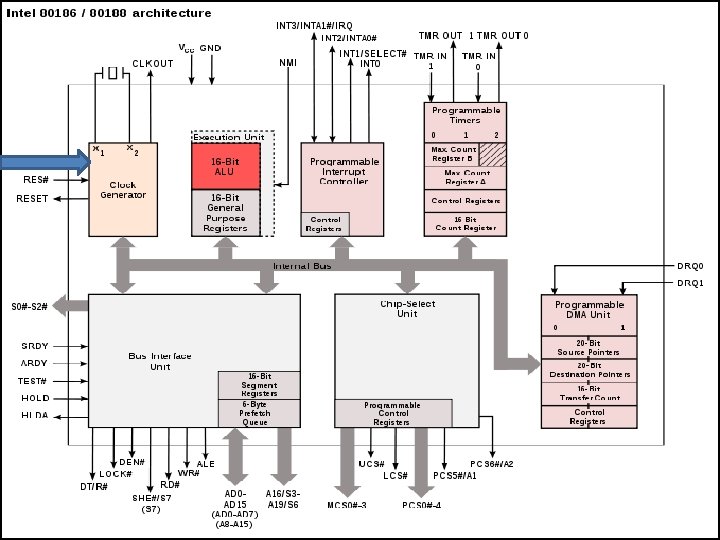

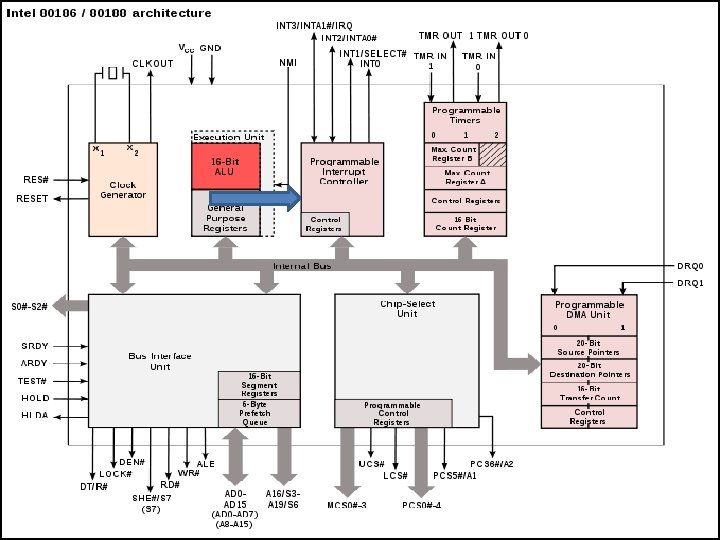

INTEL 80186 BASIC BLOCK DIAGRAM IN ADDITION TO THE BIU AND EU 80186/80188 FAMILY CONTAINS Ø A CLOCK GENERATOR, Ø A PROGRAMMABLE INTERRUPT CONTROLLER Ø PROGRAMMABLE TIMERS Ø A PROGRAMMABLE DMA CONTROLLER Ø A PROGRAMMABLE CHIP SELECTION UNIT.

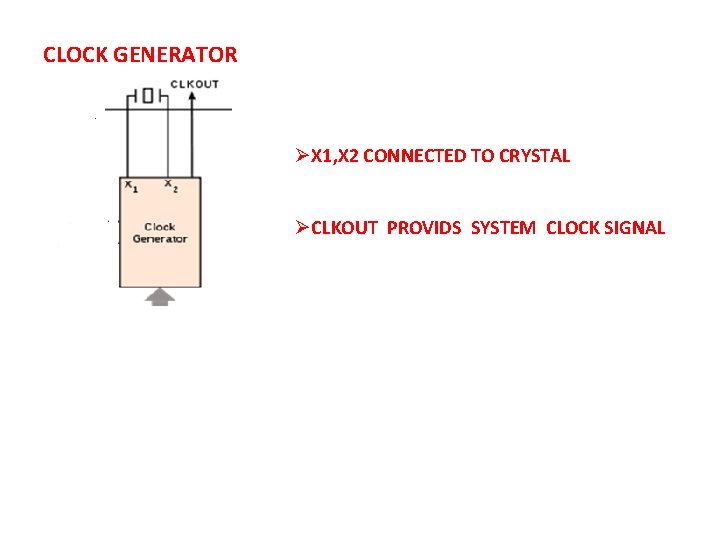

CLOCK GENERATOR ØX 1, X 2 CONNECTED TO CRYSTAL ØCLKOUT PROVIDS SYSTEM CLOCK SIGNAL

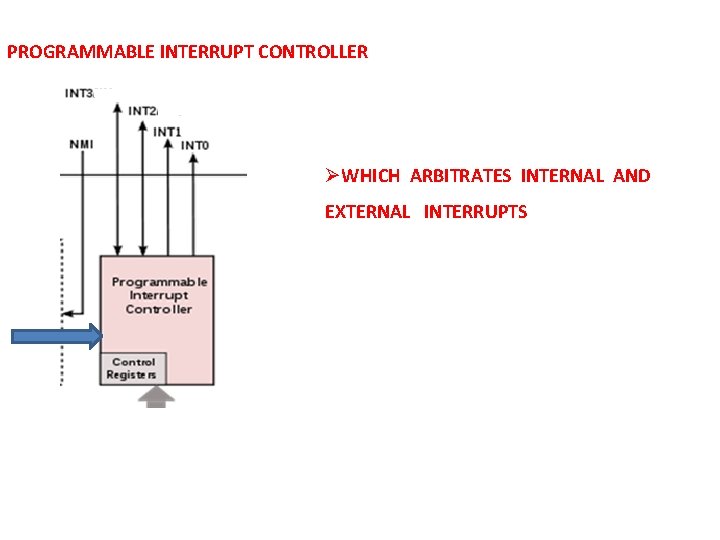

PROGRAMMABLE INTERRUPT CONTROLLER ØWHICH ARBITRATES INTERNAL AND EXTERNAL INTERRUPTS

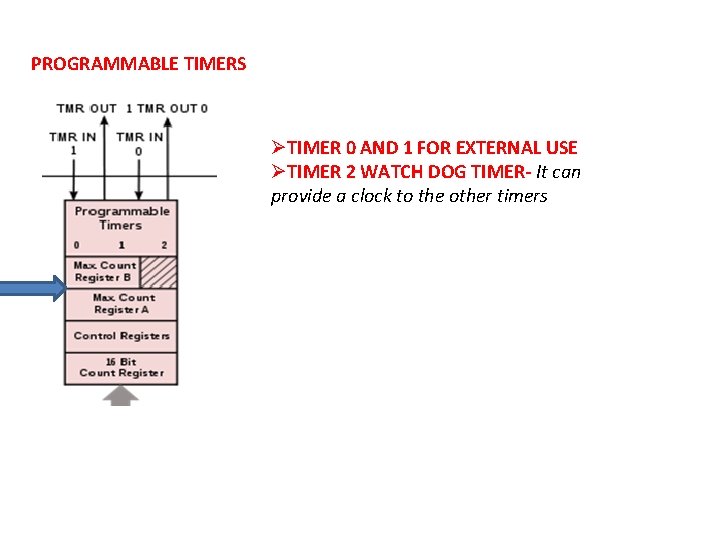

PROGRAMMABLE TIMERS ØTIMER 0 AND 1 FOR EXTERNAL USE ØTIMER 2 WATCH DOG TIMER- It can provide a clock to the other timers

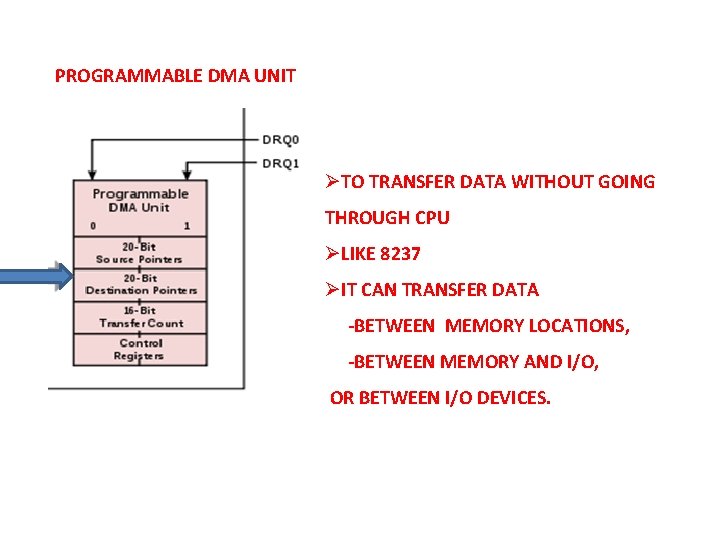

PROGRAMMABLE DMA UNIT ØTO TRANSFER DATA WITHOUT GOING THROUGH CPU ØLIKE 8237 ØIT CAN TRANSFER DATA -BETWEEN MEMORY LOCATIONS, -BETWEEN MEMORY AND I/O, OR BETWEEN I/O DEVICES.

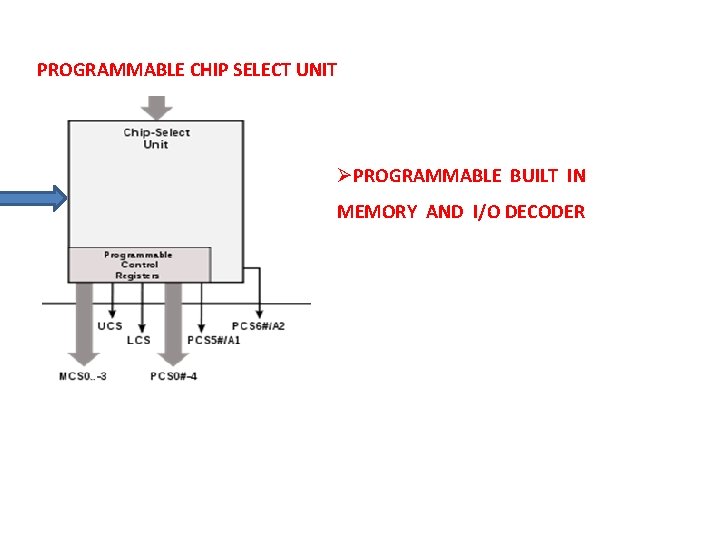

PROGRAMMABLE CHIP SELECT UNIT ØPROGRAMMABLE BUILT IN MEMORY AND I/O DECODER

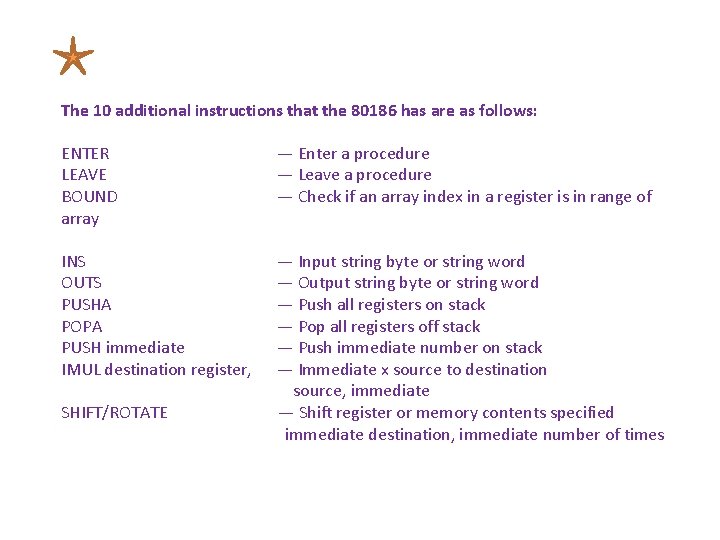

The 10 additional instructions that the 80186 has are as follows: ENTER LEAVE BOUND array — Enter a procedure — Leave a procedure — Check if an array index in a register is in range of INS OUTS PUSHA POPA PUSH immediate IMUL destination register, — Input string byte or string word — Output string byte or string word — Push all registers on stack — Pop all registers off stack — Push immediate number on stack — Immediate x source to destination source, immediate — Shift register or memory contents specified immediate destination, immediate number of times SHIFT/ROTATE

- Slides: 14