Integration of Photonic Functions in and with Silicon

![Racetrack Resonator l l l normalized transfer [d. B] l 8 m Wire width Racetrack Resonator l l l normalized transfer [d. B] l 8 m Wire width](https://slidetodoc.com/presentation_image_h2/4fa59d7032c7321bfbecc201e2734d0d/image-32.jpg)

- Slides: 50

Integration of Photonic Functions in and with Silicon Roel Baets Wim Bogaerts, Pieter Dumon, Günther Roelkens, Ilse Christiaens, Kurt De Mesel, Dirk Taillaert, Bert Luyssaert, Joris Van Campenhout, Peter Bienstman, Dries Van Thourhout, Vincent Wiaux, Johan Wouters, Stephan Beckx Photonics Research Group http: //photonics. intec. UGent. be Ghent University and IMEC

Outline • why Silicon photonics? • sub-micron photonics in Silicon? • heterogeneous integration of III-V components onto Silicon? © intec 2004 http: //photonics. intec. UGent. be 2

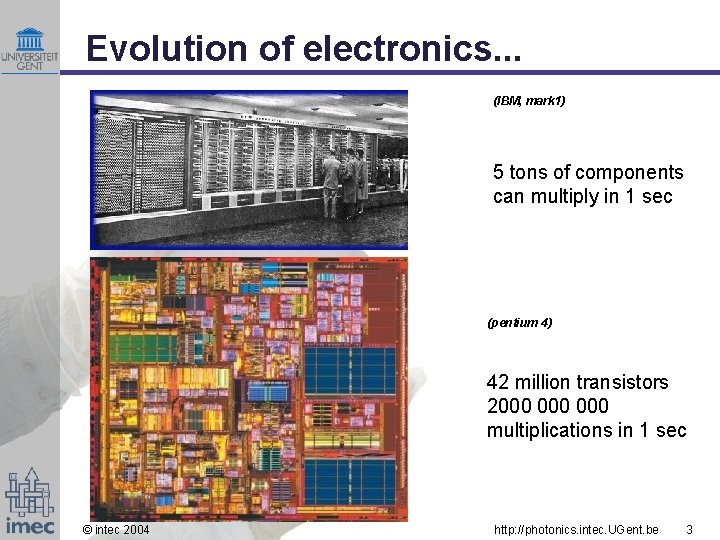

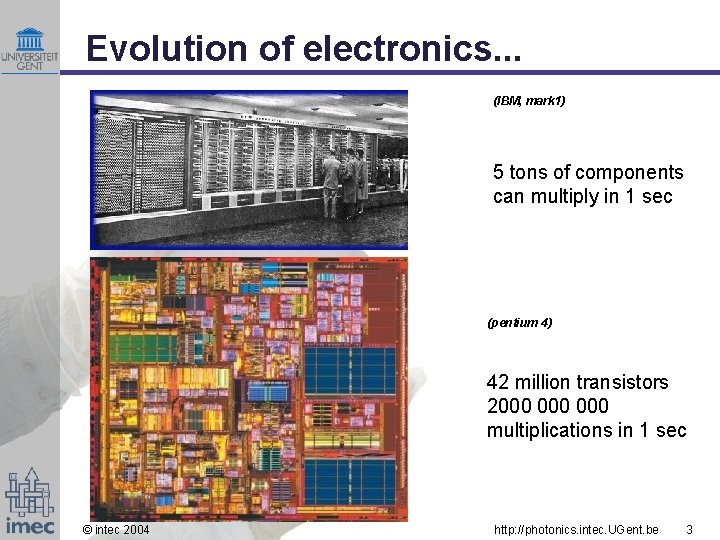

Evolution of electronics. . . (IBM, mark 1) 5 tons of components can multiply in 1 sec (pentium 4) 42 million transistors 2000 000 multiplications in 1 sec © intec 2004 http: //photonics. intec. UGent. be 3

Success of electronics? Integrated circuits l economics of wafer scale integration l performance (smaller is faster!) l miniaturization in its own right l complex function can be made by a limited number of high-yield processes l n focus on one production technology n few companies in the food chain all efforts on the same material = Silicon © intec 2004 http: //photonics. intec. UGent. be 4

Should we integrate in photonics? Yes! there are good reasons to do so l economics of wafer scale integration l performance l miniaturization l integrate with electronics l reduce costly optical packaging!!! n optical packaging is expensive! (often requires manual and/or active alignment at (sub)-micron level) n more integration = less packaging © intec 2004 http: //photonics. intec. UGent. be 5

The key bottleneck of photonic integration (By far too) many degrees of freedom l many different materials l many different component types l many different wavelength ranges Hence: l no generic integration technology for many different applications l no high volume technology platforms l too high cost Hence: Integration is not an industrial reality (yet) © intec 2004 http: //photonics. intec. UGent. be 6

The way out - a roadmap 1. Use mainstream Silicon(-based) technology l wherever possible, CMOS fab compatible l otherwise, use dedicated Silicon fab 2. Add other materials where needed for specialty functions l if the added value motivates it l 3. By using l l wherever possible : wafer-scale post-processing technology (build-up) otherwise, die-scale technology 4. Build a photonic IC industry on this basis © intec 2004 http: //photonics. intec. UGent. be 7

Silicon-based photonic components and ICs Many examples: • detector arrays and solar cells • CCD and CMOS-based image sensors • micro-displays • MEMS devices • LEDs • Silica-on-Silicon passive photonic ICs © intec 2004 http: //photonics. intec. UGent. be 8

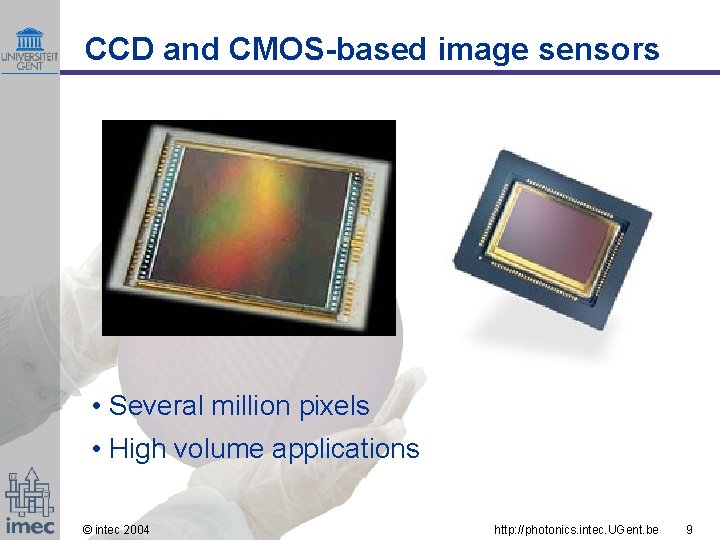

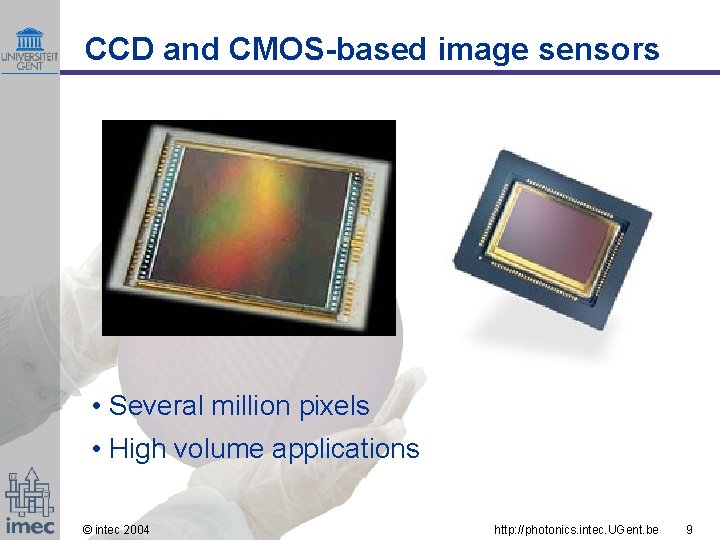

CCD and CMOS-based image sensors • Several million pixels • High volume applications © intec 2004 http: //photonics. intec. UGent. be 9

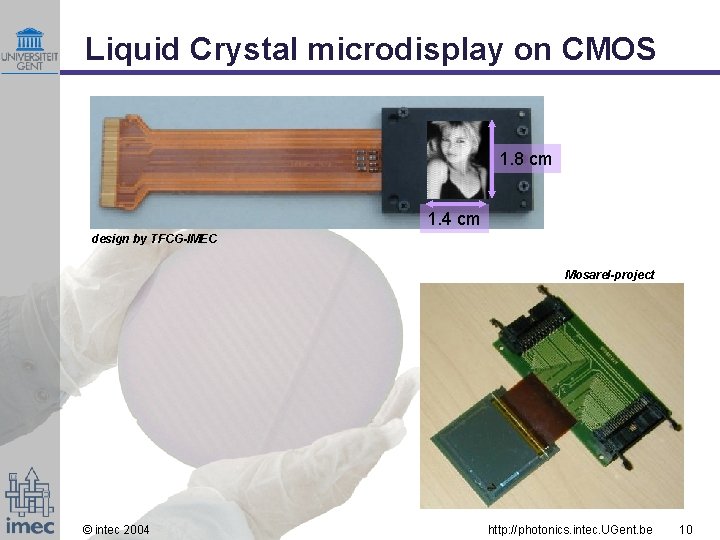

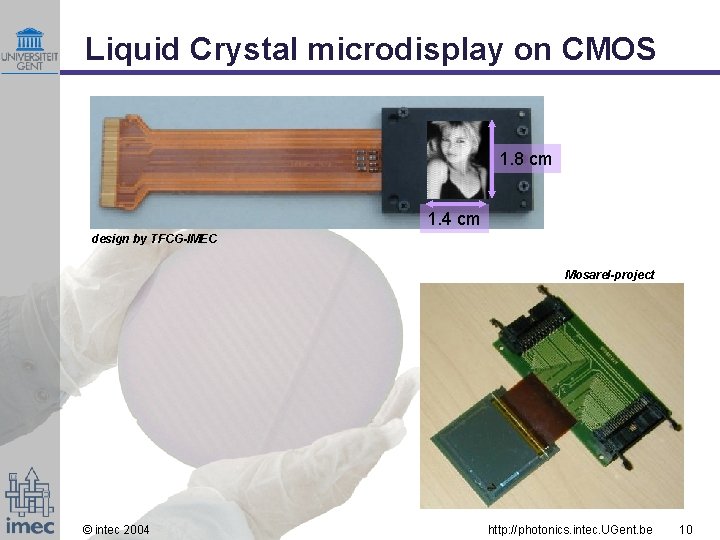

Liquid Crystal microdisplay on CMOS 1. 8 cm 1. 4 cm design by TFCG-IMEC Mosarel-project © intec 2004 http: //photonics. intec. UGent. be 10

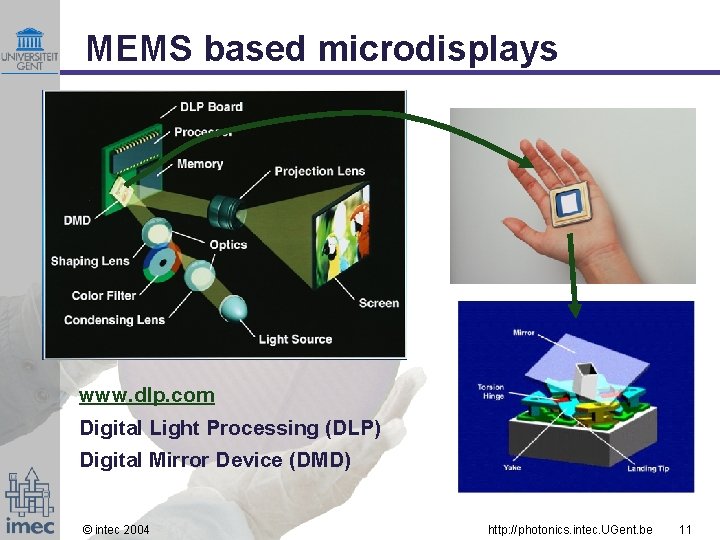

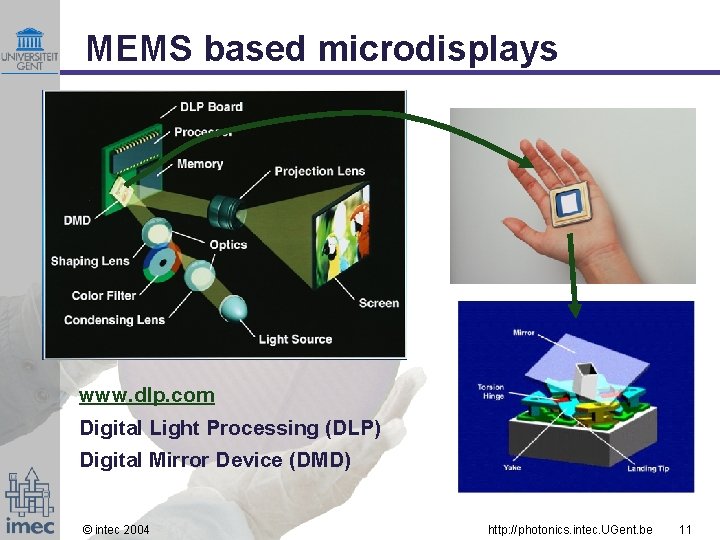

MEMS based microdisplays Display www. dlp. com Digital Light Processing (DLP) Digital Mirror Device (DMD) © intec 2004 http: //photonics. intec. UGent. be 11

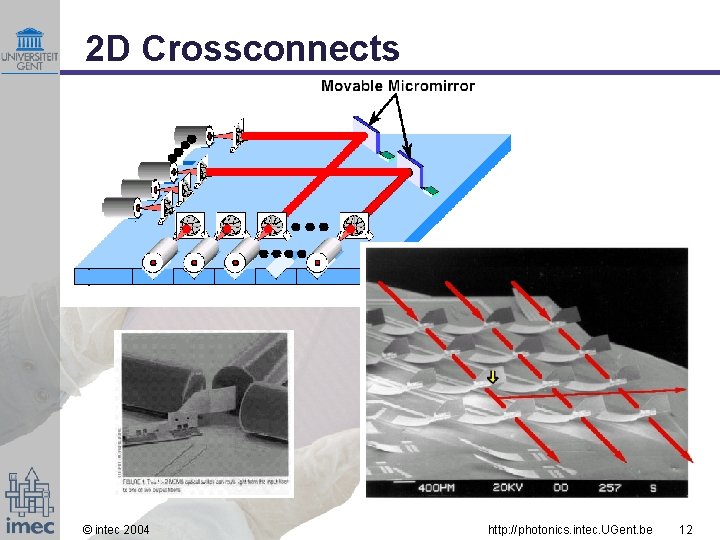

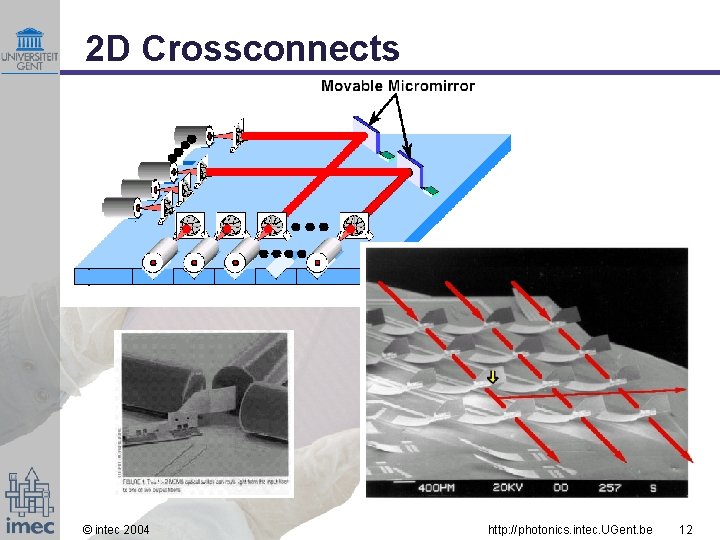

2 D Crossconnects © intec 2004 http: //photonics. intec. UGent. be 12

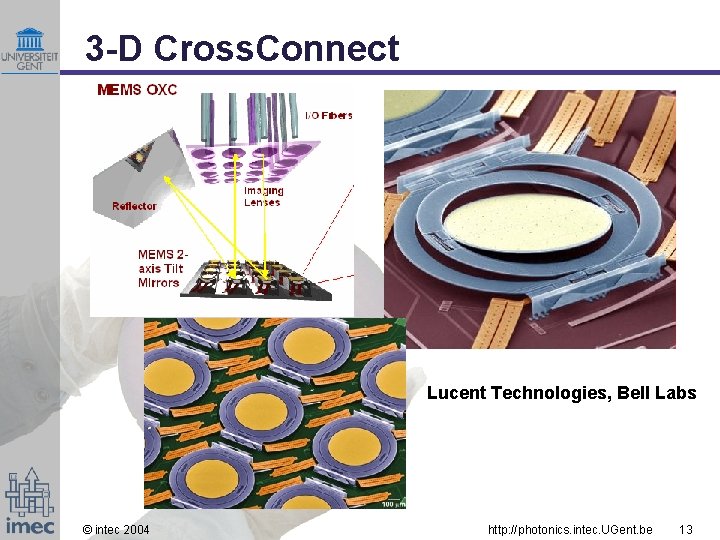

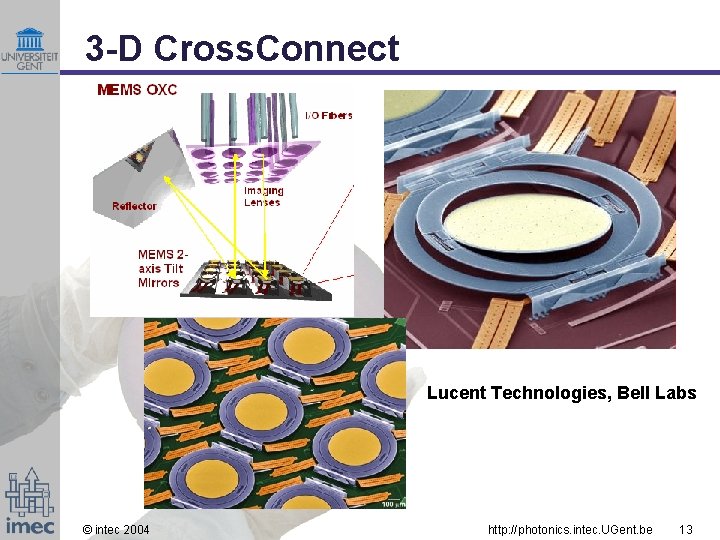

3 -D Cross. Connect Lucent Technologies, Bell Labs © intec 2004 http: //photonics. intec. UGent. be 13

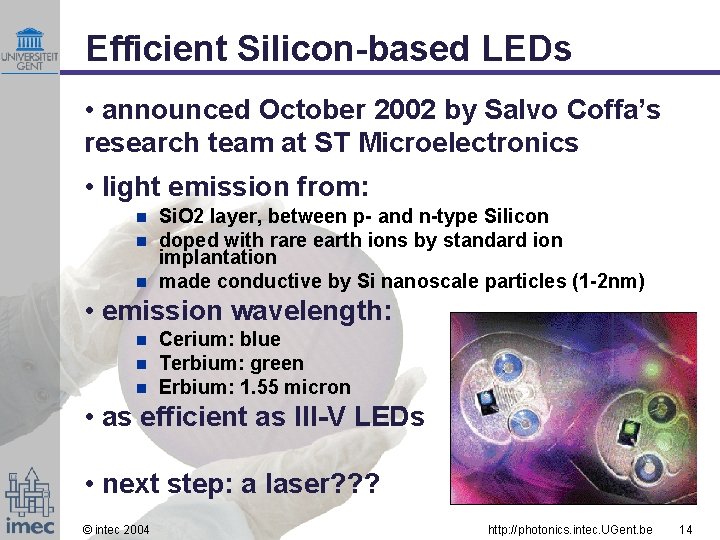

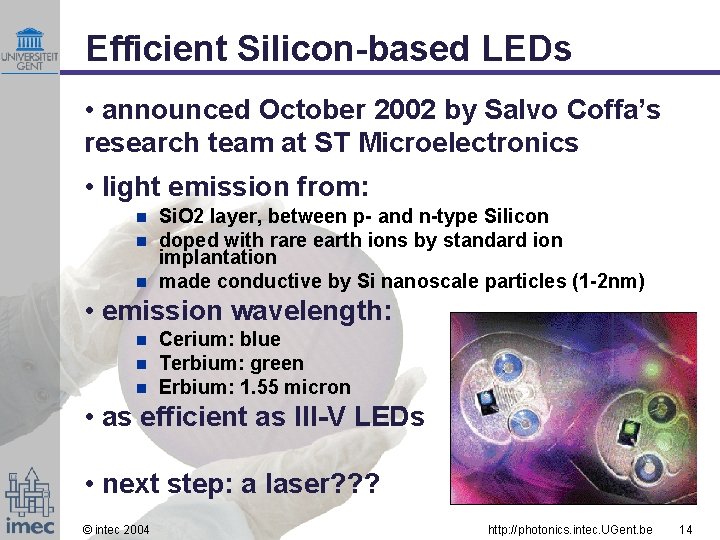

Efficient Silicon-based LEDs • announced October 2002 by Salvo Coffa’s research team at ST Microelectronics • light emission from: Si. O 2 layer, between p- and n-type Silicon doped with rare earth ions by standard ion implantation n made conductive by Si nanoscale particles (1 -2 nm) n n • emission wavelength: n n n Cerium: blue Terbium: green Erbium: 1. 55 micron • as efficient as III-V LEDs • next step: a laser? ? ? © intec 2004 http: //photonics. intec. UGent. be 14

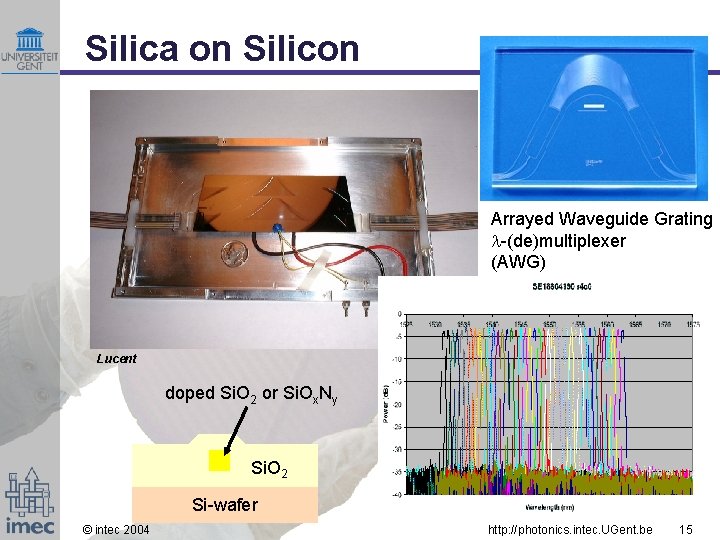

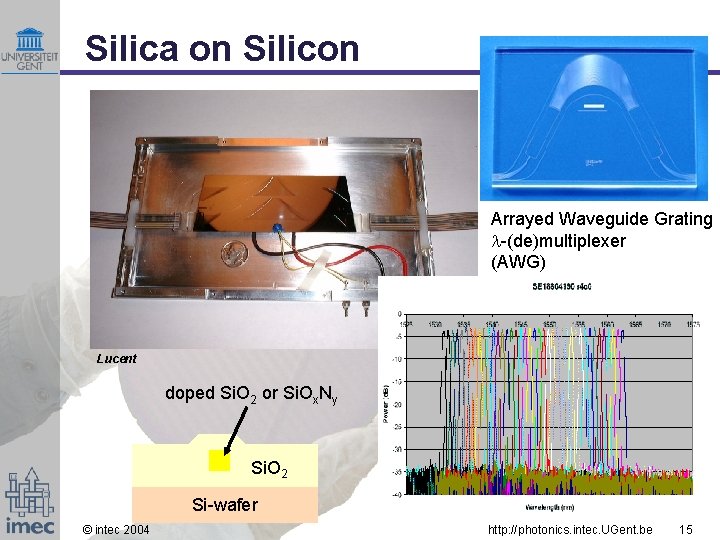

Silica on Silicon Arrayed Waveguide Grating -(de)multiplexer (AWG) Lucent doped Si. O 2 or Si. Ox. Ny Si. O 2 Si-wafer © intec 2004 http: //photonics. intec. UGent. be 15

“Group IV photonics” 1 st International Conference on Group IV Photonics Hongkong 29 September – 1 October 2004 Organized by IEEE-LEOS © intec 2004 http: //photonics. intec. UGent. be 16

Outline • why Silicon photonics? • sub-micron photonics in Silicon? • heterogeneous integration of III-V components onto Silicon? © intec 2004 http: //photonics. intec. UGent. be 17

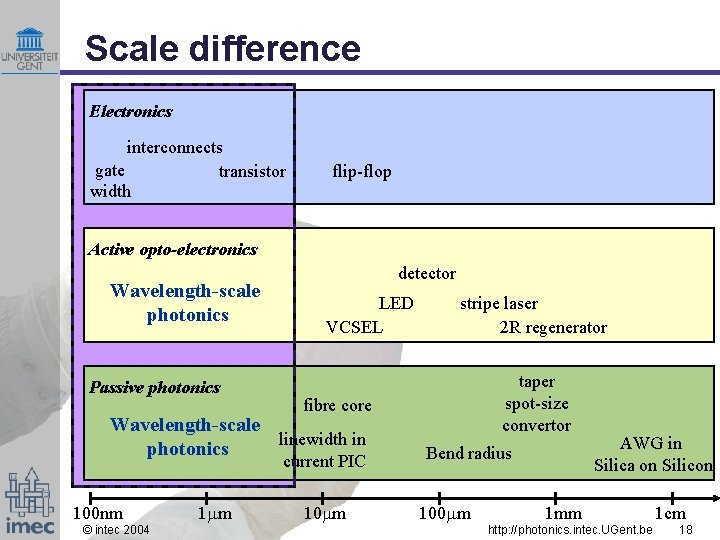

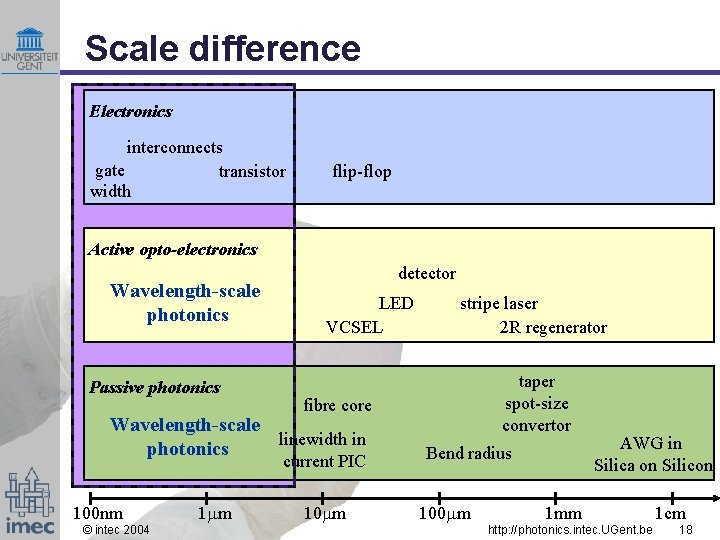

Scale difference Electronics interconnects gate transistor width flip-flop Active opto-electronics Wavelength-scale photonics Passive photonics detector LED VCSEL current PIC © intec 2004 1 m taper spot-size convertor fibre core Wavelength-scale linewidth in photonics 100 nm stripe laser 2 R regenerator 10 m Bend radius 100 m 1 mm AWG in Silica on Silicon http: //photonics. intec. UGent. be 1 cm 18

Reduce PIC-size / increase density WE NEED: Ultra-compact waveguiding with l Sharp bends (Bend radius < 10 m) l Compact splitters and combiners l Short mode-conversion distances Compact wavelength selective functions l Highly dispersive element l Small, high-Q resonators Compact non-linear functions l Increase power density by using tight confinement © intec 2004 http: //photonics. intec. UGent. be 19

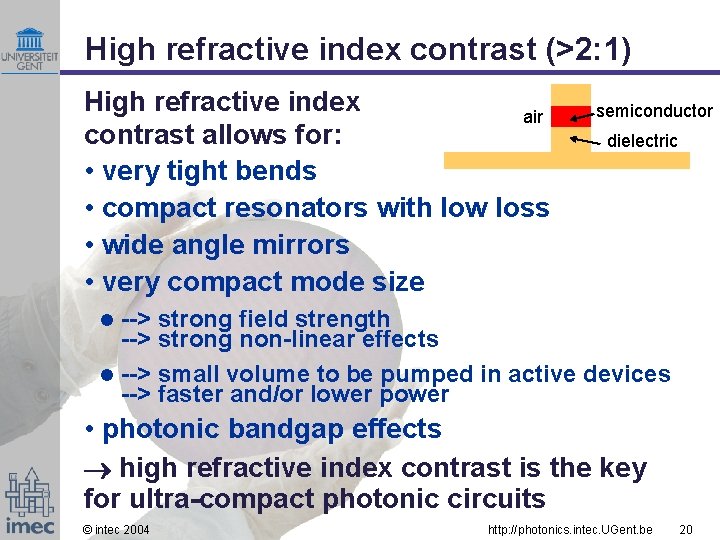

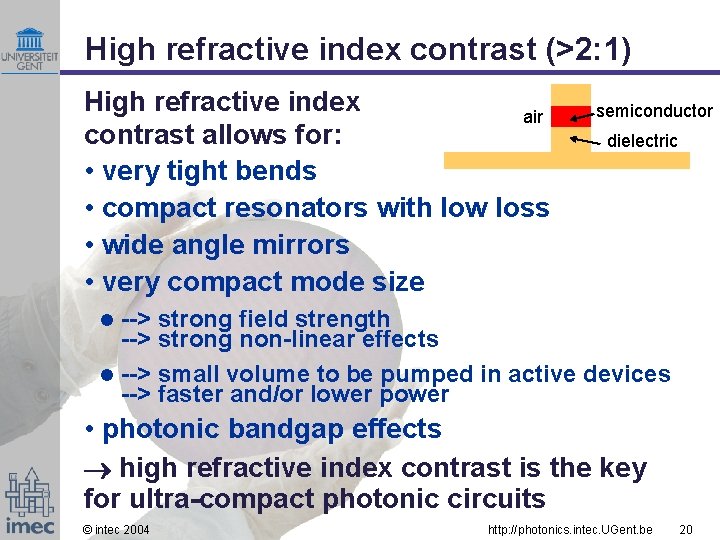

High refractive index contrast (>2: 1) High refractive index air contrast allows for: • very tight bends • compact resonators with low loss • wide angle mirrors • very compact mode size semiconductor dielectric --> strong field strength --> strong non-linear effects l --> small volume to be pumped in active devices --> faster and/or lower power l • photonic bandgap effects high refractive index contrast is the key for ultra-compact photonic circuits © intec 2004 http: //photonics. intec. UGent. be 20

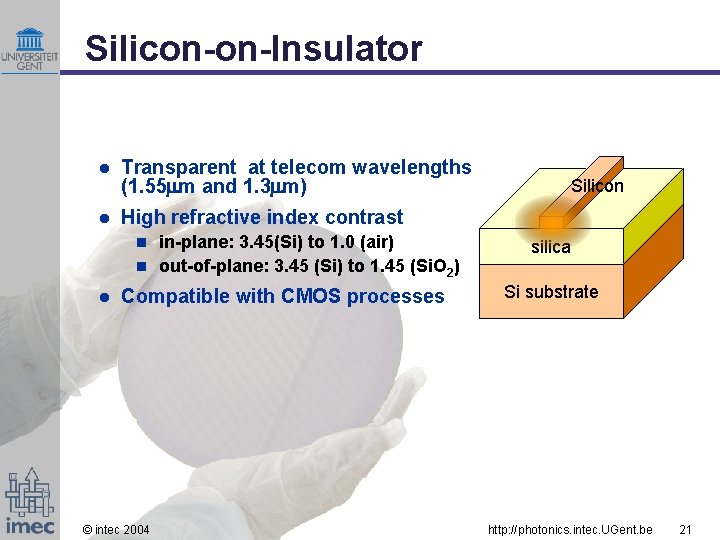

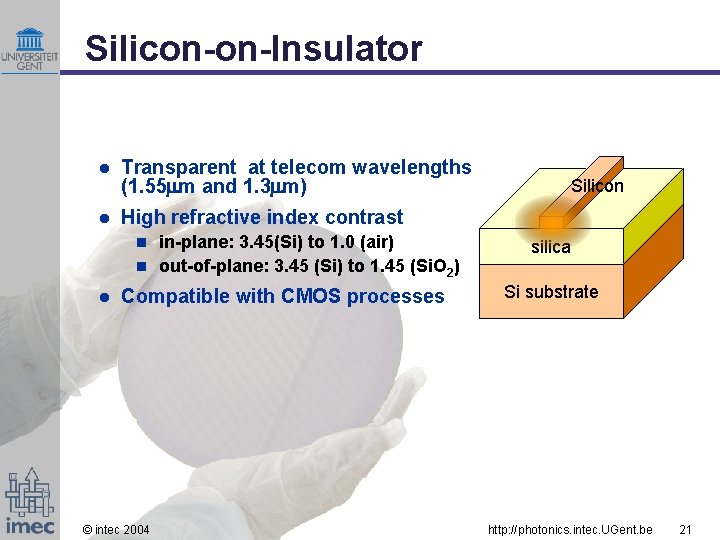

Silicon-on-Insulator l Transparent at telecom wavelengths (1. 55 m and 1. 3 m) l High refractive index contrast in-plane: 3. 45(Si) to 1. 0 (air) n out-of-plane: 3. 45 (Si) to 1. 45 (Si. O 2) n l Compatible with CMOS processes © intec 2004 Silicon silica Si substrate http: //photonics. intec. UGent. be 21

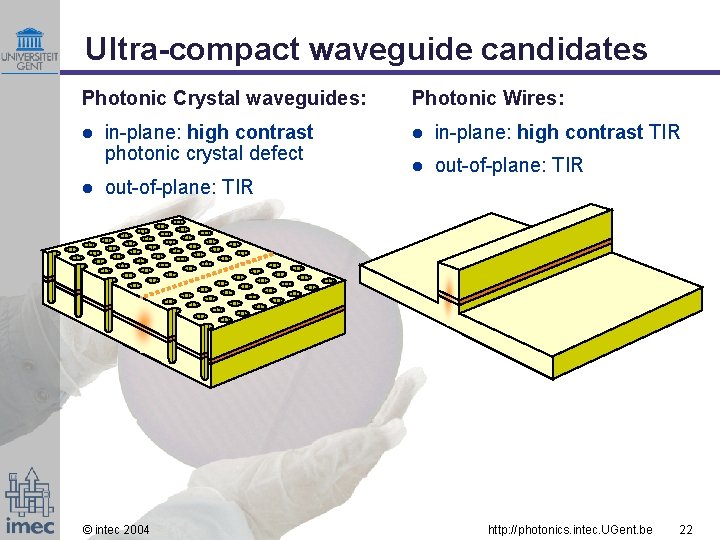

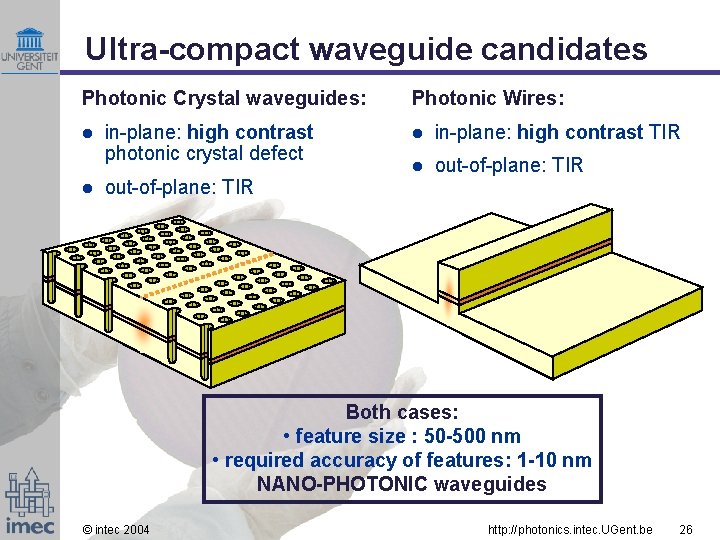

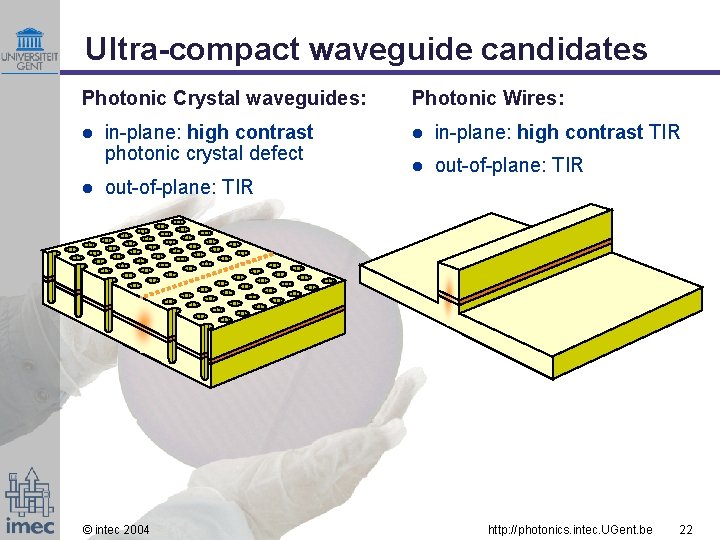

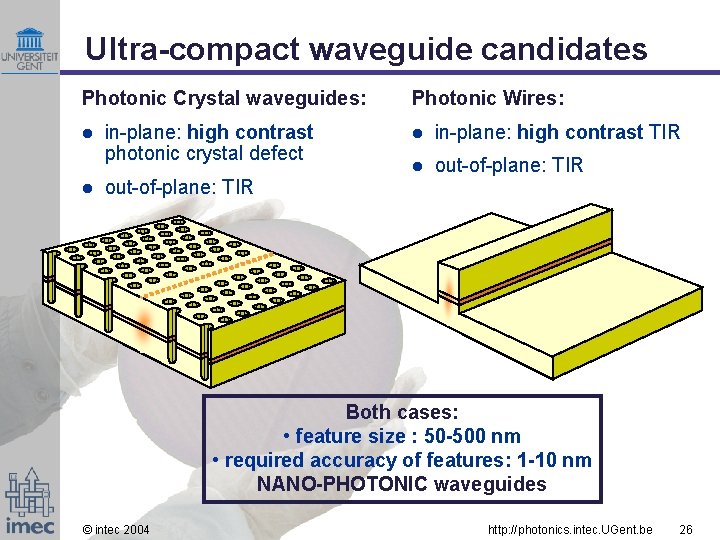

Ultra-compact waveguide candidates Photonic Crystal waveguides: l l in-plane: high contrast photonic crystal defect out-of-plane: TIR © intec 2004 Photonic Wires: l in-plane: high contrast TIR l out-of-plane: TIR http: //photonics. intec. UGent. be 22

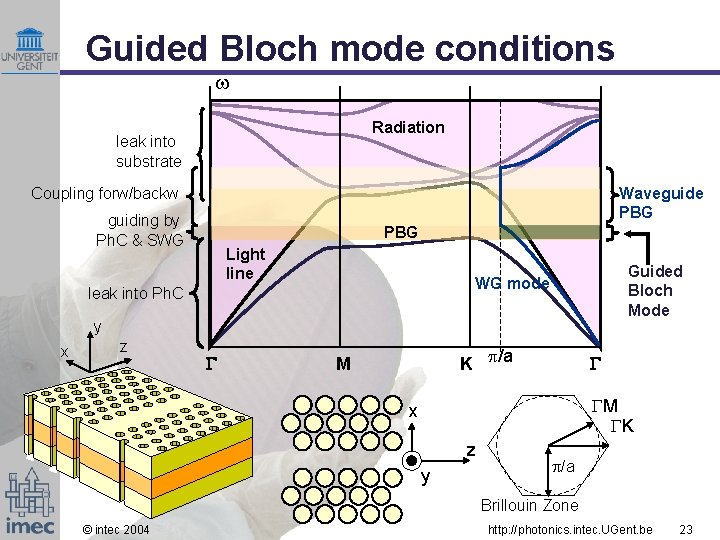

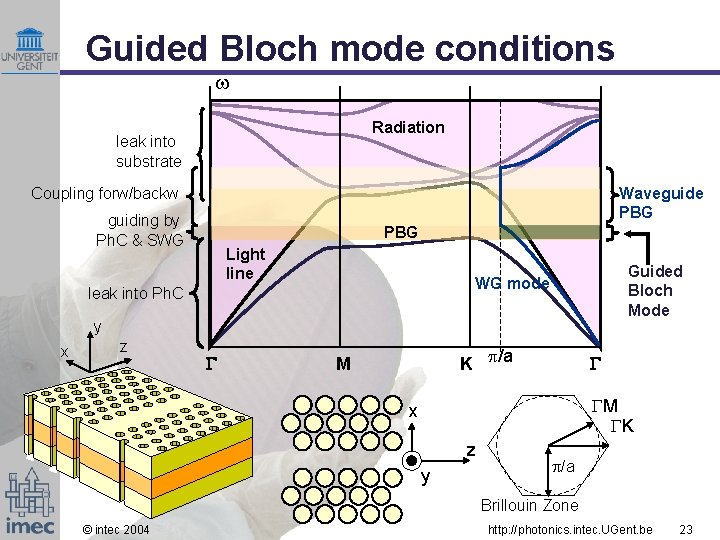

Guided Bloch mode conditions Radiation leak into substrate Coupling forw/backw Waveguide PBG guiding by Ph. C & SWG PBG Light line Guided Bloch Mode WG mode leak into Ph. C y x z K p/a M GM GK x z y p/a Brillouin Zone © intec 2004 http: //photonics. intec. UGent. be 23

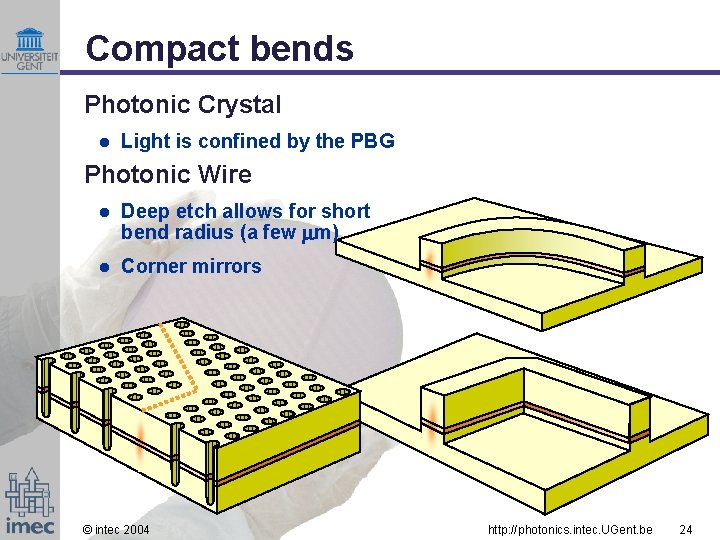

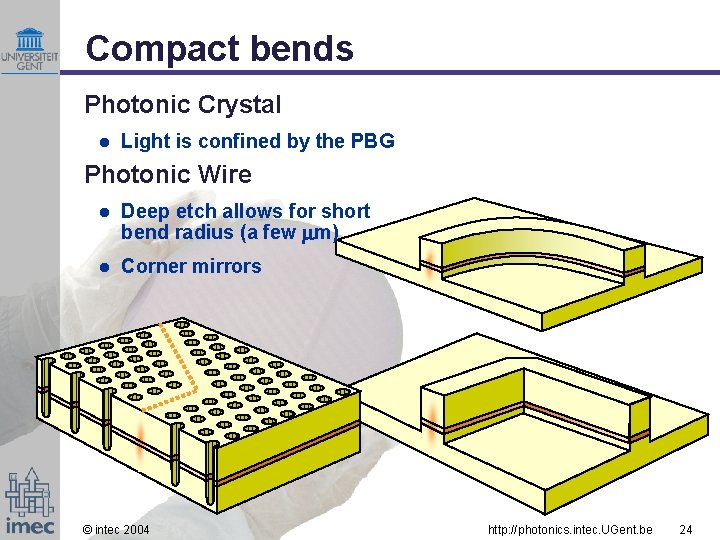

Compact bends Photonic Crystal l Light is confined by the PBG Photonic Wire l Deep etch allows for short bend radius (a few m) l Corner mirrors © intec 2004 http: //photonics. intec. UGent. be 24

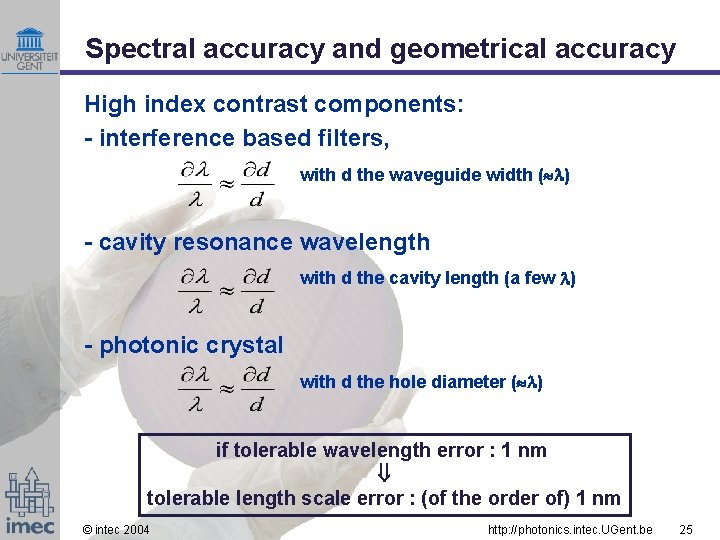

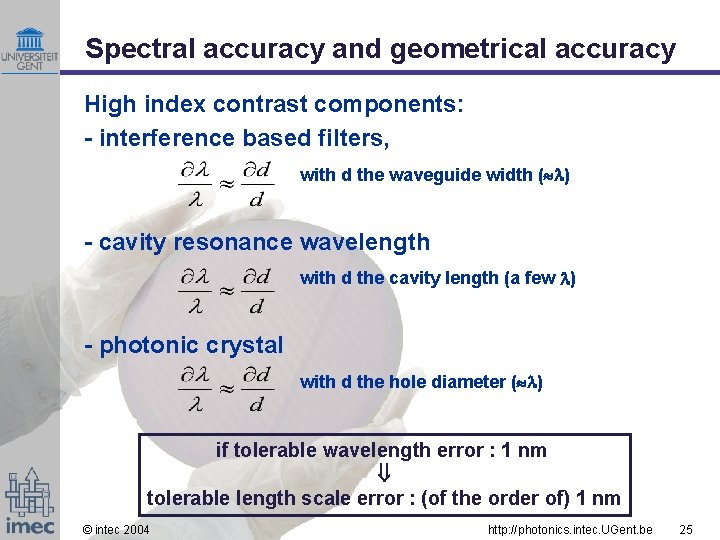

Spectral accuracy and geometrical accuracy High index contrast components: - interference based filters, with d the waveguide width ( ) - cavity resonance wavelength with d the cavity length (a few ) - photonic crystal with d the hole diameter ( ) if tolerable wavelength error : 1 nm tolerable length scale error : (of the order of) 1 nm © intec 2004 http: //photonics. intec. UGent. be 25

Ultra-compact waveguide candidates Photonic Crystal waveguides: l l in-plane: high contrast photonic crystal defect out-of-plane: TIR Photonic Wires: l in-plane: high contrast TIR l out-of-plane: TIR Both cases: • feature size : 50 -500 nm • required accuracy of features: 1 -10 nm NANO-PHOTONIC waveguides © intec 2004 http: //photonics. intec. UGent. be 26

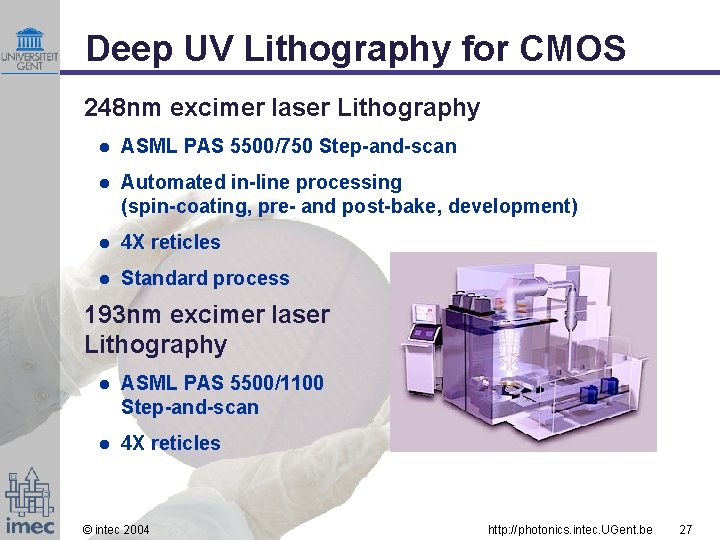

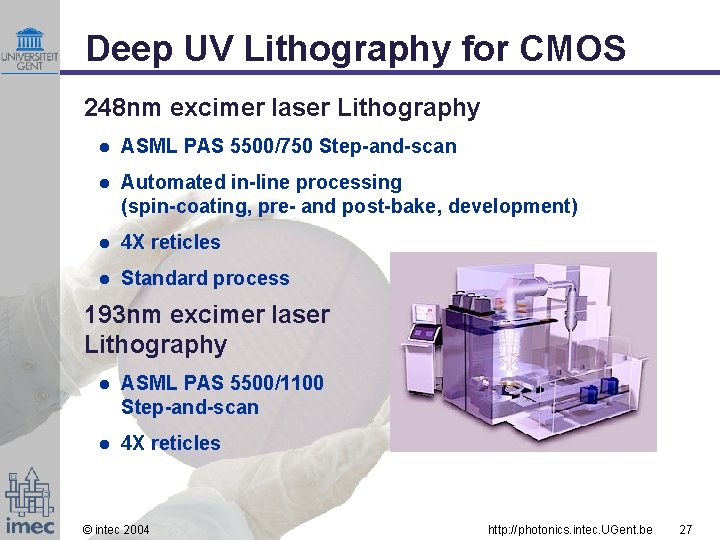

Deep UV Lithography for CMOS 248 nm excimer laser Lithography l ASML PAS 5500/750 Step-and-scan l Automated in-line processing (spin-coating, pre- and post-bake, development) l 4 X reticles l Standard process 193 nm excimer laser Lithography l ASML PAS 5500/1100 Step-and-scan l 4 X reticles © intec 2004 http: //photonics. intec. UGent. be 27

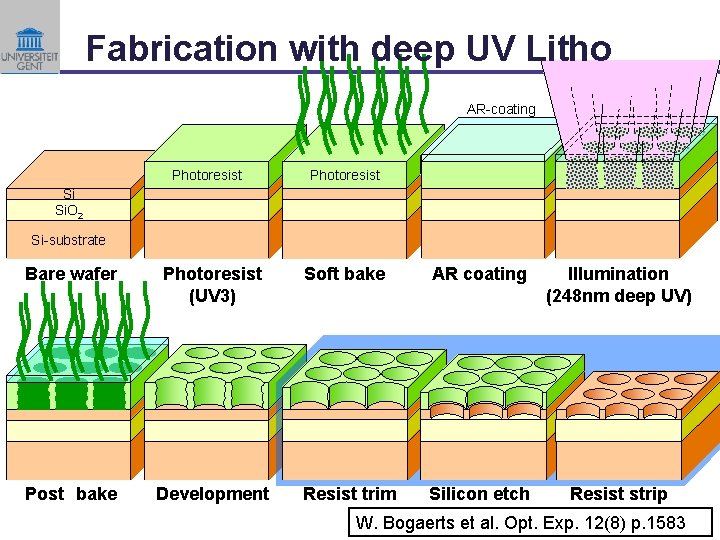

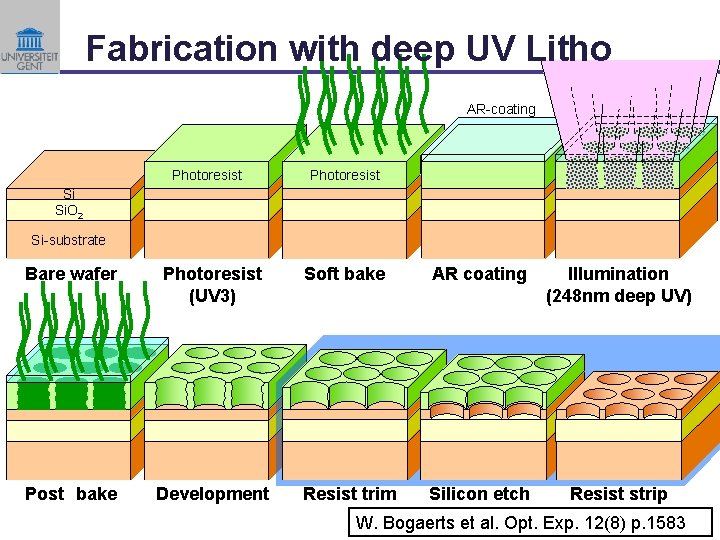

Fabrication with deep UV Litho AR-coating Photoresist Si Si. O 2 Si-substrate Bare wafer Photoresist (UV 3) Soft bake AR coating Illumination (248 nm deep UV) Post bake Development Resist trim Silicon etch Resist strip © intec 2004 W. Bogaerts et al. Opt. Exp. 12(8) p. 158328 http: //photonics. intec. UGent. be

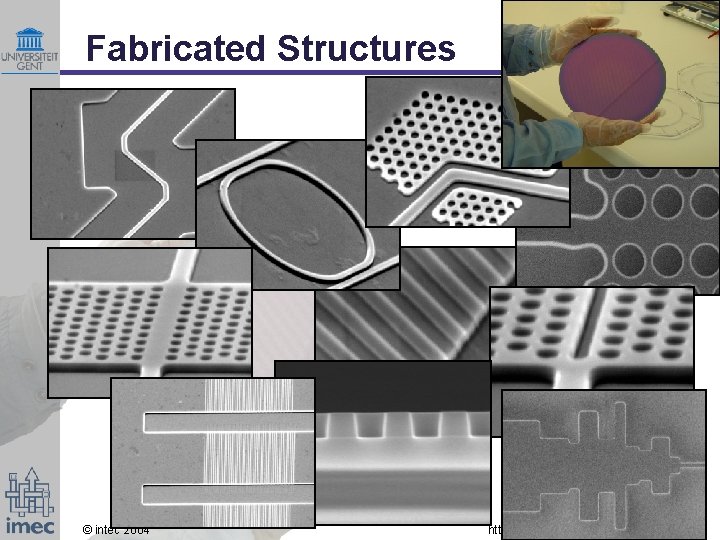

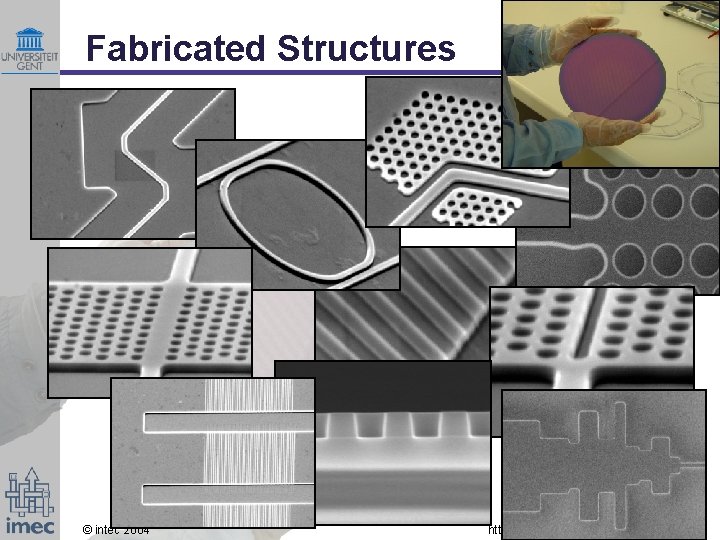

Fabricated Structures © intec 2004 http: //photonics. intec. UGent. be 29

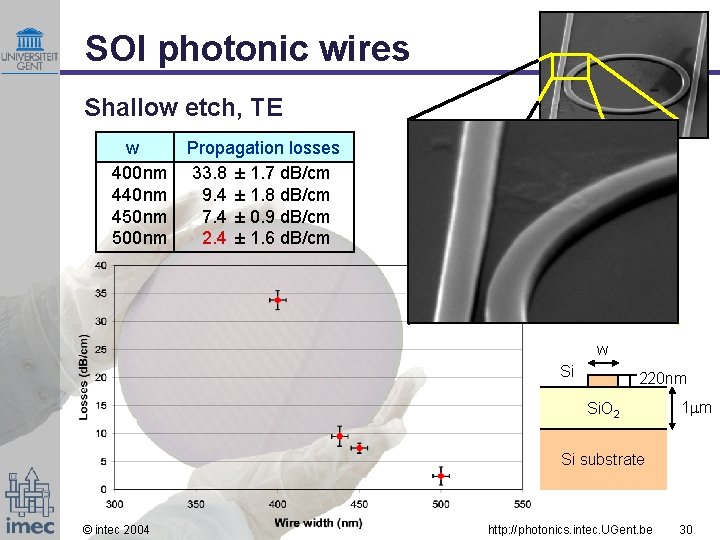

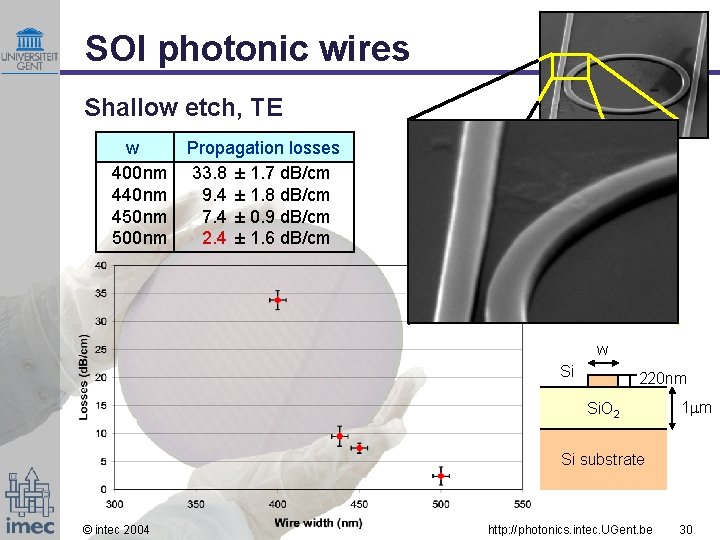

SOI photonic wires Shallow etch, TE w 400 nm 440 nm 450 nm 500 nm Propagation losses 33. 8 ± 1. 7 d. B/cm 9. 4 ± 1. 8 d. B/cm 7. 4 ± 0. 9 d. B/cm 2. 4 ± 1. 6 d. B/cm w Si 220 nm Si. O 2 1 m Si substrate © intec 2004 http: //photonics. intec. UGent. be 30

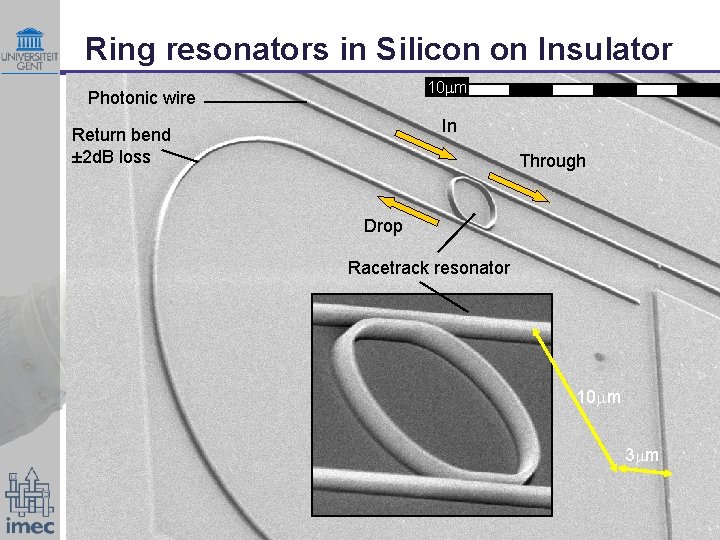

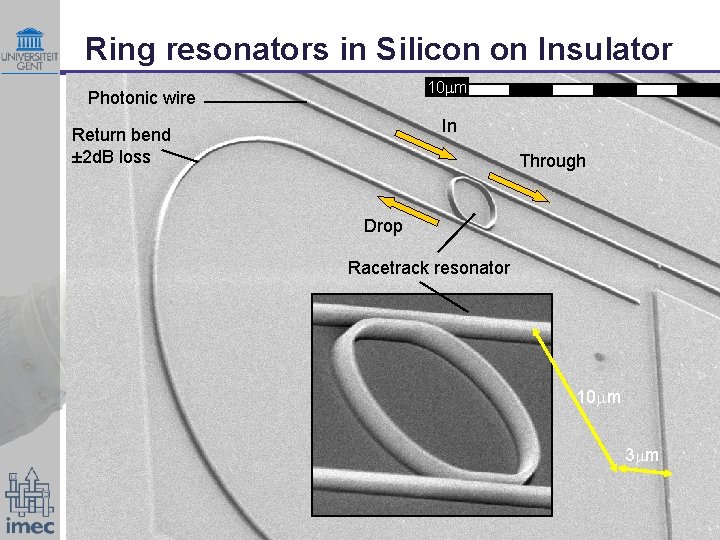

Ring resonators in Silicon on Insulator 10 m Photonic wire In Return bend ± 2 d. B loss Through Drop Racetrack resonator 10 m 3 m © intec 2004 http: //photonics. intec. UGent. be 31

![Racetrack Resonator l l l normalized transfer d B l 8 m Wire width Racetrack Resonator l l l normalized transfer [d. B] l 8 m Wire width](https://slidetodoc.com/presentation_image_h2/4fa59d7032c7321bfbecc201e2734d0d/image-32.jpg)

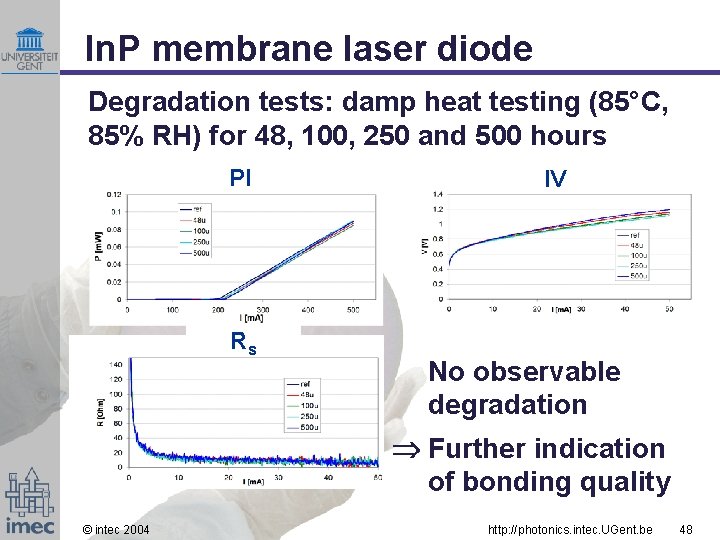

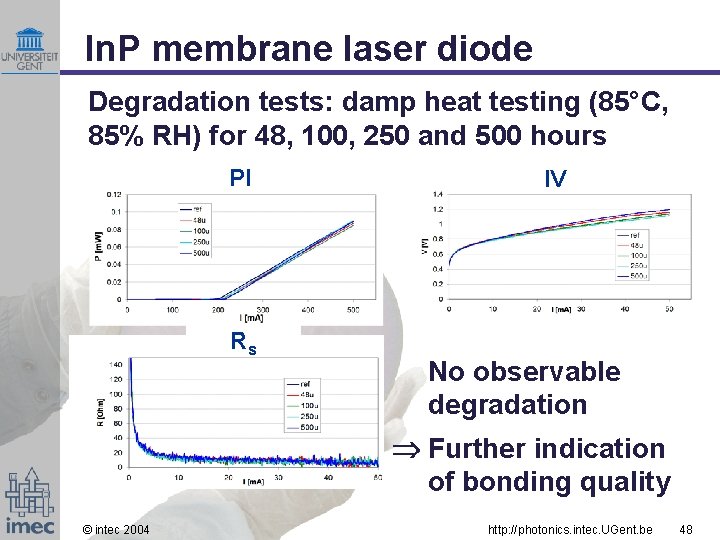

Racetrack Resonator l l l normalized transfer [d. B] l 8 m Wire width = 510 nm TE polarisation Q 12000 40% efficiency FSR=16. 5 nm Finesse=137 0 3. 14 m 4µm pass port -5 -10 -15 -20 -25 drop port -30 -35 PTL 16(5) pp. 1328 -1330 © intec 2004 1524. 5 1525 wavelength [nm] 1526 http: //photonics. intec. UGent. be 1526. 5 32

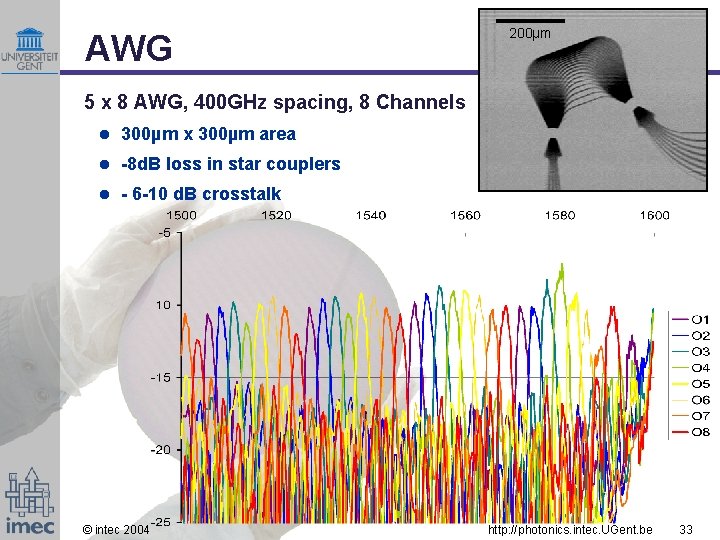

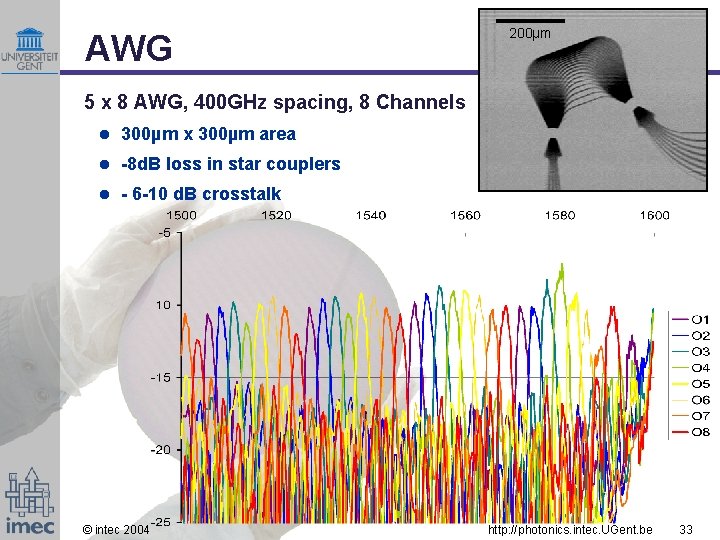

AWG 200µm 5 x 8 AWG, 400 GHz spacing, 8 Channels l 300µm x 300µm area l -8 d. B loss in star couplers l - 6 -10 d. B crosstalk © intec 2004 http: //photonics. intec. UGent. be 33

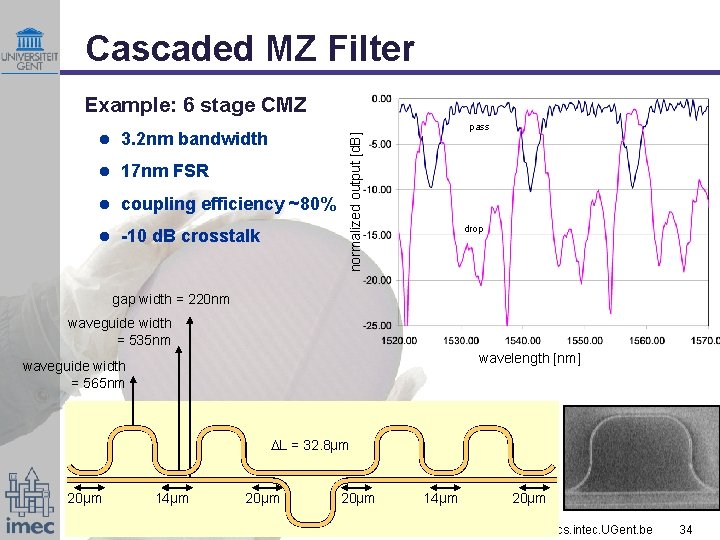

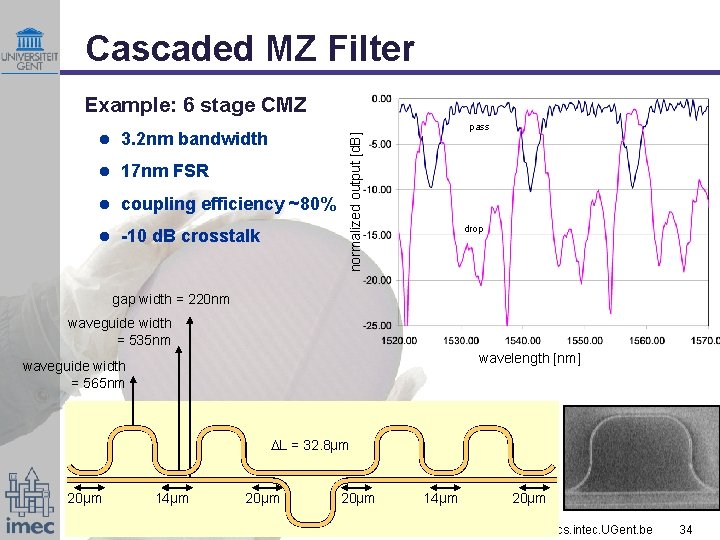

Cascaded MZ Filter Example: 6 stage CMZ l 3. 2 nm bandwidth l 17 nm FSR l coupling efficiency ~80% l -10 d. B crosstalk normalized output [d. B] pass drop gap width = 220 nm waveguide width = 535 nm wavelength [nm] waveguide width = 565 nm L = 32. 8µm 20µm © intec 2004 14µm 20µm http: //photonics. intec. UGent. be 34

Outline • why Silicon photonics? • sub-micron photonics in Silicon? • heterogeneous integration of III-V components onto Silicon? © intec 2004 http: //photonics. intec. UGent. be 35

Integration of active components • light emitters with high efficiency and high modulation bandwidth III-V semiconductors • compact optical amplifiers III-V semiconductors • high speed detectors (in particular in IR) III-V semiconductors • high speed + compact optical modulators and switches III-V semiconductors © intec 2004 http: //photonics. intec. UGent. be 36

Integration of active + passive photonics Integration of active photonics and electronics The options: • monolithic in III-V complex and costly • Silicon-based IC + hybridly mounted III-V components costly + yield problem © intec 2004 http: //photonics. intec. UGent. be 37

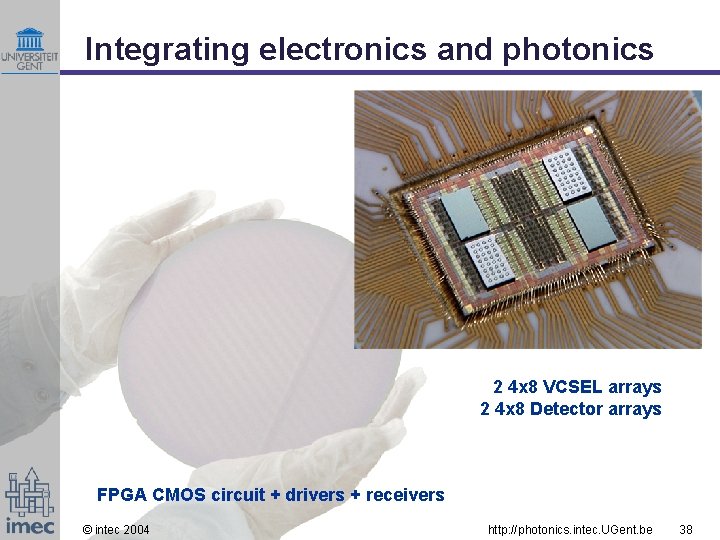

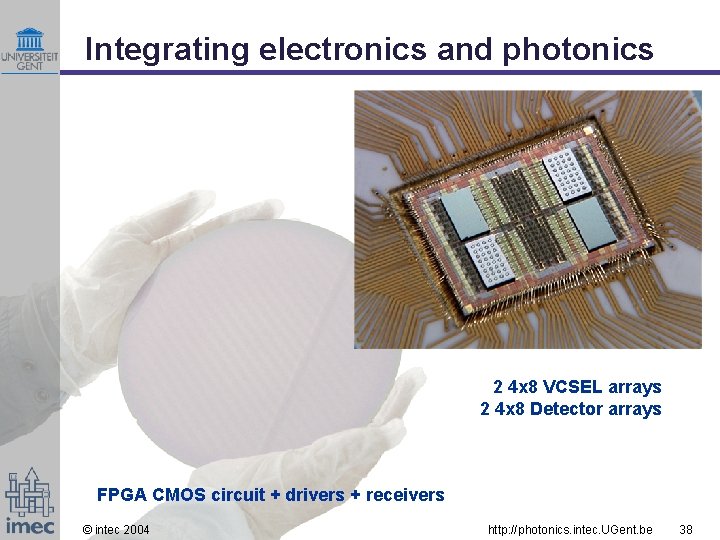

Integrating electronics and photonics 2 4 x 8 VCSEL arrays 2 4 x 8 Detector arrays FPGA CMOS circuit + drivers + receivers © intec 2004 http: //photonics. intec. UGent. be 38

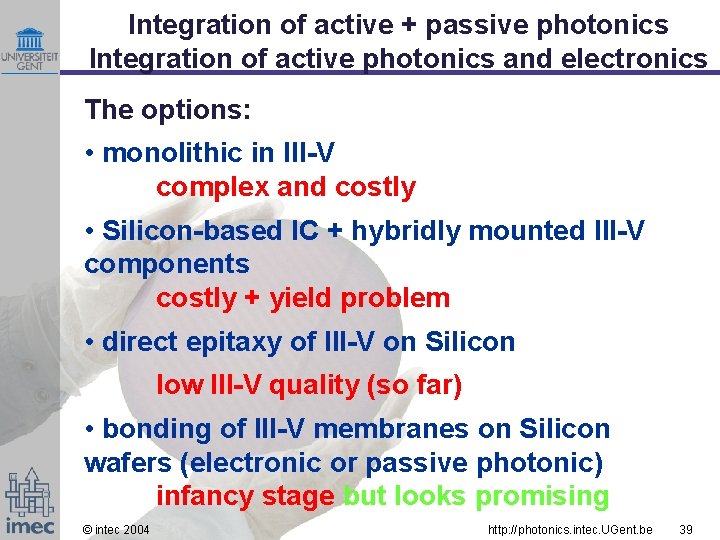

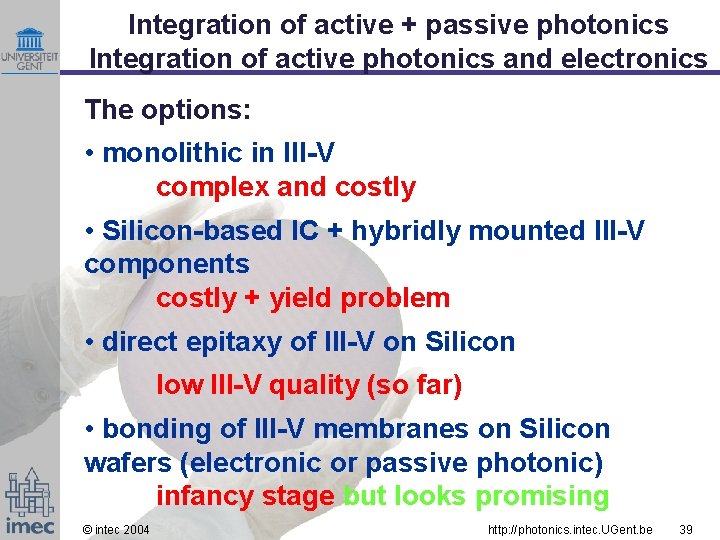

Integration of active + passive photonics Integration of active photonics and electronics The options: • monolithic in III-V complex and costly • Silicon-based IC + hybridly mounted III-V components costly + yield problem • direct epitaxy of III-V on Silicon low III-V quality (so far) • bonding of III-V membranes on Silicon wafers (electronic or passive photonic) infancy stage but looks promising © intec 2004 http: //photonics. intec. UGent. be 39

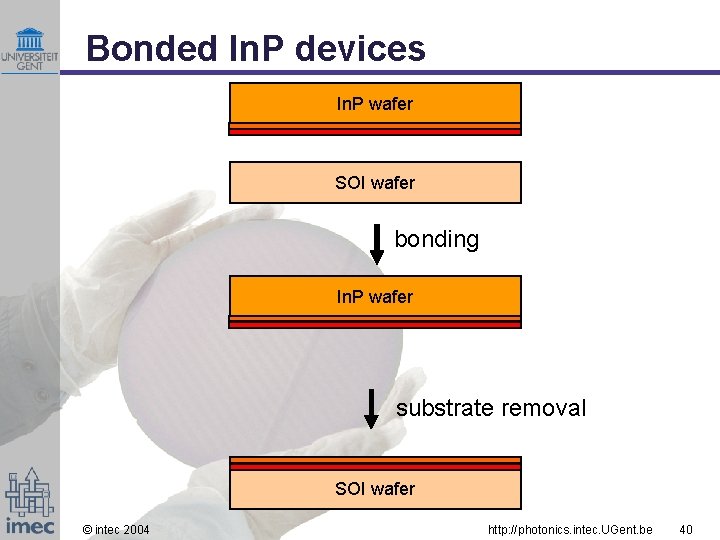

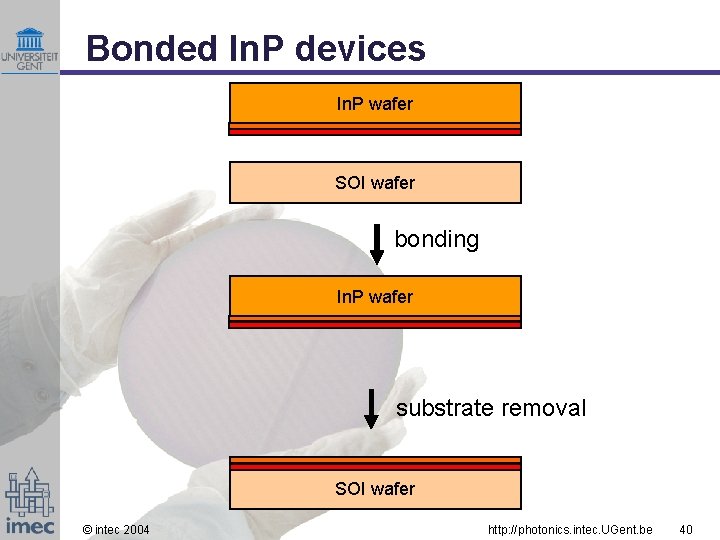

Bonded In. P devices In. P wafer SOI wafer bonding In. P wafer substrate removal SOI wafer © intec 2004 http: //photonics. intec. UGent. be 40

Bonding technologies • Direct bonding (e. g. wafer fusion) • Metallic bonding (e. g. with solder) • Bonding with intermediate ‘glue’ layer e. g. BCB, SOG • … © intec 2004 http: //photonics. intec. UGent. be 41

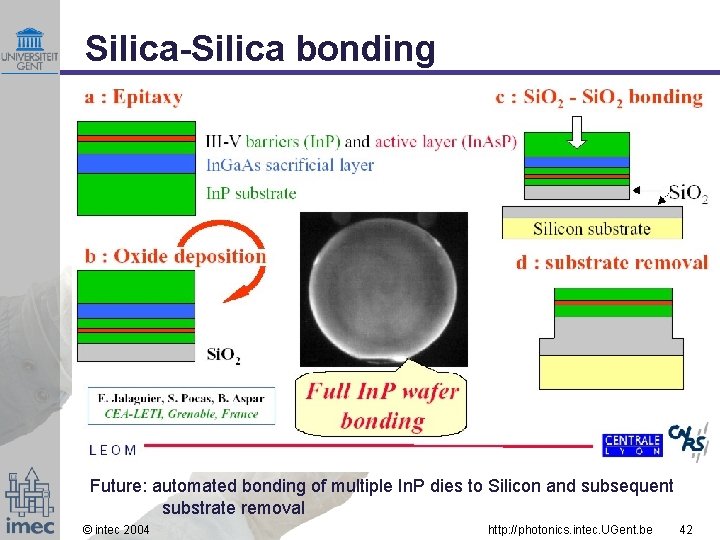

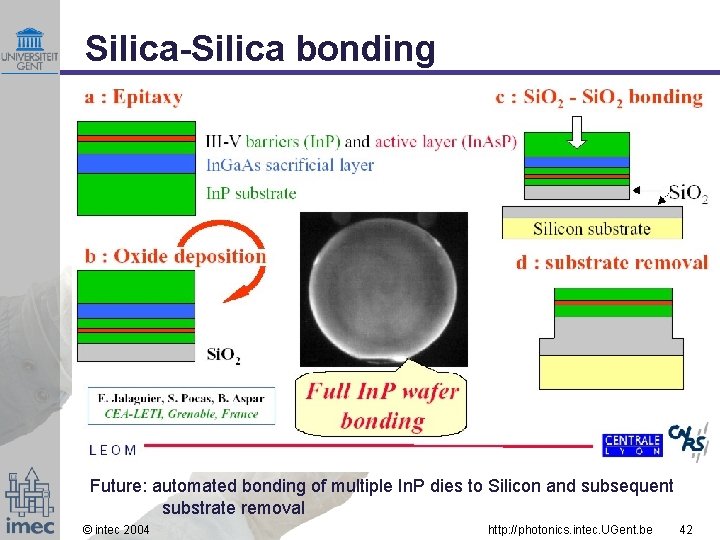

Silica-Silica bonding Future: automated bonding of multiple In. P dies to Silicon and subsequent substrate removal © intec 2004 http: //photonics. intec. UGent. be 42

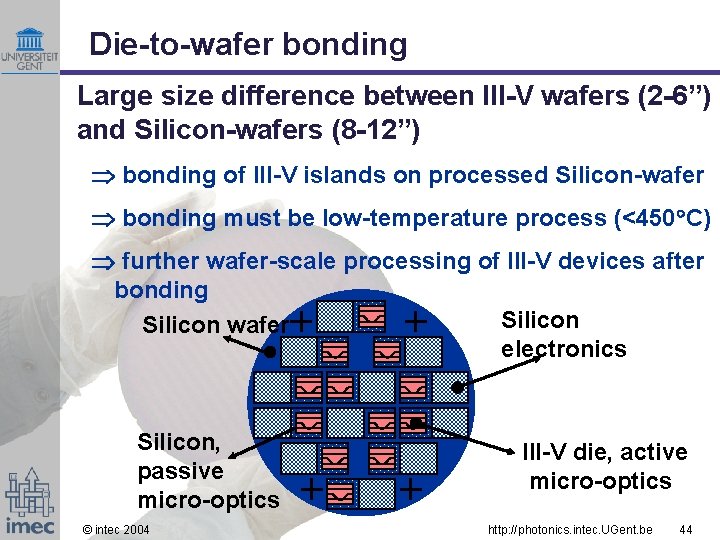

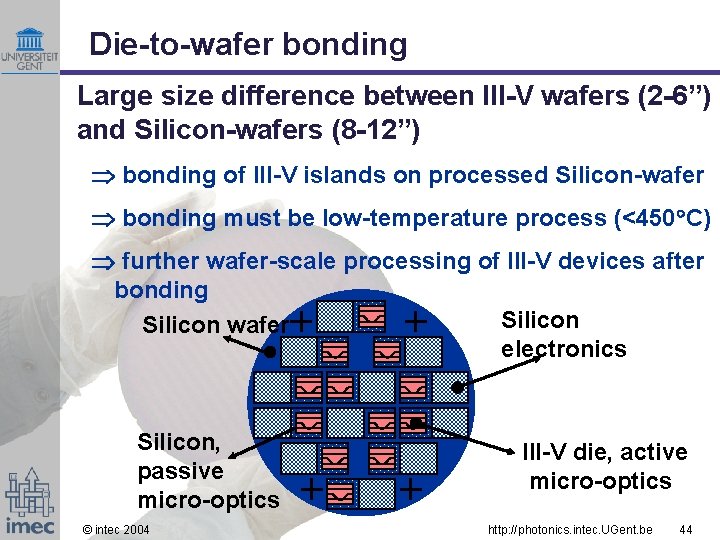

Die-to-wafer bonding Large size difference between III-V wafers (2 -6”) and Silicon-wafers (8 -12”) bonding of III-V islands on processed Silicon-wafer bonding must be low-temperature process (<450 C) further wafer-scale processing of III-V devices after bonding Silicon wafer electronics Silicon, passive micro-optics © intec 2004 III-V die, active micro-optics http: //photonics. intec. UGent. be 44

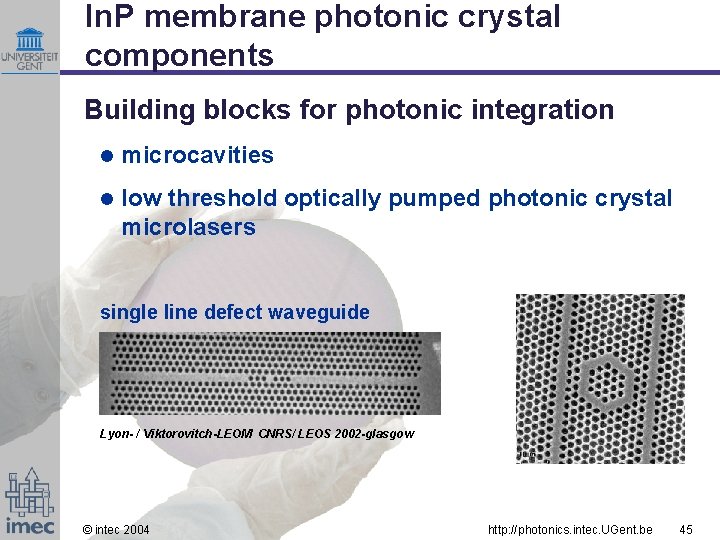

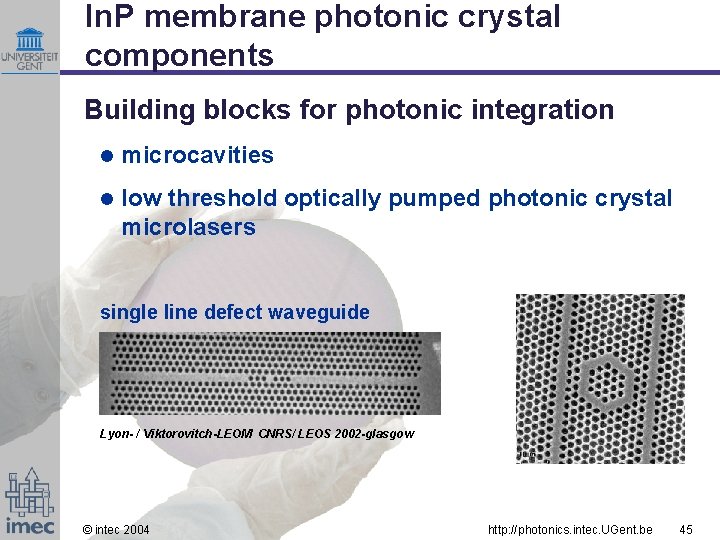

In. P membrane photonic crystal components Building blocks for photonic integration l microcavities l low threshold optically pumped photonic crystal microlasers single line defect waveguide Lyon- / Viktorovitch-LEOM CNRS/ LEOS 2002 -glasgow © intec 2004 http: //photonics. intec. UGent. be 45

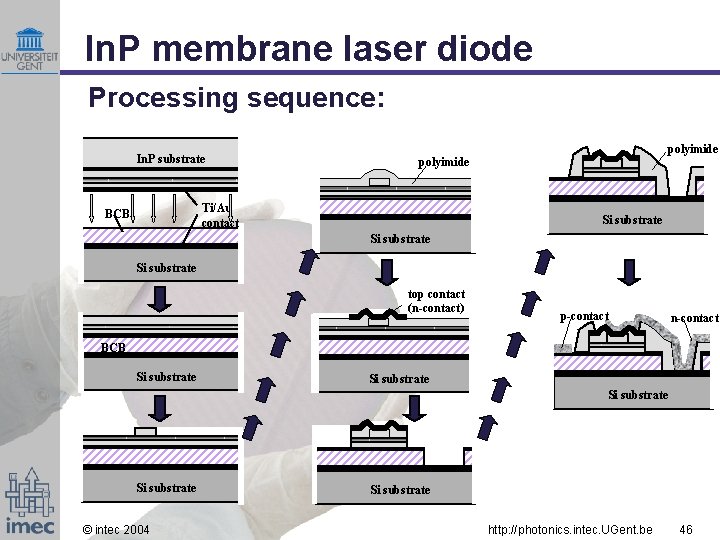

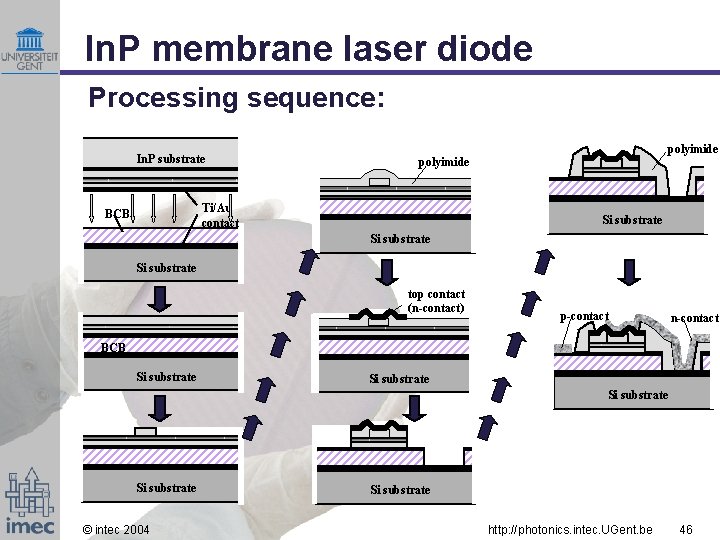

In. P membrane laser diode Processing sequence: In. P substrate Ti/Au contact BCB polyimide Si substrate top contact (n-contact) p-contact n-contact BCB Si substrate © intec 2004 Si substrate http: //photonics. intec. UGent. be 46

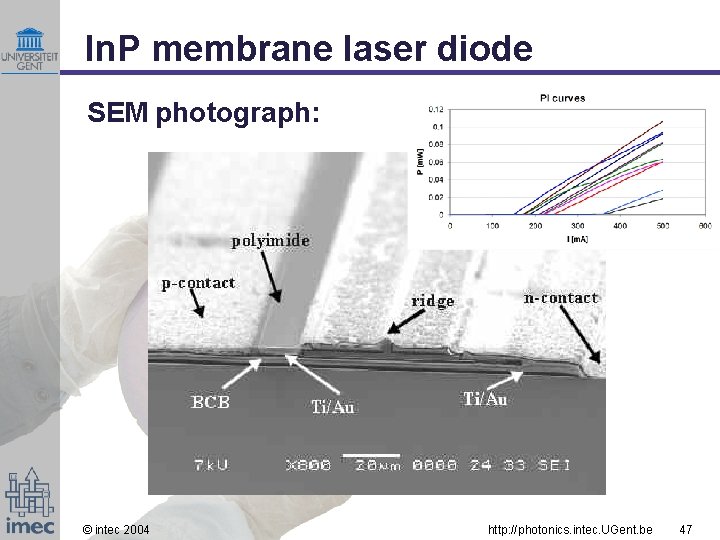

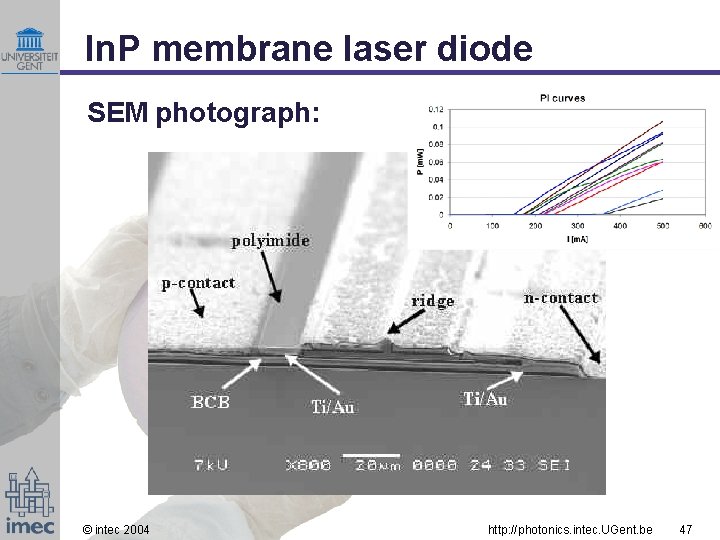

In. P membrane laser diode SEM photograph: © intec 2004 http: //photonics. intec. UGent. be 47

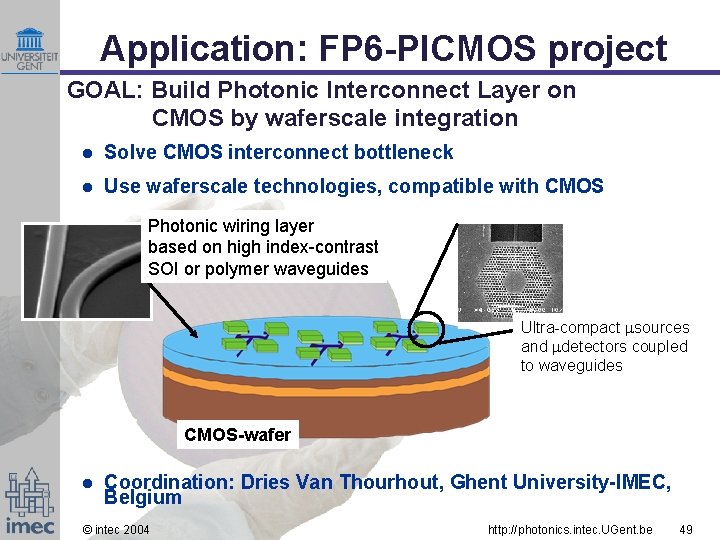

In. P membrane laser diode Degradation tests: damp heat testing (85°C, 85% RH) for 48, 100, 250 and 500 hours PI Rs IV No observable degradation Further indication of bonding quality © intec 2004 http: //photonics. intec. UGent. be 48

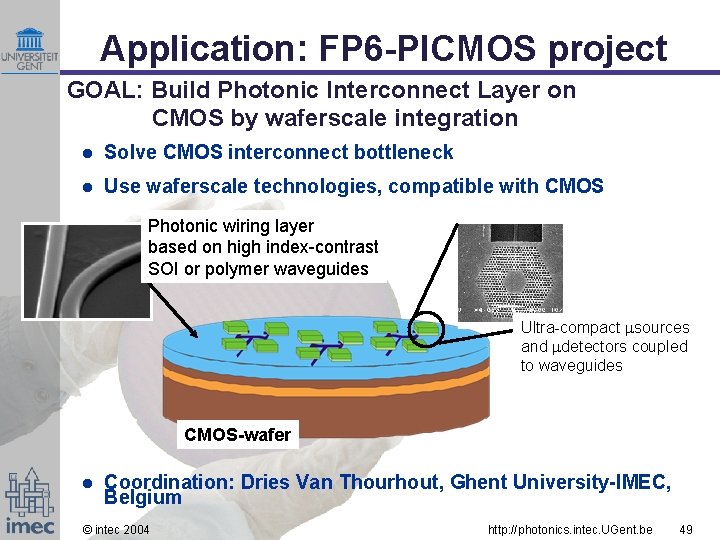

Application: FP 6 -PICMOS project GOAL: Build Photonic Interconnect Layer on CMOS by waferscale integration l Solve CMOS interconnect bottleneck l Use waferscale technologies, compatible with CMOS Photonic wiring layer based on high index-contrast SOI or polymer waveguides Ultra-compact sources and detectors coupled to waveguides CMOS-wafer l Coordination: Dries Van Thourhout, Ghent University-IMEC, Belgium © intec 2004 http: //photonics. intec. UGent. be 49

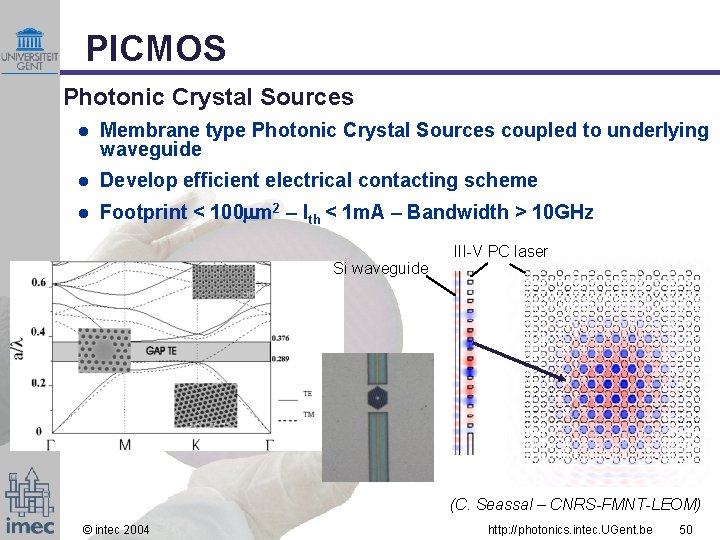

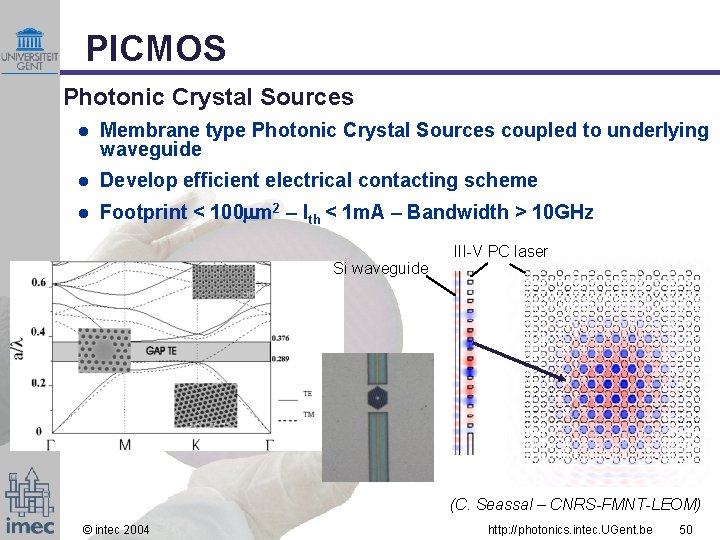

PICMOS Photonic Crystal Sources l Membrane type Photonic Crystal Sources coupled to underlying waveguide l Develop efficient electrical contacting scheme l Footprint < 100 m 2 – Ith < 1 m. A – Bandwidth > 10 GHz Si waveguide III-V PC laser (C. Seassal – CNRS-FMNT-LEOM) © intec 2004 http: //photonics. intec. UGent. be 50

Conclusions Silicon-based photonics l The power of Silicon technology brought to the world of photonics Silicon-based nanophotonics l Ultra-compact passive photonic ICs made by means of CMOS-technology Active photonic components in III-V membranes bonded to Silicon l Wafer-scale approach to the integration of n n n © intec 2004 Electronics Passive (nano)photonics Active (nano)photonics http: //photonics. intec. UGent. be 51