Integrated electronic for Si PM KOBE 29 June

Integrated electronic for Si. PM KOBE – 29 June ‘ 07 M. Bouchel, F. Dulucq, J. Fleury, C. de La Taille, G. Martin-Chassard, N. Seguin, L. Raux, S. Blin, P. Barrillon, S. Callier LAL Orsay IN 2 P 3 -CNRS – Université Paris-Sud – B. P. 34 91898 Orsay cedex – France

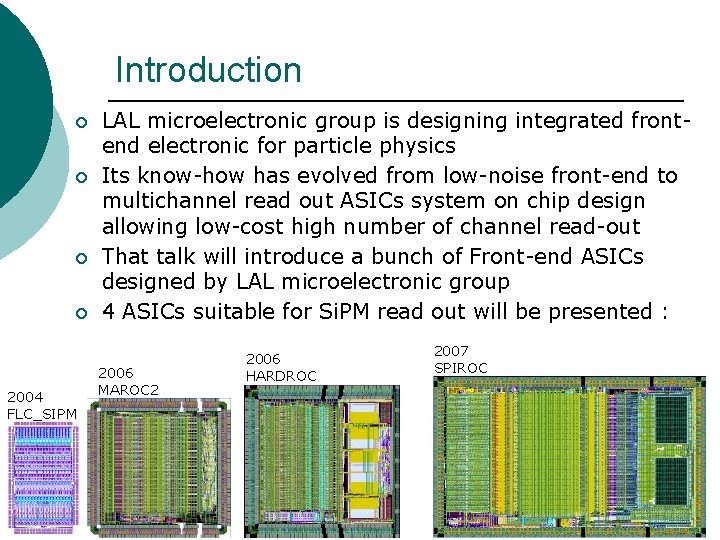

Introduction ¡ ¡ 2004 FLC_SIPM LAL microelectronic group is designing integrated frontend electronic for particle physics Its know-how has evolved from low-noise front-end to multichannel read out ASICs system on chip design allowing low-cost high number of channel read-out That talk will introduce a bunch of Front-end ASICs designed by LAL microelectronic group 4 ASICs suitable for Si. PM read out will be presented : 2006 MAROC 2 2006 HARDROC 2007 SPIROC

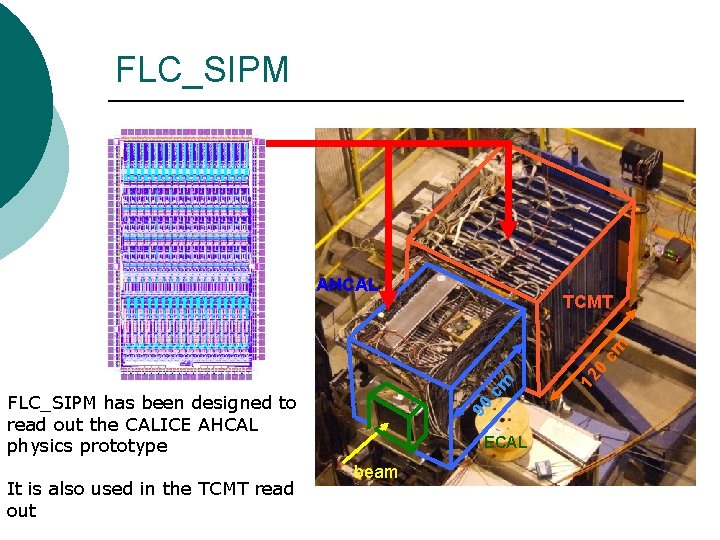

FLC_SIPM AHCAL It is also used in the TCMT read out 90 FLC_SIPM has been designed to read out the CALICE AHCAL physics prototype ECAL beam 12 0 cm cm TCMT

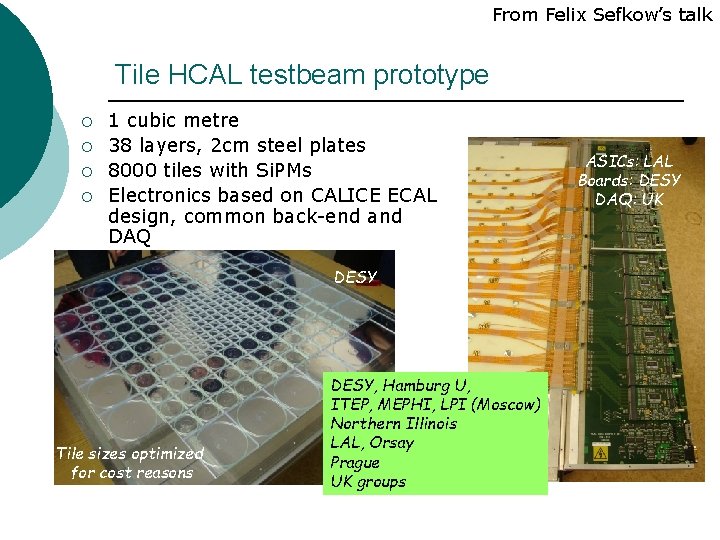

From Felix Sefkow’s talk Tile HCAL testbeam prototype ¡ ¡ 1 cubic metre 38 layers, 2 cm steel plates 8000 tiles with Si. PMs Electronics based on CALICE ECAL design, common back-end and DAQ DESY Tile sizes optimized for cost reasons DESY, Hamburg U, ITEP, MEPHI, LPI (Moscow) Northern Illinois LAL, Orsay Prague UK groups ASICs: LAL Boards: DESY DAQ: UK

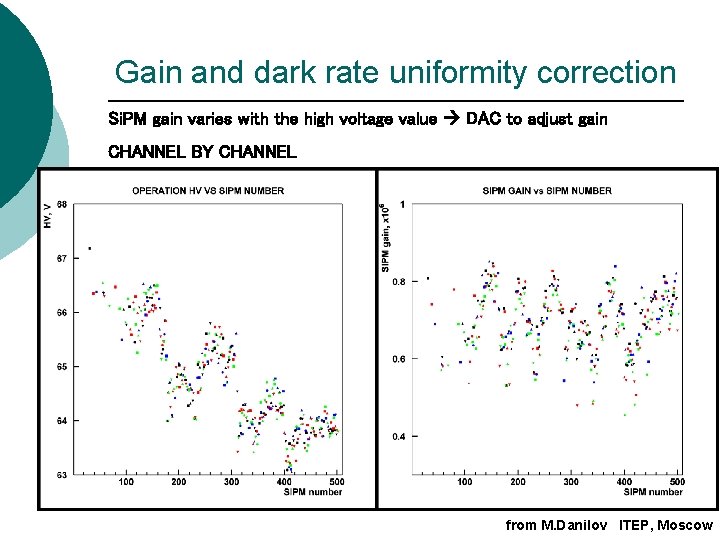

Gain and dark rate uniformity correction Si. PM gain varies with the high voltage value DAC to adjust gain CHANNEL BY CHANNEL from M. Danilov ITEP, Moscow

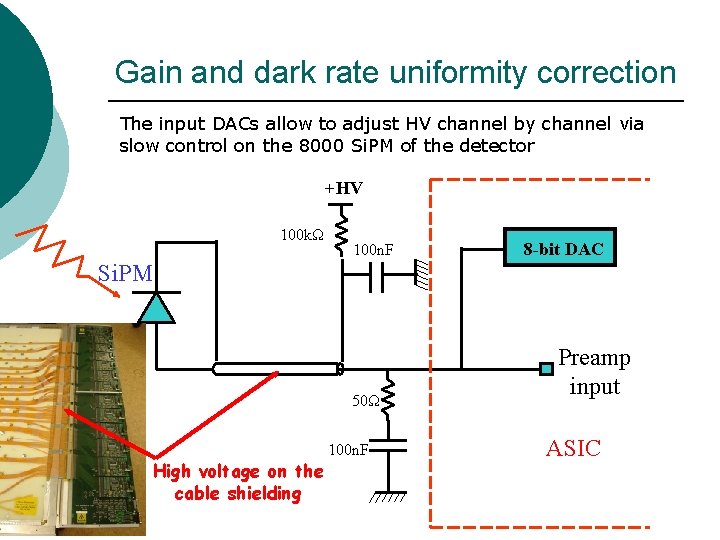

Gain and dark rate uniformity correction The input DACs allow to adjust HV channel by channel via slow control on the 8000 Si. PM of the detector +HV 100 kΩ 100 n. F 8 -bit DAC Si. PM 50Ω High voltage on the cable shielding 100 n. F Preamp input ASIC

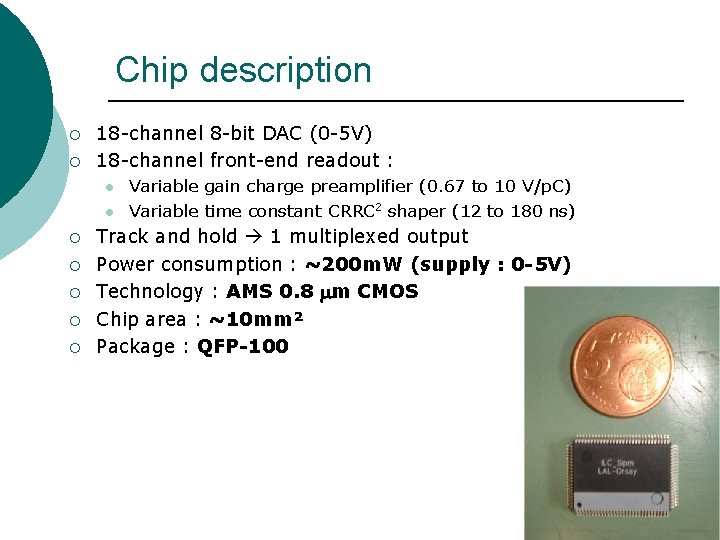

Chip description ¡ ¡ 18 -channel 8 -bit DAC (0 -5 V) 18 -channel front-end readout : l l ¡ ¡ ¡ Variable gain charge preamplifier (0. 67 to 10 V/p. C) Variable time constant CRRC 2 shaper (12 to 180 ns) Track and hold 1 multiplexed output Power consumption : ~200 m. W (supply : 0 -5 V) Technology : AMS 0. 8 m CMOS Chip area : ~10 mm² Package : QFP-100

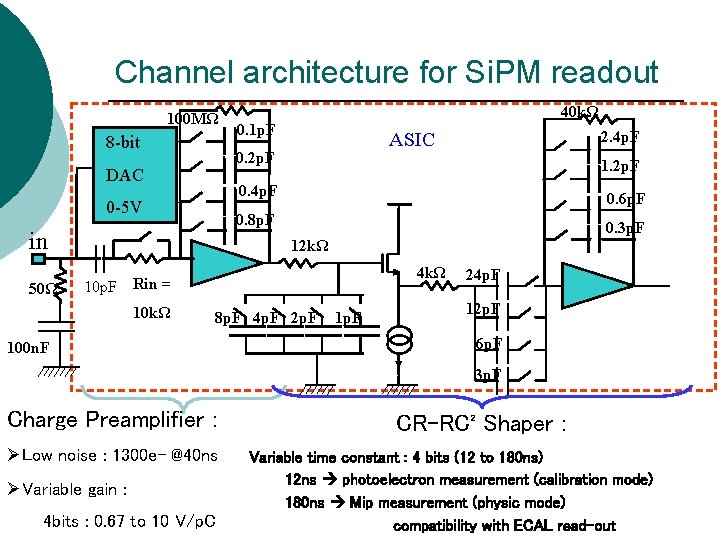

Channel architecture for Si. PM readout 100 MΩ 8 -bit 0. 1 p. F ASIC 0. 2 p. F DAC 2. 4 p. F 1. 2 p. F 0. 4 p. F 0 -5 V 0. 6 p. F 0. 8 p. F in 50Ω 40 kΩ 0. 3 p. F 12 kΩ 4 kΩ 10 p. F Rin = 10 kΩ 8 p. F 4 p. F 2 p. F 100 n. F 1 p. F 24 p. F 12 p. F 6 p. F 3 p. F Charge Preamplifier : ØLow noise : 1300 e- @40 ns ØVariable gain : 4 bits : 0. 67 to 10 V/p. C CR-RC² Shaper : Variable time constant : 4 bits (12 to 180 ns) 12 ns photoelectron measurement (calibration mode) 180 ns Mip measurement (physic mode) compatibility with ECAL read-out

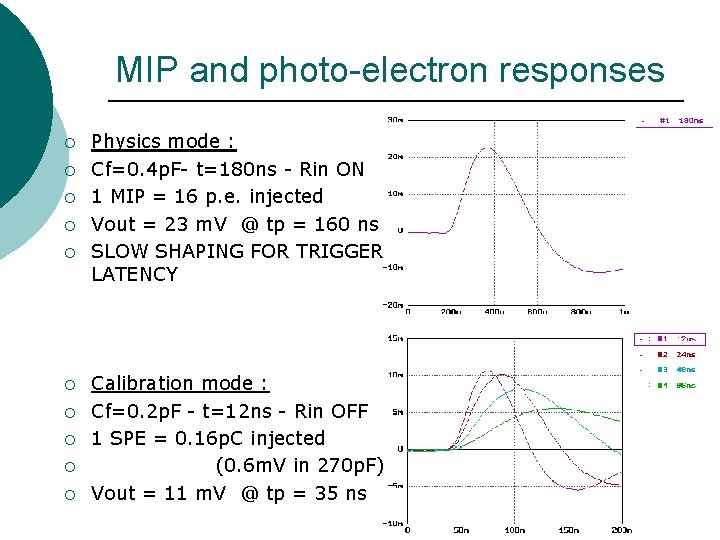

MIP and photo-electron responses ¡ ¡ ¡ ¡ ¡ Physics mode : Cf=0. 4 p. F- t=180 ns - Rin ON 1 MIP = 16 p. e. injected Vout = 23 m. V @ tp = 160 ns SLOW SHAPING FOR TRIGGER LATENCY Calibration mode : Cf=0. 2 p. F - t=12 ns - Rin OFF 1 SPE = 0. 16 p. C injected (0. 6 m. V in 270 p. F) Vout = 11 m. V @ tp = 35 ns

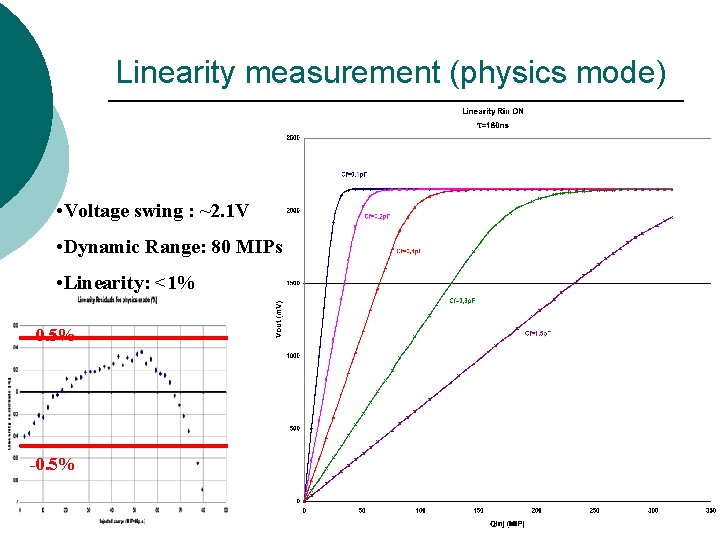

Linearity measurement (physics mode) • Voltage swing : ~2. 1 V • Dynamic Range: 80 MIPs • Linearity: <1% 0. 5% -0. 5%

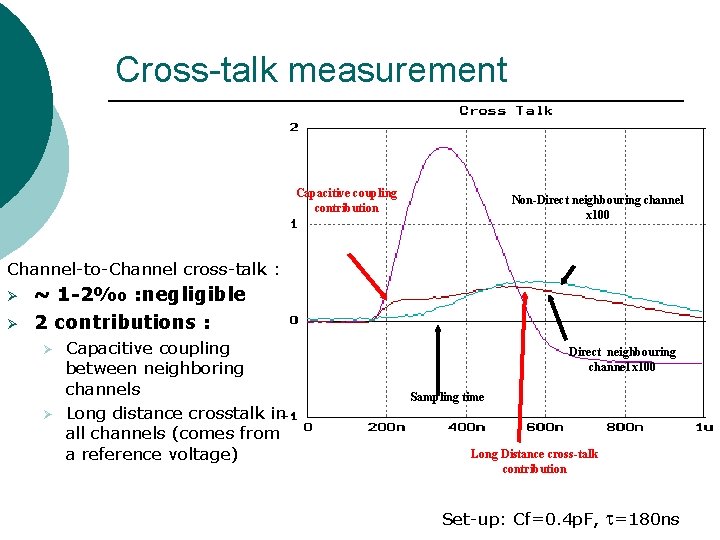

Cross-talk measurement Capacitive coupling contribution Non-Direct neighbouring channel x 100 Channel-to-Channel cross-talk : Ø Ø ~ 1 -2‰ : negligible 2 contributions : Ø Ø Capacitive coupling between neighboring channels Long distance crosstalk in all channels (comes from a reference voltage) Direct neighbouring channel x 100 Sampling time Long Distance cross-talk contribution Set-up: Cf=0. 4 p. F, t=180 ns

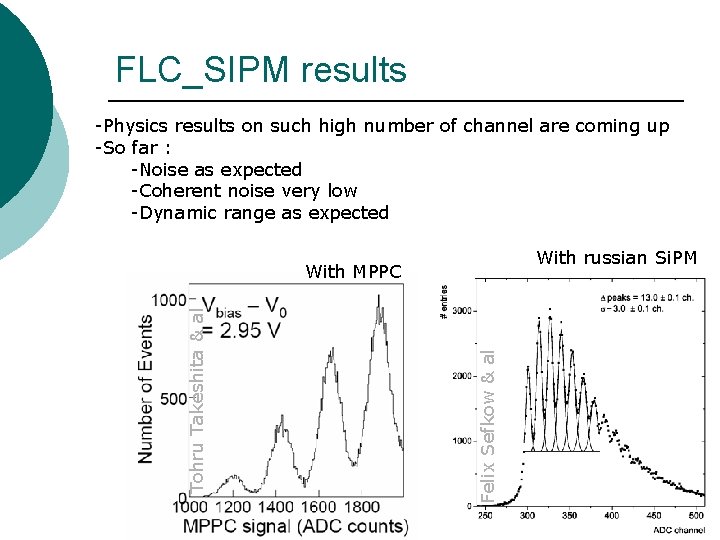

FLC_SIPM results -Physics results on such high number of channel are coming up -So far : -Noise as expected -Coherent noise very low -Dynamic range as expected With russian Si. PM Felix Sefkow & al Tohru Takeshita & al With MPPC

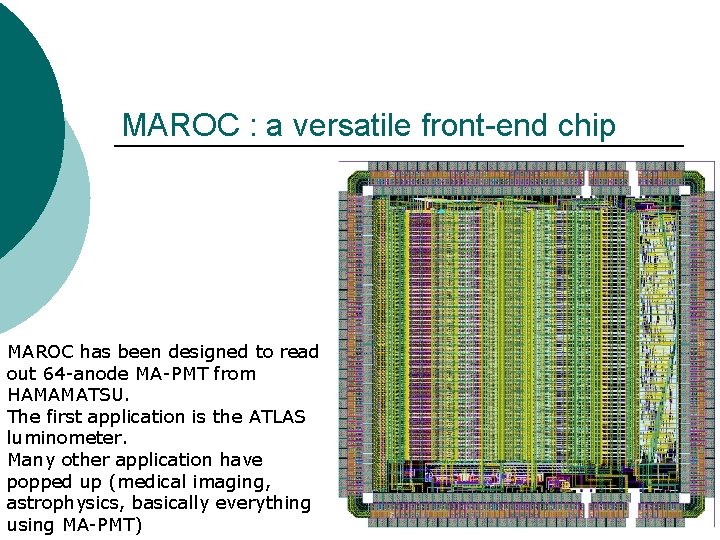

MAROC : a versatile front-end chip MAROC has been designed to read out 64 -anode MA-PMT from HAMAMATSU. The first application is the ATLAS luminometer. Many other application have popped up (medical imaging, astrophysics, basically everything using MA-PMT)

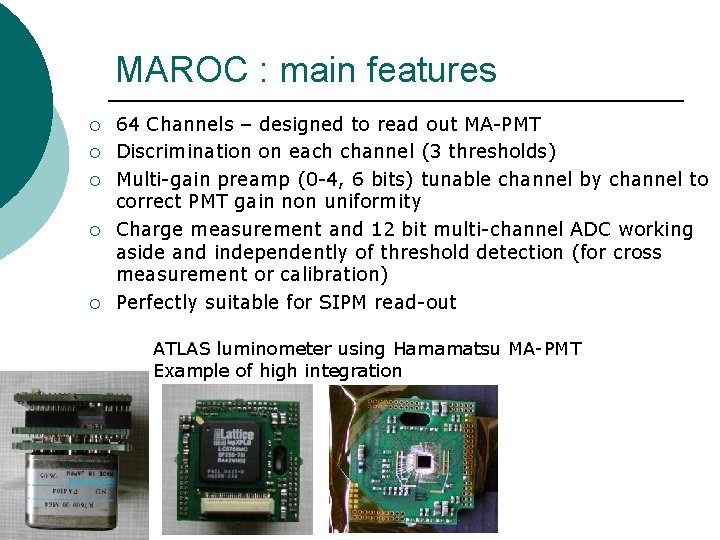

MAROC : main features ¡ ¡ ¡ 64 Channels – designed to read out MA-PMT Discrimination on each channel (3 thresholds) Multi-gain preamp (0 -4, 6 bits) tunable channel by channel to correct PMT gain non uniformity Charge measurement and 12 bit multi-channel ADC working aside and independently of threshold detection (for cross measurement or calibration) Perfectly suitable for SIPM read-out ATLAS luminometer using Hamamatsu MA-PMT Example of high integration

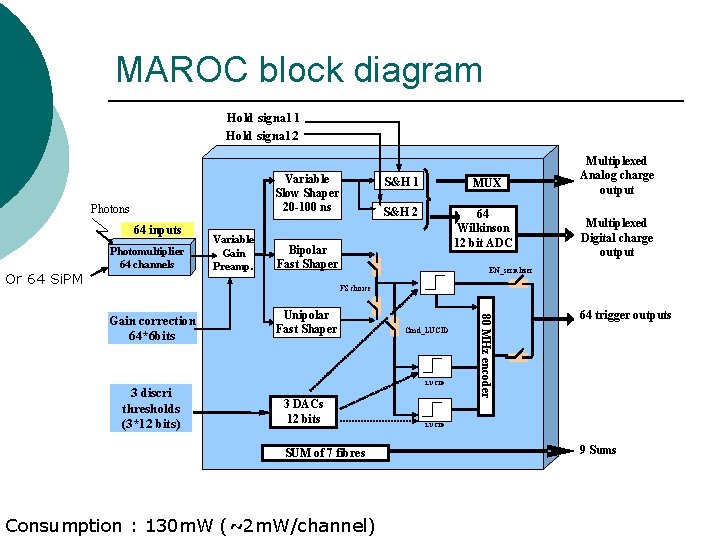

MAROC block diagram Hold signal 1 Hold signal 2 Variable Slow Shaper 20 -100 ns Photons 64 inputs Photomultiplier 64 channels Or 64 Si. PM Variable Gain Preamp. S&H 1 MUX S&H 2 64 Wilkinson 12 bit ADC Bipolar Fast Shaper Multiplexed Analog charge output Multiplexed Digital charge output EN_serializer FS choice 3 discri thresholds (3*12 bits) Unipolar Fast Shaper Cmd_LUCID 3 DACs 12 bits SUM of 7 fibres Consumption : 130 m. W (~2 m. W/channel) 80 MHz encoder Gain correction 64*6 bits 64 trigger outputs LUCID 9 Sums

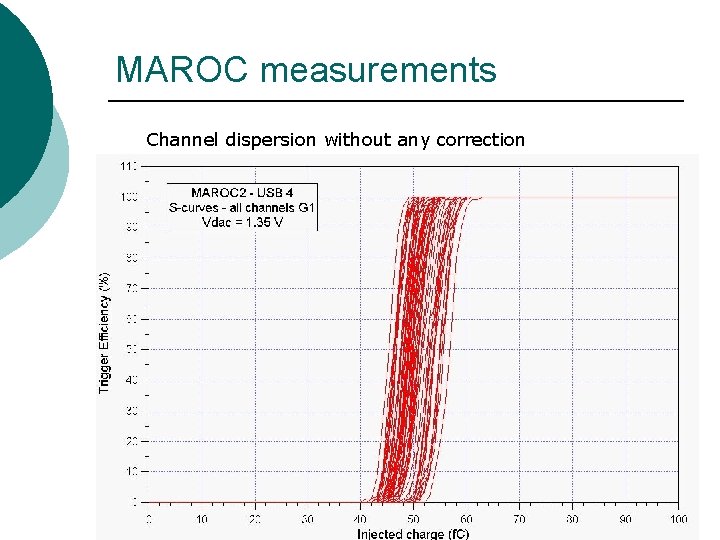

MAROC measurements Channel dispersion without any correction

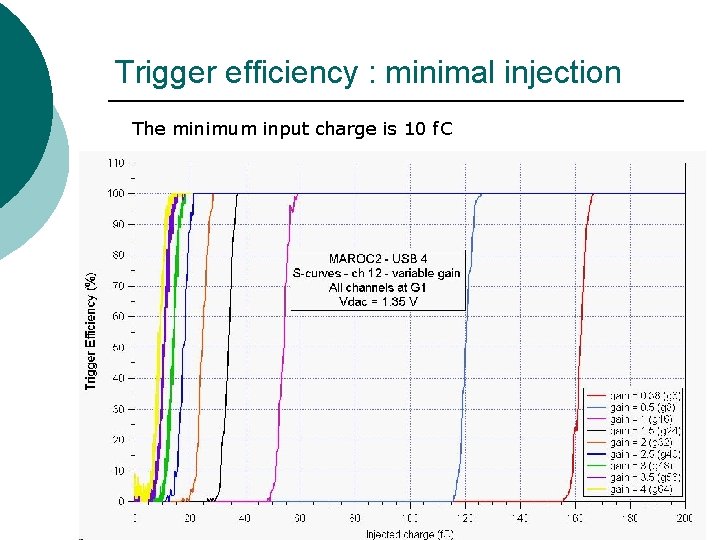

Trigger efficiency : minimal injection The minimum input charge is 10 f. C

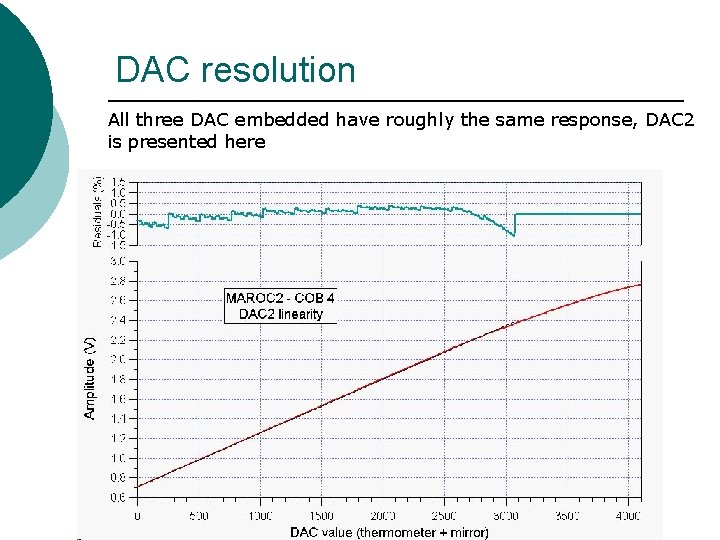

DAC resolution All three DAC embedded have roughly the same response, DAC 2 is presented here

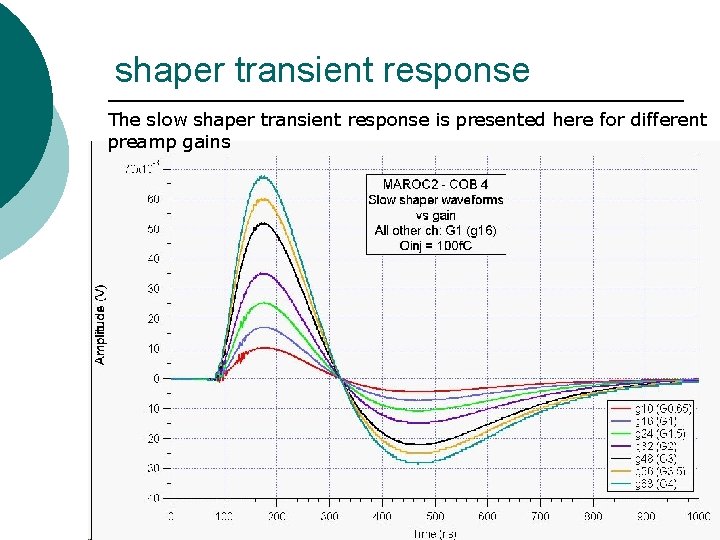

shaper transient response The slow shaper transient response is presented here for different preamp gains

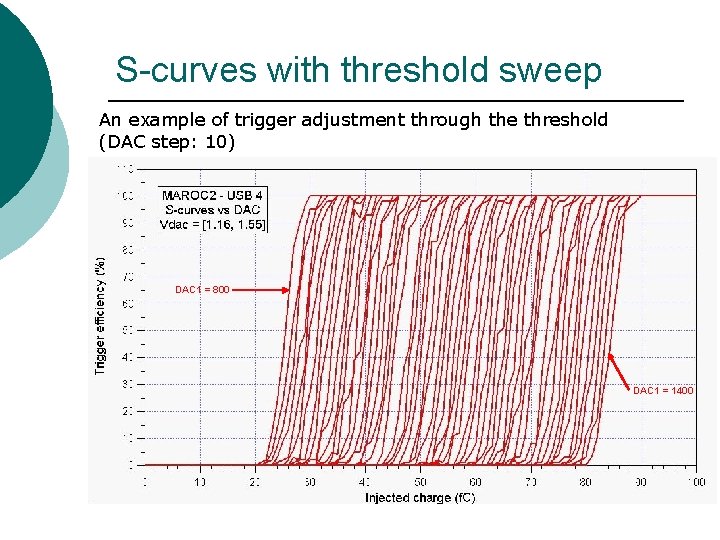

S-curves with threshold sweep An example of trigger adjustment through the threshold (DAC step: 10) DAC 1 = 800 DAC 1 = 1400

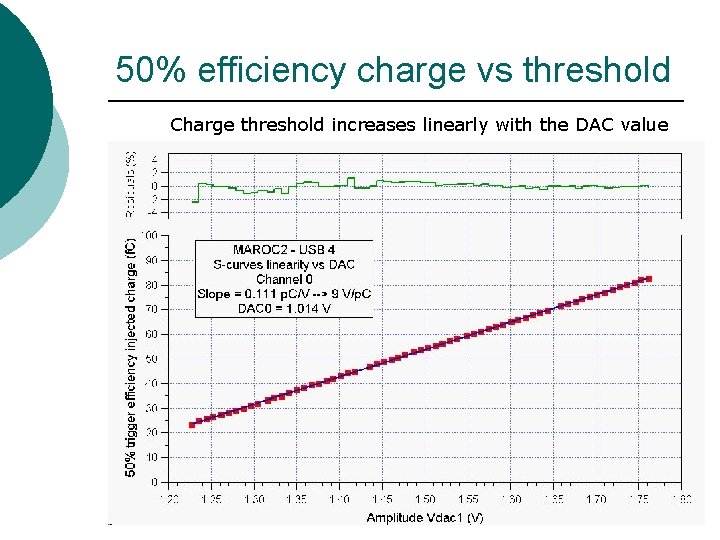

50% efficiency charge vs threshold Charge threshold increases linearly with the DAC value

HARDROC presentation HARDROC has been designed to read out the CALICE RPC DHCAL technical prototype.

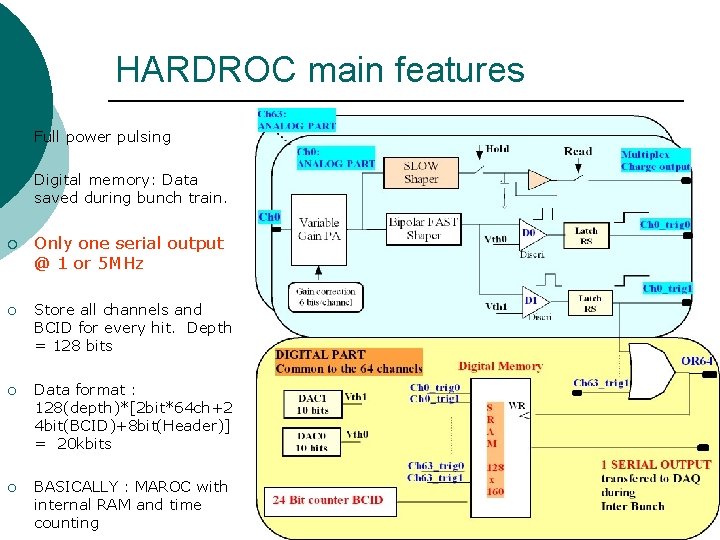

HARDROC main features ¡ Full power pulsing ¡ Digital memory: Data saved during bunch train. ¡ Only one serial output @ 1 or 5 MHz ¡ Store all channels and BCID for every hit. Depth = 128 bits ¡ Data format : 128(depth)*[2 bit*64 ch+2 4 bit(BCID)+8 bit(Header)] = 20 kbits ¡ BASICALLY : MAROC with internal RAM and time counting

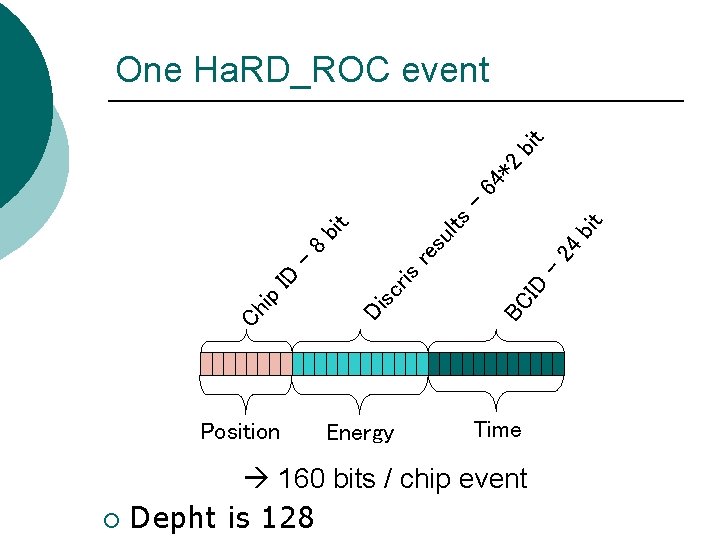

¡ bit 24 – ID BC ris sc Di Position Energy Time Ch ip ID - re 8 su bit lts – 64 *2 bit One Ha. RD_ROC event 160 bits / chip event Depht is 128

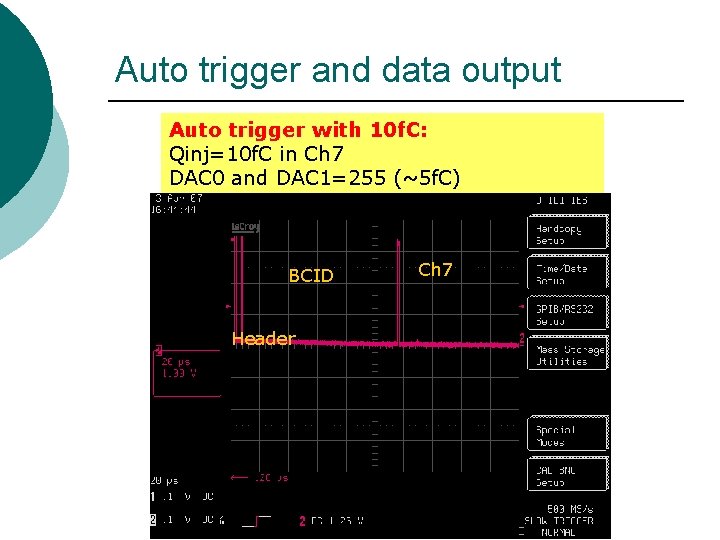

Auto trigger and data output Auto trigger with 10 f. C: Qinj=10 f. C in Ch 7 DAC 0 and DAC 1=255 (~5 f. C) BCID Header Ch 7

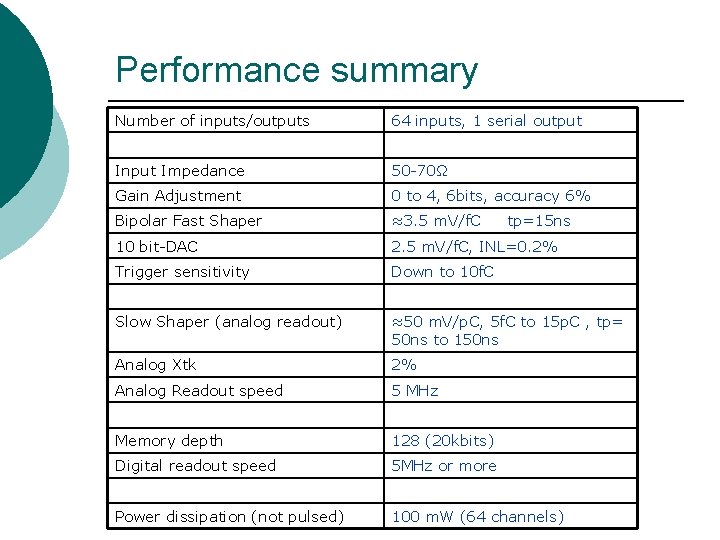

Performance summary Number of inputs/outputs 64 inputs, 1 serial output Input Impedance 50 -70Ω Gain Adjustment 0 to 4, 6 bits, accuracy 6% Bipolar Fast Shaper ≈3. 5 m. V/f. C 10 bit-DAC 2. 5 m. V/f. C, INL=0. 2% Trigger sensitivity Down to 10 f. C Slow Shaper (analog readout) ≈50 m. V/p. C, 5 f. C to 15 p. C , tp= 50 ns to 150 ns Analog Xtk 2% Analog Readout speed 5 MHz Memory depth 128 (20 kbits) Digital readout speed 5 MHz or more Power dissipation (not pulsed) 100 m. W (64 channels) tp=15 ns

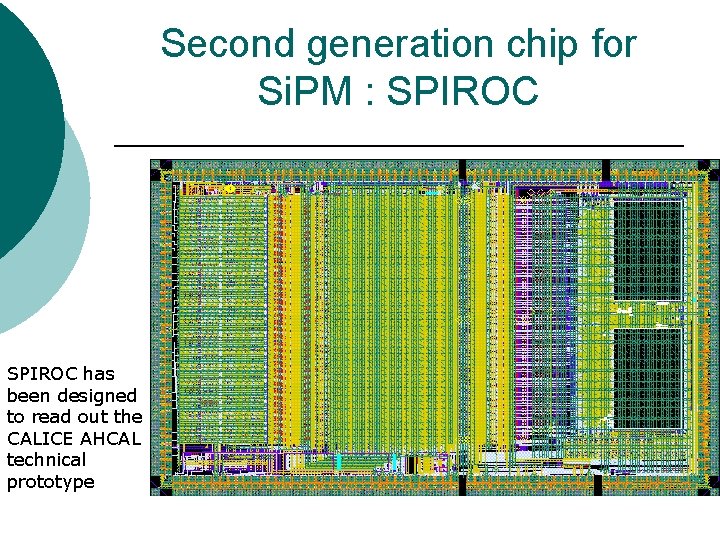

Second generation chip for Si. PM : SPIROC has been designed to read out the CALICE AHCAL technical prototype

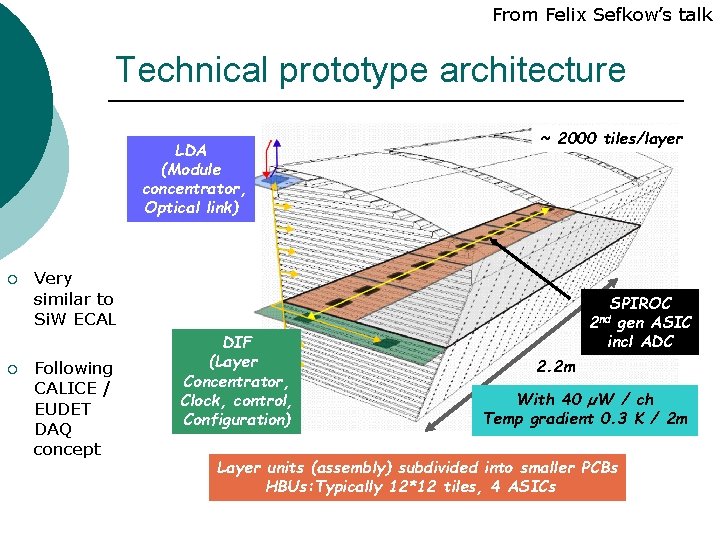

From Felix Sefkow’s talk Technical prototype architecture LDA (Module concentrator, Optical link) ¡ ¡ ~ 2000 tiles/layer Very similar to Si. W ECAL Following CALICE / EUDET DAQ concept DIF (Layer Concentrator, Clock, control, Configuration) SPIROC gen ASIC incl ADC 2 nd 2. 2 m With 40 µW / ch Temp gradient 0. 3 K / 2 m Layer units (assembly) subdivided into smaller PCBs HBUs: Typically 12*12 tiles, 4 ASICs

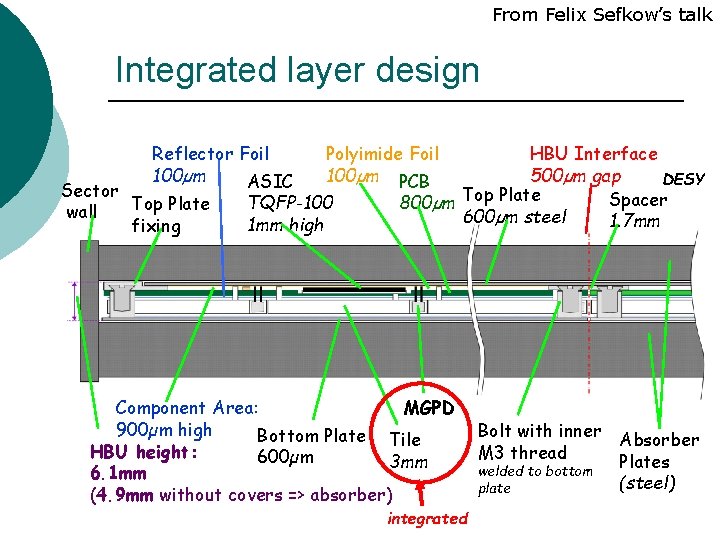

From Felix Sefkow’s talk Integrated layer design Reflector Foil Polyimide Foil HBU Interface 100µm PCB 500µm gap DESY ASIC Sector Spacer TQFP-100 800µm Top Plate wall 600µm steel 1. 7 mm 1 mm high fixing Component Area: MGPD 900µm high Bottom Plate Tile HBU height: 600µm 3 mm 6. 1 mm (4. 9 mm without covers => absorber) integrated Bolt with inner M 3 thread welded to bottom plate Absorber Plates (steel)

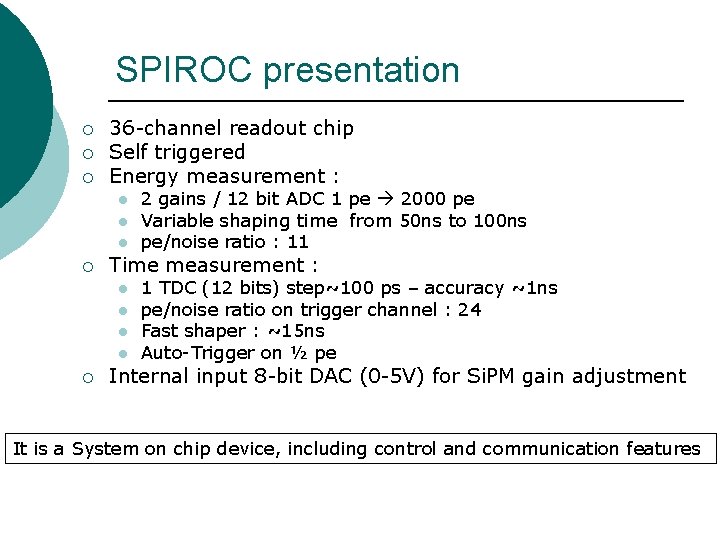

SPIROC presentation ¡ ¡ ¡ 36 -channel readout chip Self triggered Energy measurement : l l l ¡ Time measurement : l l ¡ 2 gains / 12 bit ADC 1 pe 2000 pe Variable shaping time from 50 ns to 100 ns pe/noise ratio : 11 1 TDC (12 bits) step~100 ps – accuracy ~1 ns pe/noise ratio on trigger channel : 24 Fast shaper : ~15 ns Auto-Trigger on ½ pe Internal input 8 -bit DAC (0 -5 V) for Si. PM gain adjustment It is a System on chip device, including control and communication features

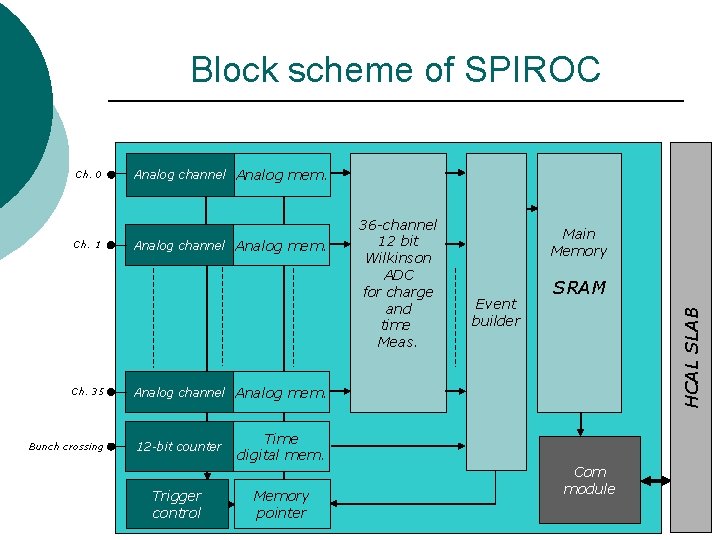

Block scheme of SPIROC Ch. 1 Ch. 35 Bunch crossing Analog channel Analog mem. 36 -channel 12 bit Wilkinson ADC for charge and time Meas. Main Memory Event builder SRAM HCAL SLAB Ch. 0 Analog channel Analog mem. 12 -bit counter Trigger control Time digital mem. Memory pointer Com module

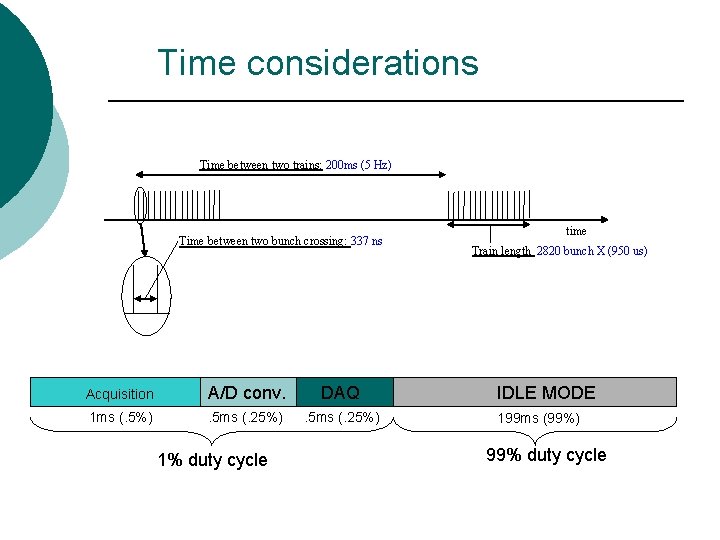

Time considerations Time between two trains: 200 ms (5 Hz) Time between two bunch crossing: 337 ns Acquisition A/D conv. DAQ 1 ms (. 5%) . 5 ms (. 25%) 1% duty cycle time Train length 2820 bunch X (950 us) IDLE MODE 199 ms (99%) 99% duty cycle

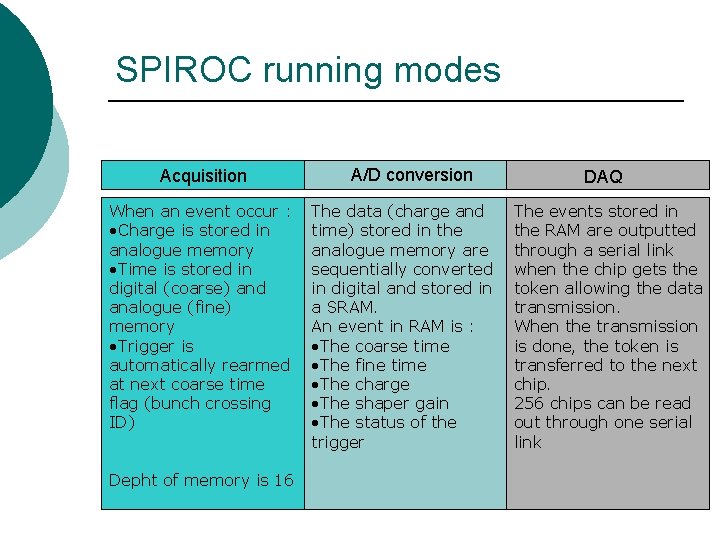

SPIROC running modes Acquisition When an event occur : • Charge is stored in analogue memory • Time is stored in digital (coarse) and analogue (fine) memory • Trigger is automatically rearmed at next coarse time flag (bunch crossing ID) Depht of memory is 16 A/D conversion The data (charge and time) stored in the analogue memory are sequentially converted in digital and stored in a SRAM. An event in RAM is : • The coarse time • The fine time • The charge • The shaper gain • The status of the trigger DAQ The events stored in the RAM are outputted through a serial link when the chip gets the token allowing the data transmission. When the transmission is done, the token is transferred to the next chip. 256 chips can be read out through one serial link

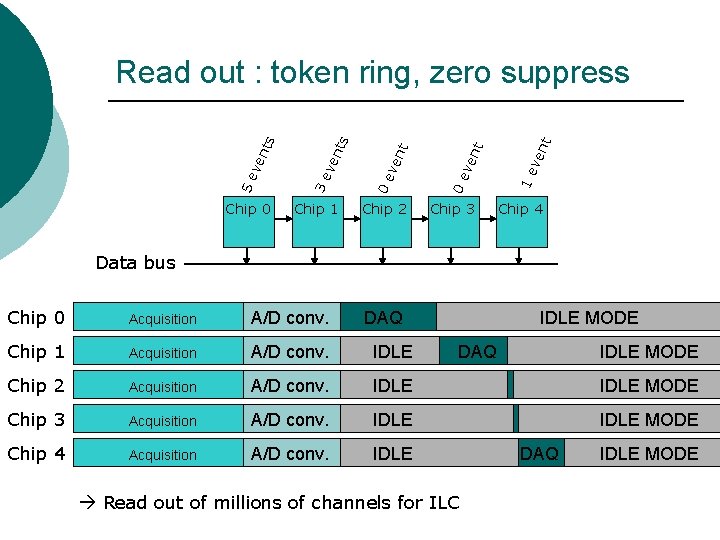

Chip 0 Chip 1 Chip 2 Chip 3 1 e ve nt 0 e ve nt 3 e ve nts 5 e ve nts Read out : token ring, zero suppress Chip 4 Data bus Chip 0 Acquisition A/D conv. Chip 1 Acquisition A/D conv. IDLE Chip 2 Acquisition A/D conv. IDLE MODE Chip 3 Acquisition A/D conv. IDLE MODE Chip 4 Acquisition A/D conv. IDLE DAQ IDLE MODE DAQ Read out of millions of channels for ILC IDLE MODE DAQ IDLE MODE

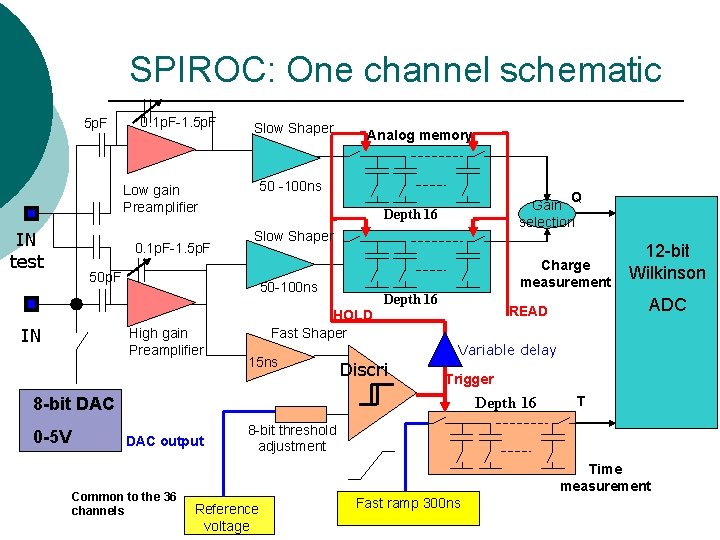

SPIROC: One channel schematic 5 p. F 0. 1 p. F-1. 5 p. F Slow Shaper 50 -100 ns Low gain Preamplifier IN test 0. 1 p. F-1. 5 p. F Slow Shaper Charge measurement 50 -100 ns High gain Preamplifier Q Gain selection Depth 16 50 p. F IN Analog memory Depth 16 15 ns Discri Variable delay Trigger Depth 16 8 -bit DAC 0 -5 V DAC output Common to the 36 channels ADC READ HOLD Fast Shaper 12 -bit Wilkinson T 8 -bit threshold adjustment Time measurement Reference voltage Fast ramp 300 ns

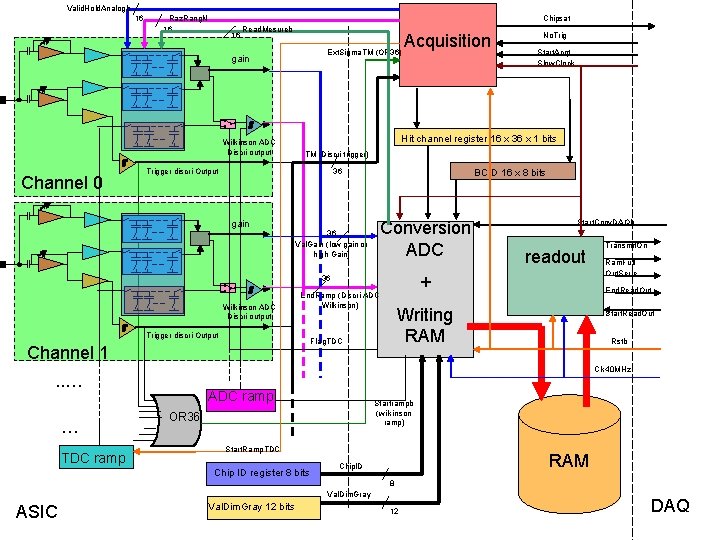

Valid. Hold. Analogb 16 Raz. Rang. N 16 Chipsat 16 Read. Mesureb Acquisition Ext. Sigma. TM (OR 36) gain Wilkinson ADC Discri output Channel 0 TM (Discri trigger) 36 36 Val. Gain (low gain or high Gain) BCID 16 x 8 bits Conversion ADC End. Ramp (Discri ADC Wilkinson) Trigger discri Output TDC ramp Transmit. On Ram. Full Out. Serie End. Read. Out Start. Read. Out Rstb Clk 40 MHz . . … … readout Writing RAM Flag. TDC Channel 1 Start. Conv. DAQb + 36 Wilkinson ADC Discri output Start. Acqt Slow. Clock Hit channel register 16 x 36 x 1 bits Trigger discri Output gain No. Trig ADC ramp Startrampb (wilkinson ramp) OR 36 Start. Ramp. TDC Chip ID register 8 bits RAM Chip. ID 8 Val. Dim. Gray ASIC Val. Dim. Gray 12 bits 12 DAQ

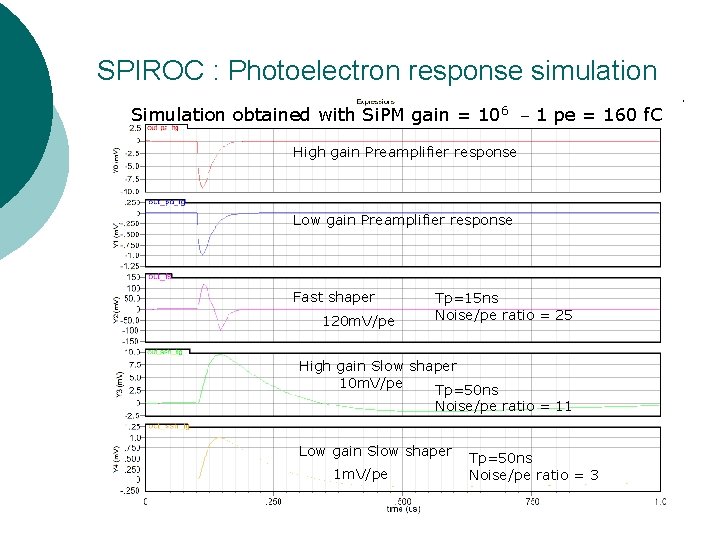

SPIROC : Photoelectron response simulation Simulation obtained with Si. PM gain = 106 _ 1 pe = 160 f. C High gain Preamplifier response Low gain Preamplifier response Fast shaper 120 m. V/pe Tp=15 ns Noise/pe ratio = 25 High gain Slow shaper 10 m. V/pe Tp=50 ns Noise/pe ratio = 11 Low gain Slow shaper 1 m. V/pe Tp=50 ns Noise/pe ratio = 3

Conclusion ¡ ¡ Our group is able to provide in short terms integrated electronic to read out MA-PMT, Si. PM or APDs. The versatility of our chips – using programmable parameters (gain, peaking time, thresholds) make them suitable for many applications Integrated electronic is the best way to read out high number of channels detectors, it allows to reduce cost and improve compacity in every application More information : fleury@lal. in 2 p 3. fr

- Slides: 38