Instruction sets z Computer architecture taxonomy z Assembly

Instruction sets z. Computer architecture taxonomy. z. Assembly language. © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

von Neumann architecture z. Memory holds data, instructions. z. Central processing unit (CPU) fetches instructions from memory. y. Separate CPU and memory distinguishes programmable computer. z. CPU registers help out: program counter (PC), instruction register (IR), generalpurpose registers, etc. © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

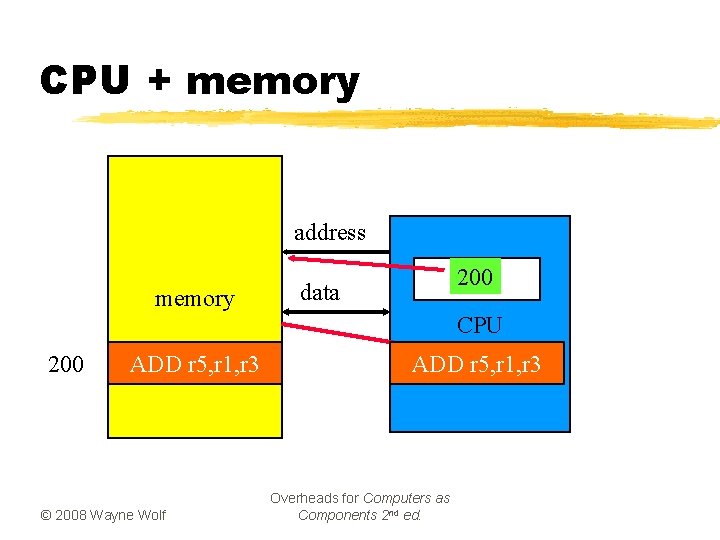

CPU + memory address memory 200 PC data CPU 200 ADD r 5, r 1, r 3 © 2008 Wayne Wolf ADD IR r 5, r 1, r 3 Overheads for Computers as Components 2 nd ed.

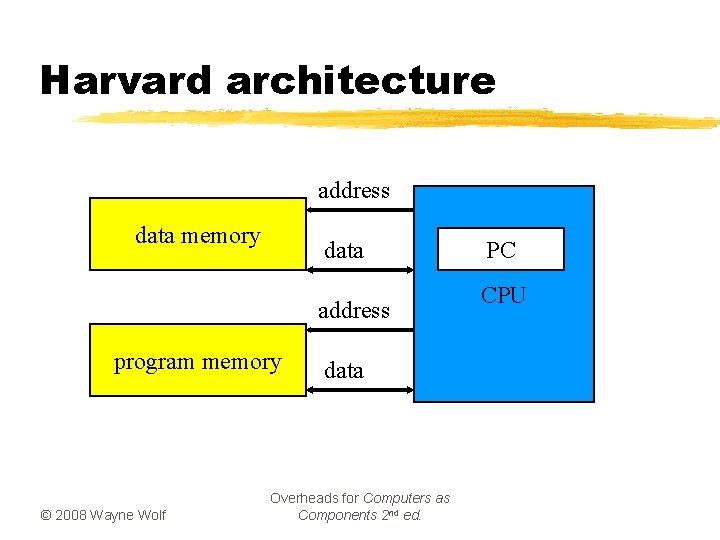

Harvard architecture address data memory data address program memory © 2008 Wayne Wolf data Overheads for Computers as Components 2 nd ed. PC CPU

von Neumann vs. Harvard z. Harvard can’t use self-modifying code. z. Harvard allows two simultaneous memory fetches. z. Most DSPs use Harvard architecture for streaming data: ygreater memory bandwidth; ymore predictable bandwidth. © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

RISC vs. CISC z. Complex instruction set computer (CISC): ymany addressing modes; ymany operations. z. Reduced instruction set computer (RISC): yload/store; ypipelinable instructions. © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

Instruction set characteristics z. Fixed vs. variable length. z. Addressing modes. z. Number of operands. z. Types of operands. © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

Programming model z. Programming model: registers visible to the programmer. z. Some registers are not visible (IR). © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

Multiple implementations z. Successful architectures have several implementations: yvarying clock speeds; ydifferent bus widths; ydifferent cache sizes; yetc. © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

Assembly language z. One-to-one with instructions (more or less). z. Basic features: y. One instruction per line. y. Labels provide names for addresses (usually in first column). y. Instructions often start in later columns. y. Columns run to end of line. © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

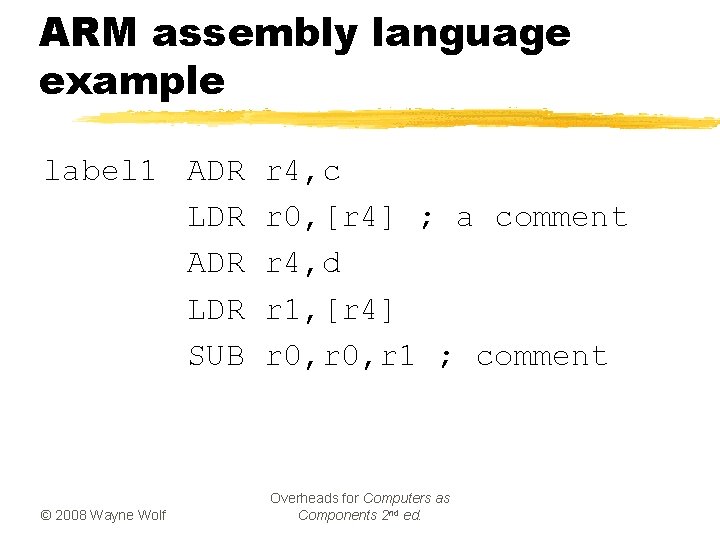

ARM assembly language example label 1 ADR LDR SUB © 2008 Wayne Wolf r 4, c r 0, [r 4] ; a comment r 4, d r 1, [r 4] r 0, r 1 ; comment Overheads for Computers as Components 2 nd ed.

Pseudo-ops z. Some assembler directives don’t correspond directly to instructions: y. Define current address. y. Reserve storage. y. Constants. © 2008 Wayne Wolf Overheads for Computers as Components 2 nd ed.

- Slides: 12