INSTRUCTION SET OF MICROPROCESSOR 8085 8085 has 246

![I] Data Transfer Group 1) MOV rd, rs : MOVE REGISTER Format: [rd] [rs] I] Data Transfer Group 1) MOV rd, rs : MOVE REGISTER Format: [rd] [rs]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-12.jpg)

![I] Data Transfer Group 2) MOV r, M : MOVE FROM MEMORY TO REGISTER I] Data Transfer Group 2) MOV r, M : MOVE FROM MEMORY TO REGISTER](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-13.jpg)

![I] Data Transfer Group 3) MOV M, r : MOVE FROM REGISTER TO MEMORY I] Data Transfer Group 3) MOV M, r : MOVE FROM REGISTER TO MEMORY](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-14.jpg)

![I] Data Transfer Group 4) MVI r, data : MOVE IMMEDIATE 8 -BIT DATA I] Data Transfer Group 4) MVI r, data : MOVE IMMEDIATE 8 -BIT DATA](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-15.jpg)

![I] Data Transfer Group 5) MVI M, data : MOVE IMMEDIATE 8 -BIT DATA I] Data Transfer Group 5) MVI M, data : MOVE IMMEDIATE 8 -BIT DATA](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-16.jpg)

![I] Data Transfer Group 6) LXI rp, 16 -bit data : LOAD REGISTER PAIR I] Data Transfer Group 6) LXI rp, 16 -bit data : LOAD REGISTER PAIR](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-17.jpg)

![I] Data Transfer Group 7) LDA address : LOAD ACCUMULATOR DIRECT WITH DATA AT I] Data Transfer Group 7) LDA address : LOAD ACCUMULATOR DIRECT WITH DATA AT](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-18.jpg)

![I] Data Transfer Group 8) STA address : LOAD ACCUMULATOR DIRECT WITH DATA AT I] Data Transfer Group 8) STA address : LOAD ACCUMULATOR DIRECT WITH DATA AT](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-19.jpg)

![I] Data Transfer Group 9) LHLD address : LOAD H & L REGISTER DIRECT I] Data Transfer Group 9) LHLD address : LOAD H & L REGISTER DIRECT](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-20.jpg)

![I] Data Transfer Group 10) SHLD address : STORE H & L REGISTER DIRECT I] Data Transfer Group 10) SHLD address : STORE H & L REGISTER DIRECT](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-21.jpg)

![I] Data Transfer Group 11) LDAX rp : LOAD ACCUMULATOR INDIRECT Format: [A] [[rp]] I] Data Transfer Group 11) LDAX rp : LOAD ACCUMULATOR INDIRECT Format: [A] [[rp]]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-22.jpg)

![I] Data Transfer Group 12) STAX rp : STORE ACCUMULATOR INDIRECT Format: [[rp]] [A] I] Data Transfer Group 12) STAX rp : STORE ACCUMULATOR INDIRECT Format: [[rp]] [A]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-23.jpg)

![I] Data Transfer Group 13) XCHG : EXCHANGE H & L WITH D & I] Data Transfer Group 13) XCHG : EXCHANGE H & L WITH D &](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-24.jpg)

![II] Arithmetic Group 1) ADD r : ADD REGISTER Format: [A] + [r] Addressing: II] Arithmetic Group 1) ADD r : ADD REGISTER Format: [A] + [r] Addressing:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-25.jpg)

![II] Arithmetic Group 2) ADD M : ADD MEMORY CONTENT TO ACCUMULATOR Format: [A] II] Arithmetic Group 2) ADD M : ADD MEMORY CONTENT TO ACCUMULATOR Format: [A]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-26.jpg)

![II] Arithmetic Group 3) ADI data : ADD IMMEDIATE TO ACCUMULATOR Format: [A] + II] Arithmetic Group 3) ADI data : ADD IMMEDIATE TO ACCUMULATOR Format: [A] +](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-27.jpg)

![II] Arithmetic Group 4) ADC r : ADD REGISTER TO ACCUMULATOR WITH CARRY Format: II] Arithmetic Group 4) ADC r : ADD REGISTER TO ACCUMULATOR WITH CARRY Format:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-28.jpg)

![II] Arithmetic Group 5) ADC M : ADD MEMORY CONTENT TO ACCUMULATOR WITH CARRY II] Arithmetic Group 5) ADC M : ADD MEMORY CONTENT TO ACCUMULATOR WITH CARRY](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-30.jpg)

![II] Arithmetic Group 6) ACI data : ADD IMMEDIATE TO ACCUMULATOR WITH CARRY Format: II] Arithmetic Group 6) ACI data : ADD IMMEDIATE TO ACCUMULATOR WITH CARRY Format:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-31.jpg)

![II] Arithmetic Group 7) SUB r : SUBTRACT REGISTER FROM ACCUMULATOR Format: [A] - II] Arithmetic Group 7) SUB r : SUBTRACT REGISTER FROM ACCUMULATOR Format: [A] -](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-32.jpg)

![II] Arithmetic Group 8) SUB M : SUBTRACT MEMORY FROM ACCUMULATOR Format: [A] - II] Arithmetic Group 8) SUB M : SUBTRACT MEMORY FROM ACCUMULATOR Format: [A] -](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-33.jpg)

![II] Arithmetic Group 9) SUI data : SUBTRACT IMMEDIATE FROM ACCUMULATOR Format: [A] – II] Arithmetic Group 9) SUI data : SUBTRACT IMMEDIATE FROM ACCUMULATOR Format: [A] –](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-34.jpg)

![II] Arithmetic Group 10) SBB r : SUBTRACT REGISTER & BORROW FROM ACCUMULATOR Format: II] Arithmetic Group 10) SBB r : SUBTRACT REGISTER & BORROW FROM ACCUMULATOR Format:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-35.jpg)

![II] Arithmetic Group 11) SBB M : SUBTRACT MEMORY CONTENT TO ACCUMULATOR WITH CARRY II] Arithmetic Group 11) SBB M : SUBTRACT MEMORY CONTENT TO ACCUMULATOR WITH CARRY](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-36.jpg)

![II] Arithmetic Group 12) SBI data : SUBTRCT IMMEDIATE WITH BORROW Format: Addressing: Group: II] Arithmetic Group 12) SBI data : SUBTRCT IMMEDIATE WITH BORROW Format: Addressing: Group:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-37.jpg)

![II] Arithmetic Group 13) INR r : INCREMENT REGISTER CONTENT BY 1 Format: [r] II] Arithmetic Group 13) INR r : INCREMENT REGISTER CONTENT BY 1 Format: [r]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-38.jpg)

![II] Arithmetic Group 14) INR M : INCREMENT MEMORY CONTENT BY 1 Format: [[H] II] Arithmetic Group 14) INR M : INCREMENT MEMORY CONTENT BY 1 Format: [[H]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-39.jpg)

![II] Arithmetic Group 15) INX rp : INCREMENT REGISTER PAIR BY 1 Format: [rp] II] Arithmetic Group 15) INX rp : INCREMENT REGISTER PAIR BY 1 Format: [rp]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-40.jpg)

![II] Arithmetic Group 16) DCR r : DECREMENT REGISTER CONTENT BY 1 Format: [r] II] Arithmetic Group 16) DCR r : DECREMENT REGISTER CONTENT BY 1 Format: [r]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-41.jpg)

![II] Arithmetic Group 17) DCR M : DECREMENT MEMORY CONTENT BY 1 Format: [[H] II] Arithmetic Group 17) DCR M : DECREMENT MEMORY CONTENT BY 1 Format: [[H]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-42.jpg)

![II] Arithmetic Group 18) DCX rp : DECREMENT REGISTER PAIR BY 1 Format: [rp] II] Arithmetic Group 18) DCX rp : DECREMENT REGISTER PAIR BY 1 Format: [rp]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-43.jpg)

![II] Arithmetic Group 19) DAD rp : ADD REGISTER PAIR TO H-L REGISTER Format: II] Arithmetic Group 19) DAD rp : ADD REGISTER PAIR TO H-L REGISTER Format:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-44.jpg)

- Slides: 44

INSTRUCTION SET OF MICROPROCESSOR 8085

8085 has 246 instructions Each instruction of microprocessor 8085 consists of opcode & operand. Opcode tells about the type of operation while operand can be data (8 or 16 bit), address, register pair, etc.

Addressing mode is format of specifying on operands Microprocessor has five addressing modes

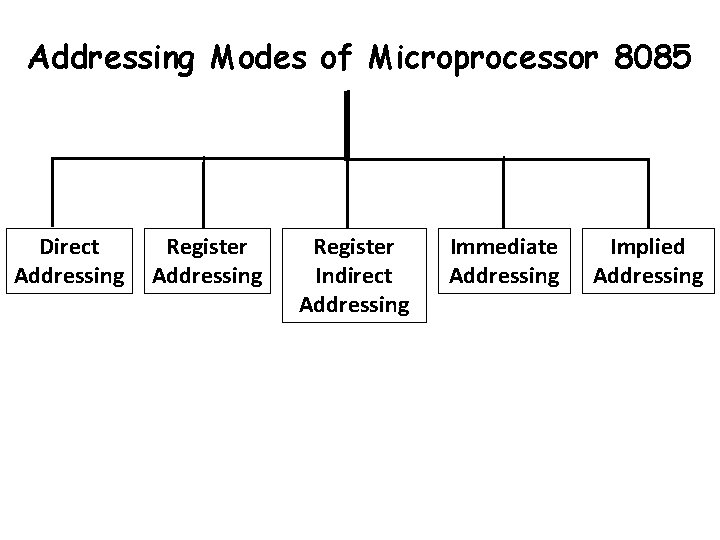

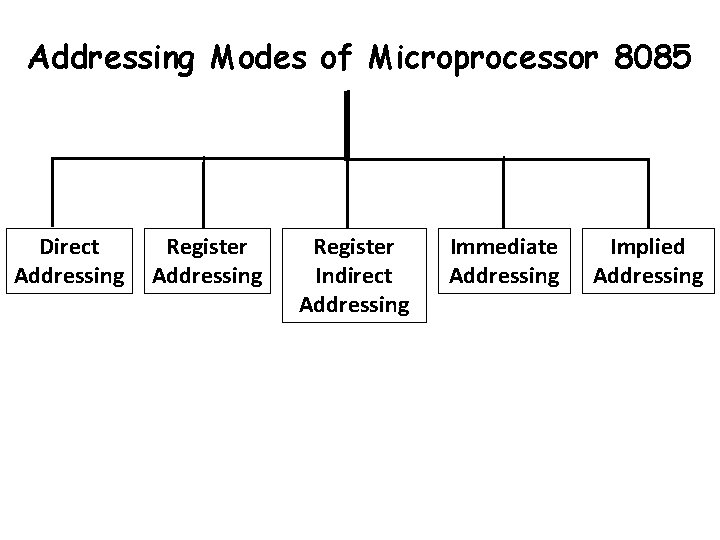

Addressing Modes of Microprocessor 8085 Direct Addressing Register Indirect Addressing Immediate Addressing Implied Addressing

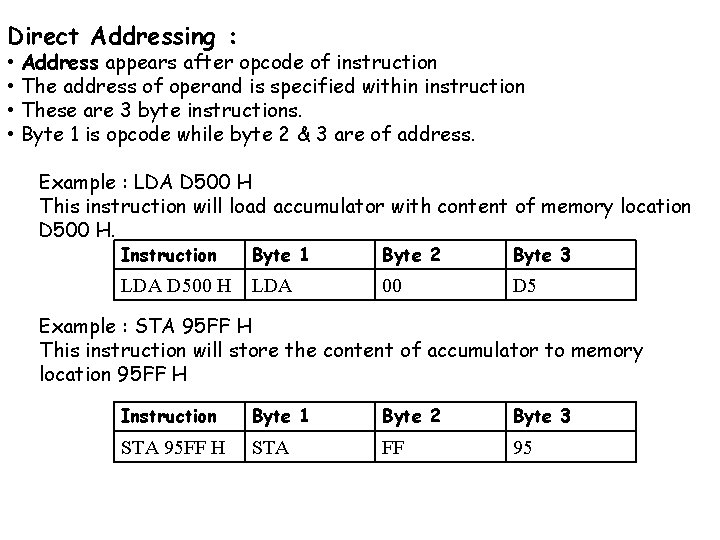

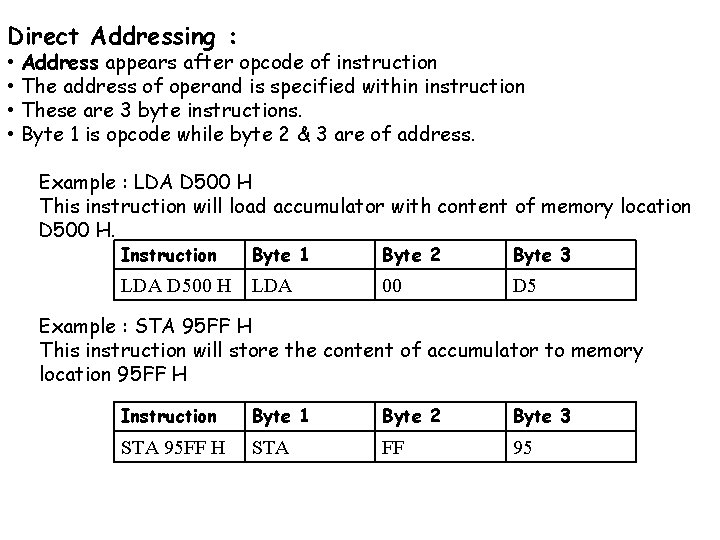

Direct Addressing : • • Address appears after opcode of instruction The address of operand is specified within instruction These are 3 byte instructions. Byte 1 is opcode while byte 2 & 3 are of address. Example : LDA D 500 H This instruction will load accumulator with content of memory location D 500 H. Instruction Byte 1 Byte 2 Byte 3 LDA D 500 H LDA 00 D 5 Example : STA 95 FF H This instruction will store the content of accumulator to memory location 95 FF H Instruction Byte 1 Byte 2 Byte 3 STA 95 FF H STA FF 95

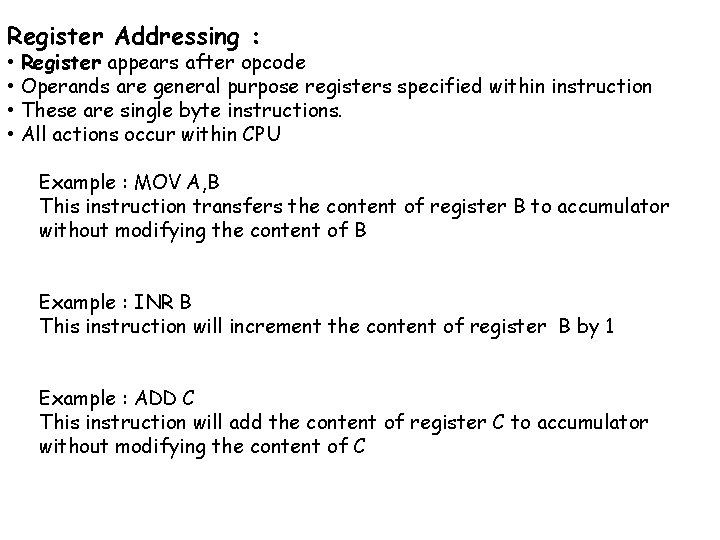

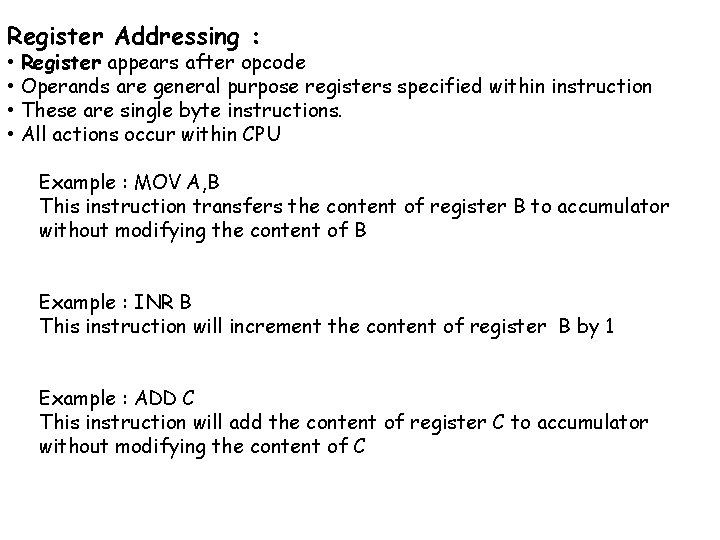

Register Addressing : • • Register appears after opcode Operands are general purpose registers specified within instruction These are single byte instructions. All actions occur within CPU Example : MOV A, B This instruction transfers the content of register B to accumulator without modifying the content of B Example : INR B This instruction will increment the content of register B by 1 Example : ADD C This instruction will add the content of register C to accumulator without modifying the content of C

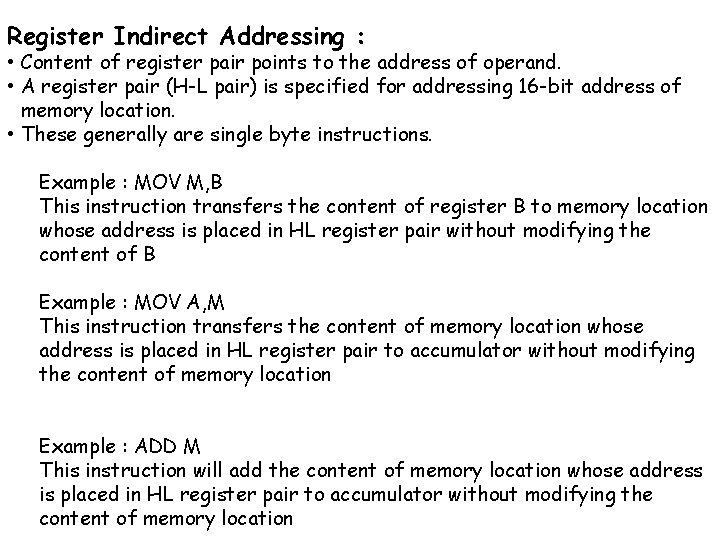

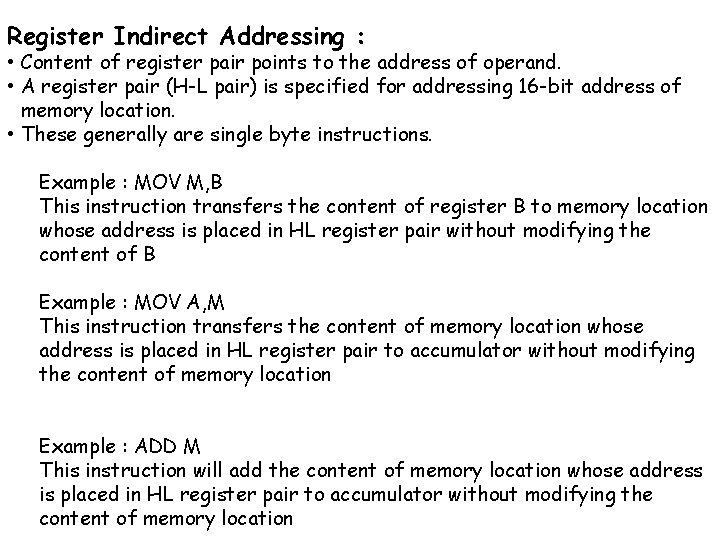

Register Indirect Addressing : • Content of register pair points to the address of operand. • A register pair (H-L pair) is specified for addressing 16 -bit address of memory location. • These generally are single byte instructions. Example : MOV M, B This instruction transfers the content of register B to memory location whose address is placed in HL register pair without modifying the content of B Example : MOV A, M This instruction transfers the content of memory location whose address is placed in HL register pair to accumulator without modifying the content of memory location Example : ADD M This instruction will add the content of memory location whose address is placed in HL register pair to accumulator without modifying the content of memory location

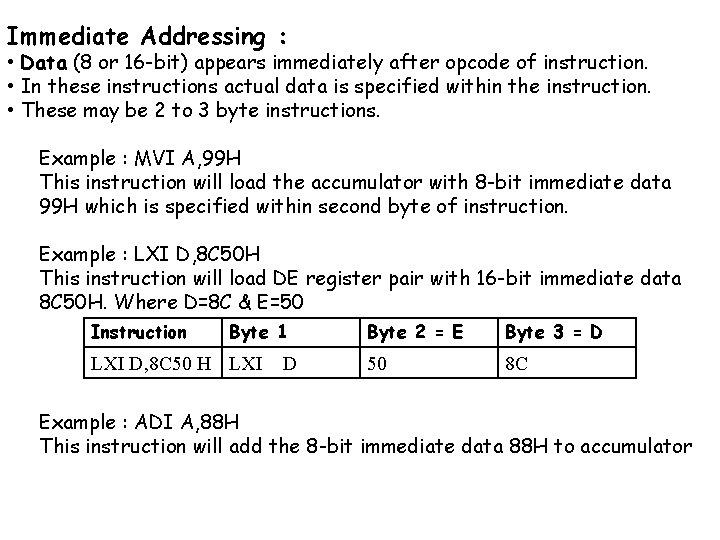

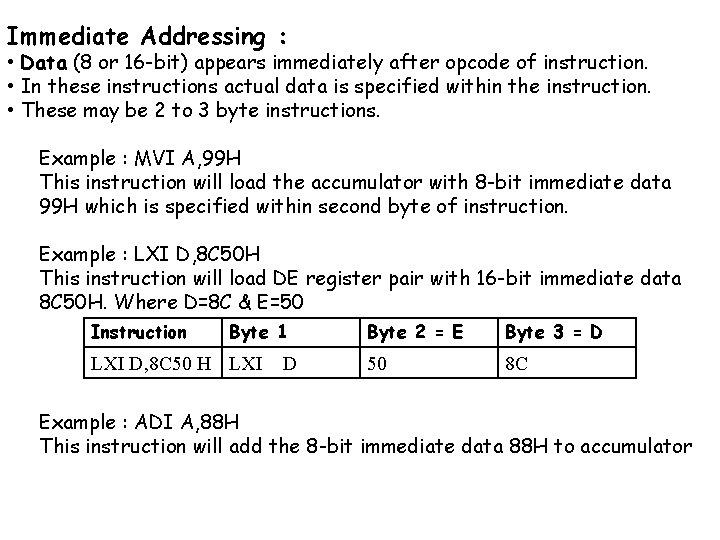

Immediate Addressing : • Data (8 or 16 -bit) appears immediately after opcode of instruction. • In these instructions actual data is specified within the instruction. • These may be 2 to 3 byte instructions. Example : MVI A, 99 H This instruction will load the accumulator with 8 -bit immediate data 99 H which is specified within second byte of instruction. Example : LXI D, 8 C 50 H This instruction will load DE register pair with 16 -bit immediate data 8 C 50 H. Where D=8 C & E=50 Instruction Byte 1 LXI D, 8 C 50 H LXI D Byte 2 = E Byte 3 = D 50 8 C Example : ADI A, 88 H This instruction will add the 8 -bit immediate data 88 H to accumulator

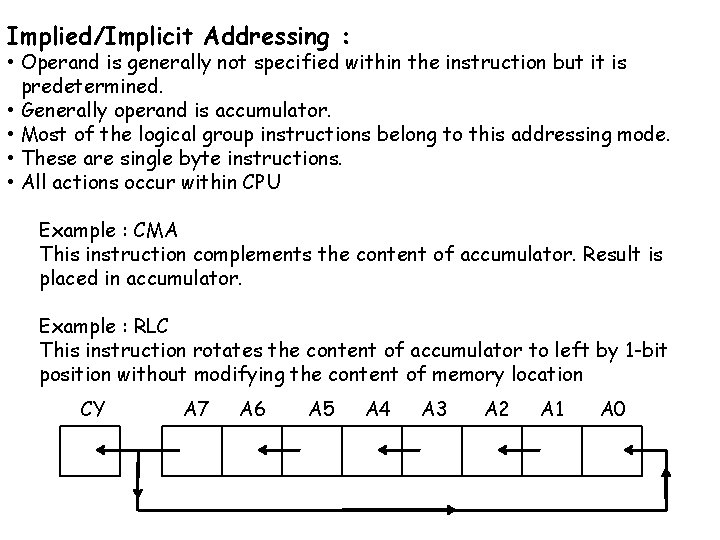

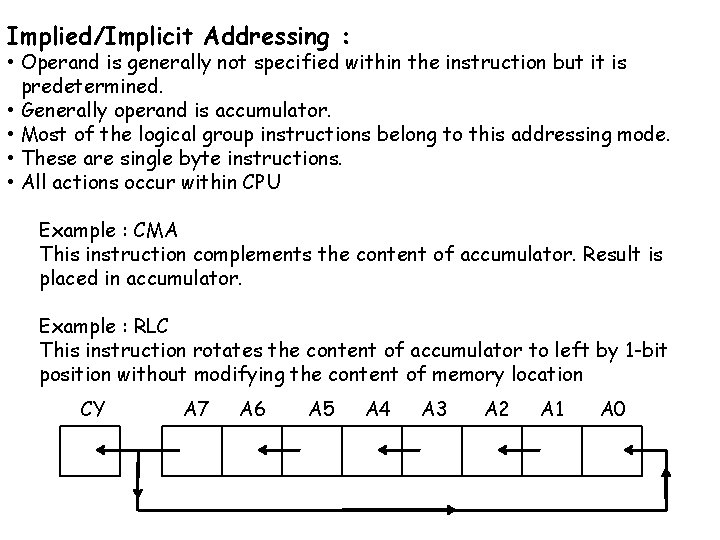

Implied/Implicit Addressing : • Operand is generally not specified within the instruction but it is predetermined. • Generally operand is accumulator. • Most of the logical group instructions belong to this addressing mode. • These are single byte instructions. • All actions occur within CPU Example : CMA This instruction complements the content of accumulator. Result is placed in accumulator. Example : RLC This instruction rotates the content of accumulator to left by 1 -bit position without modifying the content of memory location CY A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0

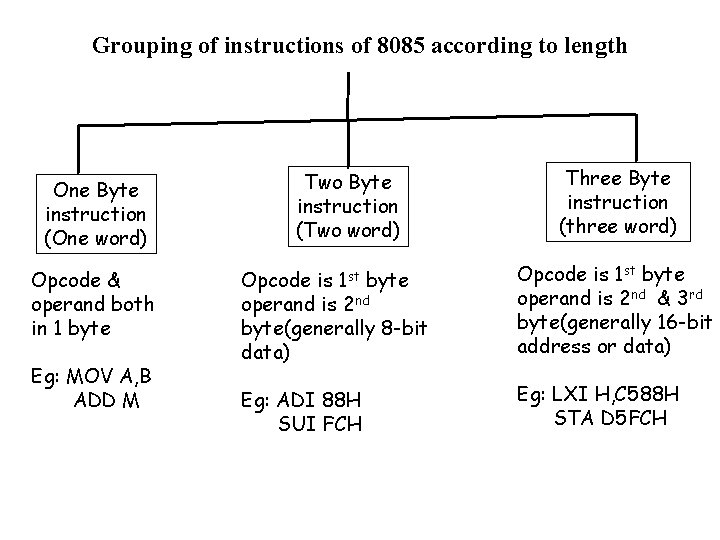

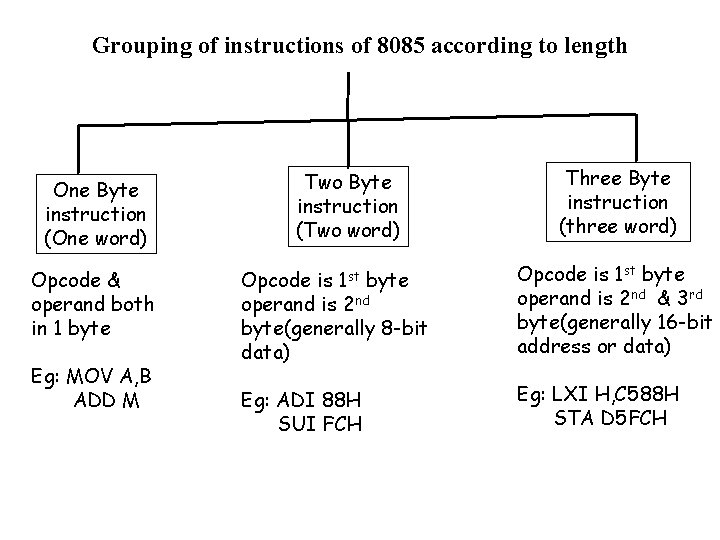

Grouping of instructions of 8085 according to length One Byte instruction (One word) Opcode & operand both in 1 byte Eg: MOV A, B ADD M Two Byte instruction (Two word) Three Byte instruction (three word) Opcode is 1 st byte operand is 2 nd byte(generally 8 -bit data) Opcode is 1 st byte operand is 2 nd & 3 rd byte(generally 16 -bit address or data) Eg: ADI 88 H SUI FCH Eg: LXI H, C 588 H STA D 5 FCH

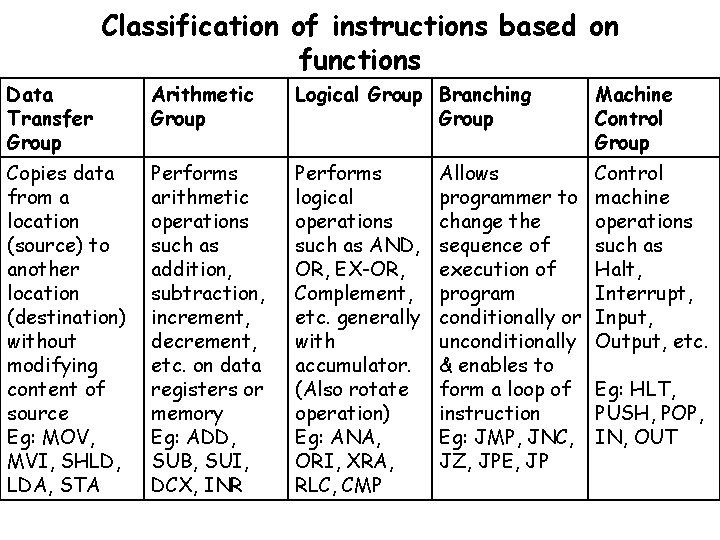

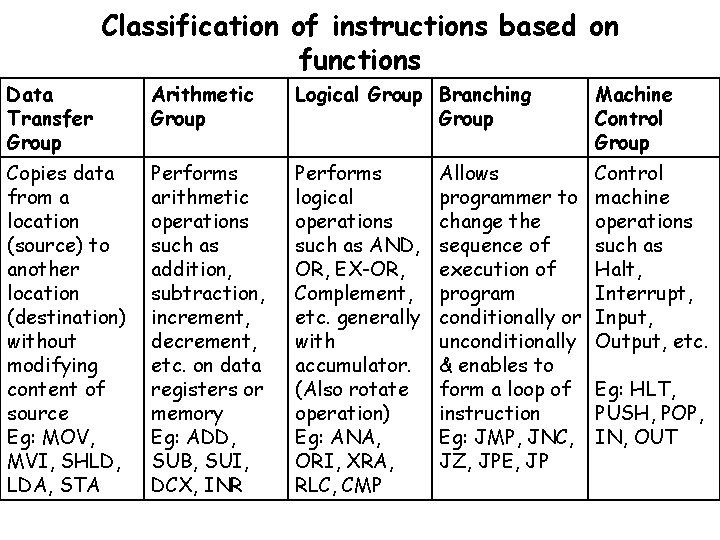

Classification of instructions based on functions Data Transfer Group Arithmetic Group Logical Group Branching Group Machine Control Group Copies data from a location (source) to another location (destination) without modifying content of source Eg: MOV, MVI, SHLD, LDA, STA Performs arithmetic operations such as addition, subtraction, increment, decrement, etc. on data registers or memory Eg: ADD, SUB, SUI, DCX, INR Performs logical operations such as AND, OR, EX-OR, Complement, etc. generally with accumulator. (Also rotate operation) Eg: ANA, ORI, XRA, RLC, CMP Control machine operations such as Halt, Interrupt, Input, Output, etc. Allows programmer to change the sequence of execution of program conditionally or unconditionally & enables to form a loop of instruction Eg: JMP, JNC, JZ, JPE, JP Eg: HLT, PUSH, POP, IN, OUT

![I Data Transfer Group 1 MOV rd rs MOVE REGISTER Format rd rs I] Data Transfer Group 1) MOV rd, rs : MOVE REGISTER Format: [rd] [rs]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-12.jpg)

I] Data Transfer Group 1) MOV rd, rs : MOVE REGISTER Format: [rd] [rs] Addressing: Register addressing Group: Data transfer group Bytes: 1 byte Flags: None This instruction will copy contents of source register to destination register without modifying content of source register. Example: Let [A] = 87 H & [C] = 55 H Instruction: MOV C, A (hence ‘A’ is rs & ‘C’ is rd) After execution: [A] = 87 H & [C] = 87 H

![I Data Transfer Group 2 MOV r M MOVE FROM MEMORY TO REGISTER I] Data Transfer Group 2) MOV r, M : MOVE FROM MEMORY TO REGISTER](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-13.jpg)

I] Data Transfer Group 2) MOV r, M : MOVE FROM MEMORY TO REGISTER Format: [r] [[H-L]] Addressing: Register indirect addressing Group: Data transfer group Bytes: 1 byte Flags: None This instruction will load destination register with content of memory location whose address is stored in HL register pair without modifying content of memory location. Example: Let [H-L] = C 050 H, [C 050] = 58 H & [B] = C 5 H Instruction: MOV B, M After execution: [B] = 58 H & [C 050] = 58 H

![I Data Transfer Group 3 MOV M r MOVE FROM REGISTER TO MEMORY I] Data Transfer Group 3) MOV M, r : MOVE FROM REGISTER TO MEMORY](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-14.jpg)

I] Data Transfer Group 3) MOV M, r : MOVE FROM REGISTER TO MEMORY Format: [[H-L]] [r] Addressing: Register indirect addressing Group: Data transfer group Bytes: 1 byte Flags: None This instruction will copy content of source register to the memory location whose address is stored in HL register pair without modifying content of source. Example: Let [H-L] = C 050 H, [C 050] = 58 H & [A] = C 5 H Instruction: MOV M, A After execution: [A] = C 5 H & [C 050] = C 5 H

![I Data Transfer Group 4 MVI r data MOVE IMMEDIATE 8 BIT DATA I] Data Transfer Group 4) MVI r, data : MOVE IMMEDIATE 8 -BIT DATA](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-15.jpg)

I] Data Transfer Group 4) MVI r, data : MOVE IMMEDIATE 8 -BIT DATA TO REGISTER Format: [r] data (2 nd byte) Addressing: Immediate addressing Group: Data transfer group Bytes: 2 byte Flags: None This instruction will load register r with 8 -bit immediate data specified in 2 nd byte of instruction. Example: Instruction: MVI C, 23 H After execution: [C] = 23 H

![I Data Transfer Group 5 MVI M data MOVE IMMEDIATE 8 BIT DATA I] Data Transfer Group 5) MVI M, data : MOVE IMMEDIATE 8 -BIT DATA](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-16.jpg)

I] Data Transfer Group 5) MVI M, data : MOVE IMMEDIATE 8 -BIT DATA TO MEMORY Format: [[H-L]] data (2 nd byte) Addressing: Immediate/ Register indirect addressing Group: Data transfer group Bytes: 2 byte Flags: None This instruction will load the memory location whose address is stored in HL register pair with 8 -bit immediate data specified in 2 nd byte of instruction. Example: Let [H] = C 0 H & [L] = 50 H i. e. , [H-L] = C 050 H Instruction: MVI M, 88 H After execution: [C 050] = 88 H

![I Data Transfer Group 6 LXI rp 16 bit data LOAD REGISTER PAIR I] Data Transfer Group 6) LXI rp, 16 -bit data : LOAD REGISTER PAIR](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-17.jpg)

I] Data Transfer Group 6) LXI rp, 16 -bit data : LOAD REGISTER PAIR IMMEDIATE Format: [rp] 16 -bit data i. e, . [rh] 3 rd byte, [rl] 2 nd byte Addressing: Immediate addressing Group: Data transfer group Bytes: 3 byte Flags: None This instruction will load the specified register pair with 16 -bit data specified in last 2 bytes of instruction. Byte 3 is moved into higher order register & byte 2 is moved into lower order register. Example: Instruction LXI B, D 500 H This instruction will load BC register pair with D 500 H. D 5 H will be in higher order register (B) & 00 H will be in lower order register (C) Instruction Byte 1 LXI B, D 500 H LXI B Byte 2 00 [C] Byte 3 D 5 [B]

![I Data Transfer Group 7 LDA address LOAD ACCUMULATOR DIRECT WITH DATA AT I] Data Transfer Group 7) LDA address : LOAD ACCUMULATOR DIRECT WITH DATA AT](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-18.jpg)

I] Data Transfer Group 7) LDA address : LOAD ACCUMULATOR DIRECT WITH DATA AT GIVEN ADDRESS Format: [A] [16 -bit address] i. e, . [A] [[byte 3][byte 2]] Addressing: Direct addressing Group: Data transfer group Bytes: 3 bytes Flags: None This instruction will load accumulator with content of memory location whose address is given in the last 2 bytes of instruction. Content of the memory location remains unchanged. Example: Let [9580] = 28 H & [A] = 55 H Instruction: LDA 9580 H After execution: [A] = 28 H [9580] = 28 H Instruction Byte 1 Byte 2 Byte 3 LDA 9580 H LDA 80 95

![I Data Transfer Group 8 STA address LOAD ACCUMULATOR DIRECT WITH DATA AT I] Data Transfer Group 8) STA address : LOAD ACCUMULATOR DIRECT WITH DATA AT](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-19.jpg)

I] Data Transfer Group 8) STA address : LOAD ACCUMULATOR DIRECT WITH DATA AT GIVEN ADDRESS Format: [16 -bit address] [A] i. e, . [[byte 3][byte 2]] [A] Addressing: Direct addressing Group: Data transfer group Bytes: 3 bytes Flags: None This instruction will store content of accumulator direct into the memory location whose address is given in the last 2 bytes of instruction. Content of accumulator remains unchanged Example: Let [C 050] = 28 H & [A] = 66 H Instruction: STA C 050 H After execution: [A] = 66 H [C 050] = 66 H Instruction Byte 1 Byte 2 Byte 3 STA C 050 H STA 50 C 0

![I Data Transfer Group 9 LHLD address LOAD H L REGISTER DIRECT I] Data Transfer Group 9) LHLD address : LOAD H & L REGISTER DIRECT](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-20.jpg)

I] Data Transfer Group 9) LHLD address : LOAD H & L REGISTER DIRECT Format: [L] [16 -bit addr] i. e. , [L] [[byte 3][byte 2]] [H] [16 -bit addr +1] i. e. , [H] [[byte 3][byte 2]+1] Addressing: Direct addressing Group: Data transfer group Bytes: 3 bytes Flags: None 1 st byte is opcode, 2 nd & 3 rd byte give 16 -bit address of memory location. The content of memory location whose address is given in the last 2 bytes of instruction is loaded into register L & the content of next memory location is loaded into register H. Example: Let [C 050] = 28 H & [C 051] = 66 H Instruction: LHLD C 050 H After execution: [H] = 66 H & [L] = 28 H Instruction Byte 1 LHLD C 050 H LHLD Byte 2 Byte 3 50 C 0

![I Data Transfer Group 10 SHLD address STORE H L REGISTER DIRECT I] Data Transfer Group 10) SHLD address : STORE H & L REGISTER DIRECT](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-21.jpg)

I] Data Transfer Group 10) SHLD address : STORE H & L REGISTER DIRECT Format: [16 -bit addr] [L] i. e. , [[byte 3][byte 2]] [L] [16 -bit addr +1] [H] i. e. , [[byte 3][byte 2]+1] [H] Addressing: Direct addressing Group: Data transfer group Bytes: 3 bytes Flags: None 1 st byte is opcode, 2 nd & 3 rd byte give 16 -bit address of memory location. The content of register L is stored into the memory location whose address is given in the last 2 bytes of instruction & the content of register H is stored into the next memory location. Example: Let [H] = 34 H & [L] = 89 H Instruction: SHLD C 050 H After execution: [C 050] = 89 H & [C 051] = 34 H Instruction Byte 1 SHLD C 050 H SHLD Byte 2 Byte 3 50 C 0

![I Data Transfer Group 11 LDAX rp LOAD ACCUMULATOR INDIRECT Format A rp I] Data Transfer Group 11) LDAX rp : LOAD ACCUMULATOR INDIRECT Format: [A] [[rp]]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-22.jpg)

I] Data Transfer Group 11) LDAX rp : LOAD ACCUMULATOR INDIRECT Format: [A] [[rp]] Addressing: Register Indirect addressing Group: Data transfer group Bytes: 1 byte Flags: None The content of memory location whose address is stored in register pair specified in instruction is loaded into accumulator. The content of memory location remains unchanged. Here rp can be B (B-C pair) or D (D -E pair). Example: Let [B] = 35 H & [C] = 45 H & [3545] = 22 H Instruction: LDAX B After execution: [A] = 22 H & [3545] = 22 H

![I Data Transfer Group 12 STAX rp STORE ACCUMULATOR INDIRECT Format rp A I] Data Transfer Group 12) STAX rp : STORE ACCUMULATOR INDIRECT Format: [[rp]] [A]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-23.jpg)

I] Data Transfer Group 12) STAX rp : STORE ACCUMULATOR INDIRECT Format: [[rp]] [A] Addressing: Register Indirect addressing Group: Data transfer group Bytes: 1 byte Flags: None The content of accumulator is stored into the memory location whose address is stored in register pair specified in instruction. The content of accumulator remains unchanged. Here rp can be B (B-C pair) or D (D -E pair). Example: Let [A] = 88 H, [D] = 35 H, [E] = 45 H & [3545] = 22 H Instruction: STAX D After execution: [A] = 88 H & [3545] = 88 H

![I Data Transfer Group 13 XCHG EXCHANGE H L WITH D I] Data Transfer Group 13) XCHG : EXCHANGE H & L WITH D &](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-24.jpg)

I] Data Transfer Group 13) XCHG : EXCHANGE H & L WITH D & E Format: [H] [D] [L] [E] Addressing: Register addressing Group: Data transfer group Bytes: 1 byte Flags: None The content of register H is exchanged with that of register D & the content of register L is exchanged with that of register E. Example: Let [H] = 28 H, [L] = 35 H, [D] = 45 H & [E] = 22 H Instruction: XCHG After execution: [H] = 45 H & [L] = 22 H [D] = 28 H & [E] = 35 H

![II Arithmetic Group 1 ADD r ADD REGISTER Format A r Addressing II] Arithmetic Group 1) ADD r : ADD REGISTER Format: [A] + [r] Addressing:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-25.jpg)

II] Arithmetic Group 1) ADD r : ADD REGISTER Format: [A] + [r] Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: All The content of register r is added to the content of accumulator. The result is stored in accumulator. All flags may be affected Example: Let [C] = 27 H & [A] = 15 H Instruction: ADD C Addition: 27 H = 0 0 1 1 1 +15 H = 0 0 0 1 0 1 ------------3 C H = 0 0 1 1 0 0 S = 0, Z = 0, Ac = 0 P = 1, Cy = 0 After execution: [A] = 3 C H [C] = 27 Flag register - 0 0 0 1 0

![II Arithmetic Group 2 ADD M ADD MEMORY CONTENT TO ACCUMULATOR Format A II] Arithmetic Group 2) ADD M : ADD MEMORY CONTENT TO ACCUMULATOR Format: [A]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-26.jpg)

II] Arithmetic Group 2) ADD M : ADD MEMORY CONTENT TO ACCUMULATOR Format: [A] + [[H] [L]] Addressing: Register Indirect addressing Group: Arithmetic group Bytes: 1 byte Flags: All The content of accumulator is added to the content of memory location, whose address is stored in HL register pair. The result is stored in accumulator. All flags may be affected Example: Let [HL] = C 000 H & [C 000] = 15 H & [A] =30 H Instruction: ADD M Addition: 15 H = 0 0 0 1 0 1 +30 H = 0 0 1 1 0 0 ------------45 H = 0 1 0 0 0 1 S = 0, Z = 0, Ac = 0 P = 0, Cy = 0 After execution: [A] = 45 H [C 000] = 15 H Flag register - 0 0 0

![II Arithmetic Group 3 ADI data ADD IMMEDIATE TO ACCUMULATOR Format A II] Arithmetic Group 3) ADI data : ADD IMMEDIATE TO ACCUMULATOR Format: [A] +](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-27.jpg)

II] Arithmetic Group 3) ADI data : ADD IMMEDIATE TO ACCUMULATOR Format: [A] + data (BYTE 2) Addressing: Immediate addressing Group: Arithmetic group Bytes: 2 bytes Flags: All The 8 -bit immediate data specified in 2 nd byte instruction is added to the content accumulator. The result is stored in accumulator. All flags may be affected Example: Let [A] = 8 A H Instruction: ADI 28 H Addition: 8 AH = 1 0 0 0 1 0 + 28 H = 0 0 1 0 0 0 ------------B 2 H = 1 0 1 1 0 0 1 0 S = 1, Z = 0, Ac = 1 P = 1, Cy = 0 After execution: [A] = B 2 H Flag register - 1 0 1 1 0

![II Arithmetic Group 4 ADC r ADD REGISTER TO ACCUMULATOR WITH CARRY Format II] Arithmetic Group 4) ADC r : ADD REGISTER TO ACCUMULATOR WITH CARRY Format:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-28.jpg)

II] Arithmetic Group 4) ADC r : ADD REGISTER TO ACCUMULATOR WITH CARRY Format: [A] + [r] + [Cy] Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: All The content of accumulator is added to the content of register & the content of the carry flag. The result is stored in accumulator. All flags may be affected Example: Let [A] = 4 C H & [B] = 25 H & [Cy] =01 H Instruction: ADC B Addition: [A] : 4 CH = 0 1 0 0 1 1 0 0 [B] : +25 H = 0 0 1 0 1 [Cy] : +01 H = 0 0 0 0 1 -----------------After execution: [A] = 72 H = 0 1 1 1 0 0 1 0 S = 0, Z = 0, Ac = 1 P = 1, Cy = 0 Flag register - 0 0 1 1 0

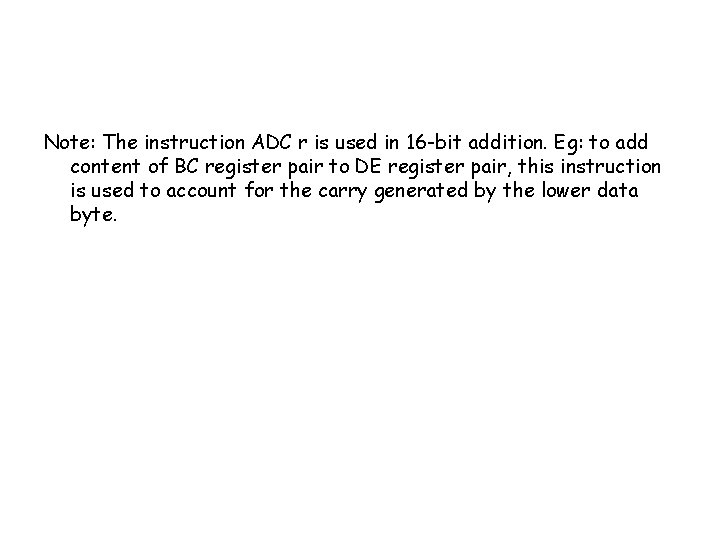

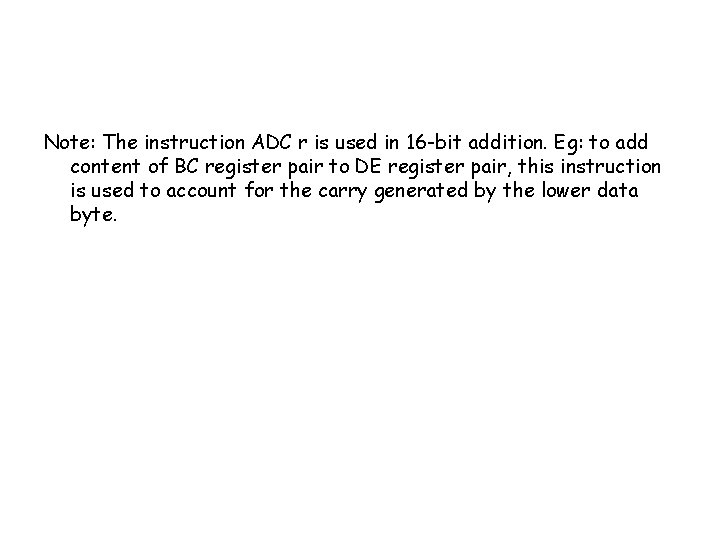

Note: The instruction ADC r is used in 16 -bit addition. Eg: to add content of BC register pair to DE register pair, this instruction is used to account for the carry generated by the lower data byte.

![II Arithmetic Group 5 ADC M ADD MEMORY CONTENT TO ACCUMULATOR WITH CARRY II] Arithmetic Group 5) ADC M : ADD MEMORY CONTENT TO ACCUMULATOR WITH CARRY](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-30.jpg)

II] Arithmetic Group 5) ADC M : ADD MEMORY CONTENT TO ACCUMULATOR WITH CARRY Format: [A] + [[H-L]] + [Cy] Addressing: Register Indirect addressing Group: Arithmetic group Bytes: 1 byte Flags: All The content of memory location whose address is stored in HL register pair is added to the content of accumulator & the content of the carry flag. The result is stored in accumulator. All flags may be affected Example: Let [A] = 2 B H, [HL] = C 050 H, [C 050] = 58 H & [Cy] =00 H Instruction: ADC M Addition: [A] : 2 BH = 0 0 1 0 1 1 [B] : +58 H = 0 1 1 0 0 0 [Cy] : +00 H = 0 0 0 0 -----------------After execution: [A] = 83 H = 1 0 0 0 1 1 S = 1, Z = 0, Ac = 1 P = 0, Cy = 0 Flag register 1 0 0

![II Arithmetic Group 6 ACI data ADD IMMEDIATE TO ACCUMULATOR WITH CARRY Format II] Arithmetic Group 6) ACI data : ADD IMMEDIATE TO ACCUMULATOR WITH CARRY Format:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-31.jpg)

II] Arithmetic Group 6) ACI data : ADD IMMEDIATE TO ACCUMULATOR WITH CARRY Format: [A] + data + [Cy] Addressing: Immediate addressing Group: Arithmetic group Bytes: 2 bytes Flags: All The 8 -bit immediate data specified in 2 nd byte instruction is added to the content accumulator & to the contents of carry flag. The result is stored in accumulator. All flags may be affected Example: Let [A] = 8 A H & [Cy] = 01 H Instruction: ACI 28 H Addition: 8 AH = 1 0 0 0 1 0 +28 H = 0 0 1 0 0 0 +00 H = 0 0 0 0 ------------B 2 H = 1 0 1 1 0 0 1 0 S = 1, Z = 0, Ac = 1 P = 1, Cy = 0 After execution: [A] = B 2 H Flag register - 1 0 1 1 0

![II Arithmetic Group 7 SUB r SUBTRACT REGISTER FROM ACCUMULATOR Format A II] Arithmetic Group 7) SUB r : SUBTRACT REGISTER FROM ACCUMULATOR Format: [A] -](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-32.jpg)

II] Arithmetic Group 7) SUB r : SUBTRACT REGISTER FROM ACCUMULATOR Format: [A] - [r] Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: All The content of register r is subtracted from the content of accumulator. The result is placed in accumulator. All flags may be affected Example: Let [B] = 27 H & [A] = 15 H Instruction: SUB B …………. . i. e, . [A] – [B] Subtraction: [B] : 27 H = 0 0 1 1 1 2’s complement = 1101 1001 +[A] : +15 H = 0 0 0 1 0 1 ------------------S = 1, Z = 0, Ac = 0 /1 1 1 0 0 + 1 Complement carry : / 1 1 1 0 After execution: 1[A] =0 EE -H 0[C] =- 27 1 Flag register – P = 1, Cy = 1 - 0 The result as a negative number will be in 2’s complement & Carry (Borrow) flag is set

![II Arithmetic Group 8 SUB M SUBTRACT MEMORY FROM ACCUMULATOR Format A II] Arithmetic Group 8) SUB M : SUBTRACT MEMORY FROM ACCUMULATOR Format: [A] -](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-33.jpg)

II] Arithmetic Group 8) SUB M : SUBTRACT MEMORY FROM ACCUMULATOR Format: [A] - [[H-L]] Addressing: Register Indirect addressing Group: Arithmetic group Bytes: 1 byte Flags: All The content of memory location whose address is stored in HL register pair is subtracted from the content of accumulator. The result is placed in accumulator. All flags may be affected Example: Let [H-L] = F 000 H & [F 000] = 02 H & [A] = 05 H Instruction: SUB M Subtraction: [A] – [[H-L]] = [A] – [F 000] = 05 H – 02 H = 03 H After execution: [A] = 03 H

![II Arithmetic Group 9 SUI data SUBTRACT IMMEDIATE FROM ACCUMULATOR Format A II] Arithmetic Group 9) SUI data : SUBTRACT IMMEDIATE FROM ACCUMULATOR Format: [A] –](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-34.jpg)

II] Arithmetic Group 9) SUI data : SUBTRACT IMMEDIATE FROM ACCUMULATOR Format: [A] – data (byte 2) Addressing: Immediate addressing Group: Arithmetic group Bytes: 2 byte Flags: All The 8 -bit immediate data specified in 2 nd byte of instruction is subtracted from the content of accumulator. The result is placed in accumulator. All flags may be affected Example: Let [A] = 22 H Instruction: SUI 10 H After execution: [A] = 12 H

![II Arithmetic Group 10 SBB r SUBTRACT REGISTER BORROW FROM ACCUMULATOR Format II] Arithmetic Group 10) SBB r : SUBTRACT REGISTER & BORROW FROM ACCUMULATOR Format:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-35.jpg)

II] Arithmetic Group 10) SBB r : SUBTRACT REGISTER & BORROW FROM ACCUMULATOR Format: [A] - [r] - [Cy] Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: All The content of register r & carry flag is subtracted from the content of accumulator. The result is placed in accumulator. All flags may be affected Example: Let [A] = 3 AH & [C] = 15 H & [Cy] = 01 H Instruction: SBB C Subtraction: [C] : 15 H = 0 0 0 1 0 1 Borrow : +01 H = 0 0 0 0 1 ------------------0001 0110 + 2’s complement = 1110 1010 +3 A H = 0 0 1 1 1 0 -----------1 /0010 0100 complement carry : Cy flag is RESET After execution: [A] = 24 H

![II Arithmetic Group 11 SBB M SUBTRACT MEMORY CONTENT TO ACCUMULATOR WITH CARRY II] Arithmetic Group 11) SBB M : SUBTRACT MEMORY CONTENT TO ACCUMULATOR WITH CARRY](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-36.jpg)

II] Arithmetic Group 11) SBB M : SUBTRACT MEMORY CONTENT TO ACCUMULATOR WITH CARRY Format: [A] - [[H-L]] - [Cy] Addressing: Register Indirect addressing Group: Arithmetic group Bytes: 1 byte Flags: All The content of memory location whose address is stored in HL register pair is subtracted along with carry bit from the content of accumulator. The result is placed in accumulator. All flags may be affected Example: Let [A] = 2 C H, [HL] = C 050 H, [C 050] = 28 H & [Cy] =00 H Instruction: SBB M After execution: [A] = 04 H = 0 0 0 1 0 0 S = 0, Z = 0, Ac = 0 P = 0, Cy = 0 Flag register 0 0 - 0

![II Arithmetic Group 12 SBI data SUBTRCT IMMEDIATE WITH BORROW Format Addressing Group II] Arithmetic Group 12) SBI data : SUBTRCT IMMEDIATE WITH BORROW Format: Addressing: Group:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-37.jpg)

II] Arithmetic Group 12) SBI data : SUBTRCT IMMEDIATE WITH BORROW Format: Addressing: Group: Bytes: Flags: [A] - data - [Cy] Immediate addressing Arithmetic group 2 bytes All The 8 -bit immediate data specified in 2 nd byte instruction is subtracted along with the carry bit from the content accumulator. The result is placed in accumulator. All flags may be affected Example: Let [A] = 29 H & [Cy] = 01 H Instruction: SBI 28 H After execution: [A] = 00 H

![II Arithmetic Group 13 INR r INCREMENT REGISTER CONTENT BY 1 Format r II] Arithmetic Group 13) INR r : INCREMENT REGISTER CONTENT BY 1 Format: [r]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-38.jpg)

II] Arithmetic Group 13) INR r : INCREMENT REGISTER CONTENT BY 1 Format: [r] + 1 Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: S, Z, P, Ac The content of register r is incremented by 1 & the result is placed in the same register. All flags except carry flag may be affected. Here r can be A, B, C, D, E, H & L Example: Let [C] = FF H Instruction: INR C After execution: [C] = 00 H

![II Arithmetic Group 14 INR M INCREMENT MEMORY CONTENT BY 1 Format H II] Arithmetic Group 14) INR M : INCREMENT MEMORY CONTENT BY 1 Format: [[H]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-39.jpg)

II] Arithmetic Group 14) INR M : INCREMENT MEMORY CONTENT BY 1 Format: [[H] [L]] + 1 Addressing: Register Indirect addressing Group: Arithmetic group Bytes: 1 byte Flags: S, Z, P, Ac The content of memory location whose address is stored in H-L register pair is incremented by 1 & the result is placed in the same place. All flags except carry flag may be affected. Example: Let [H-L] = F 050 H Instruction: INR M & After execution: [F 050] = 06 H [F 050] = 05 H

![II Arithmetic Group 15 INX rp INCREMENT REGISTER PAIR BY 1 Format rp II] Arithmetic Group 15) INX rp : INCREMENT REGISTER PAIR BY 1 Format: [rp]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-40.jpg)

II] Arithmetic Group 15) INX rp : INCREMENT REGISTER PAIR BY 1 Format: [rp] + 1 Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: None The content of register pair is incremented by 1. No flags are affected. This instruction views the content of register pair as 16 -bit data. Example: Let [H-L] = F 050 H Instruction: INX H After execution: [H-L] = F 051 H

![II Arithmetic Group 16 DCR r DECREMENT REGISTER CONTENT BY 1 Format r II] Arithmetic Group 16) DCR r : DECREMENT REGISTER CONTENT BY 1 Format: [r]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-41.jpg)

II] Arithmetic Group 16) DCR r : DECREMENT REGISTER CONTENT BY 1 Format: [r] - 1 Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: S, Z, P, Ac The content of register r is decremented by 1 & the result is placed in the same register. All flags except carry flag may be affected. Here r can be A, B, C, D, E, H & L Example: Let [C] = FF H Instruction: DCR C After execution: [C] = FE H

![II Arithmetic Group 17 DCR M DECREMENT MEMORY CONTENT BY 1 Format H II] Arithmetic Group 17) DCR M : DECREMENT MEMORY CONTENT BY 1 Format: [[H]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-42.jpg)

II] Arithmetic Group 17) DCR M : DECREMENT MEMORY CONTENT BY 1 Format: [[H] [L]] - 1 Addressing: Register Indirect addressing Group: Arithmetic group Bytes: 1 byte Flags: S, Z, P, Ac The content of memory location whose address is stored in H-L register pair is decremented by 1 & the result is placed in the same place. All flags except carry flag may be affected. Example: Let [H-L] = F 050 H Instruction: DCR M & After execution: [F 050] = 04 H [F 050] = 05 H

![II Arithmetic Group 18 DCX rp DECREMENT REGISTER PAIR BY 1 Format rp II] Arithmetic Group 18) DCX rp : DECREMENT REGISTER PAIR BY 1 Format: [rp]](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-43.jpg)

II] Arithmetic Group 18) DCX rp : DECREMENT REGISTER PAIR BY 1 Format: [rp] - 1 Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: None The content of register pair is decremented by 1. No flags are affected. This instruction views the content of register pair as 16 -bit data. Example: Let [H-L] = F 050 H Instruction: INX H After execution: [H-L] = F 04 F H

![II Arithmetic Group 19 DAD rp ADD REGISTER PAIR TO HL REGISTER Format II] Arithmetic Group 19) DAD rp : ADD REGISTER PAIR TO H-L REGISTER Format:](https://slidetodoc.com/presentation_image_h2/c952d67060a5957f5710333275b4967f/image-44.jpg)

II] Arithmetic Group 19) DAD rp : ADD REGISTER PAIR TO H-L REGISTER Format: [H][L] + [rh] [rl] Addressing: Register addressing Group: Arithmetic group Bytes: 1 byte Flags: Cy The content of register pair rp is added to the content of H-L register pair. The result is placed in H-L register pair. Only carry flag may be affected. Example: Let [H] = F 050 H Instruction: INX H After execution: [H-L] = F 051 H