Instruction Set Architecture 1 CHAPTER 6 1222022 Topics

![C language to Memory instructions 11 g = h + A[8] Compile • lw C language to Memory instructions 11 g = h + A[8] Compile • lw](https://slidetodoc.com/presentation_image_h2/8734b7f3c32df257ee51ff661901ed6f/image-11.jpg)

![Instructions for Iteration (while) while (save[i] == k) i = i + 1; Let Instructions for Iteration (while) while (save[i] == k) i = i + 1; Let](https://slidetodoc.com/presentation_image_h2/8734b7f3c32df257ee51ff661901ed6f/image-17.jpg)

- Slides: 20

Instruction Set Architecture 1 CHAPTER 6 1/22/2022

Topics for Discussion 2 Instruction set architecture Stored program computer Interface between software and hardware Instructions Design principles Instructions, registers, and memory Simple instructions types and formats 1/22/2022

Where do you go from here (CSE 241): Computer Organization 3 Is the study of major components of a modern digital computer, their organization and assembly, and the architecture and inner workings of these components. It also deals with design principles for a good performance. 1/22/2022

Mother Board 4 Contains packages of integrated circuit chips (IC chips) including a processor, cache (several), memory (DRAM), connections for IO devices (networks, disks) 1/22/2022

Central Processing Unit (CPU) 5 Example: Intel 80386 80486 Pentium Main components of a CPU are datapath and control unit Datapath is the component of the processor that performs (arithmetic) operations Control is the component of the processor that commands the datapath, memory , IO device according to instruction of the program Cache provides but fast memory that acts as a buffer for slower /larger memory outside the chip. 1/22/2022

Instruction set Architecture 6 An important abstraction between hardware and software. Lets discuss this concept. Computer operation is historically called an instruction. Instructions stored similar to data in a memory give rise to an important foundational concept called the stored program computer. Lets look at MIPS: Microprocessor without Interlocked Pipelined Stages 1/22/2022

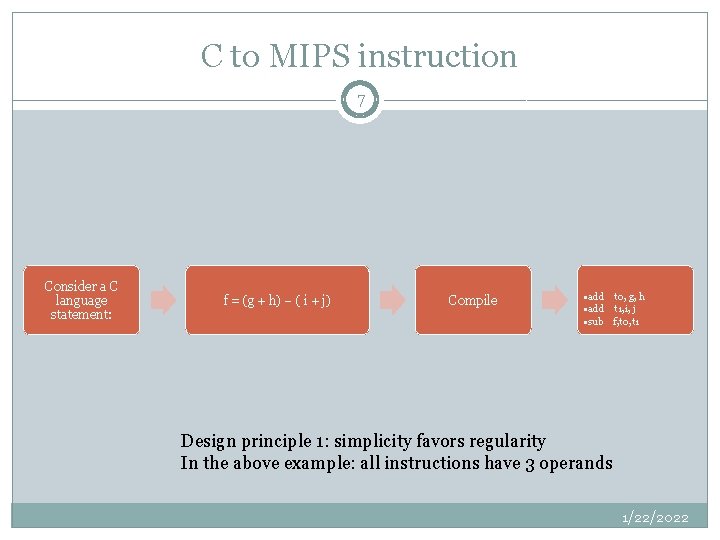

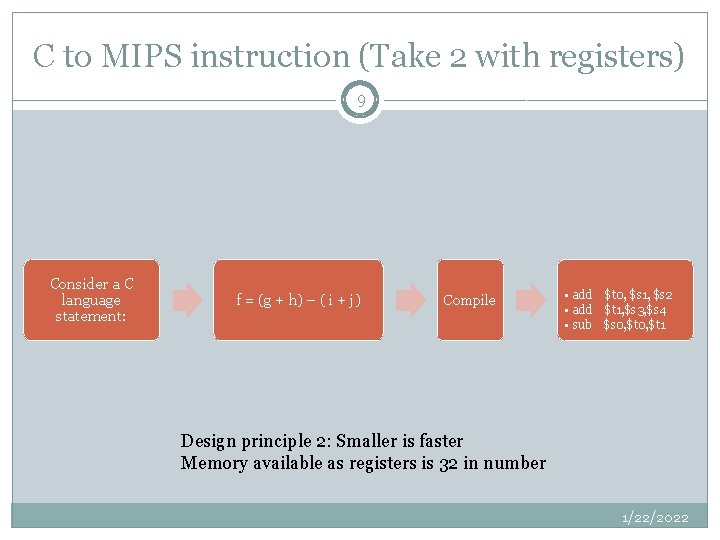

C to MIPS instruction 7 Consider a C language statement: f = (g + h) – ( i + j) Compile • add t 0, g, h • add t 1, i, j • sub f, t 0, t 1 Design principle 1: simplicity favors regularity In the above example: all instructions have 3 operands 1/22/2022

Register set 8 Where do the data get stored in the CPU? Named locations called registers? How many? Typical small compared to memory sizes. Registers: MIPS-32 has 32 register Denoted by s 0, s 1, etc. $s 0, $s 5 Temporary registers are denoted by $t 0, $t 1 1/22/2022

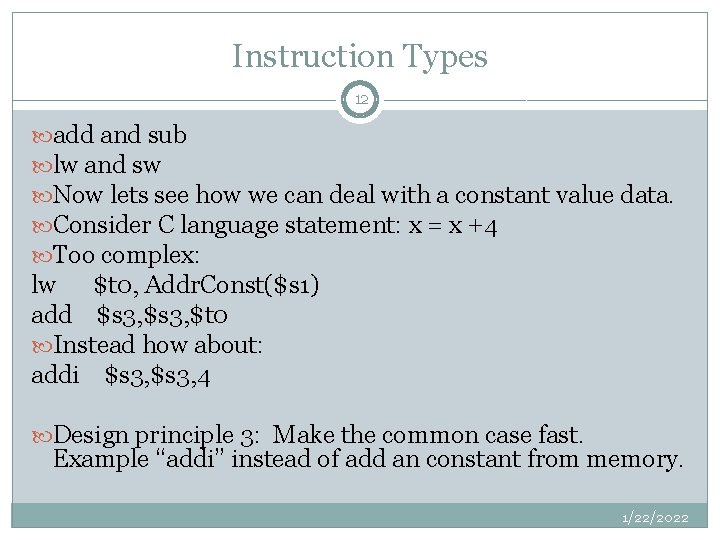

C to MIPS instruction (Take 2 with registers) 9 Consider a C language statement: f = (g + h) – ( i + j) Compile • add $t 0, $s 1, $s 2 • add $t 1, $s 3, $s 4 • sub $s 0, $t 1 Design principle 2: Smaller is faster Memory available as registers is 32 in number 1/22/2022

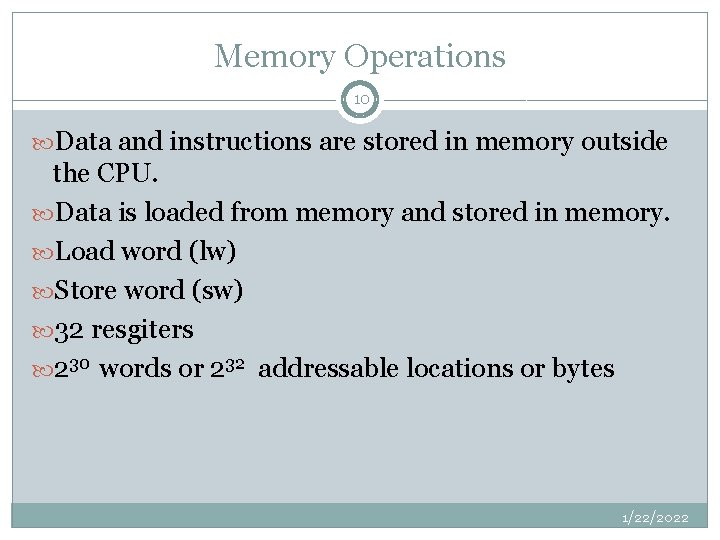

Memory Operations 10 Data and instructions are stored in memory outside the CPU. Data is loaded from memory and stored in memory. Load word (lw) Store word (sw) 32 resgiters 230 words or 232 addressable locations or bytes 1/22/2022

![C language to Memory instructions 11 g h A8 Compile lw C language to Memory instructions 11 g = h + A[8] Compile • lw](https://slidetodoc.com/presentation_image_h2/8734b7f3c32df257ee51ff661901ed6f/image-11.jpg)

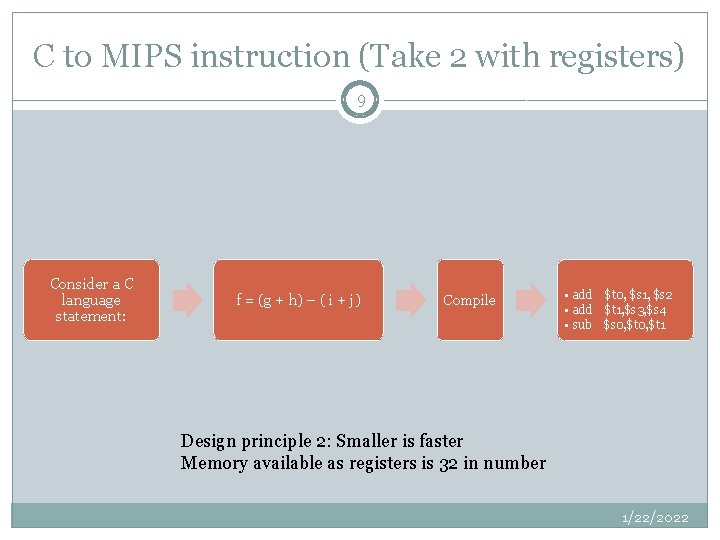

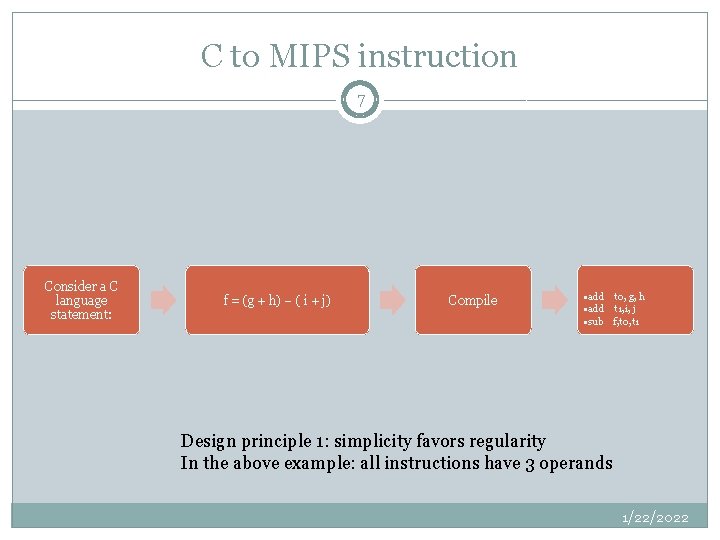

C language to Memory instructions 11 g = h + A[8] Compile • lw $t 0, 32($s 3) • add $s 1, $s 2, $t 0 • sw $t 0, 48($s 3) Base register concept: base register is $s 3 and Offset of 32 for 8 words and offset of 48 for 12 words 1/22/2022

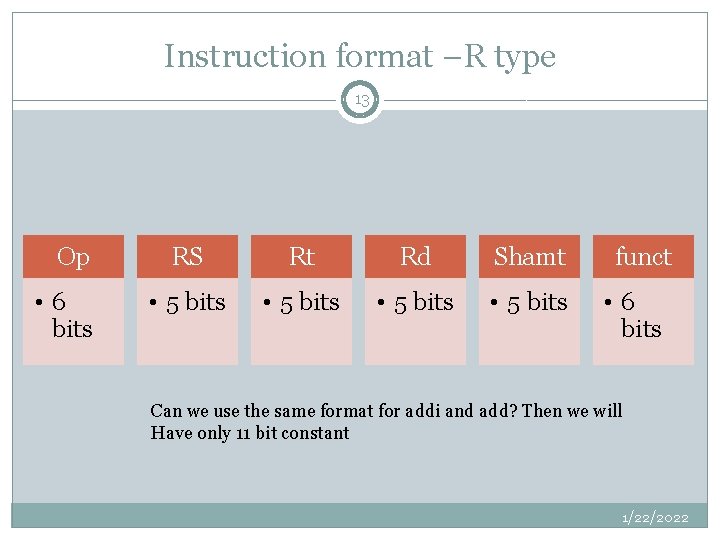

Instruction Types 12 add and sub lw and sw Now lets see how we can deal with a constant value data. Consider C language statement: x = x +4 Too complex: lw $t 0, Addr. Const($s 1) add $s 3, $t 0 Instead how about: addi $s 3, 4 Design principle 3: Make the common case fast. Example “addi” instead of add an constant from memory. 1/22/2022

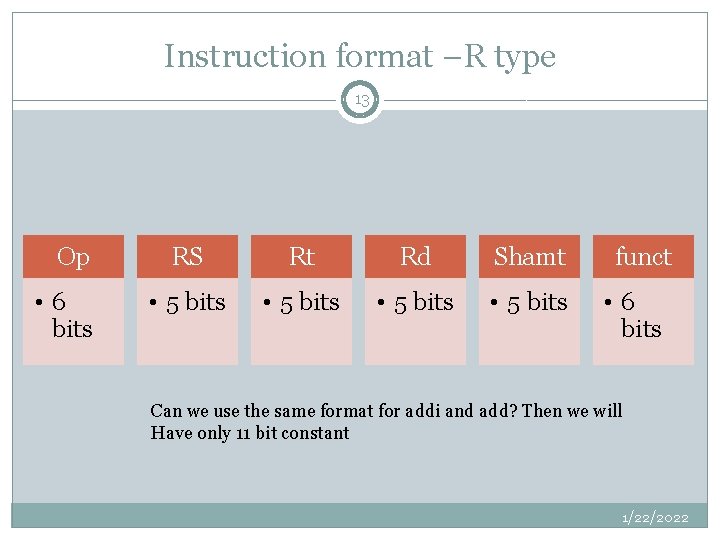

Instruction format –R type 13 Op • 6 bits RS Rt Rd Shamt • 5 bits funct • 6 bits Can we use the same format for addi and add? Then we will Have only 11 bit constant 1/22/2022

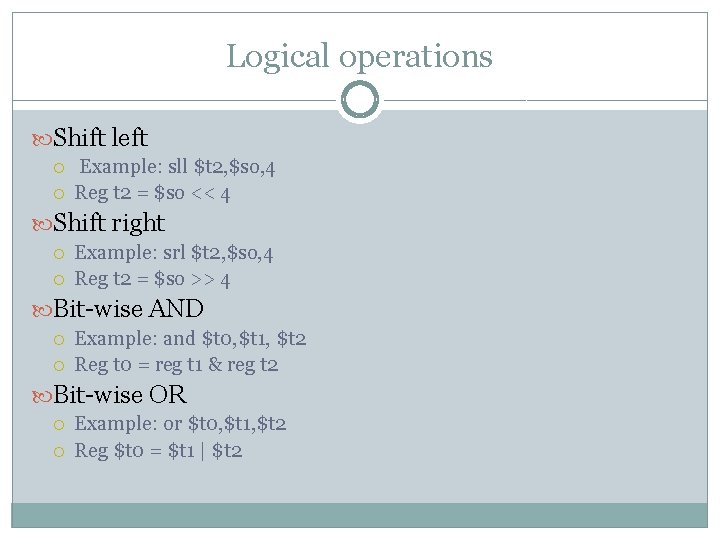

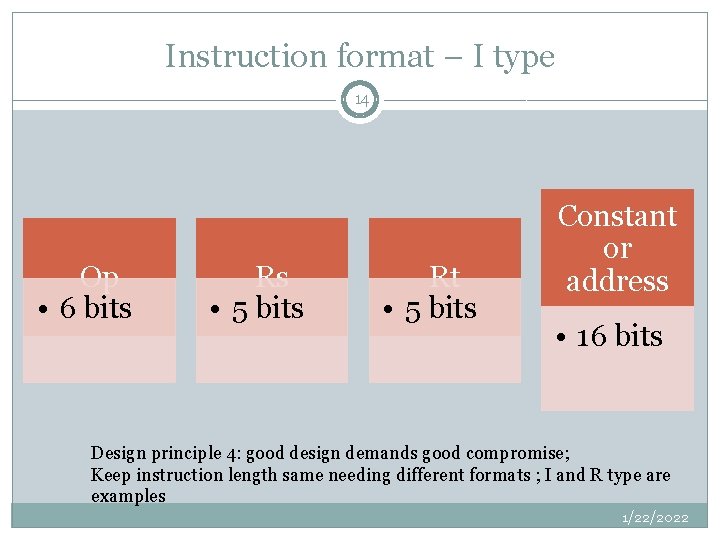

Instruction format – I type 14 Op • 6 bits Rs • 5 bits Rt • 5 bits Constant or address • 16 bits Design principle 4: good design demands good compromise; Keep instruction length same needing different formats ; I and R type are examples 1/22/2022

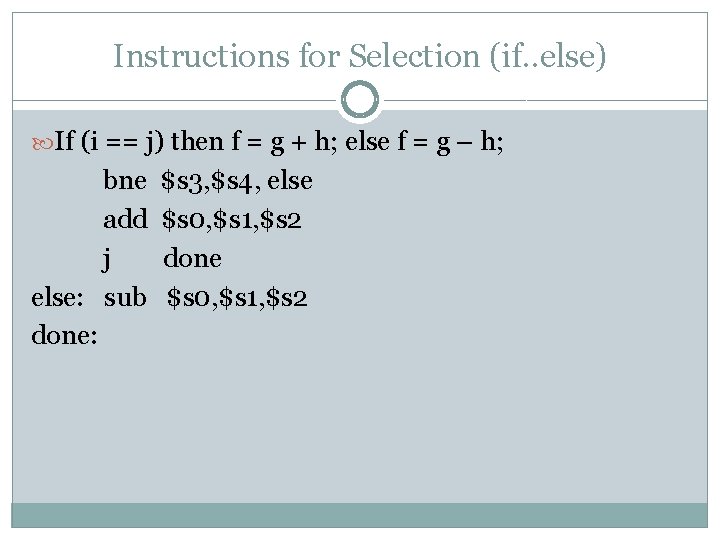

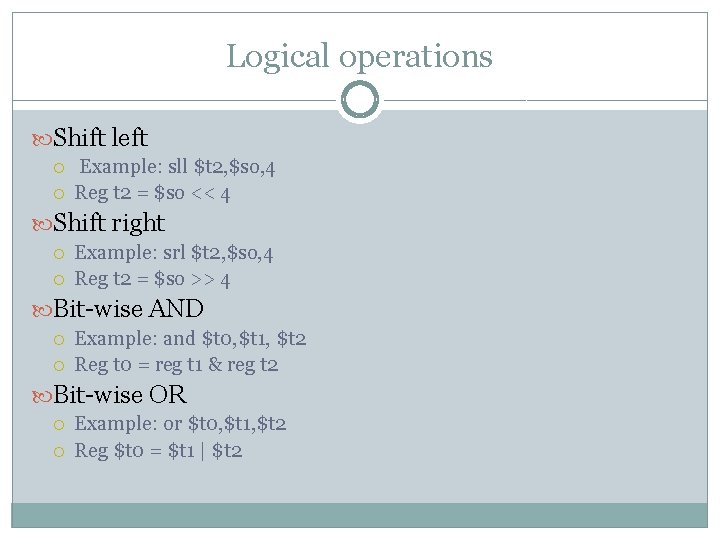

Logical operations Shift left Example: sll $t 2, $so, 4 Reg t 2 = $so << 4 Shift right Example: srl $t 2, $so, 4 Reg t 2 = $so >> 4 Bit-wise AND Example: and $t 0, $t 1, $t 2 Reg t 0 = reg t 1 & reg t 2 Bit-wise OR Example: or $t 0, $t 1, $t 2 Reg $t 0 = $t 1 | $t 2

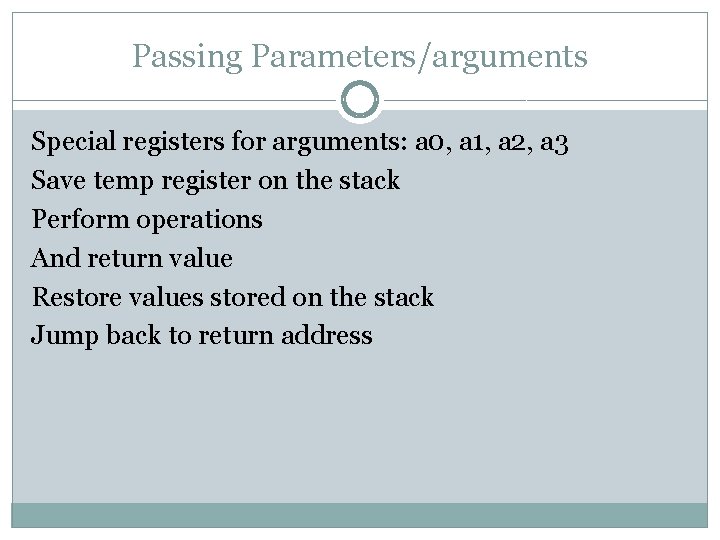

Instructions for Selection (if. . else) If (i == j) then f = g + h; else f = g – h; bne add j else: sub done: $s 3, $s 4, else $s 0, $s 1, $s 2 done $s 0, $s 1, $s 2

![Instructions for Iteration while while savei k i i 1 Let Instructions for Iteration (while) while (save[i] == k) i = i + 1; Let](https://slidetodoc.com/presentation_image_h2/8734b7f3c32df257ee51ff661901ed6f/image-17.jpg)

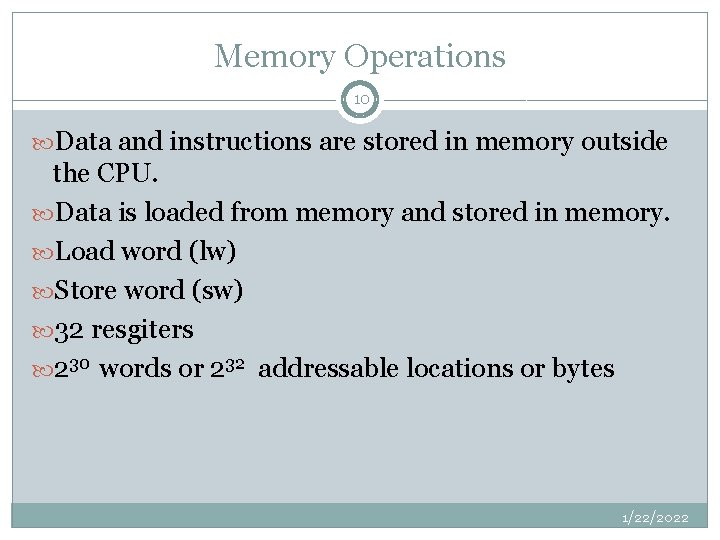

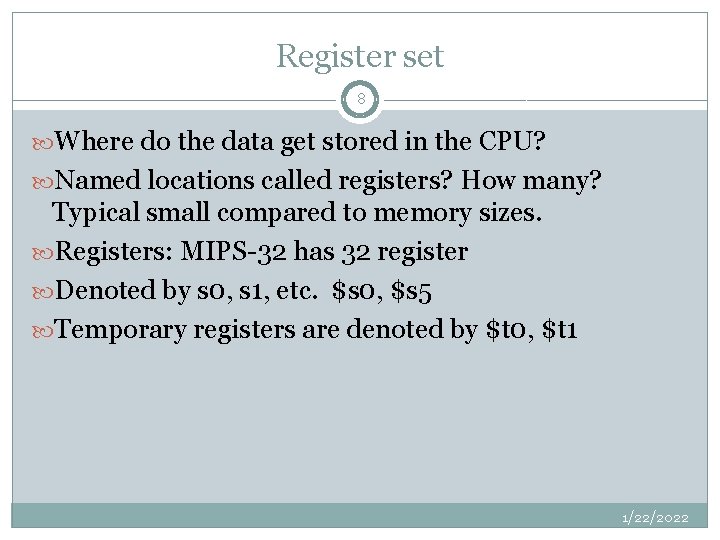

Instructions for Iteration (while) while (save[i] == k) i = i + 1; Let i be in reg $s 3 Let k be in reg $s 5 Let $t 1 have the address of Save array element Loop: sll $t 1, $s 3, 2 add $t 1, $t 1$s 6 lw $t 0, 0($t 1) bne $t 0, $s 5, Exit addi $s 3, 1 j Loop

Compiling C procedures int leaf_example (int g, int h, int i, int j) { int f; f = (g + h) – (i + j); return f; } How do you pass the parameters? How does compiler transport the parameters?

Passing Parameters/arguments Special registers for arguments: a 0, a 1, a 2, a 3 Save temp register on the stack Perform operations And return value Restore values stored on the stack Jump back to return address

Summary 20 MIPS operands MIPS memory MIPS Assembly language MIPS instructions type and formats And of course, the four design principles. 1/22/2022