INSTITUTE OF HIGH ENERGY PHYSICS CAS A BunchbyBunch

中国科学院高能物理研究所 INSTITUTE OF HIGH ENERGY PHYSICS, CAS A Bunch-by-Bunch Beam Position Monitor Fang Liu Institute of High Energy Physics, Chinese Academy of Sciences 2019 -6 -5 © 2019 BI Group, Acc-Center, IHEP 1

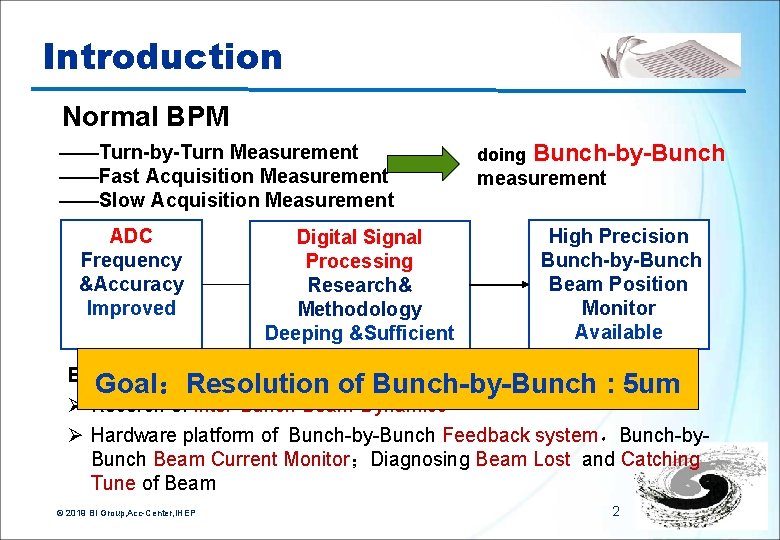

Introduction Normal BPM ——Turn-by-Turn Measurement ——Fast Acquisition Measurement ——Slow Acquisition Measurement ADC Frequency &Accuracy Improved Digital Signal Processing Research& Methodology Deeping &Sufficient doing Bunch-by-Bunch measurement High Precision Bunch-by-Bunch Beam Position Monitor Available Based Research Goal:Resolution of Bunch-by-Bunch Ø Reserch of Inter-Bunch Beam Dynamics : 5 um Ø Hardware platform of Bunch-by-Bunch Feedback system,Bunch-by. Bunch Beam Current Monitor;Diagnosing Beam Lost and Catching Tune of Beam © 2019 BI Group, Acc-Center, IHEP 2

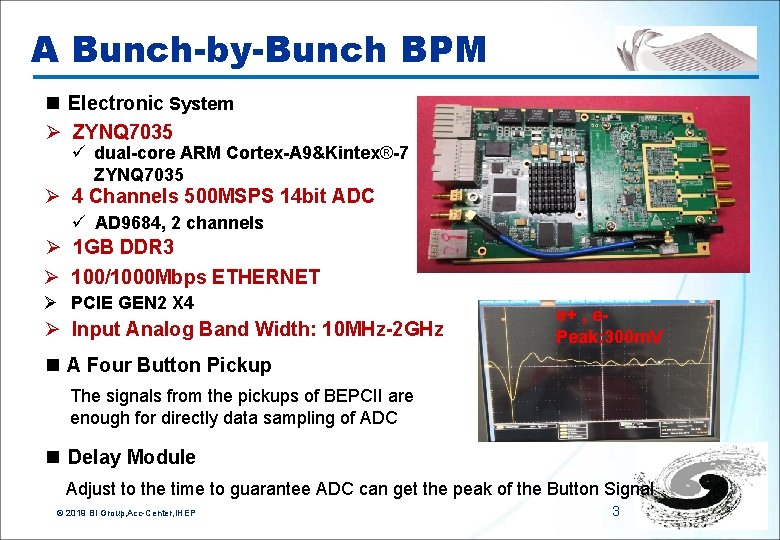

A Bunch-by-Bunch BPM n Electronic System Ø ZYNQ 7035 ü dual-core ARM Cortex-A 9&Kintex®-7 ZYNQ 7035 Ø 4 Channels 500 MSPS 14 bit ADC ü AD 9684, 2 channels Ø 1 GB DDR 3 Ø 100/1000 Mbps ETHERNET Ø PCIE GEN 2 X 4 Ø Input Analog Band Width: 10 MHz-2 GHz e+ , e. Peak: 300 m. V n A Four Button Pickup The signals from the pickups of BEPCII are enough for directly data sampling of ADC n Delay Module Adjust to the time to guarantee ADC can get the peak of the Button Signal © 2019 BI Group, Acc-Center, IHEP 3

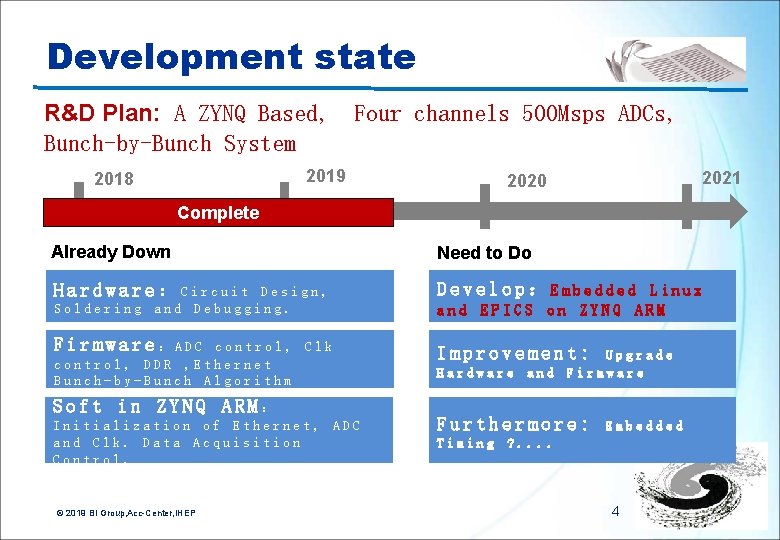

Development state R&D Plan: A ZYNQ Based, Bunch-by-Bunch System Four channels 500 Msps ADCs, 2019 2018 2021 2020 Complete Already Down Need to Do Hardware:Circuit Develop:Embedded Firmware:ADC Improvement: Design, Soldering and Debugging. control, Clk control, DDR , Ethernet Bunch-by-Bunch Algorithm Soft in ZYNQ ARM: Initialization of Ethernet, ADC and Clk. Data Acquisition Control. © 2019 BI Group, Acc-Center, IHEP Linux and EPICS on ZYNQ ARM Upgrade Hardware and Firmware Furthermore: Embedded Timing ? . . 4

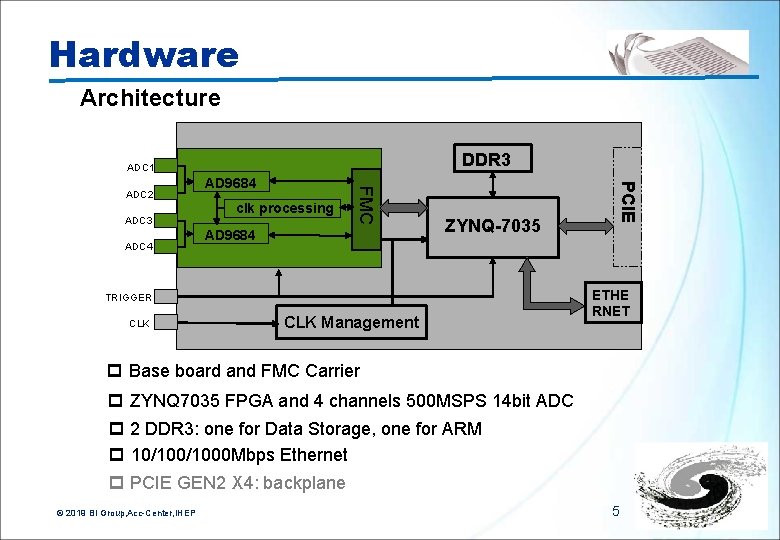

Hardware Architecture DDR 3 ADC 1 ADC 4 clk processing AD 9684 ZYNQ-7035 TRIGGER CLK Management PCIE ADC 3 AD 9684 FMC ADC 2 ETHE RNET p Base board and FMC Carrier p ZYNQ 7035 FPGA and 4 channels 500 MSPS 14 bit ADC p 2 DDR 3: one for Data Storage, one for ARM p 10/1000 Mbps Ethernet p PCIE GEN 2 X 4: backplane © 2019 BI Group, Acc-Center, IHEP 5

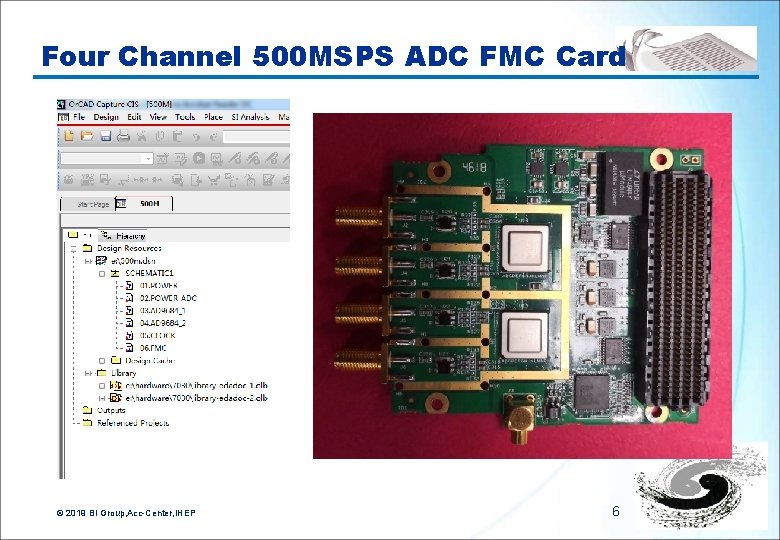

Four Channel 500 MSPS ADC FMC Card © 2019 BI Group, Acc-Center, IHEP 6

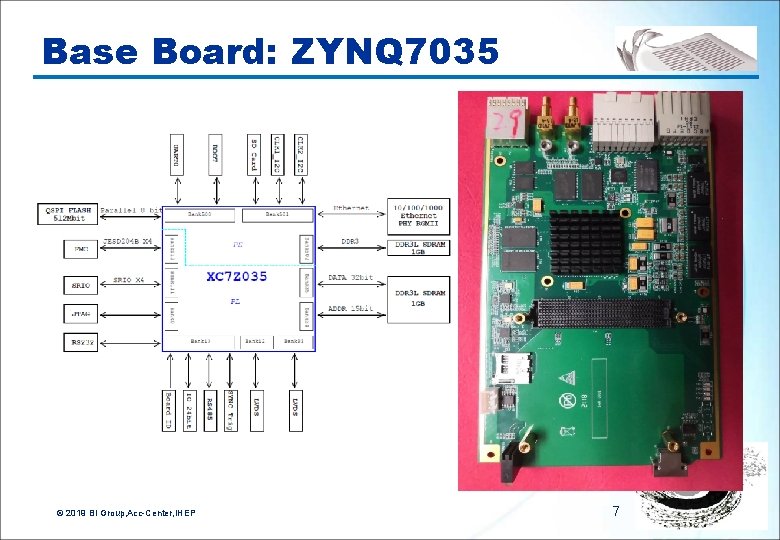

Base Board: ZYNQ 7035 © 2019 BI Group, Acc-Center, IHEP 7

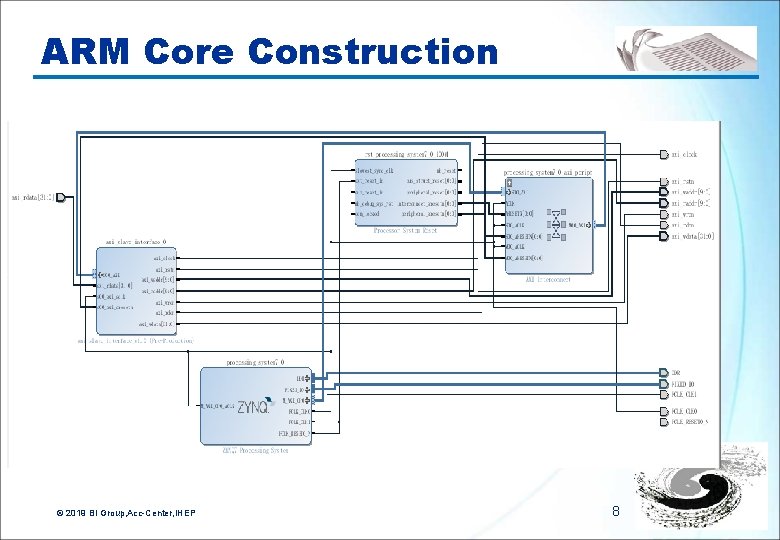

ARM Core Construction © 2019 BI Group, Acc-Center, IHEP 8

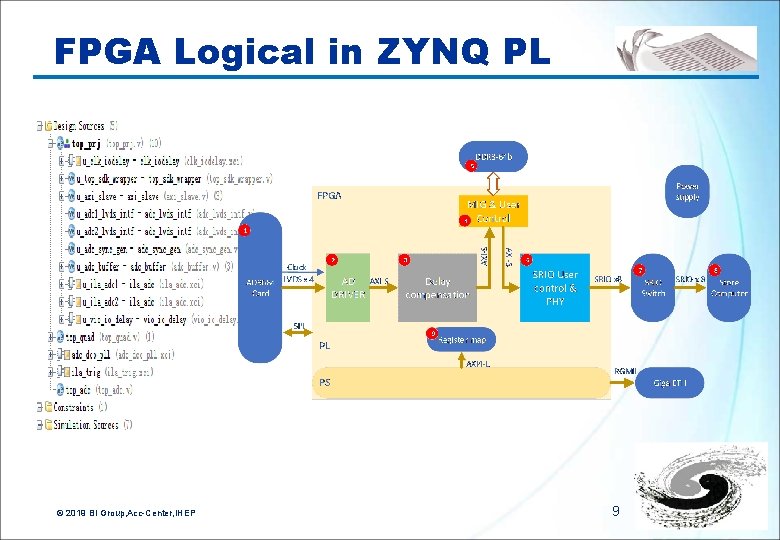

FPGA Logical in ZYNQ PL © 2019 BI Group, Acc-Center, IHEP 9

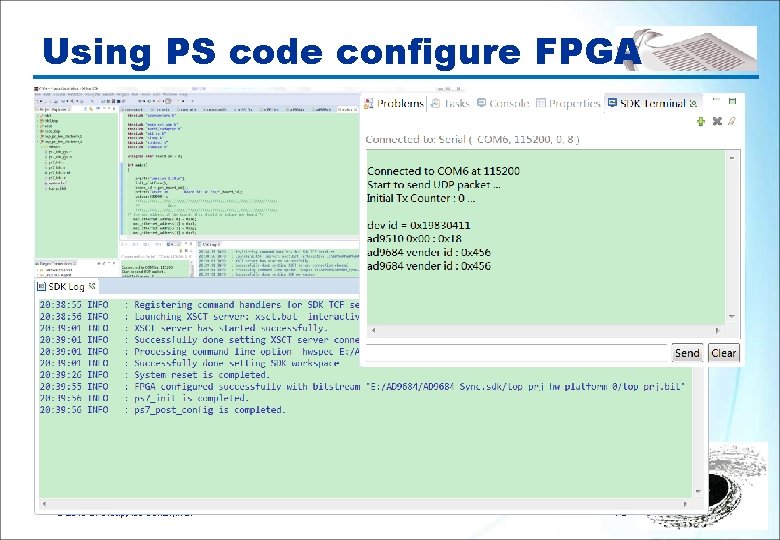

Using PS code configure FPGA © 2019 BI Group, Acc-Center, IHEP 10

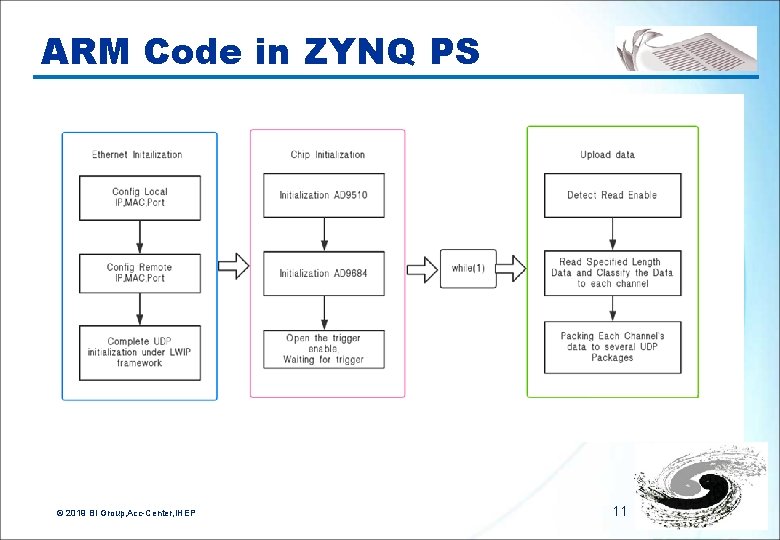

ARM Code in ZYNQ PS © 2019 BI Group, Acc-Center, IHEP 11

Test in Lab © 2019 BI Group, Acc-Center, IHEP 12

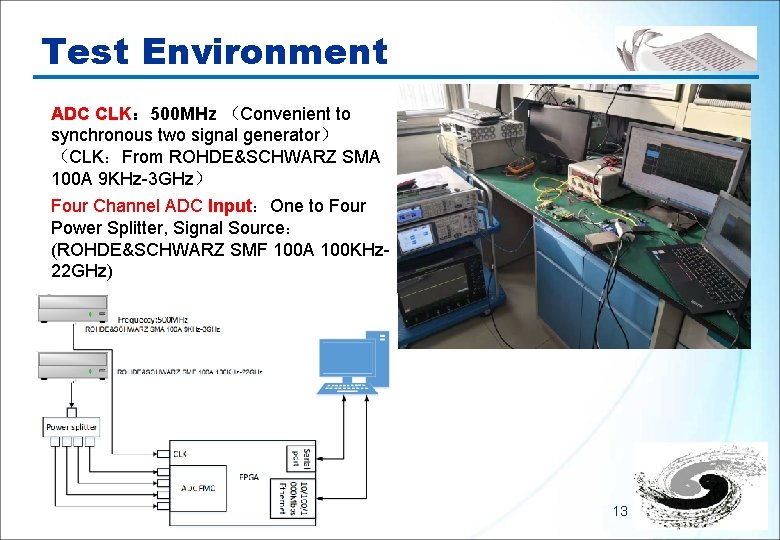

Test Environment ADC CLK: 500 MHz (Convenient to synchronous two signal generator) (CLK:From ROHDE&SCHWARZ SMA 100 A 9 KHz-3 GHz) Four Channel ADC Input:One to Four Power Splitter, Signal Source: (ROHDE&SCHWARZ SMF 100 A 100 KHz 22 GHz) © 2019 BI Group, Acc-Center, IHEP 13

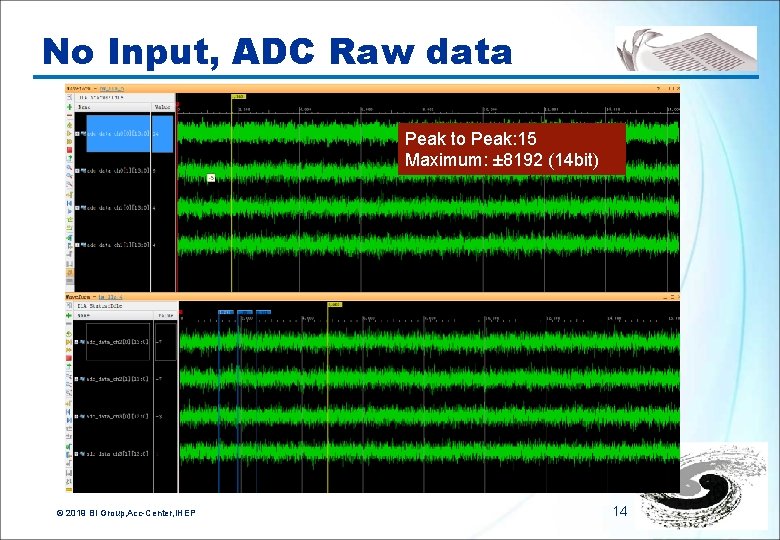

No Input, ADC Raw data Peak to Peak: 15 Maximum: ± 8192 (14 bit) © 2019 BI Group, Acc-Center, IHEP 14

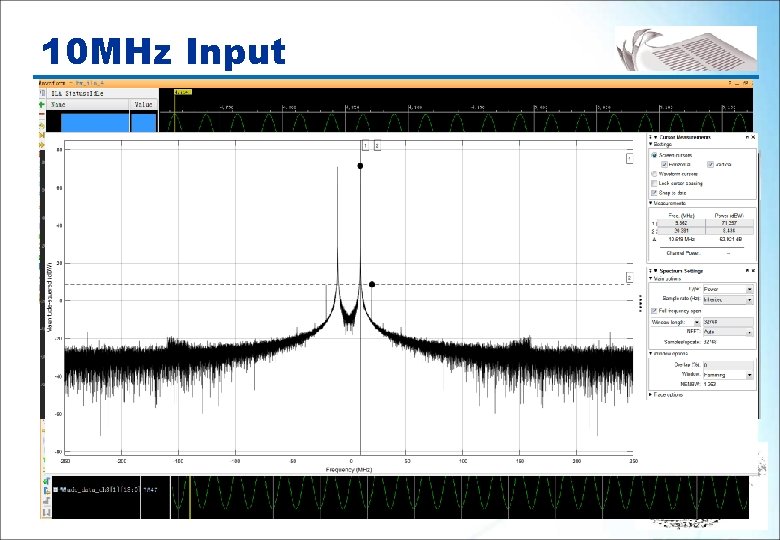

10 MHz Input © 2019 BI Group, Acc-Center, IHEP 15

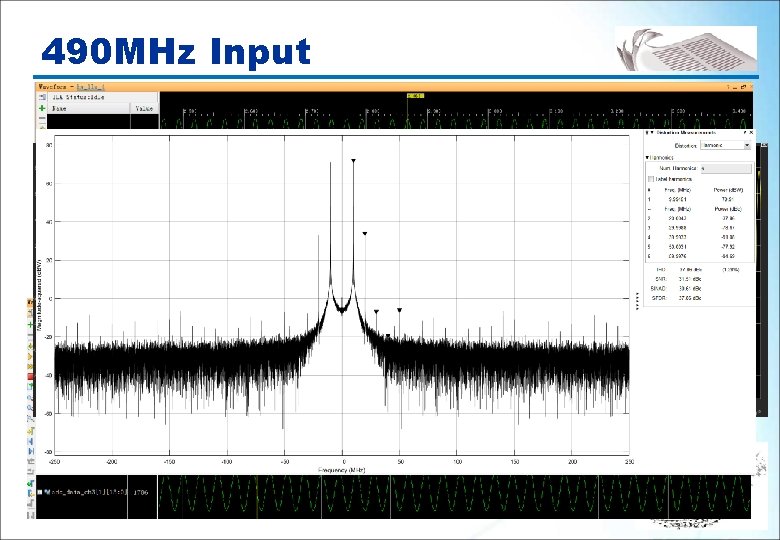

490 MHz Input © 2019 BI Group, Acc-Center, IHEP 16

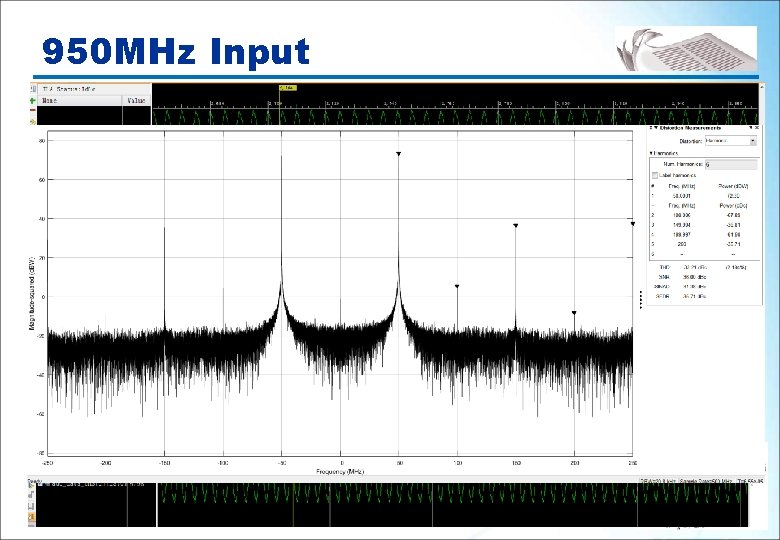

950 MHz Input © 2019 BI Group, Acc-Center, IHEP 17

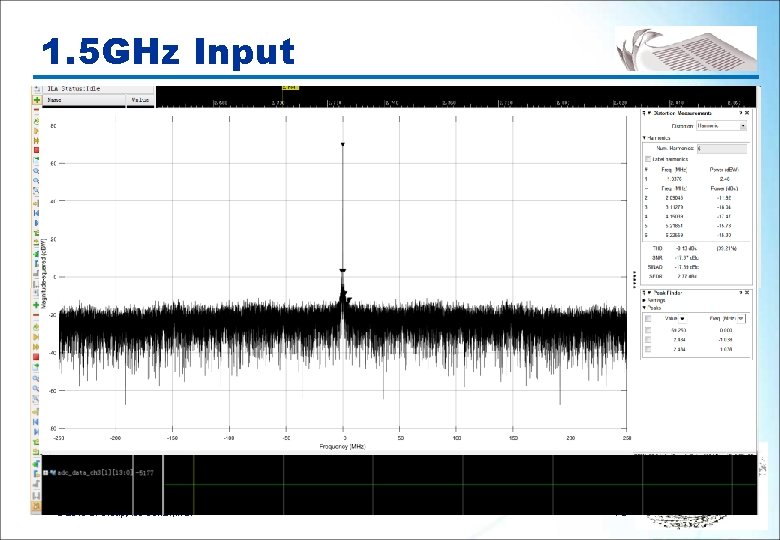

1. 5 GHz Input © 2019 BI Group, Acc-Center, IHEP 18

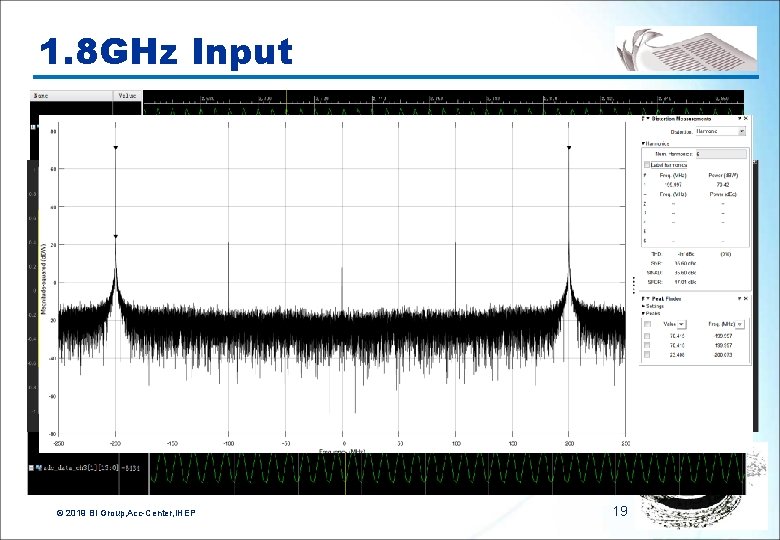

1. 8 GHz Input © 2019 BI Group, Acc-Center, IHEP 19

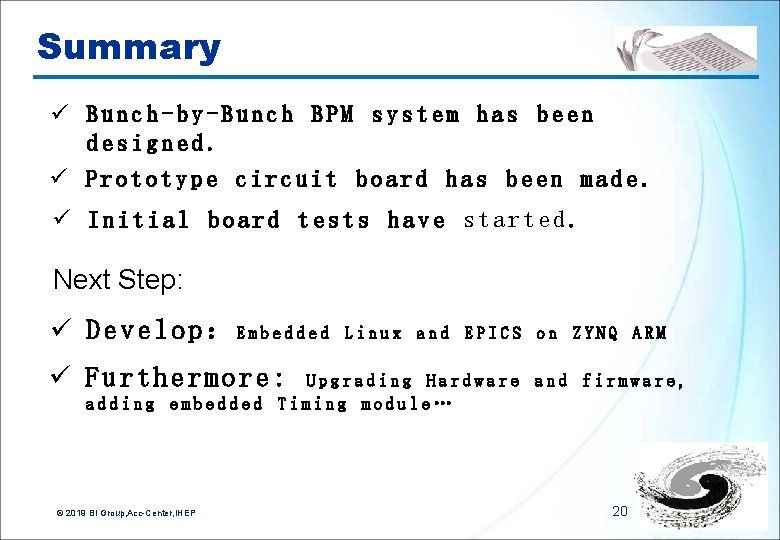

Summary ü Bunch-by-Bunch BPM system has been designed. ü Prototype circuit board has been made. ü Initial board tests have started. Next Step: Improvement: Upgrade of Hardware and Firmware ü Develop:Embedded Linux and EPICS on ZYNQ ARM ü Furthermore: Upgrading Hardware and firmware, adding embedded Timing module… © 2019 BI Group, Acc-Center, IHEP 20

Thank you! © 2019 BI Group, Acc-Center, IHEP 21

- Slides: 21