Input and Output Programmed IO Interrupts and Exception

- Slides: 30

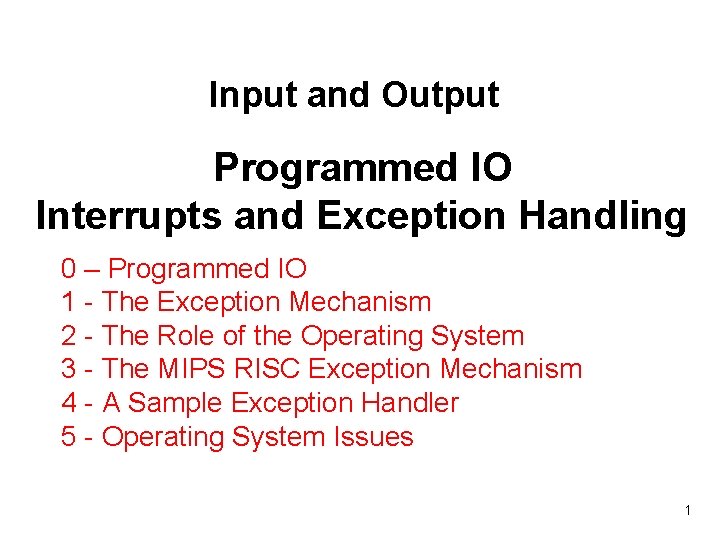

Input and Output Programmed IO Interrupts and Exception Handling 0 – Programmed IO 1 - The Exception Mechanism 2 - The Role of the Operating System 3 - The MIPS RISC Exception Mechanism 4 - A Sample Exception Handler 5 - Operating System Issues 1

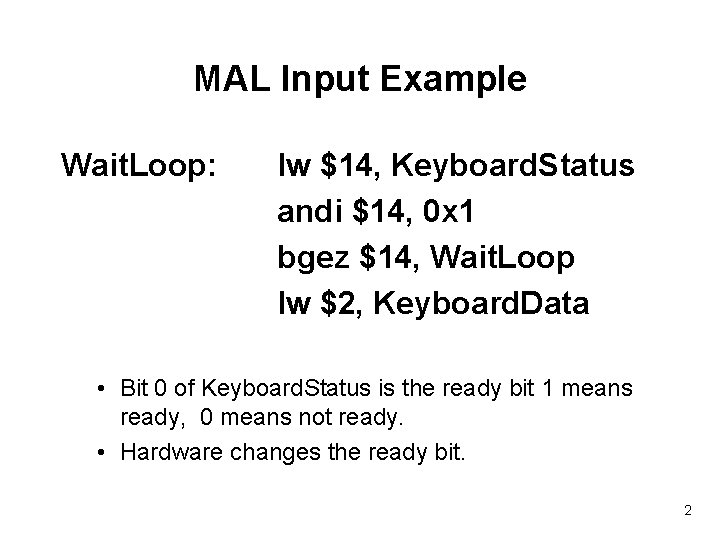

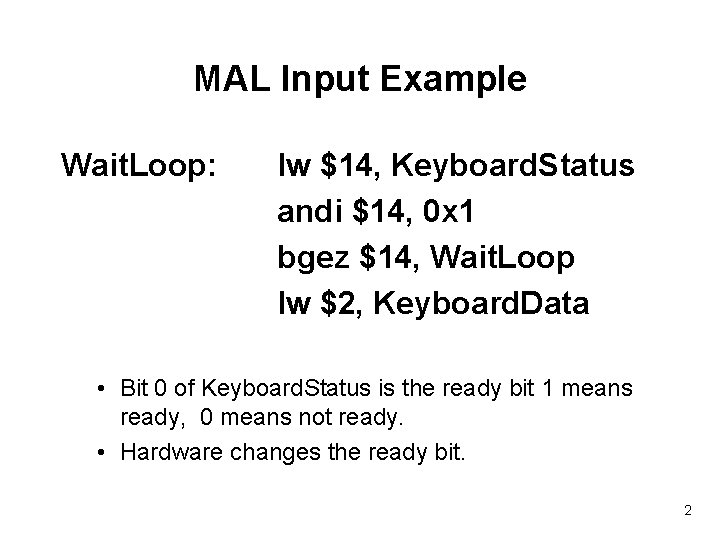

MAL Input Example Wait. Loop: lw $14, Keyboard. Status andi $14, 0 x 1 bgez $14, Wait. Loop lw $2, Keyboard. Data • Bit 0 of Keyboard. Status is the ready bit 1 means ready, 0 means not ready. • Hardware changes the ready bit. 2

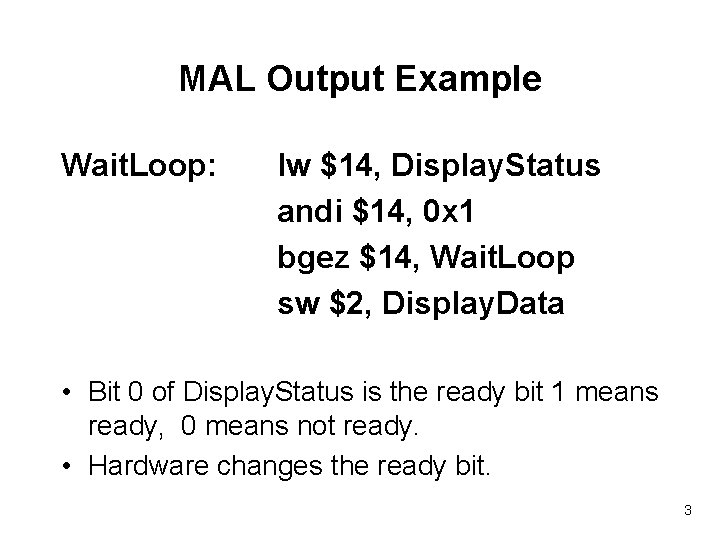

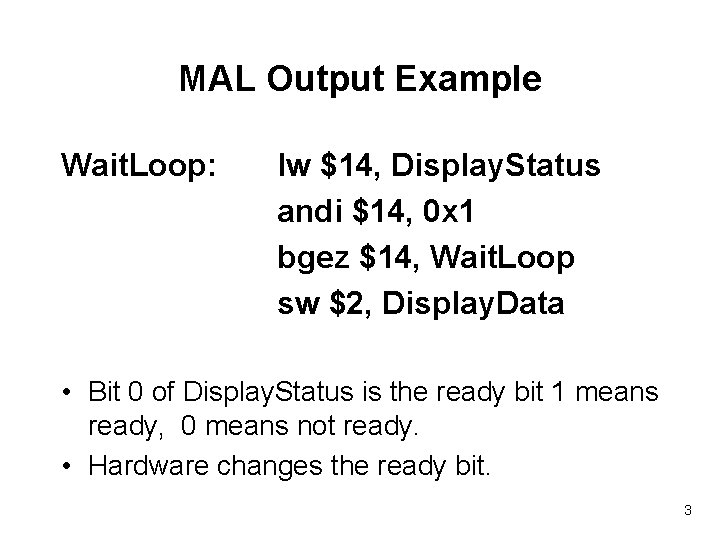

MAL Output Example Wait. Loop: lw $14, Display. Status andi $14, 0 x 1 bgez $14, Wait. Loop sw $2, Display. Data • Bit 0 of Display. Status is the ready bit 1 means ready, 0 means not ready. • Hardware changes the ready bit. 3

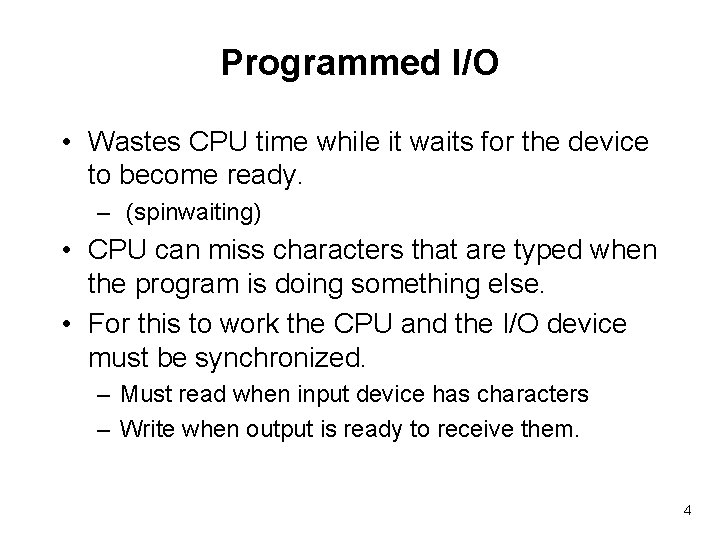

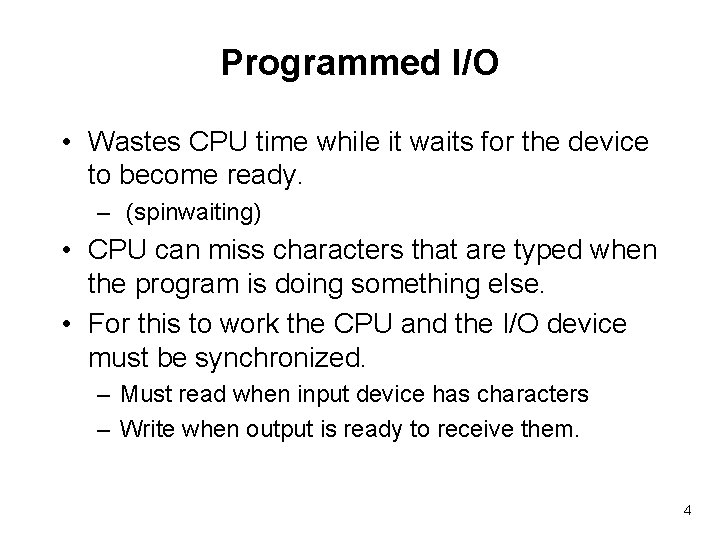

Programmed I/O • Wastes CPU time while it waits for the device to become ready. – (spinwaiting) • CPU can miss characters that are typed when the program is doing something else. • For this to work the CPU and the I/O device must be synchronized. – Must read when input device has characters – Write when output is ready to receive them. 4

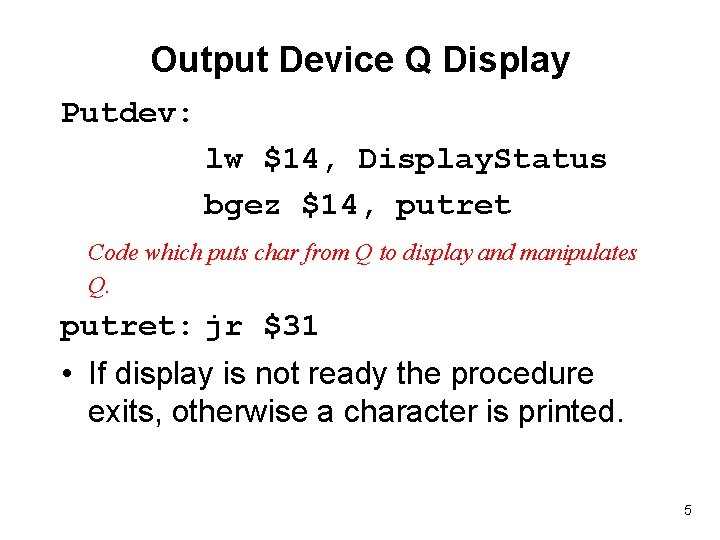

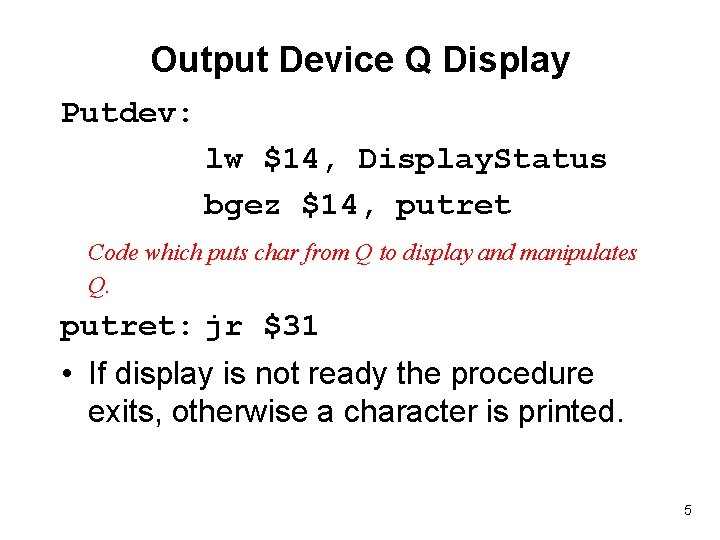

Output Device Q Display Putdev: lw $14, Display. Status bgez $14, putret Code which puts char from Q to display and manipulates Q. putret: jr $31 • If display is not ready the procedure exits, otherwise a character is printed. 5

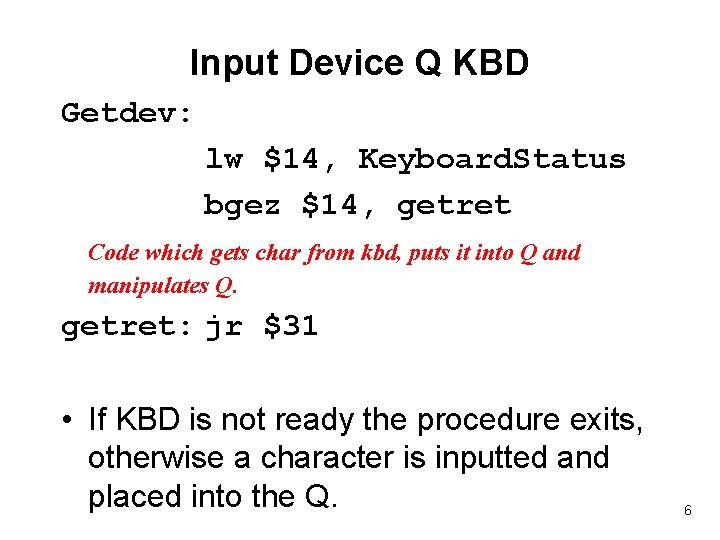

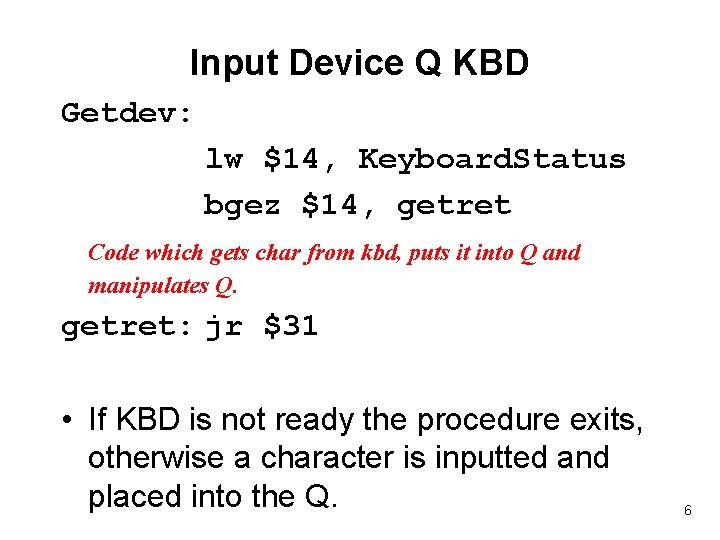

Input Device Q KBD Getdev: lw $14, Keyboard. Status bgez $14, getret Code which gets char from kbd, puts it into Q and manipulates Q. getret: jr $31 • If KBD is not ready the procedure exits, otherwise a character is inputted and placed into the Q. 6

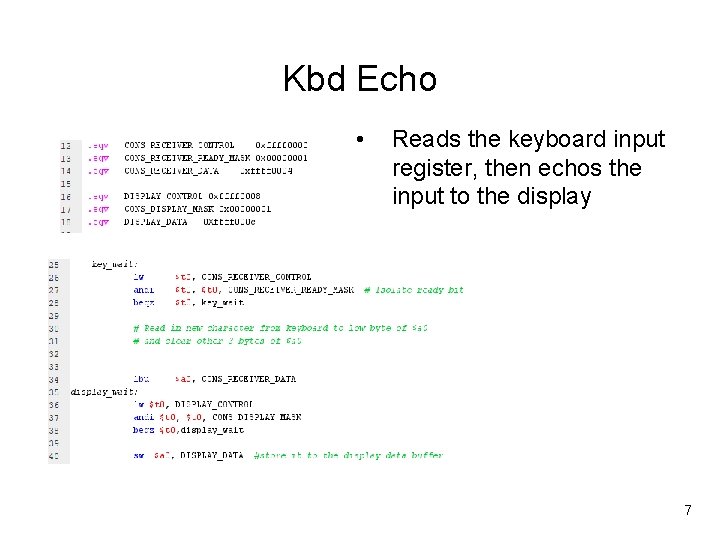

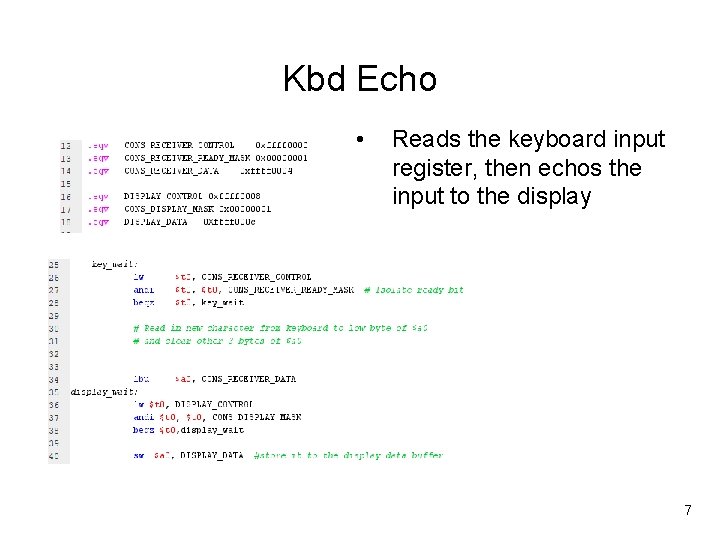

Kbd Echo • Reads the keyboard input register, then echos the input to the display 7

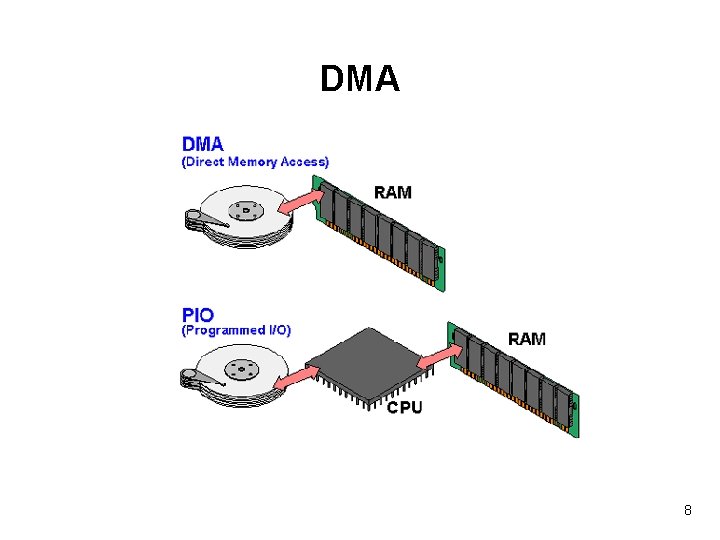

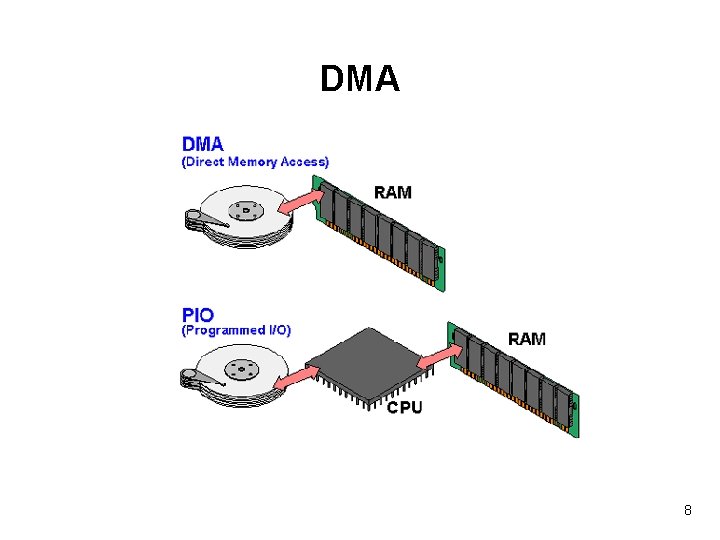

DMA 8

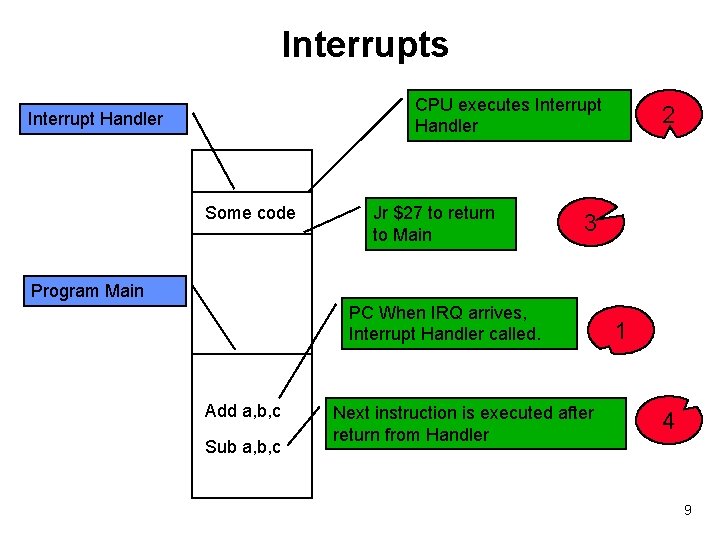

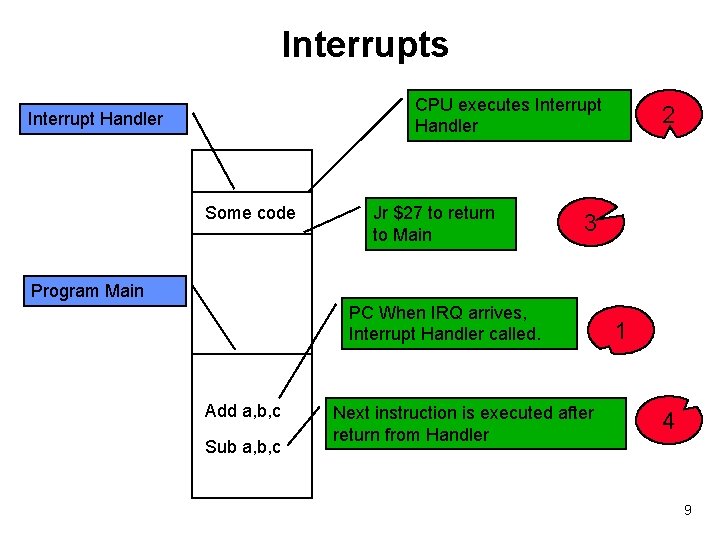

Interrupts CPU executes Interrupt Handler Some code Jr $27 to return to Main 2 3 Program Main PC When IRQ arrives, Interrupt Handler called. Add a, b, c Sub a, b, c Next instruction is executed after return from Handler 1 4 9

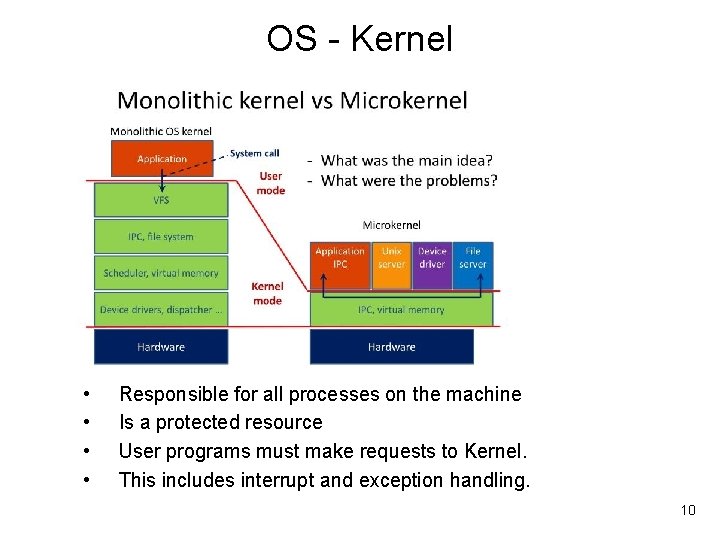

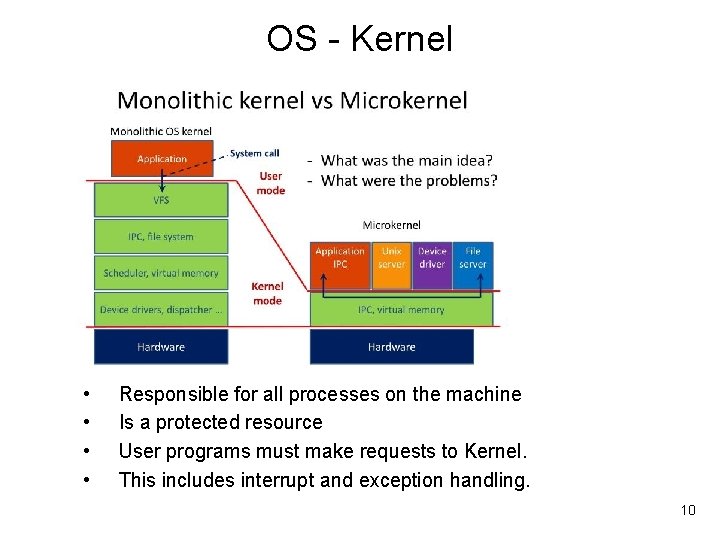

OS - Kernel • • Responsible for all processes on the machine Is a protected resource User programs must make requests to Kernel. This includes interrupt and exception handling. 10

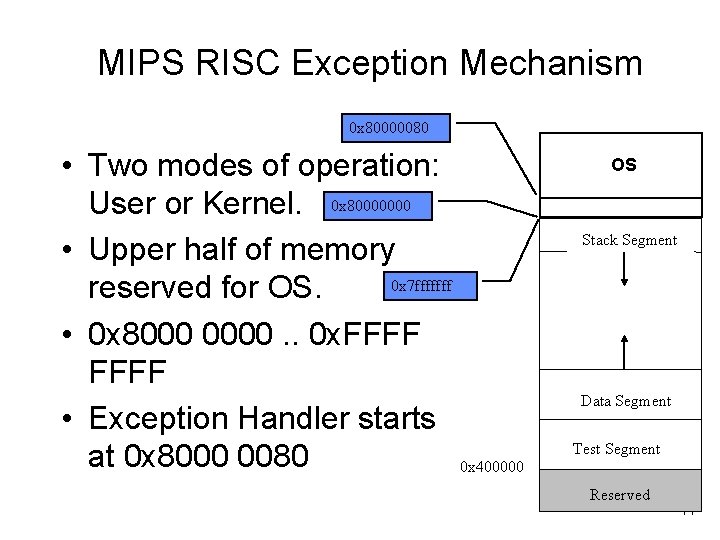

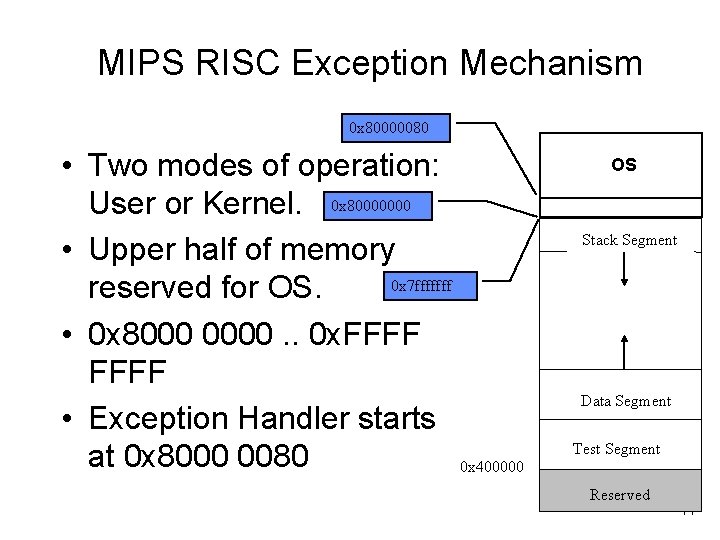

MIPS RISC Exception Mechanism 0 x 80000080 • Two modes of operation: User or Kernel. 0 x 80000000 • Upper half of memory 0 x 7 fffffff reserved for OS. • 0 x 8000 0000. . 0 x. FFFF • Exception Handler starts at 0 x 8000 0080 0 x 400000 OS Stack Segment Data Segment Test Segment Reserved 11

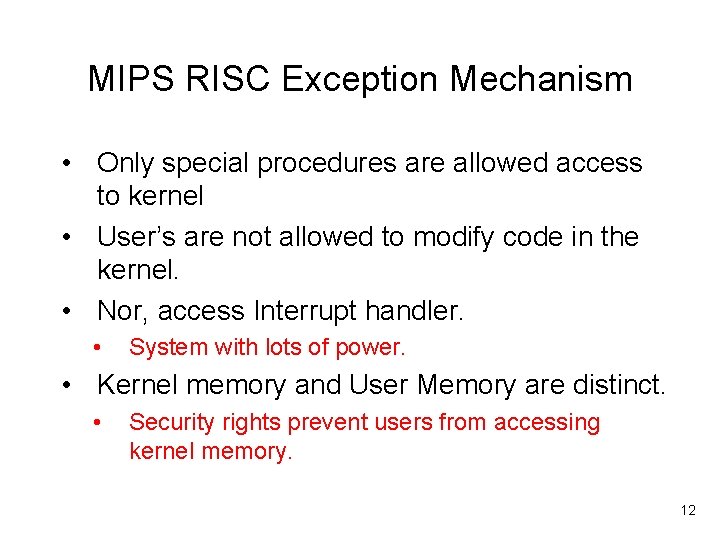

MIPS RISC Exception Mechanism • Only special procedures are allowed access to kernel • User’s are not allowed to modify code in the kernel. • Nor, access Interrupt handler. • System with lots of power. • Kernel memory and User Memory are distinct. • Security rights prevent users from accessing kernel memory. 12

Asynchronous Interrupts • Generated by h/w devices. • Interrupts, can appear at any time • State of system is not known at time of interrupt. • We can not count on any general purpose register being free. • 2 registers $k 0, $k 1 ($26, $27) are kernel reserved to cleanly transition to and from an interrupt. • This prevents clobbering information stored in user program registers. 13

Synchronous Traps • Traps are software interrupts generated by software. • Thus are Predictable • Handed by the OS. • Device drivers • • Service routines • • Buffer flush VM Page Fault Fatal coding errors • • • Divide by Zero Overflow Memory violation. User program tries to access kernel memory, or another user programs memory. 14

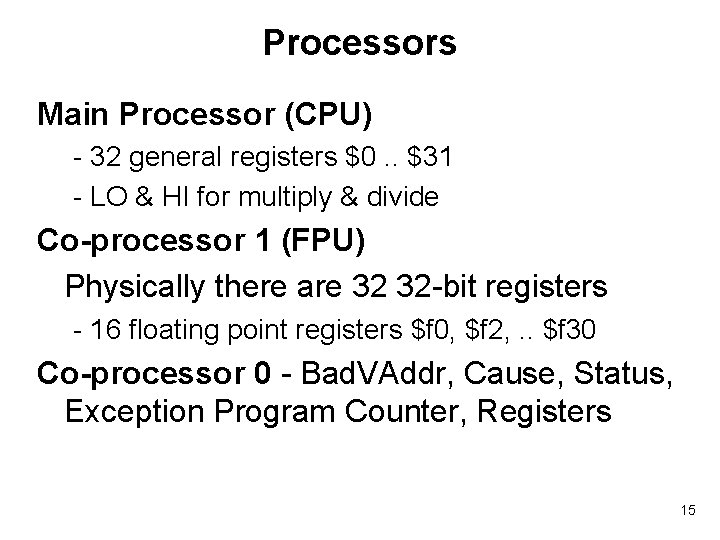

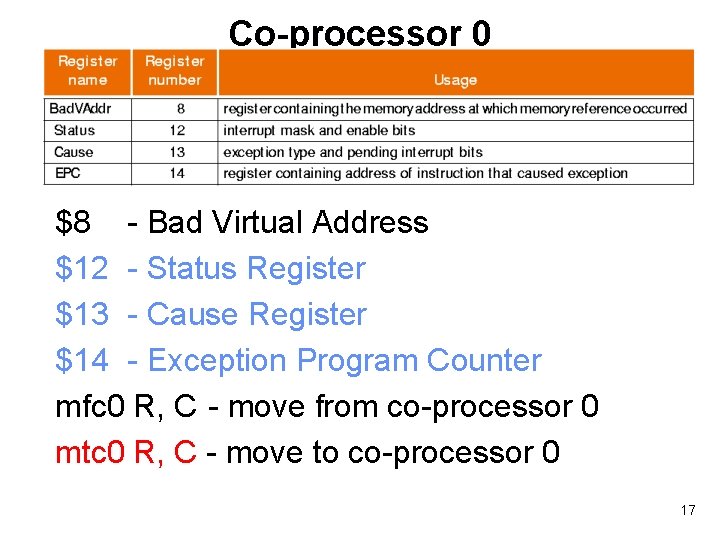

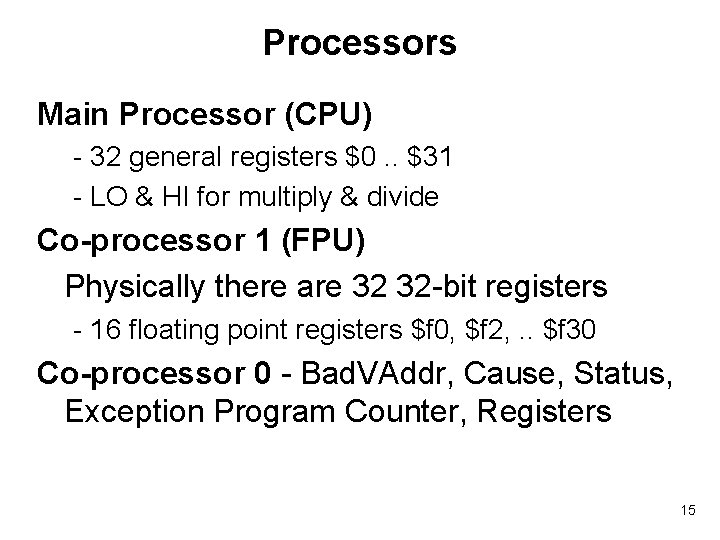

Processors Main Processor (CPU) - 32 general registers $0. . $31 - LO & HI for multiply & divide Co-processor 1 (FPU) Physically there are 32 32 -bit registers - 16 floating point registers $f 0, $f 2, . . $f 30 Co-processor 0 - Bad. VAddr, Cause, Status, Exception Program Counter, Registers 15

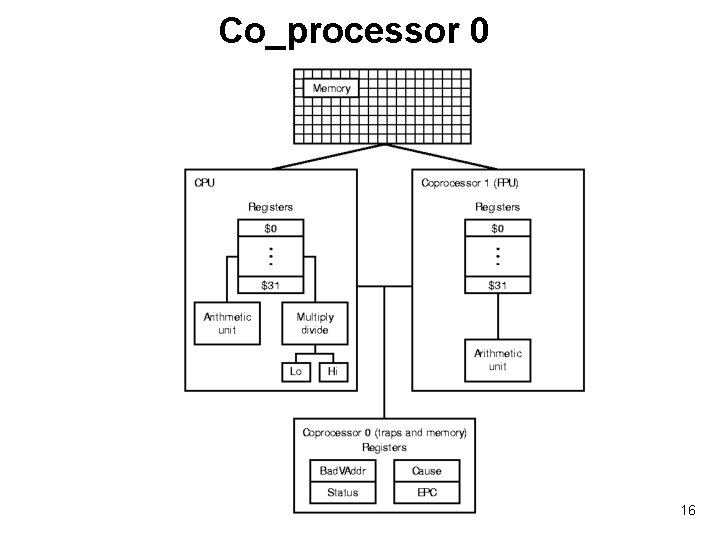

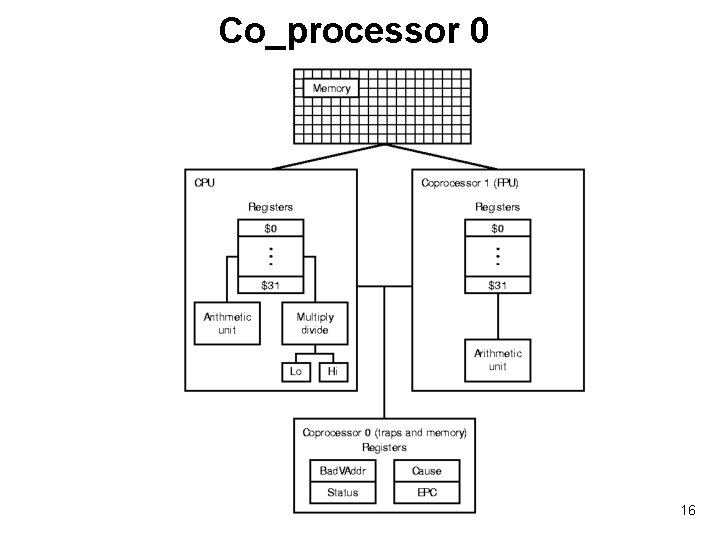

Co_processor 0 16

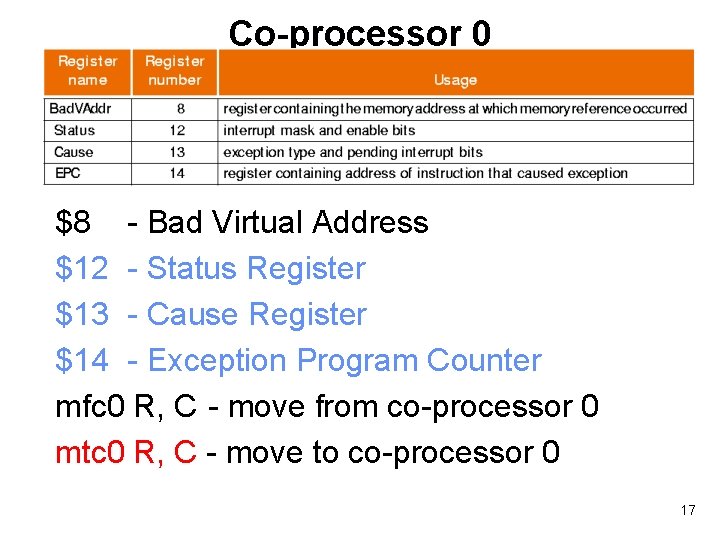

Co-processor 0 $8 - Bad Virtual Address $12 - Status Register $13 - Cause Register $14 - Exception Program Counter mfc 0 R, C - move from co-processor 0 mtc 0 R, C - move to co-processor 0 17

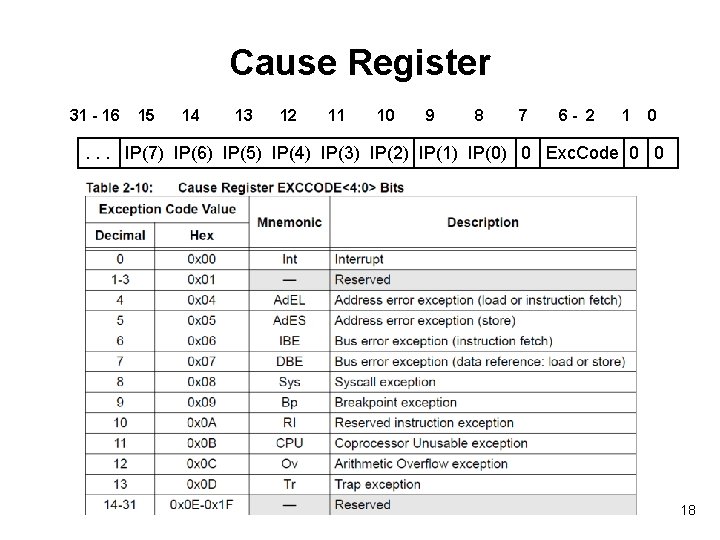

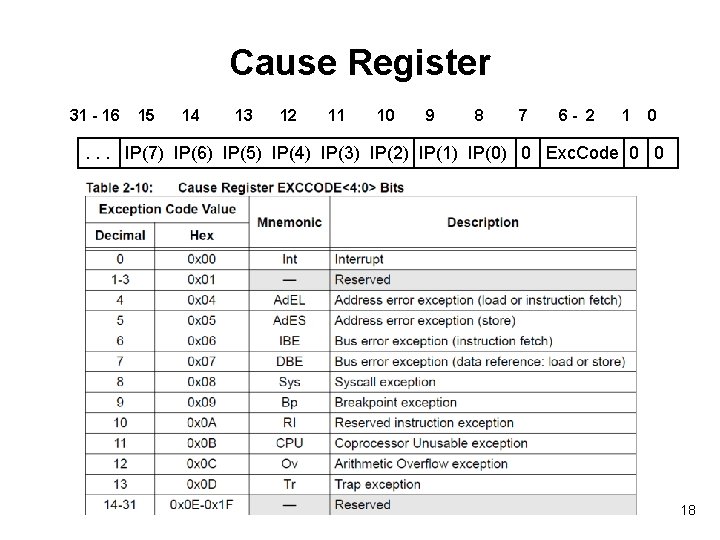

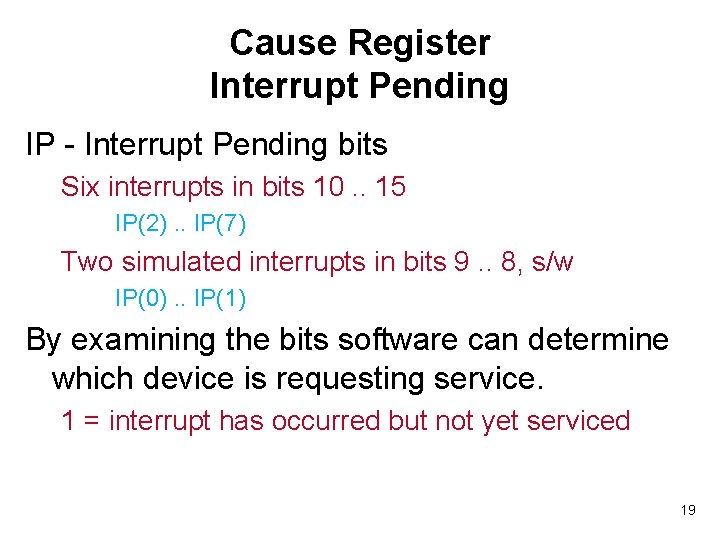

Cause Register 31 - 16 15 14 13 12 11 10 9 8 7 6 - 2 1 0 . . . IP(7) IP(6) IP(5) IP(4) IP(3) IP(2) IP(1) IP(0) 0 Exc. Code 0 0 18

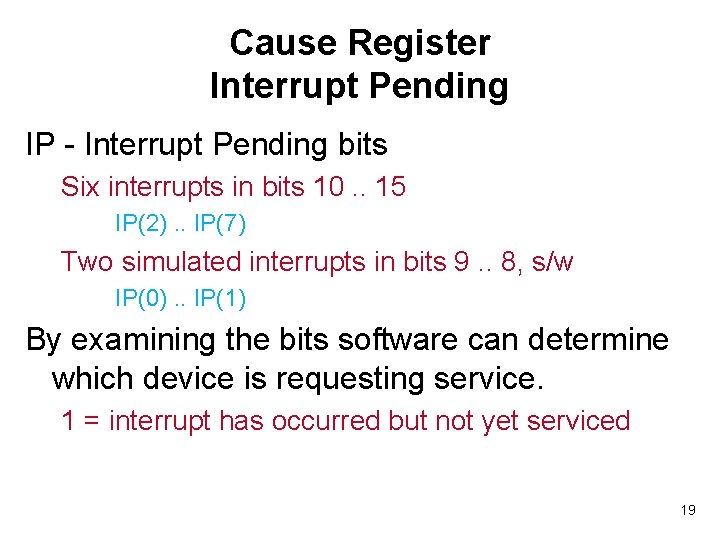

Cause Register Interrupt Pending IP - Interrupt Pending bits Six interrupts in bits 10. . 15 IP(2). . IP(7) Two simulated interrupts in bits 9. . 8, s/w IP(0). . IP(1) By examining the bits software can determine which device is requesting service. 1 = interrupt has occurred but not yet serviced 19

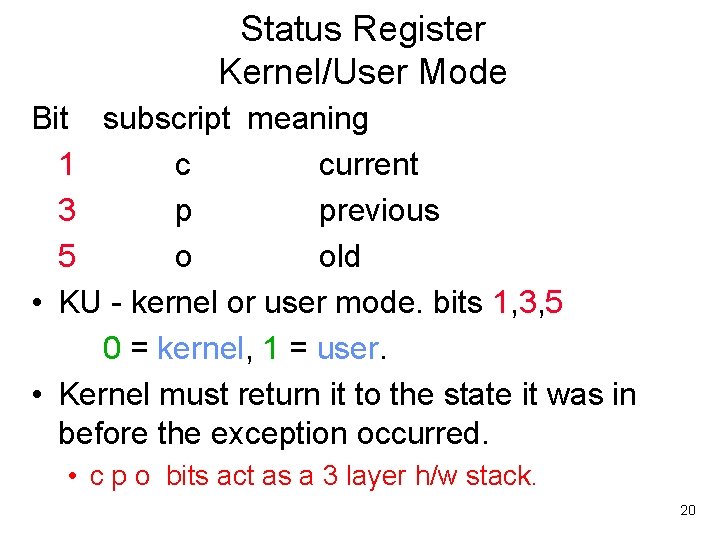

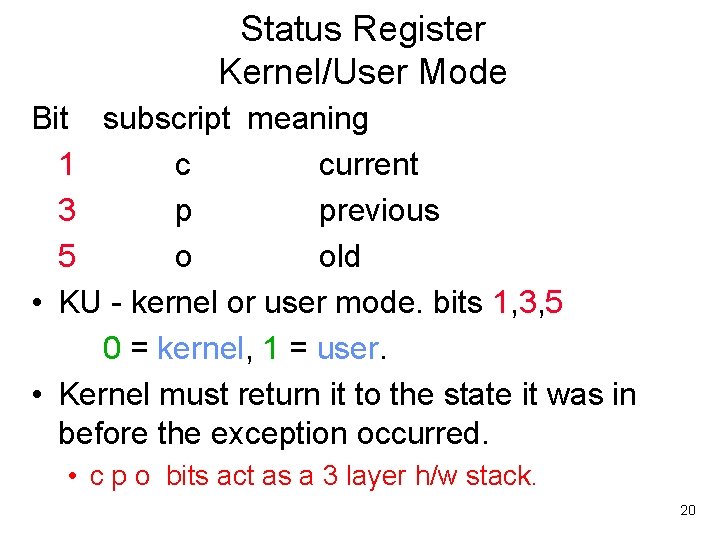

Status Register Kernel/User Mode Bit subscript meaning 1 c current 3 p previous 5 o old • KU - kernel or user mode. bits 1, 3, 5 0 = kernel, 1 = user. • Kernel must return it to the state it was in before the exception occurred. • c p o bits act as a 3 layer h/w stack. 20

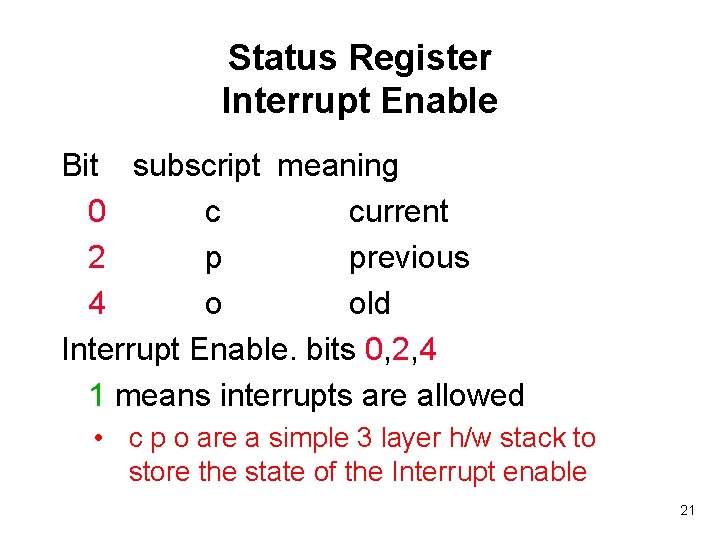

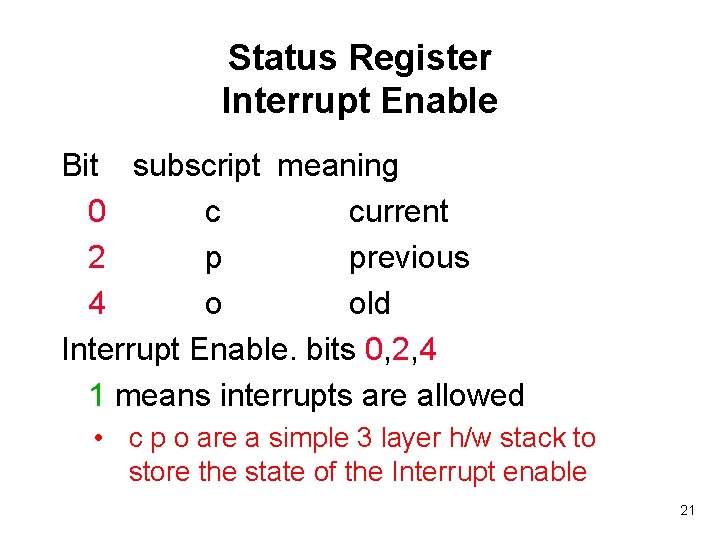

Status Register Interrupt Enable Bit subscript meaning 0 c current 2 p previous 4 o old Interrupt Enable. bits 0, 2, 4 1 means interrupts are allowed • c p o are a simple 3 layer h/w stack to store the state of the Interrupt enable 21

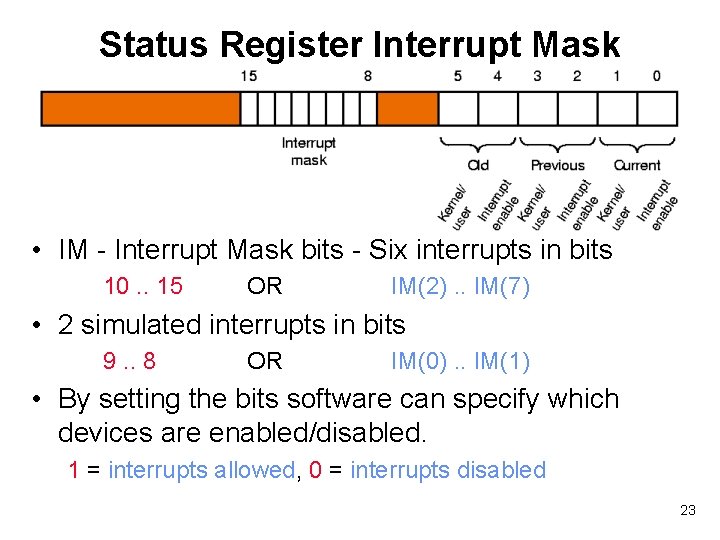

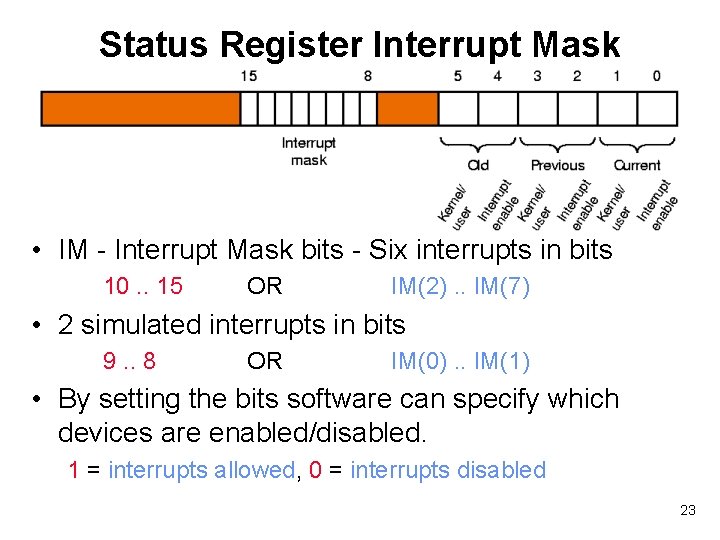

Status Register Interrupt Mask • IM - Interrupt Mask bits - Six interrupts in bits 10. . 15 OR IM(2). . IM(7) • 2 simulated interrupts in bits 9. . 8 OR IM(0). . IM(1) • By setting the bits software can specify which devices are enabled/disabled. 1 = interrupts allowed, 0 = interrupts disabled 23

EPC Register ($14) • Holds return address for exception handler • Exceptions can come from anywhere • • • user program (syscall) kernel (trap) external (device) • When an exception is raised: • • • Must save the return address in EPC Normally return address is done with JAL but it is not used when an exception occurs. An exception can occur before between JAL and the saving of $ra. Making the use of $ra problematic. 24

EPC Register ($14). • Example • • Interrupt is received PC is saved in EPC PC is modified to point to the handler. When done PC is reloaded with EPC. 25

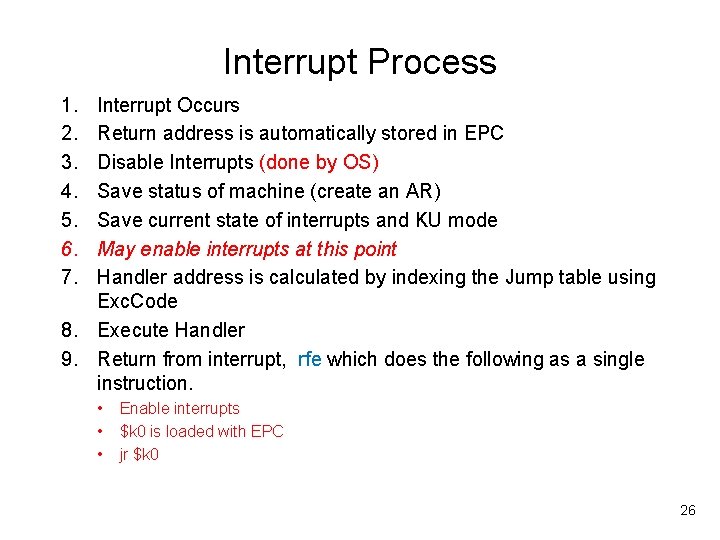

Interrupt Process 1. 2. 3. 4. 5. 6. 7. Interrupt Occurs Return address is automatically stored in EPC Disable Interrupts (done by OS) Save status of machine (create an AR) Save current state of interrupts and KU mode May enable interrupts at this point Handler address is calculated by indexing the Jump table using Exc. Code 8. Execute Handler 9. Return from interrupt, rfe which does the following as a single instruction. • • • Enable interrupts $k 0 is loaded with EPC jr $k 0 26

Re-entrant and Non Re-entrant Handlers • Interrupts maybe disables so an interrupt can not interrupt a handler. • These handlers then must execute to completion before another interrupt into the handler is allowed. Non re-entrant. • E. g. Kbd handler interrupted by the Kbd is bad. • key sequences can then arrive out of order. • However, kbd handler can be interrupted by a bad address handler. • Safe operation • Generally this is done on a case by case basis. 27

Disabling Interrupts 1 - Set (make it 0) bit zero of the status register to disable all interrupts. 2 - Set an individual bit or bits in the Interrupt Mask to disable one or more. 28

Priority Interrupts • Interrupts have priorities. • Lower interrupts, higher priority. • Typically the timer has highest. • Sends an interrupt at regular intervals so OS always has control. • Prevents processes from hogging the CPU. • Kbd is 2 nd. • Always good for the user to have control. • Handlers are executed based on priority. 29

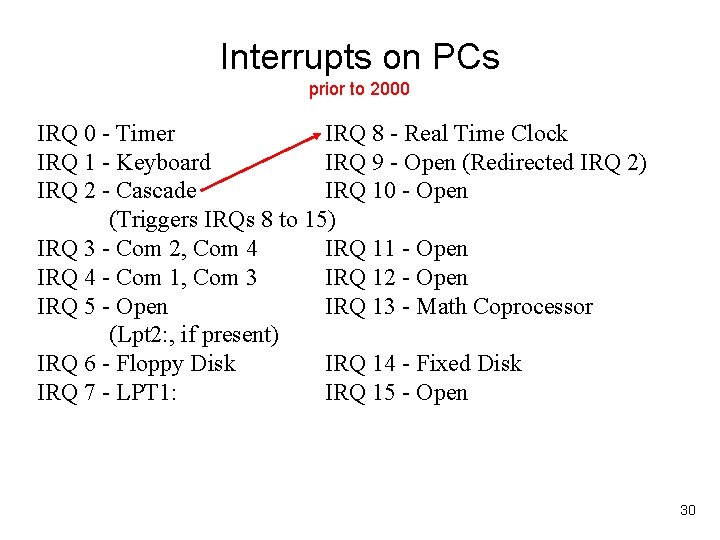

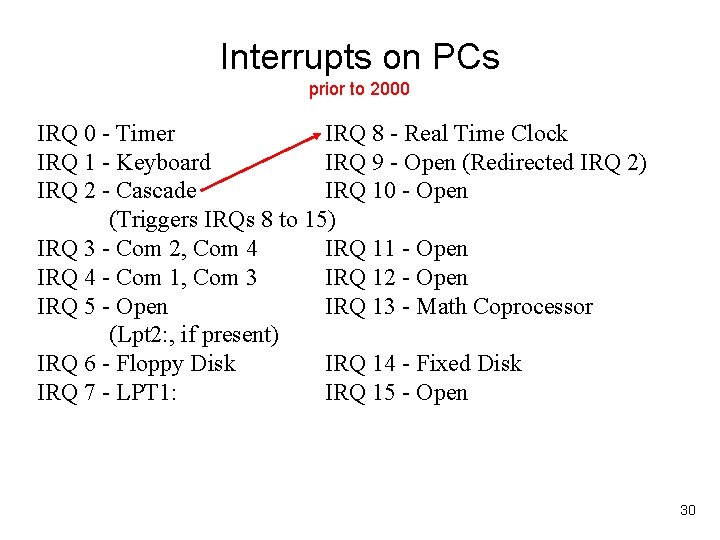

Interrupts on PCs prior to 2000 IRQ 0 - Timer IRQ 8 - Real Time Clock IRQ 1 - Keyboard IRQ 9 - Open (Redirected IRQ 2) IRQ 2 - Cascade IRQ 10 - Open (Triggers IRQs 8 to 15) IRQ 3 - Com 2, Com 4 IRQ 11 - Open IRQ 4 - Com 1, Com 3 IRQ 12 - Open IRQ 5 - Open IRQ 13 - Math Coprocessor (Lpt 2: , if present) IRQ 6 - Floppy Disk IRQ 14 - Fixed Disk IRQ 7 - LPT 1: IRQ 15 - Open 30

End 31