Input 0 0001 Input 0 0038 Input 0

- Slides: 144

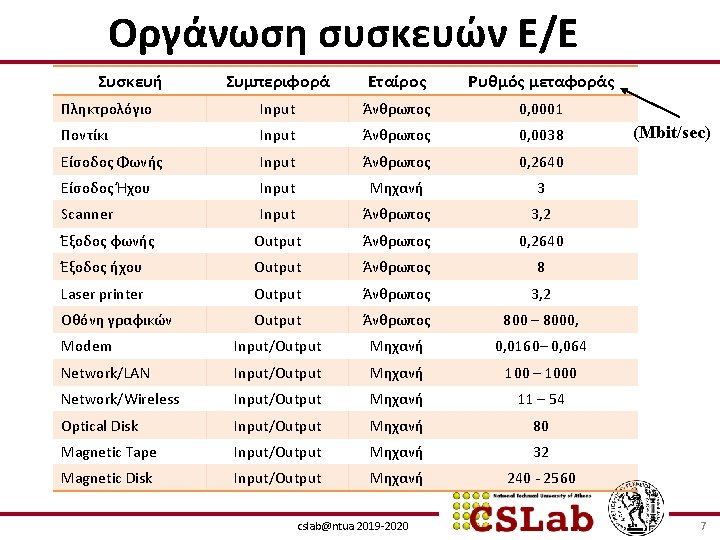

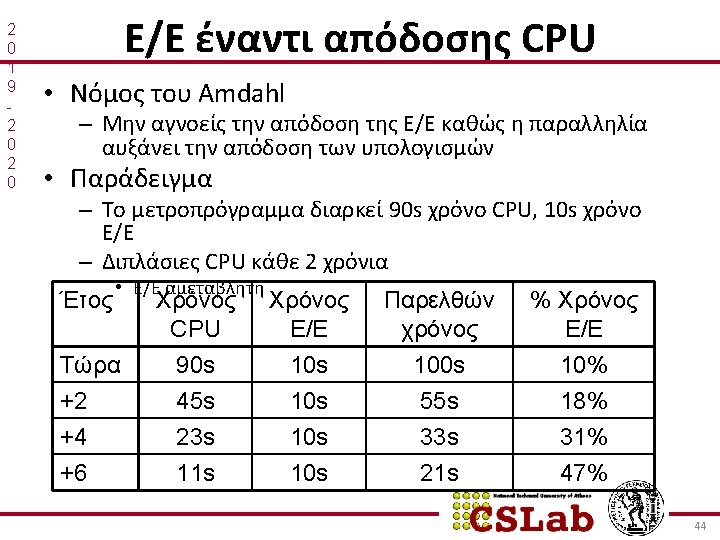

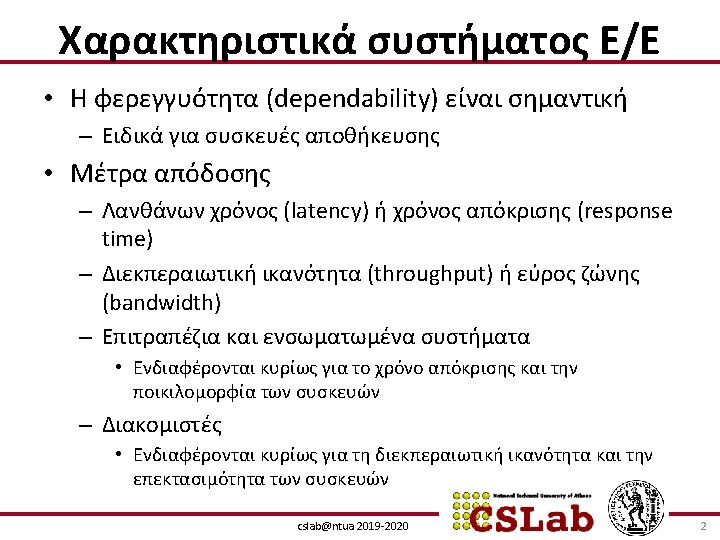

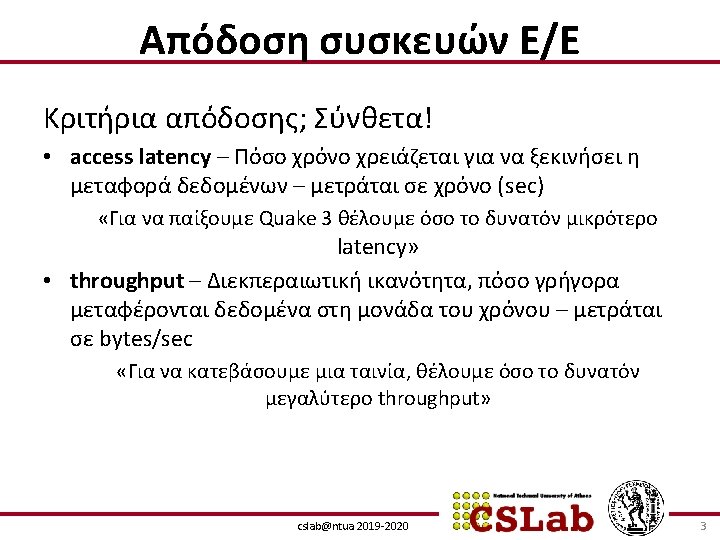

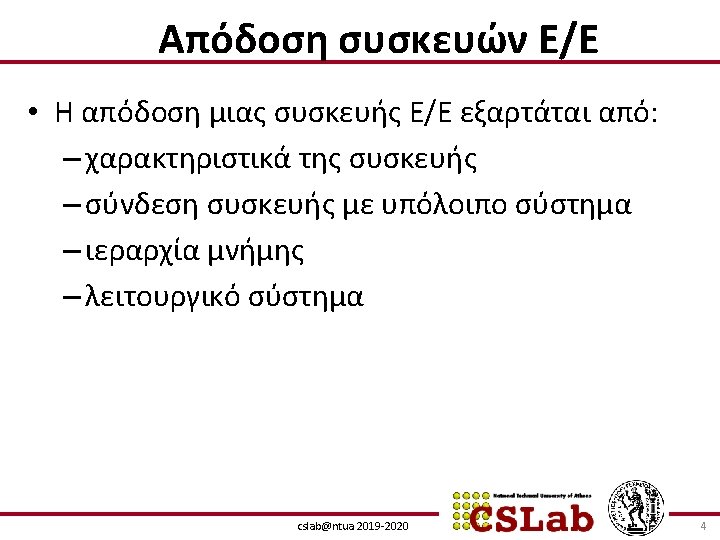

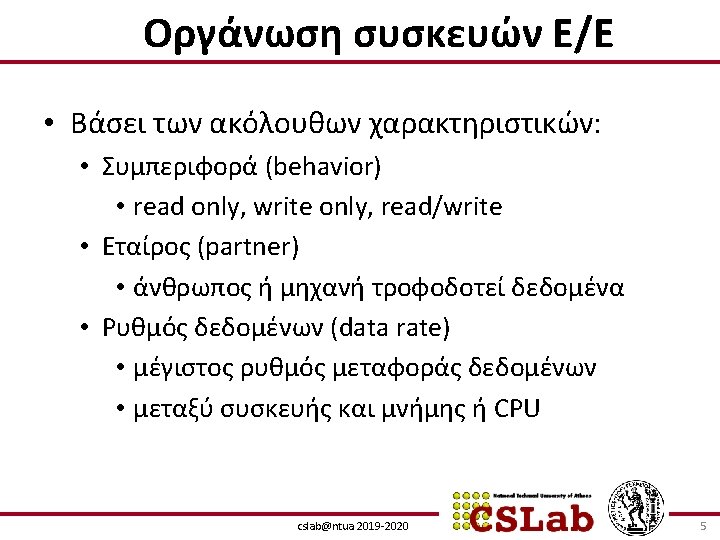

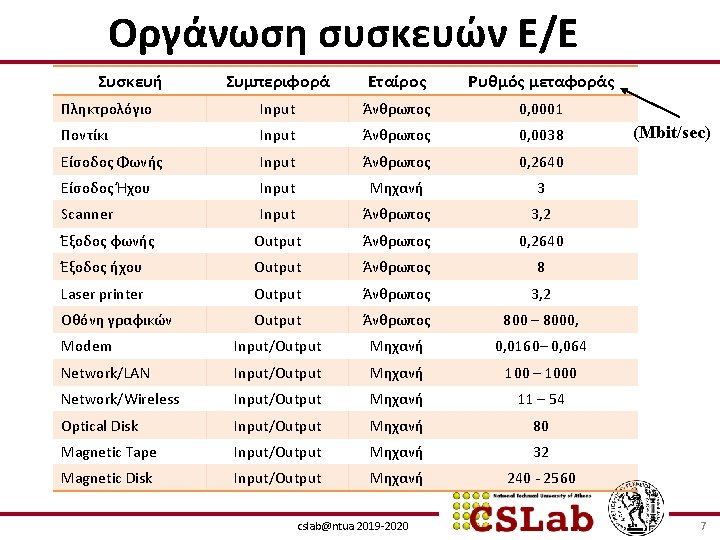

Οργάνωση συσκευών Ε/Ε Συσκευή Συμπεριφορά Εταίρος Ρυθμός μεταφοράς Πληκτρολόγιο Input Άνθρωπος 0, 0001 Ποντίκι Input Άνθρωπος 0, 0038 Είσοδος Φωνής Input Άνθρωπος 0, 2640 Είσοδος Ήχου Input Μηχανή 3 Scanner Input Άνθρωπος 3, 2 Έξοδος φωνής Output Άνθρωπος 0, 2640 Έξοδος ήχου Output Άνθρωπος 8 Laser printer Output Άνθρωπος 3, 2 Οθόνη γραφικών Output Άνθρωπος 800 – 8000, Modem Input/Output Μηχανή 0, 0160– 0, 064 Network/LAN Input/Output Μηχανή 100 – 1000 Network/Wireless Input/Output Μηχανή 11 – 54 Optical Disk Input/Output Μηχανή 80 Magnetic Tape Input/Output Μηχανή 32 Magnetic Disk Input/Output Μηχανή 240 - 2560 cslab@ntua 2019 -2020 (Mbit/sec) 7

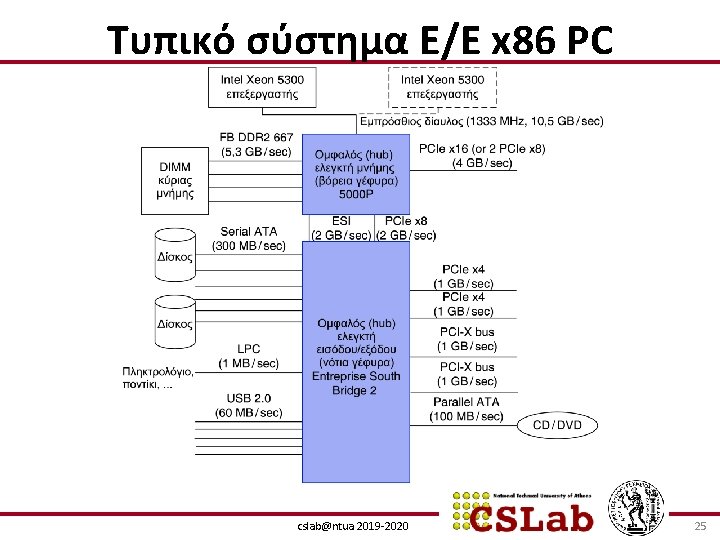

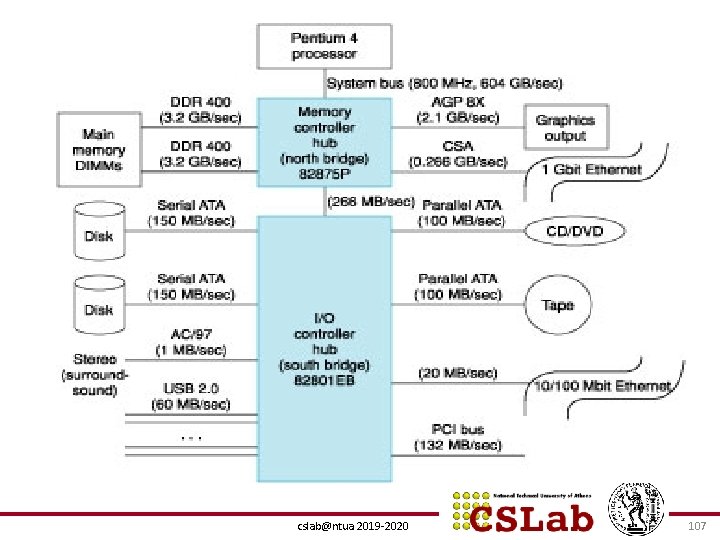

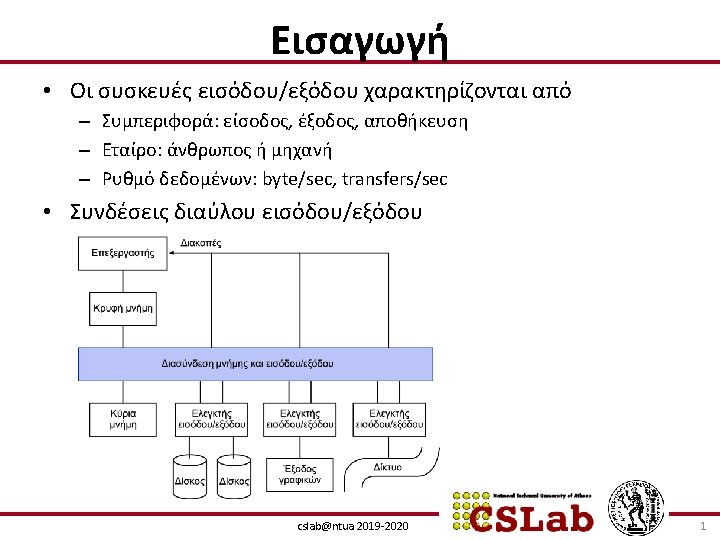

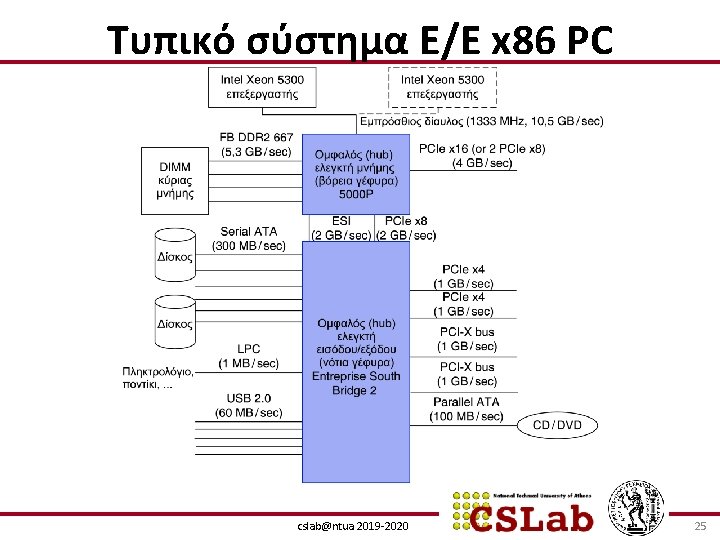

Τυπικό σύστημα Ε/Ε x 86 PC cslab@ntua 2019 -2020 25

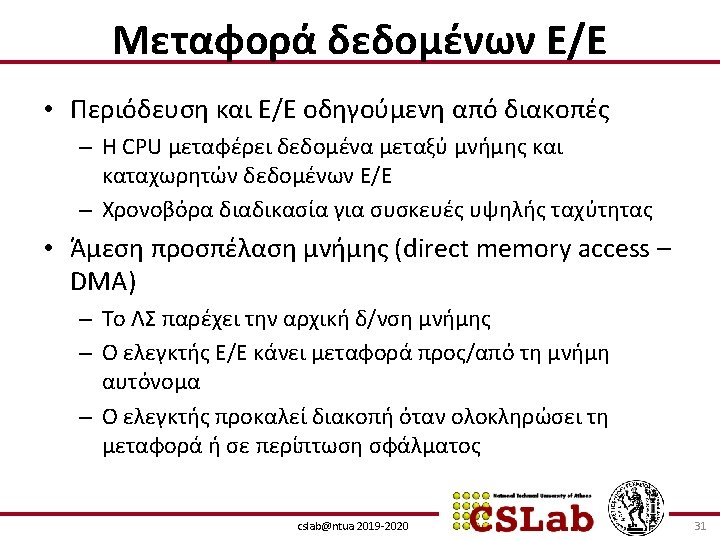

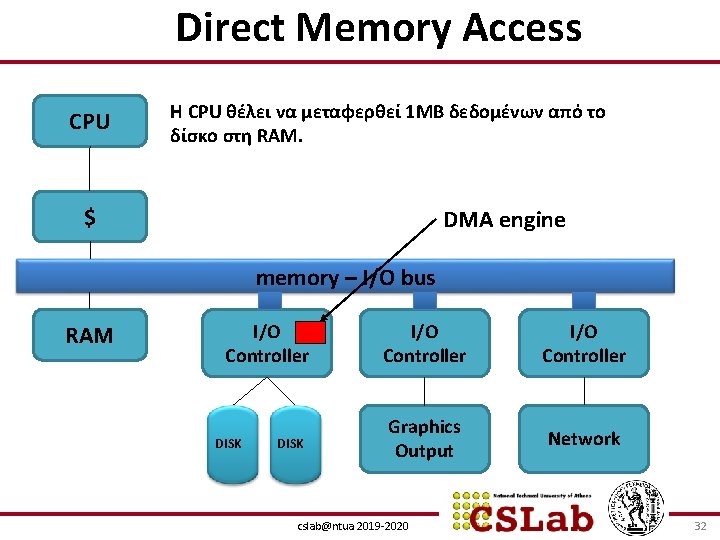

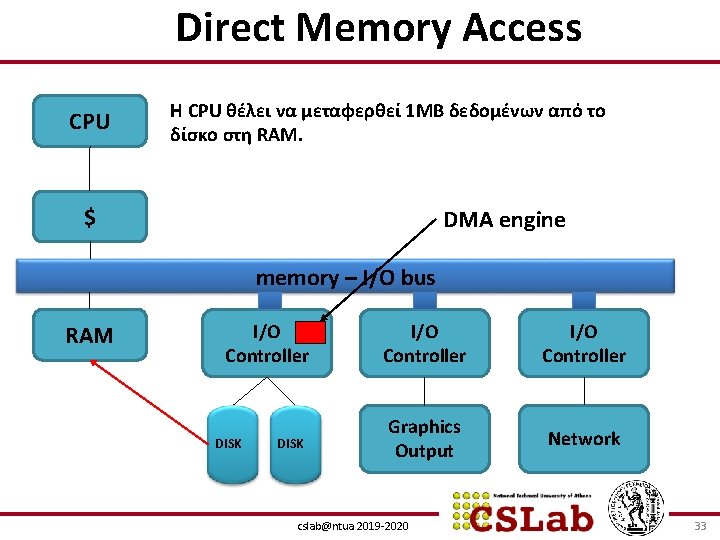

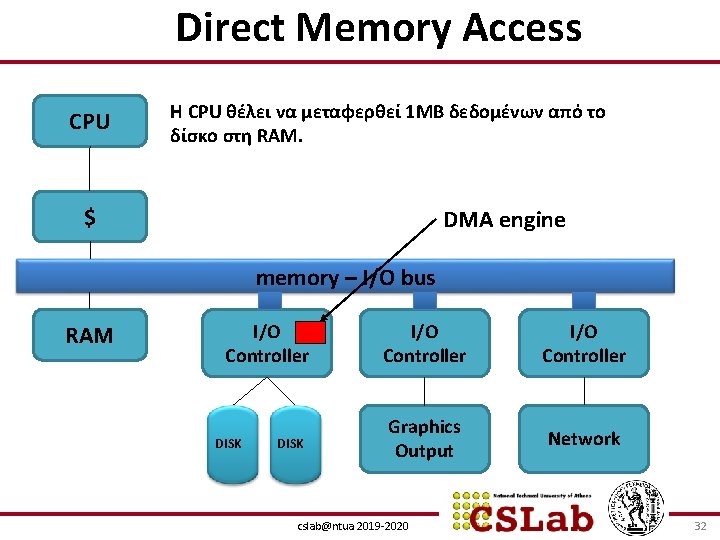

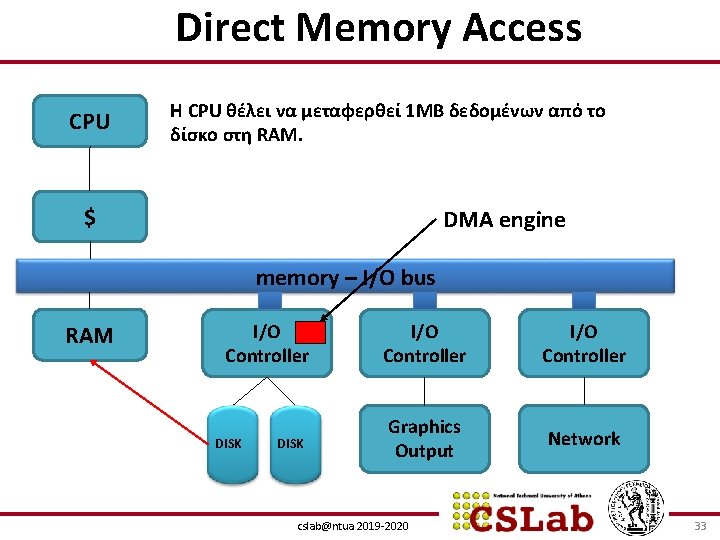

Direct Memory Access CPU H CPU θέλει να μεταφερθεί 1 MB δεδομένων από το δίσκο στη RAM. $ DMA engine memory – I/O bus RAM I/O Controller DISK I/O Controller Graphics Output Network cslab@ntua 2019 -2020 32

Direct Memory Access CPU H CPU θέλει να μεταφερθεί 1 MB δεδομένων από το δίσκο στη RAM. $ DMA engine memory – I/O bus RAM I/O Controller DISK I/O Controller Graphics Output Network cslab@ntua 2019 -2020 33

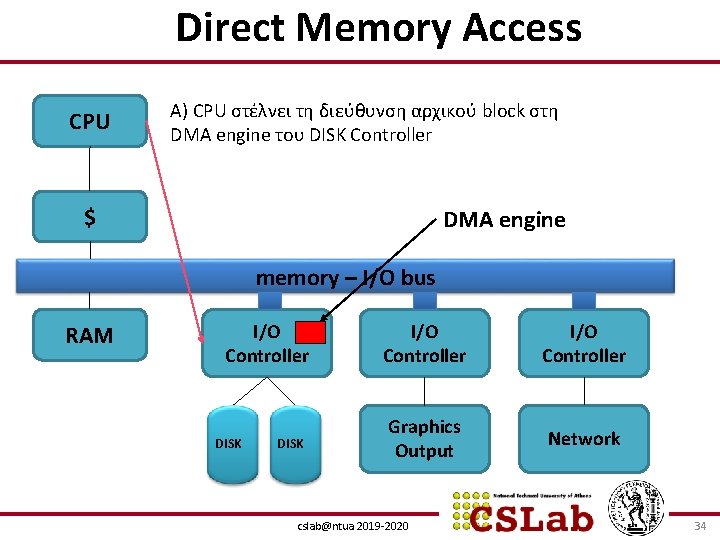

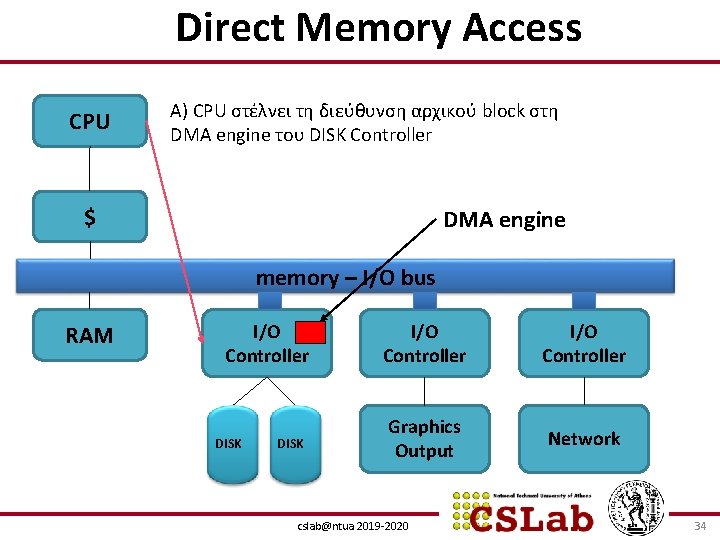

Direct Memory Access CPU Α) CPU στέλνει τη διεύθυνση αρχικού block στη DMA engine του DISK Controller $ DMA engine memory – I/O bus RAM I/O Controller DISK I/O Controller Graphics Output Network cslab@ntua 2019 -2020 34

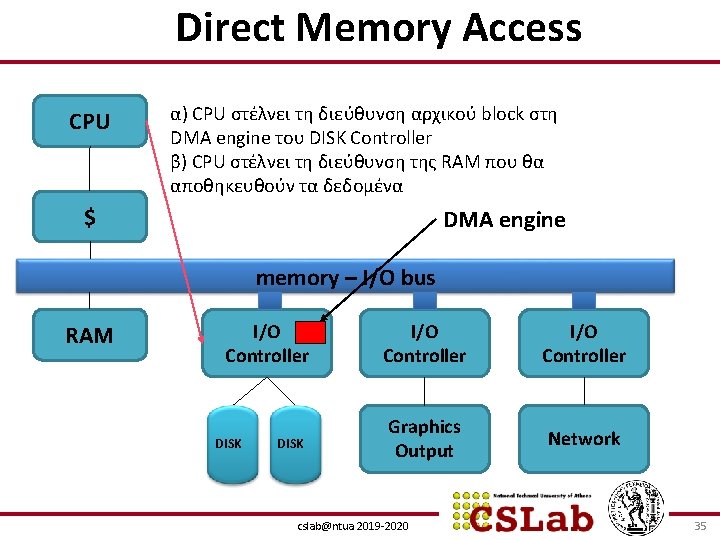

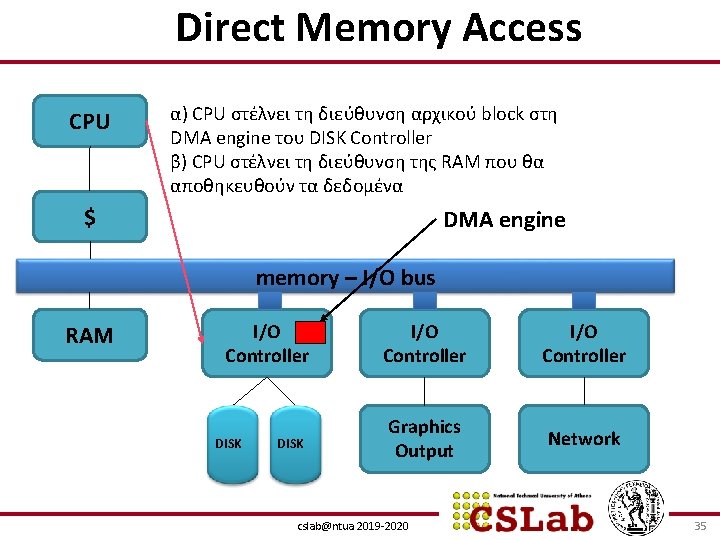

Direct Memory Access CPU α) CPU στέλνει τη διεύθυνση αρχικού block στη DMA engine του DISK Controller β) CPU στέλνει τη διεύθυνση της RAM που θα αποθηκευθούν τα δεδομένα $ DMA engine memory – I/O bus RAM I/O Controller DISK I/O Controller Graphics Output Network cslab@ntua 2019 -2020 35

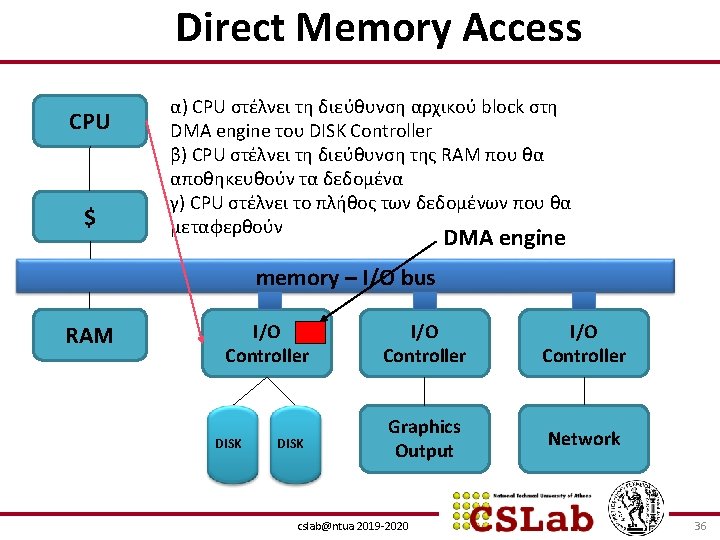

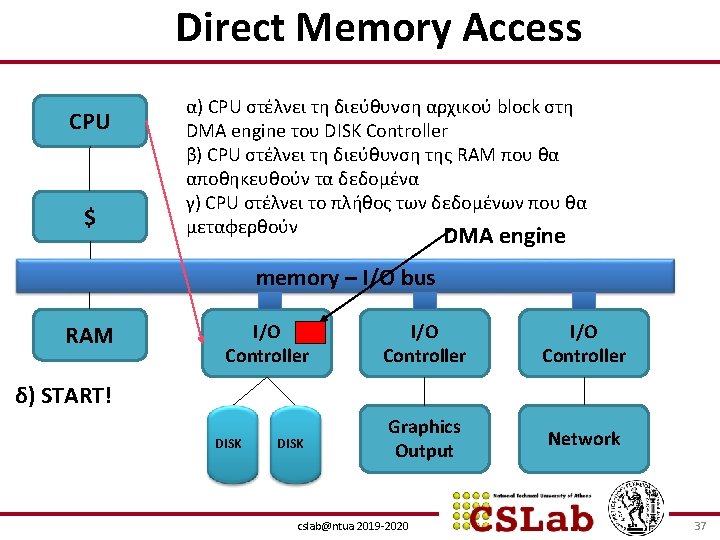

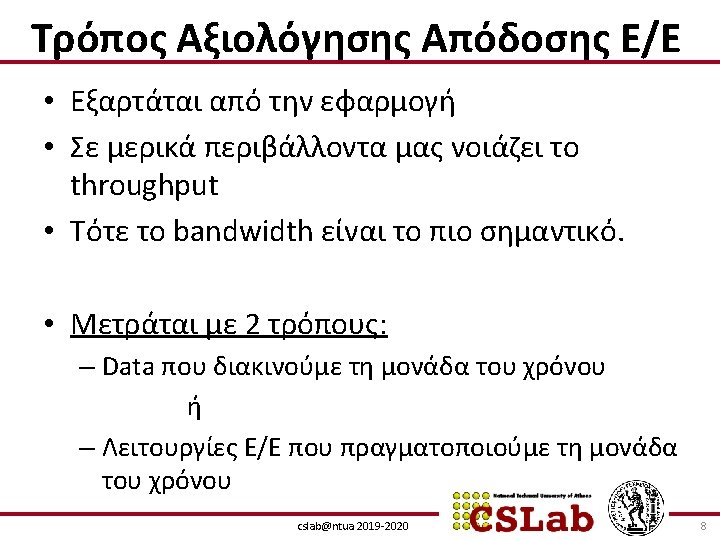

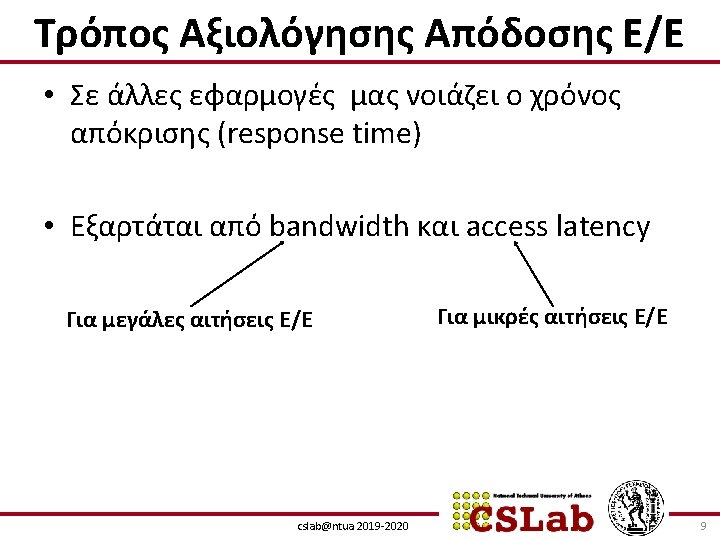

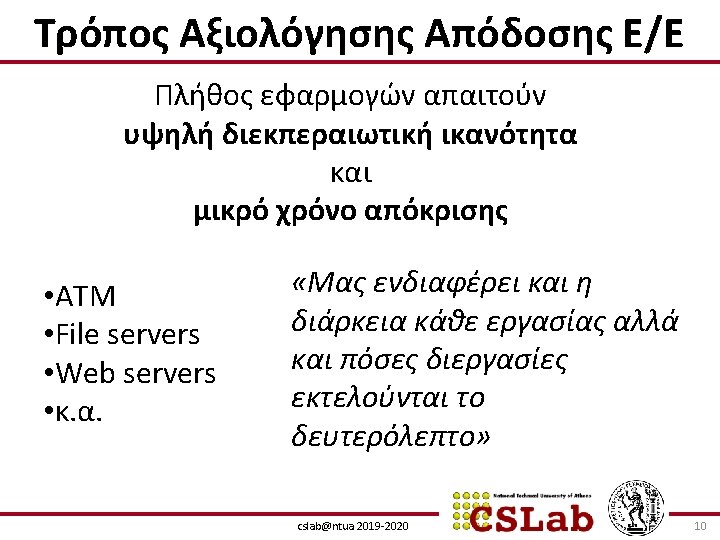

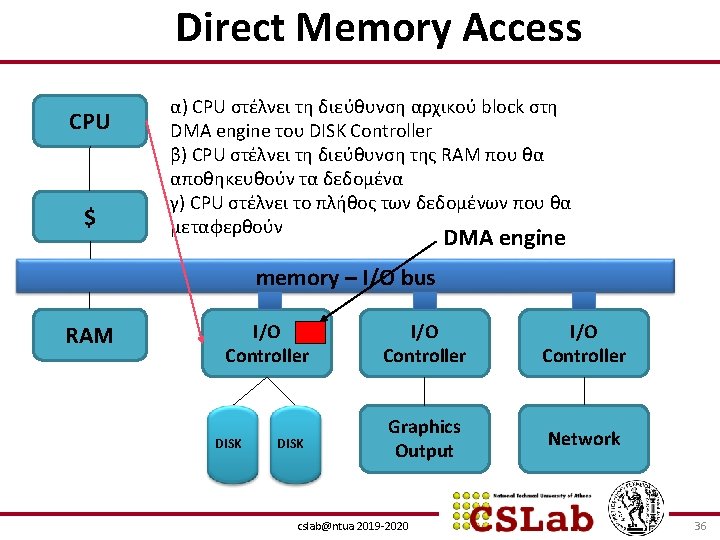

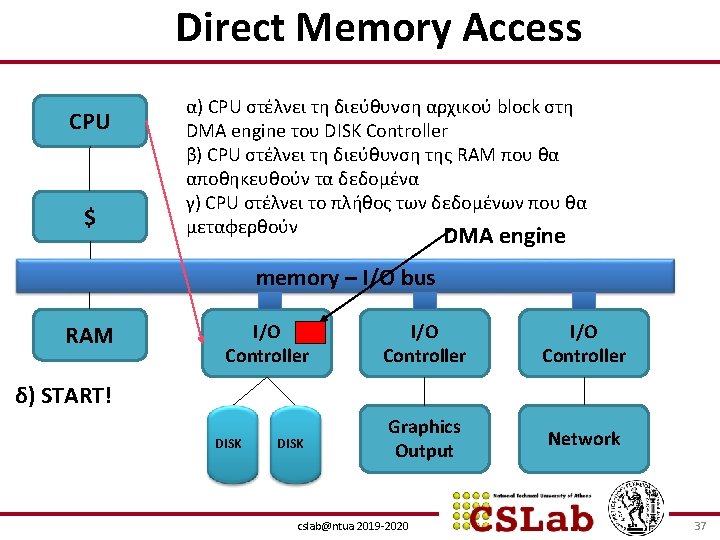

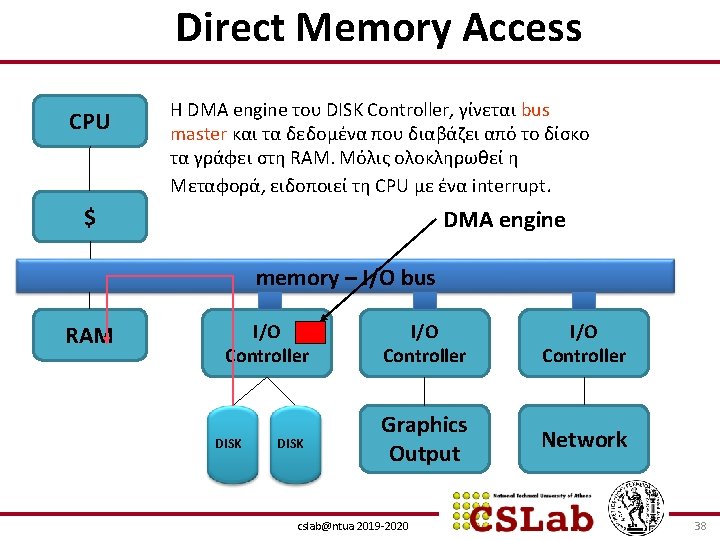

Direct Memory Access CPU $ α) CPU στέλνει τη διεύθυνση αρχικού block στη DMA engine του DISK Controller β) CPU στέλνει τη διεύθυνση της RAM που θα αποθηκευθούν τα δεδομένα γ) CPU στέλνει το πλήθος των δεδομένων που θα μεταφερθούν DMA engine memory – I/O bus RAM I/O Controller DISK I/O Controller Graphics Output Network cslab@ntua 2019 -2020 36

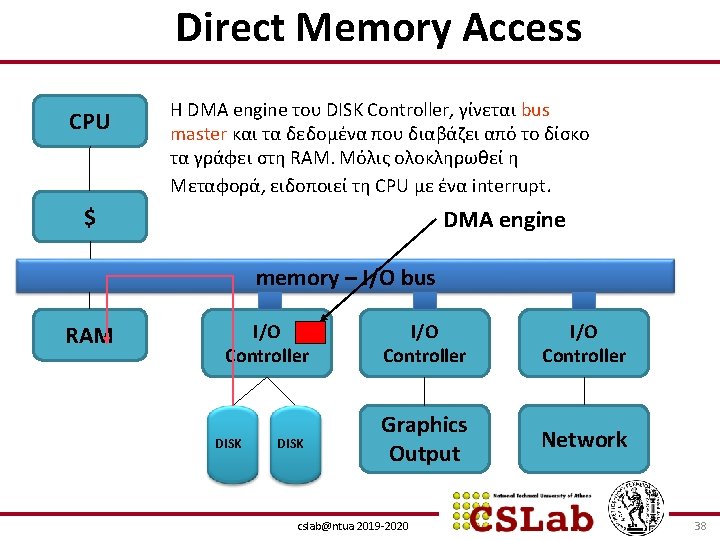

Direct Memory Access CPU H DMA engine του DISK Controller, γίνεται bus master και τα δεδομένα που διαβάζει από το δίσκο τα γράφει στη RAM. Μόλις ολοκληρωθεί η Μεταφορά, ειδοποιεί τη CPU με ένα interrupt. $ DMA engine memory – I/O bus RAM I/O Controller DISK I/O Controller Graphics Output Network cslab@ntua 2019 -2020 38

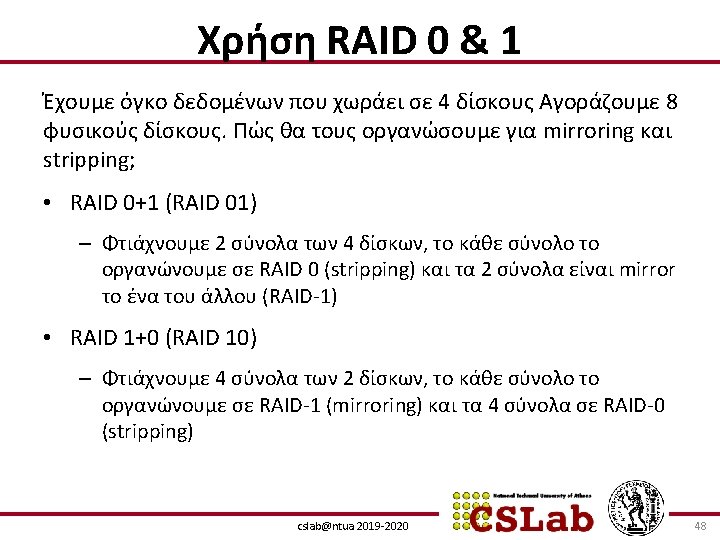

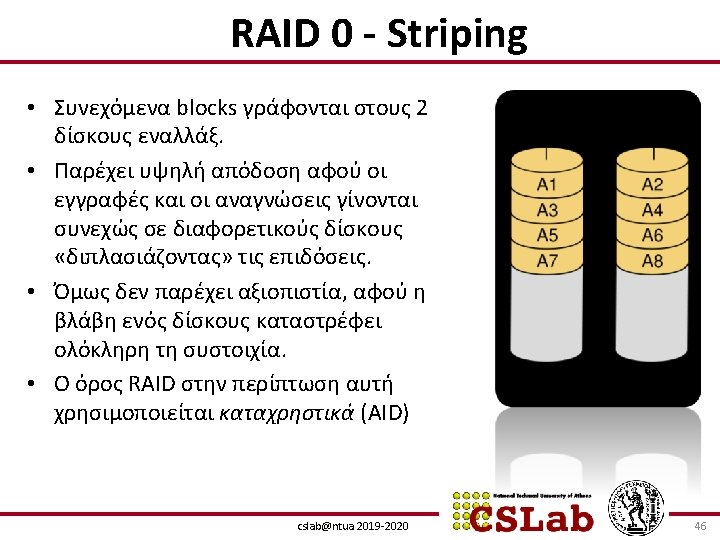

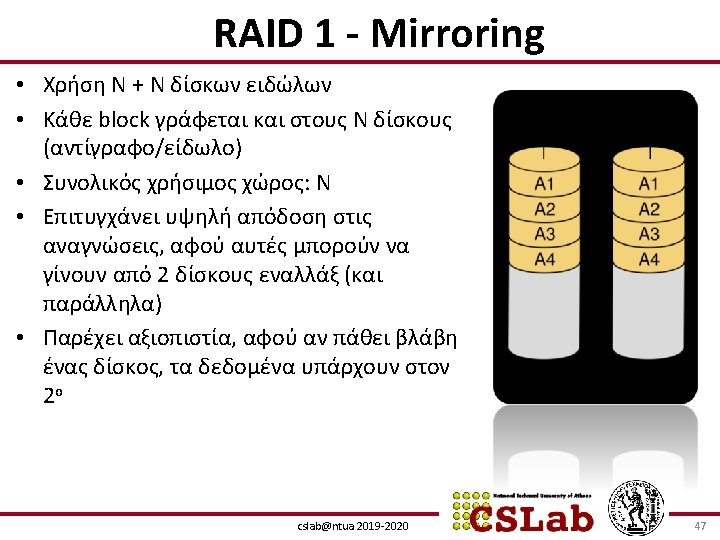

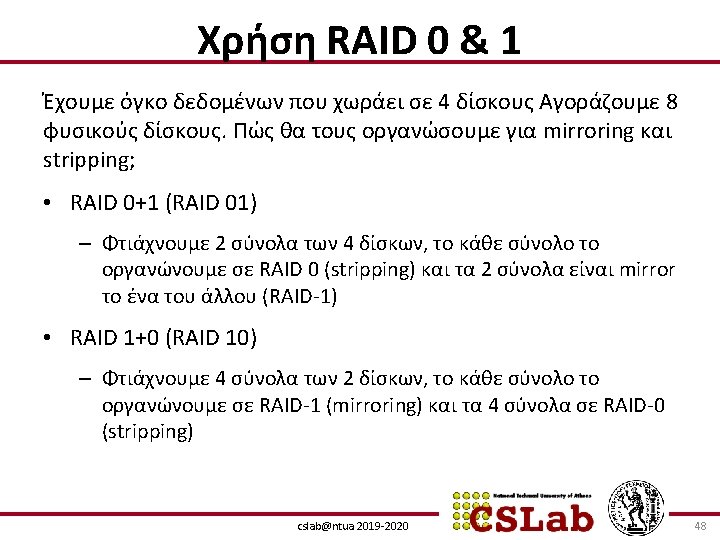

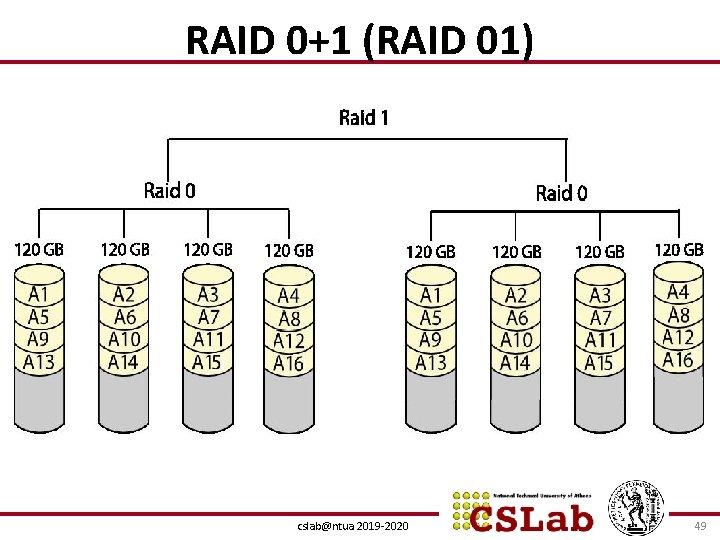

RAID 0+1 (RAID 01) cslab@ntua 2019 -2020 49

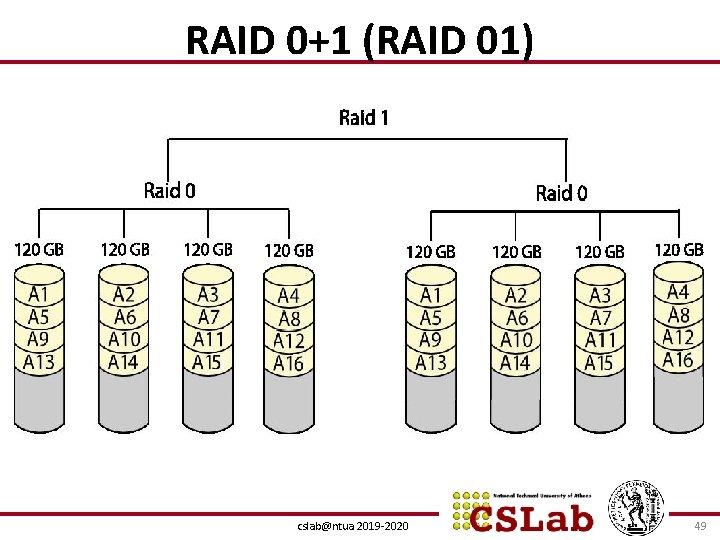

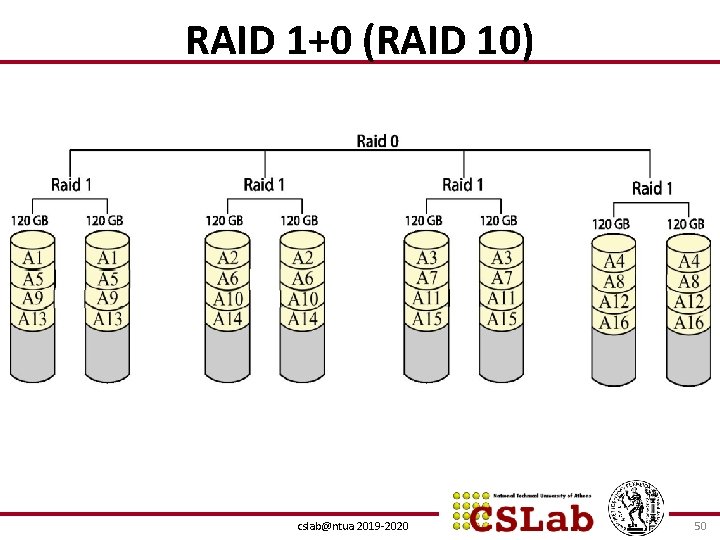

RAID 1+0 (RAID 10) cslab@ntua 2019 -2020 50

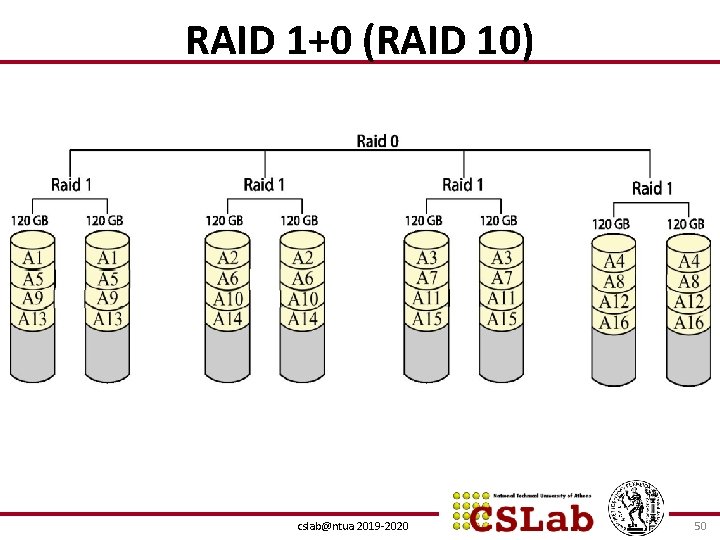

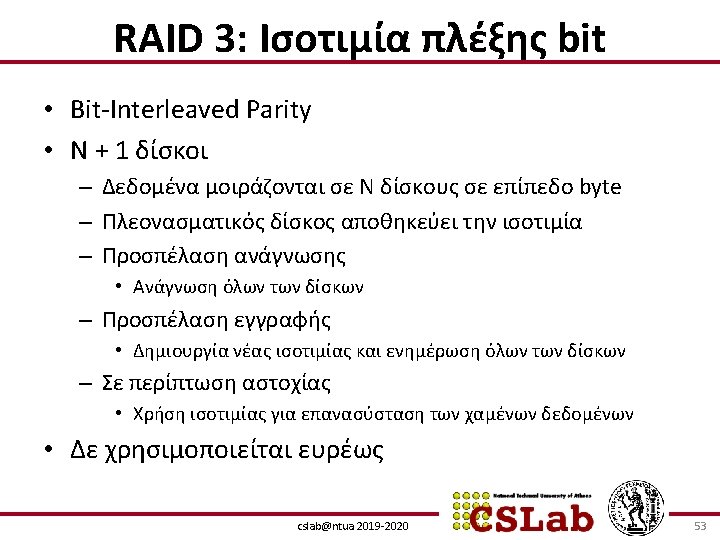

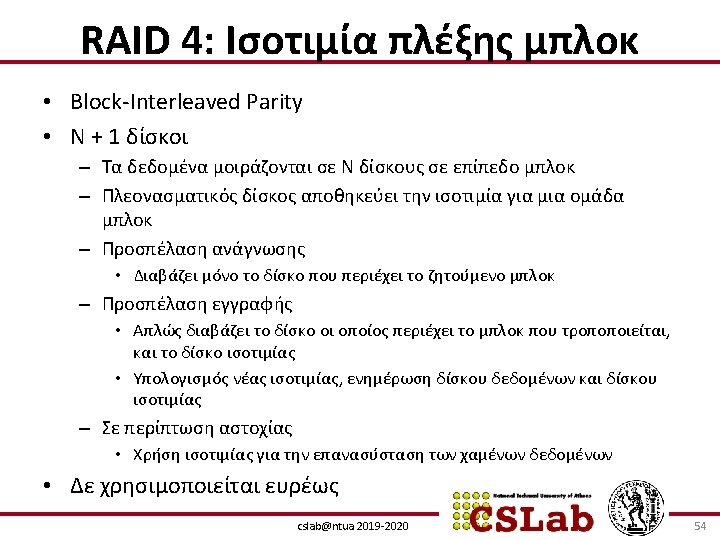

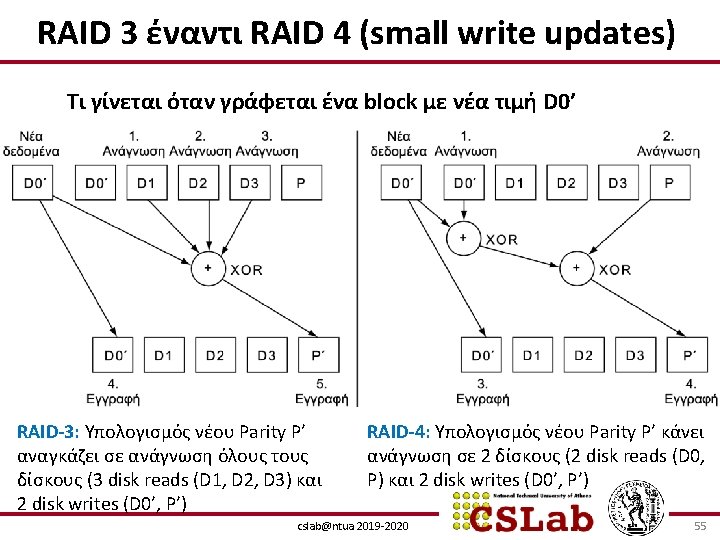

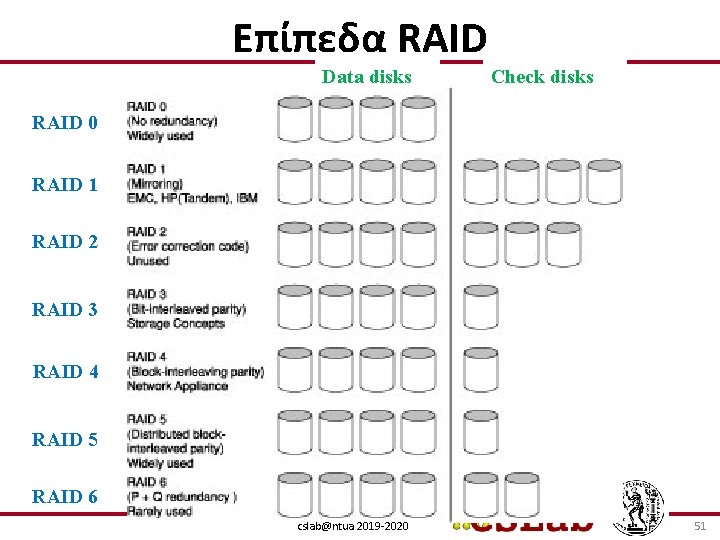

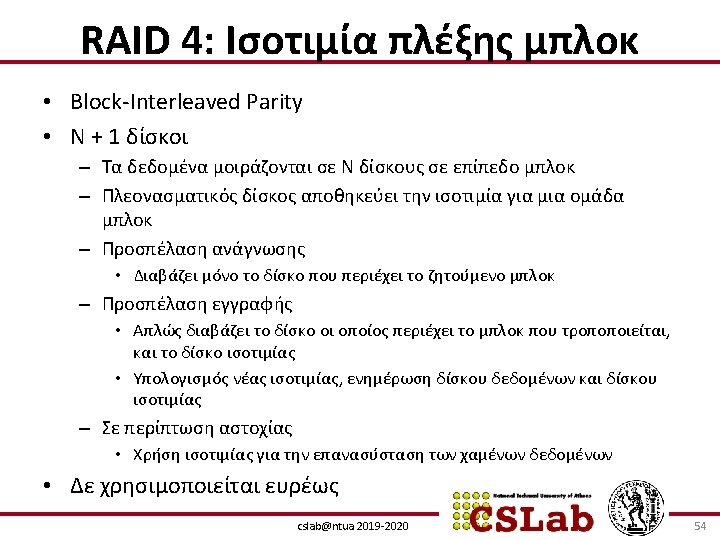

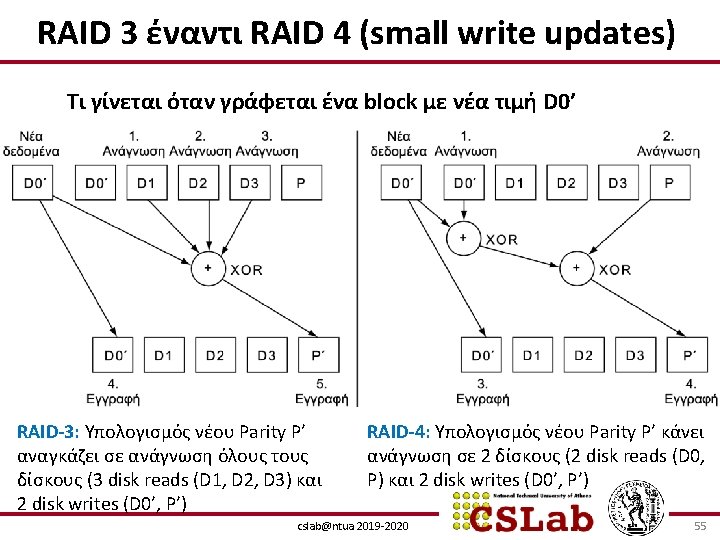

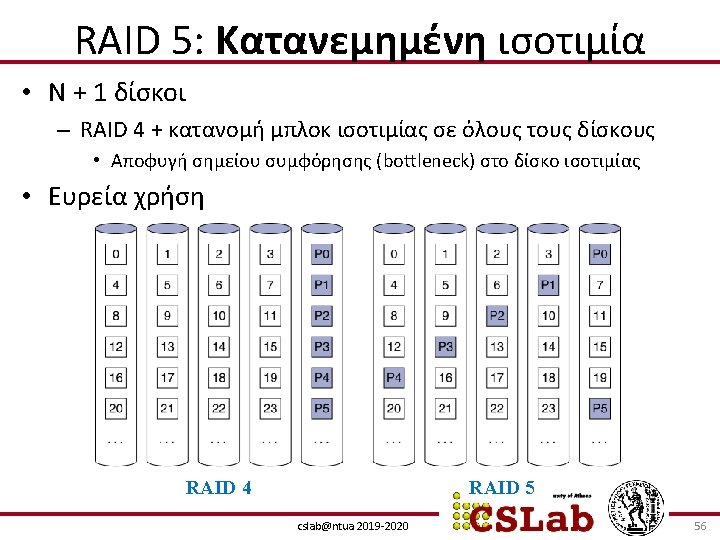

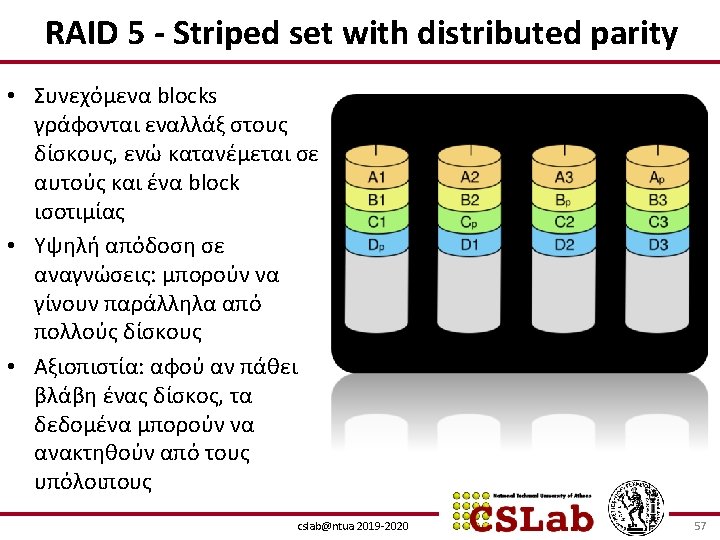

Επίπεδα RAID Data disks Check disks RAID 0 RAID 1 RAID 2 RAID 3 RAID 4 RAID 5 RAID 6 cslab@ntua 2019 -2020 51

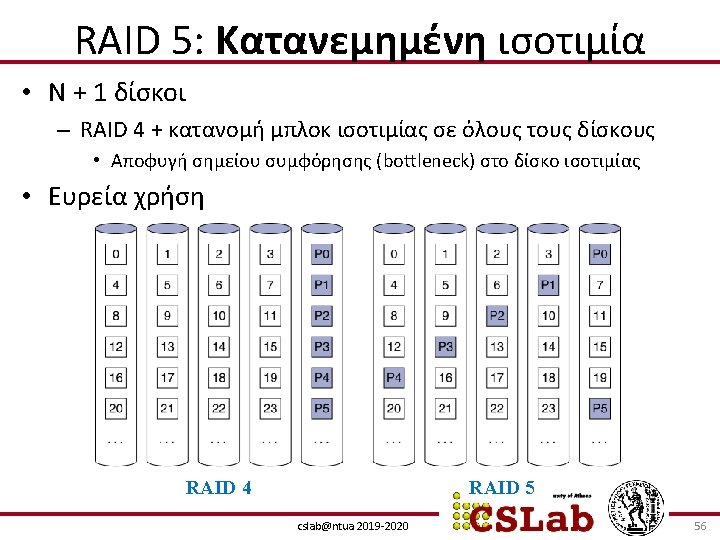

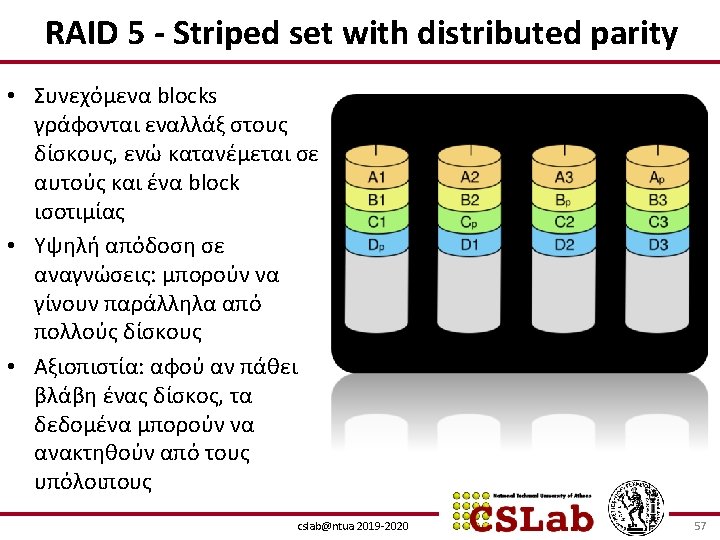

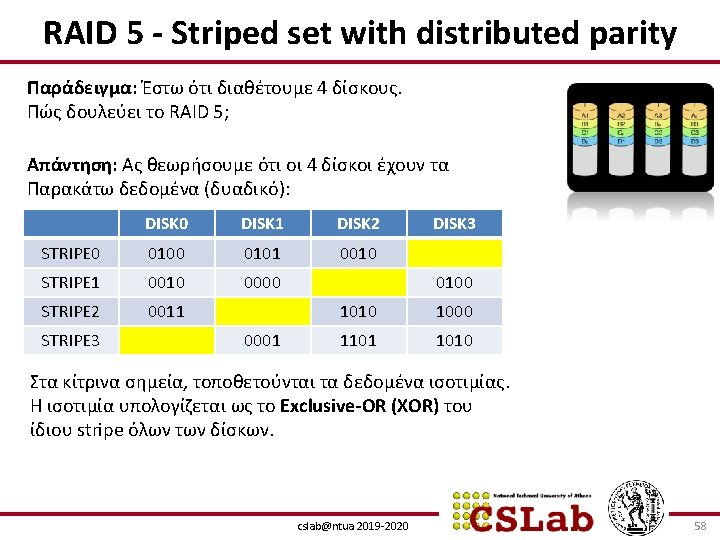

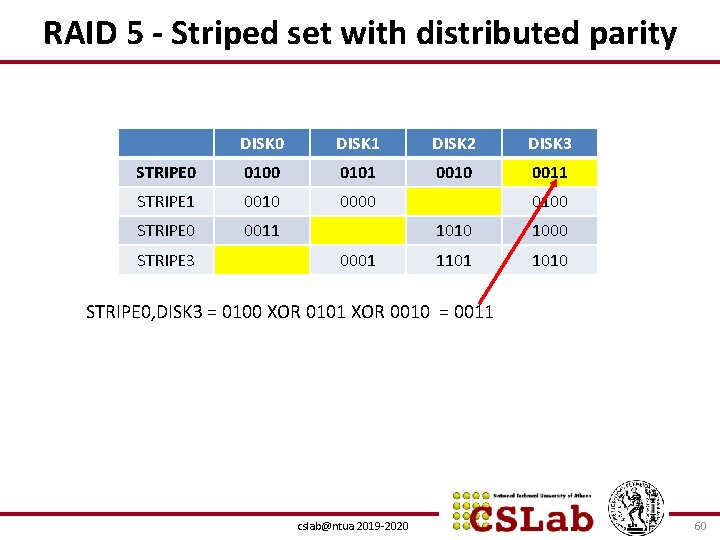

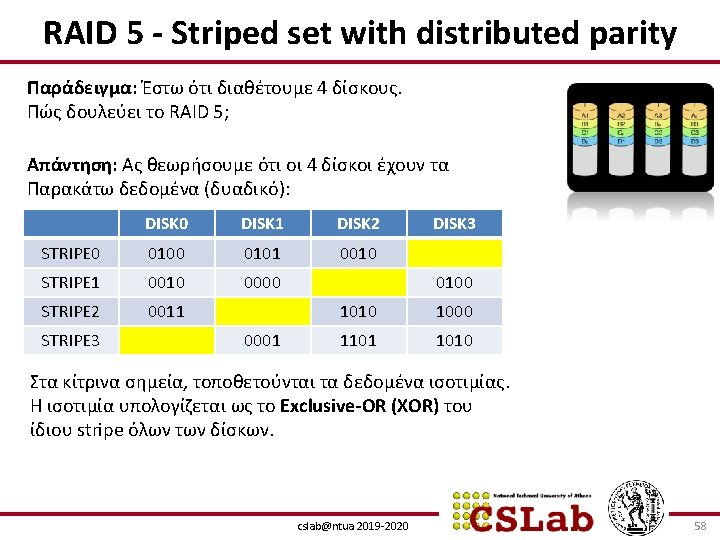

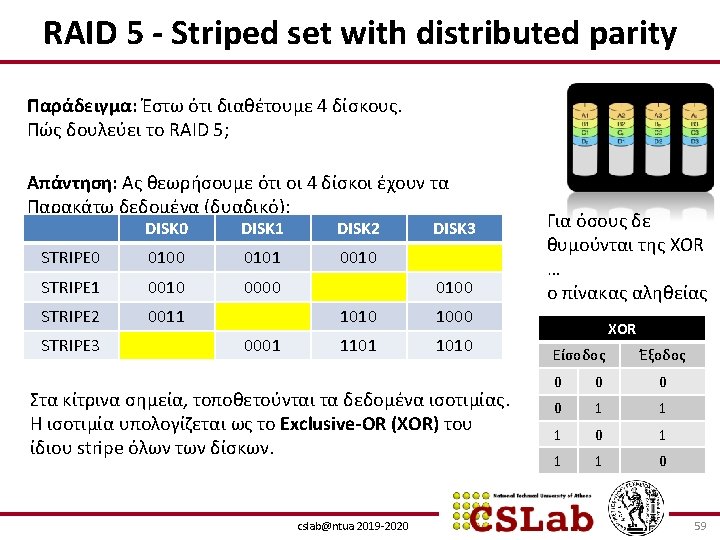

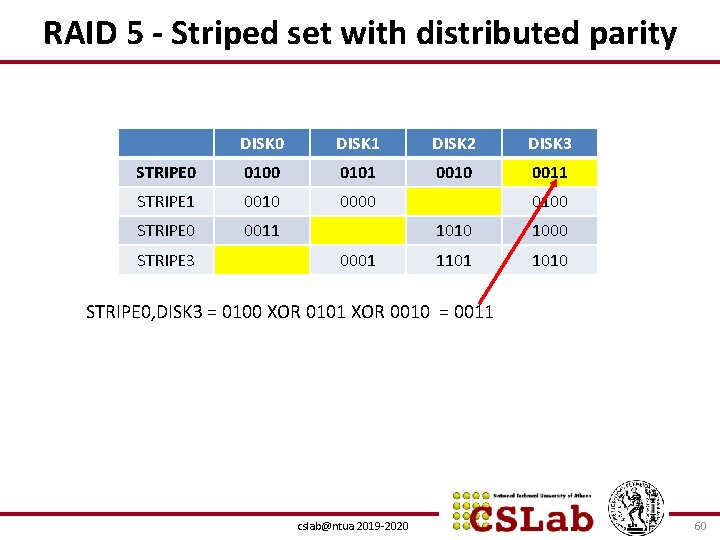

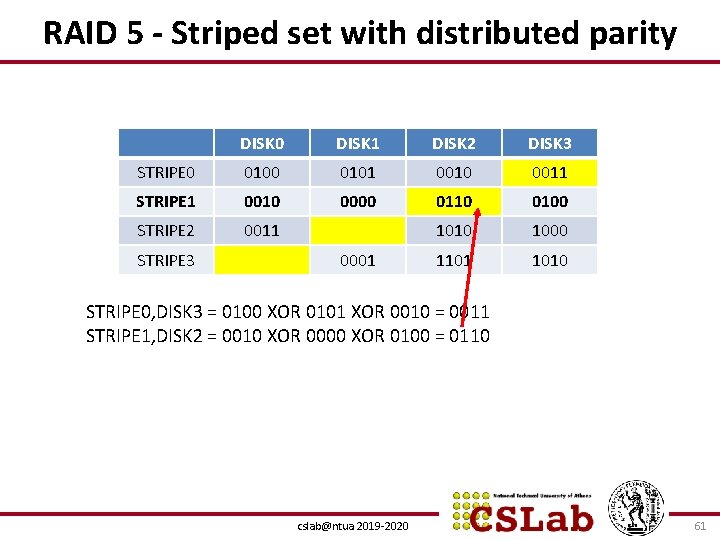

RAID 5 - Striped set with distributed parity DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 0010 0011 STRIPE 1 0010 0000 STRIPE 0 0011 STRIPE 3 0001 0100 1010 1000 1101 1010 STRIPE 0, DISK 3 = 0100 XOR 0101 XOR 0010 = 0011 cslab@ntua 2019 -2020 60

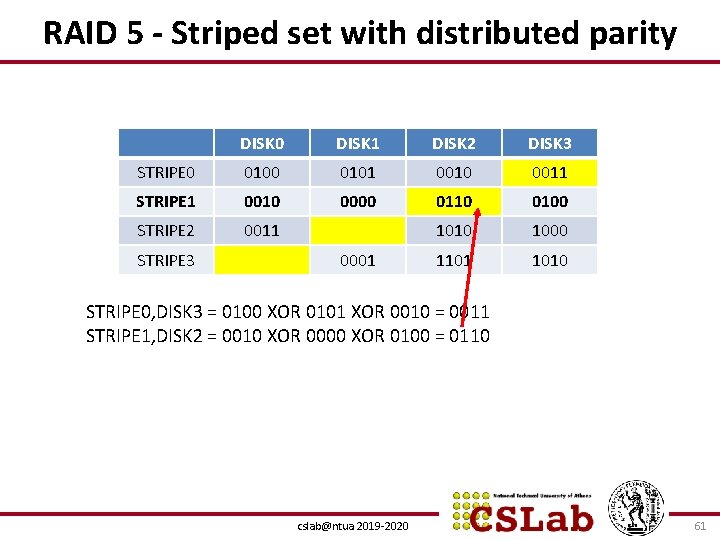

RAID 5 - Striped set with distributed parity DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 0010 0011 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 1010 1000 1101 1010 STRIPE 3 0001 STRIPE 0, DISK 3 = 0100 XOR 0101 XOR 0010 = 0011 STRIPE 1, DISK 2 = 0010 XOR 0000 XOR 0100 = 0110 cslab@ntua 2019 -2020 61

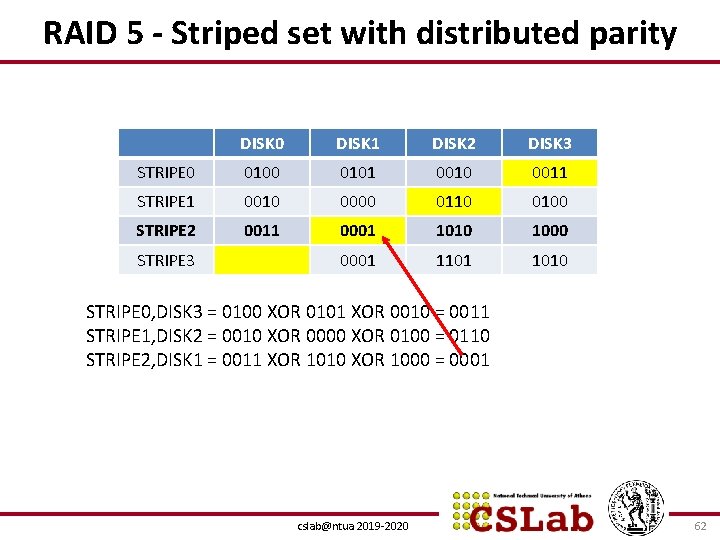

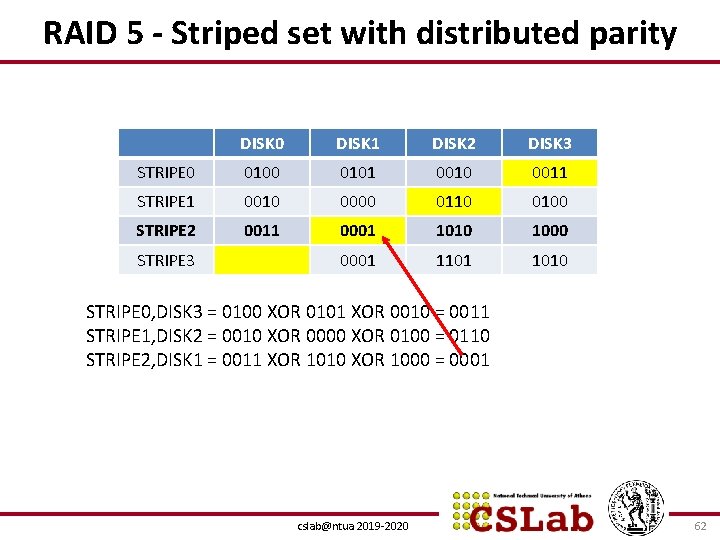

RAID 5 - Striped set with distributed parity DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 0010 0011 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 0001 1101 1010 STRIPE 3 STRIPE 0, DISK 3 = 0100 XOR 0101 XOR 0010 = 0011 STRIPE 1, DISK 2 = 0010 XOR 0000 XOR 0100 = 0110 STRIPE 2, DISK 1 = 0011 XOR 1010 XOR 1000 = 0001 cslab@ntua 2019 -2020 62

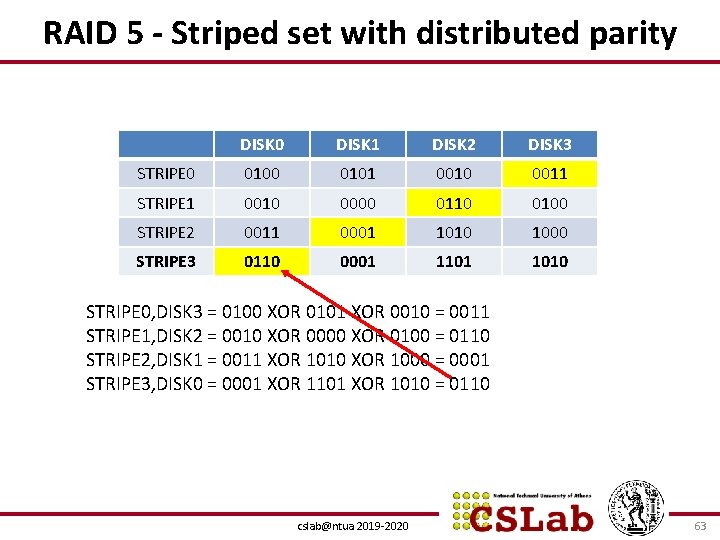

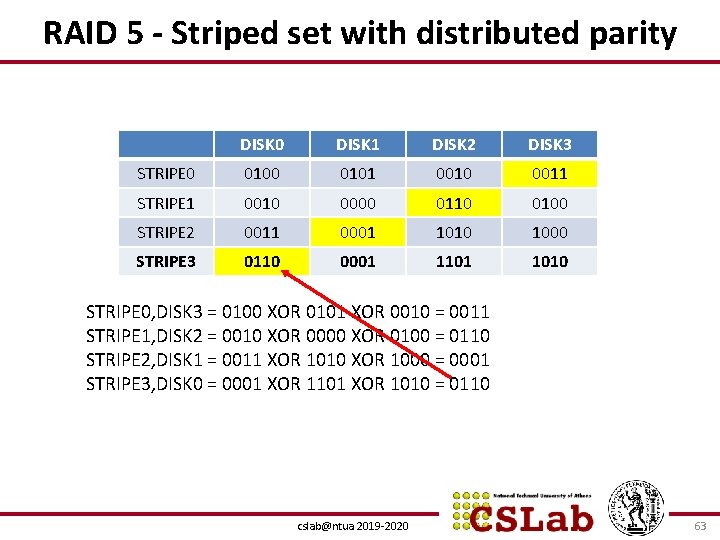

RAID 5 - Striped set with distributed parity DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 0010 0011 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 STRIPE 0, DISK 3 = 0100 XOR 0101 XOR 0010 = 0011 STRIPE 1, DISK 2 = 0010 XOR 0000 XOR 0100 = 0110 STRIPE 2, DISK 1 = 0011 XOR 1010 XOR 1000 = 0001 STRIPE 3, DISK 0 = 0001 XOR 1101 XOR 1010 = 0110 cslab@ntua 2019 -2020 63

RAID 5 - Striped set with distributed parity Τελική Εικόνα της συστοιχίας ΔΙΣΚΩΝ με διάταξη RAID 5 DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 0010 0011 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 cslab@ntua 2019 -2020 64

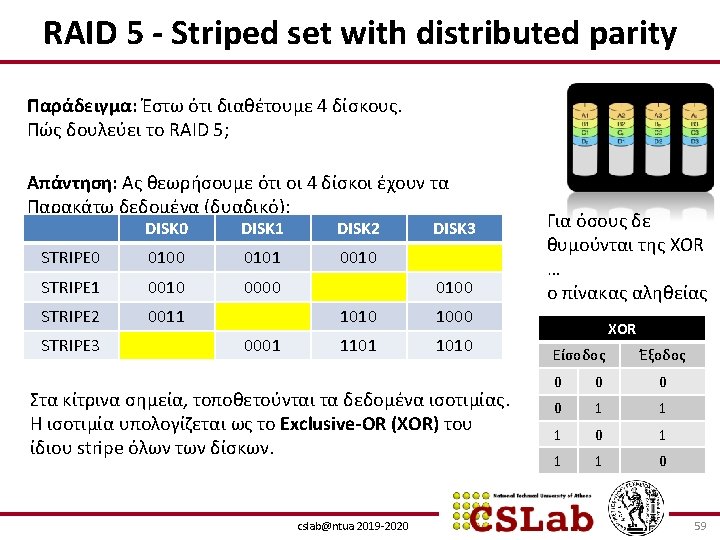

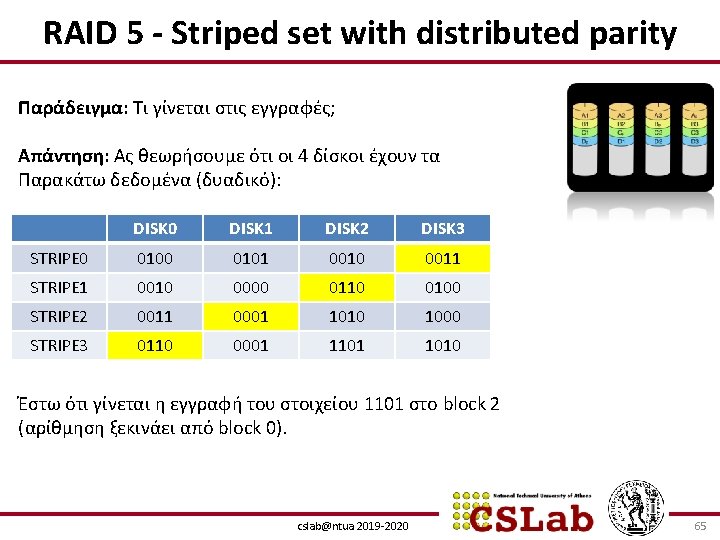

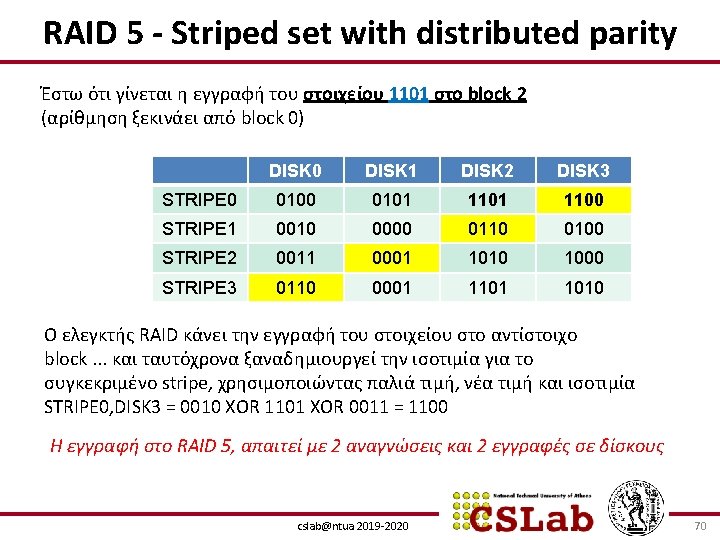

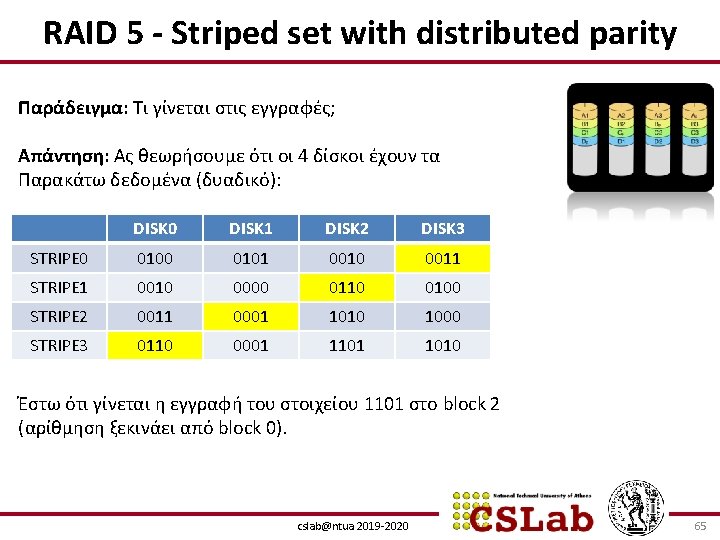

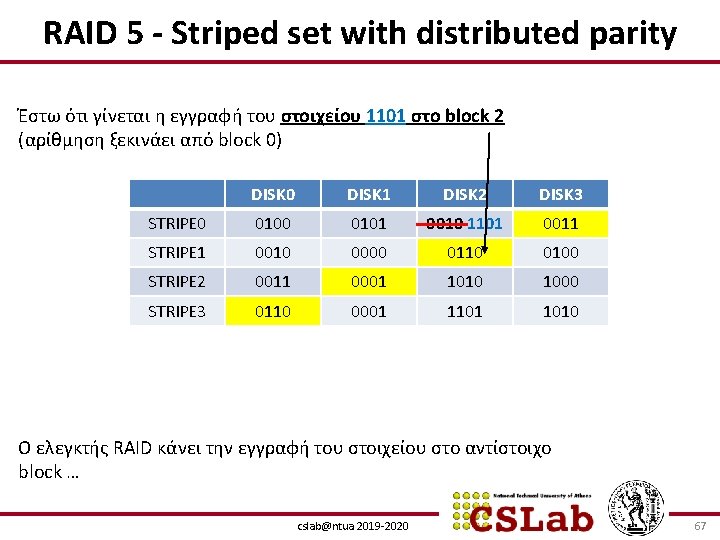

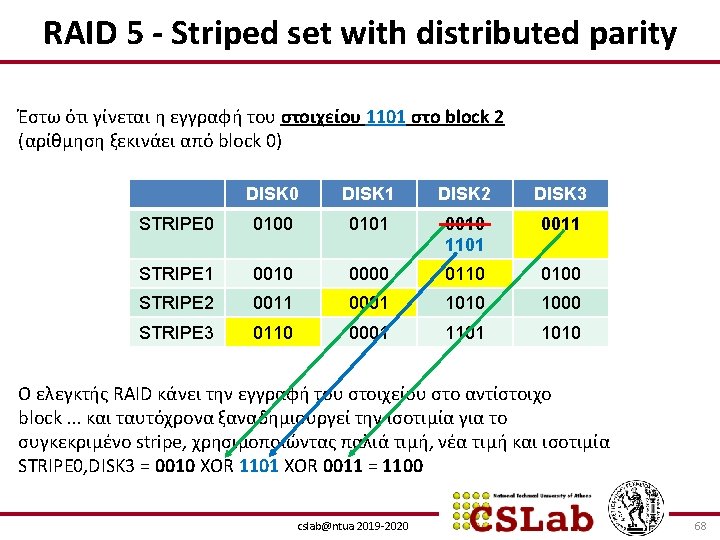

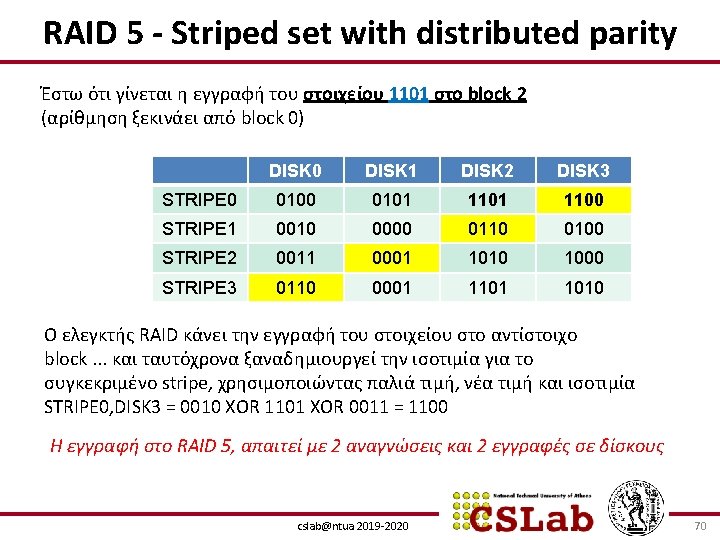

RAID 5 - Striped set with distributed parity Παράδειγμα: Τι γίνεται στις εγγραφές; Απάντηση: Ας θεωρήσουμε ότι οι 4 δίσκοι έχουν τα Παρακάτω δεδομένα (δυαδικό): DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 0010 0011 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 Έστω ότι γίνεται η εγγραφή του στοιχείου 1101 στο block 2 (αρίθμηση ξεκινάει από block 0). cslab@ntua 2019 -2020 65

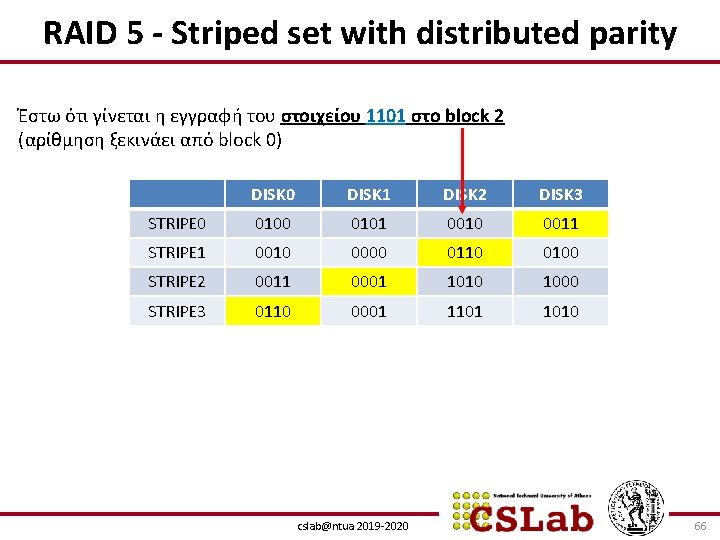

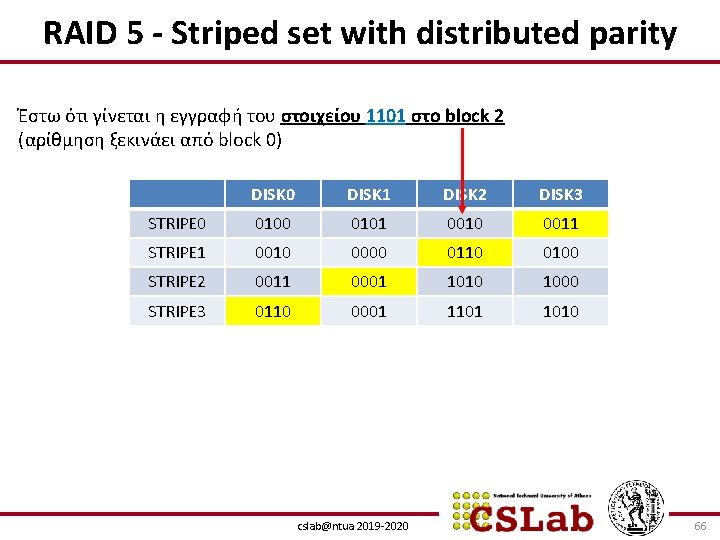

RAID 5 - Striped set with distributed parity Έστω ότι γίνεται η εγγραφή του στοιχείου 1101 στο block 2 (αρίθμηση ξεκινάει από block 0) DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 0010 0011 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 cslab@ntua 2019 -2020 66

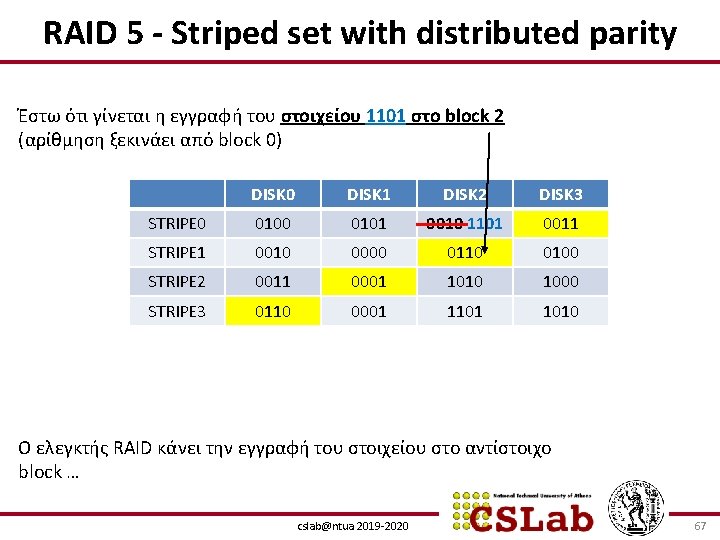

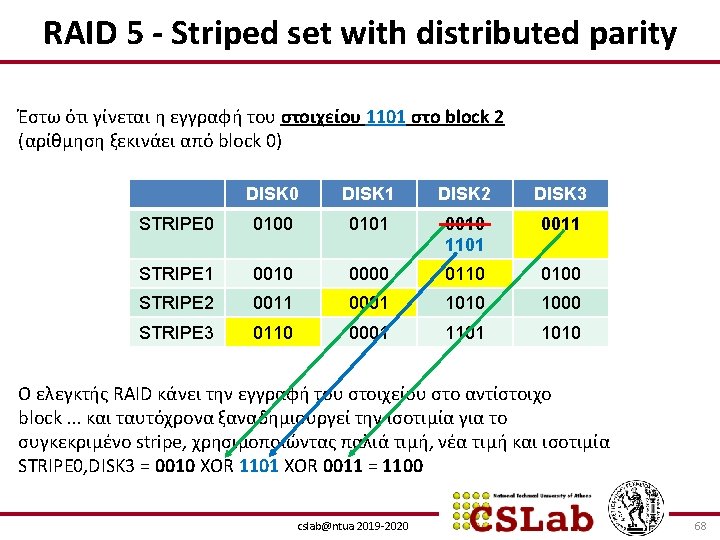

RAID 5 - Striped set with distributed parity Έστω ότι γίνεται η εγγραφή του στοιχείου 1101 στο block 2 (αρίθμηση ξεκινάει από block 0) DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 0010 1101 0011 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 Ο ελεγκτής RAID κάνει την εγγραφή του στοιχείου στο αντίστοιχο block … cslab@ntua 2019 -2020 67

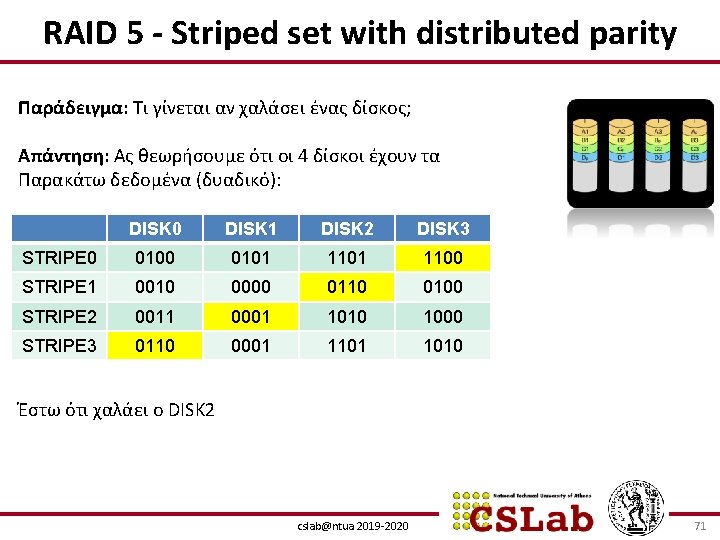

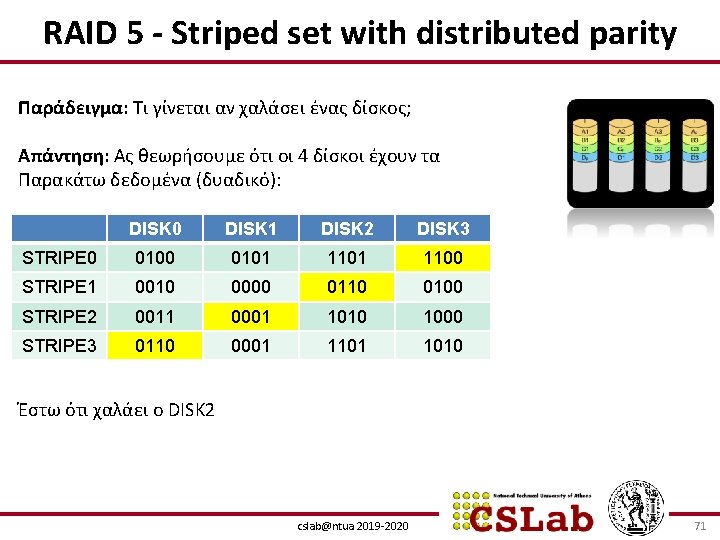

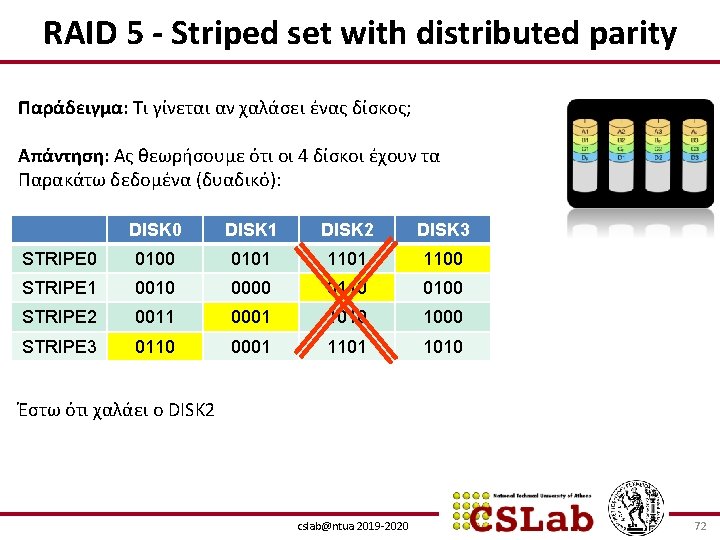

RAID 5 - Striped set with distributed parity Παράδειγμα: Τι γίνεται αν χαλάσει ένας δίσκος; Απάντηση: Ας θεωρήσουμε ότι οι 4 δίσκοι έχουν τα Παρακάτω δεδομένα (δυαδικό): DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 1100 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 Έστω ότι χαλάει ο DISK 2 cslab@ntua 2019 -2020 71

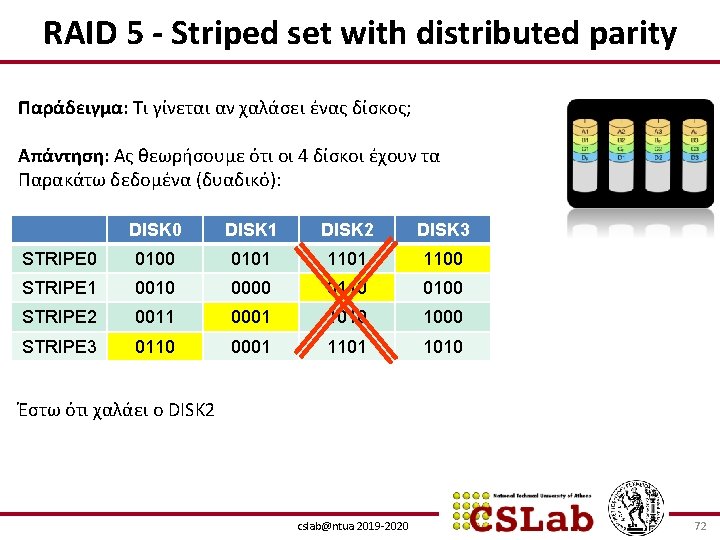

RAID 5 - Striped set with distributed parity Παράδειγμα: Τι γίνεται αν χαλάσει ένας δίσκος; Απάντηση: Ας θεωρήσουμε ότι οι 4 δίσκοι έχουν τα Παρακάτω δεδομένα (δυαδικό): DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 1100 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 Έστω ότι χαλάει ο DISK 2 cslab@ntua 2019 -2020 72

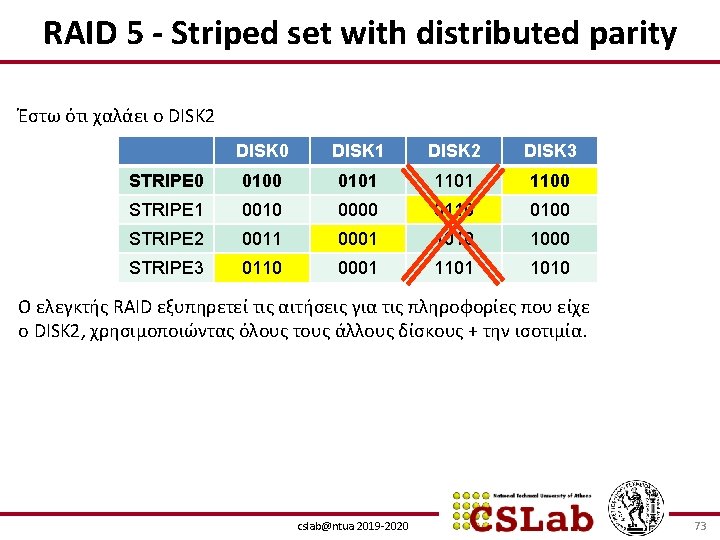

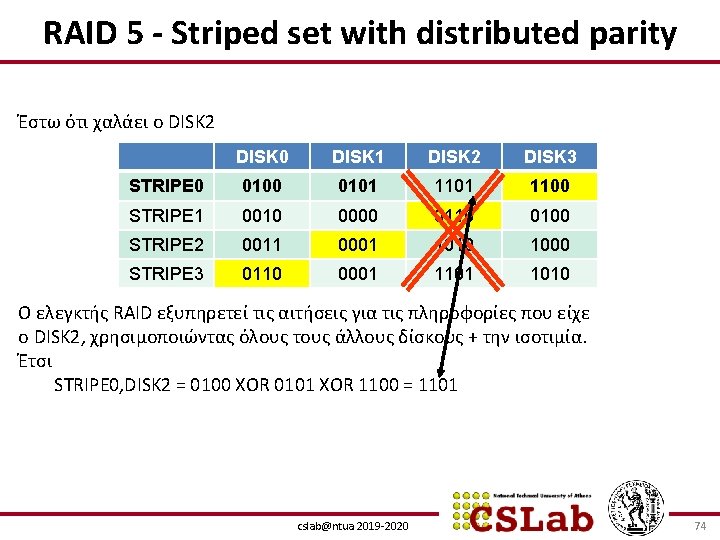

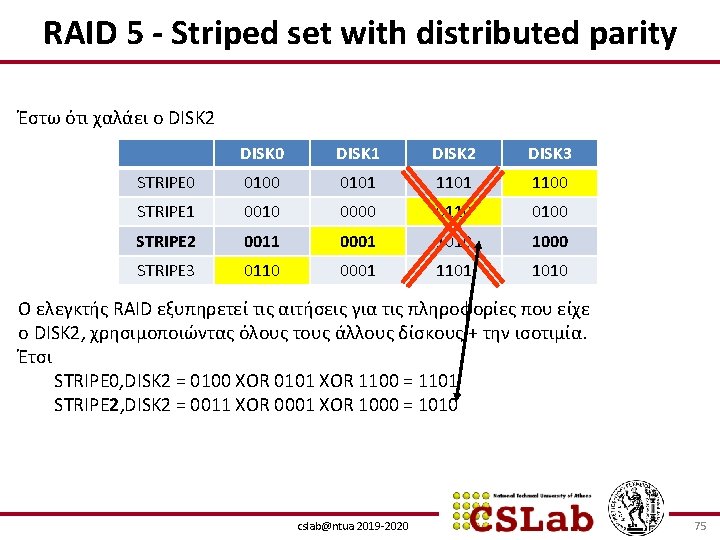

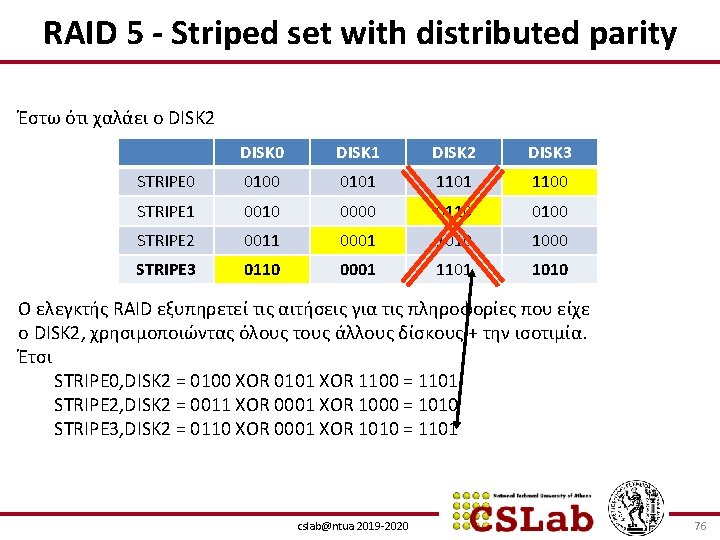

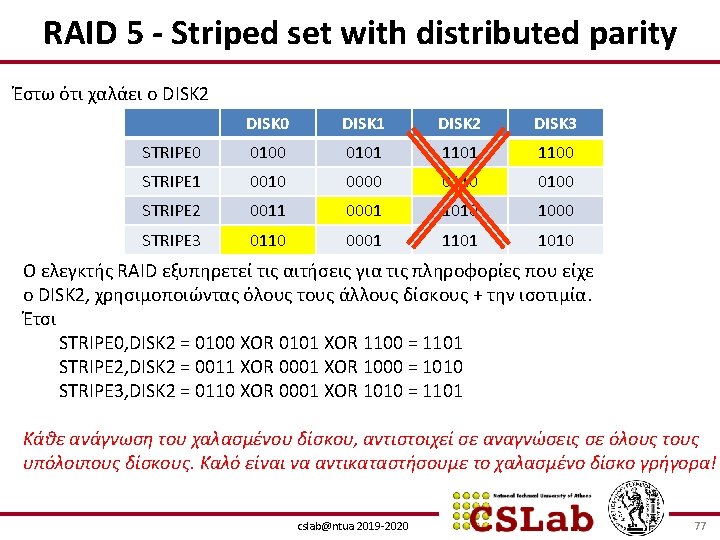

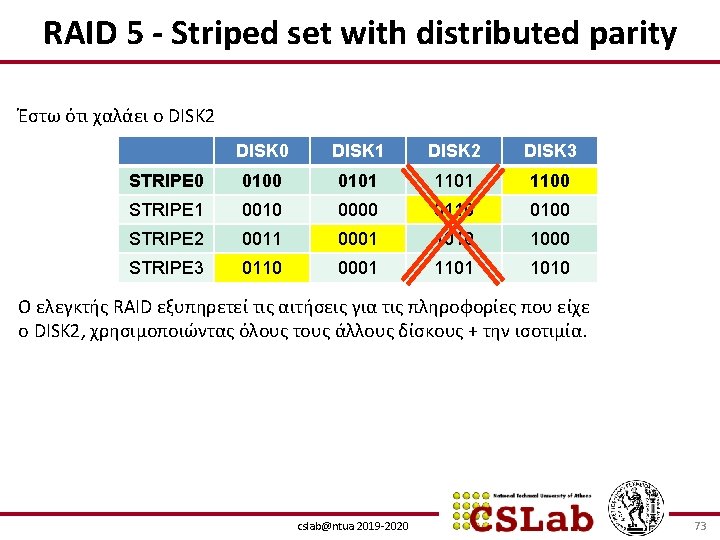

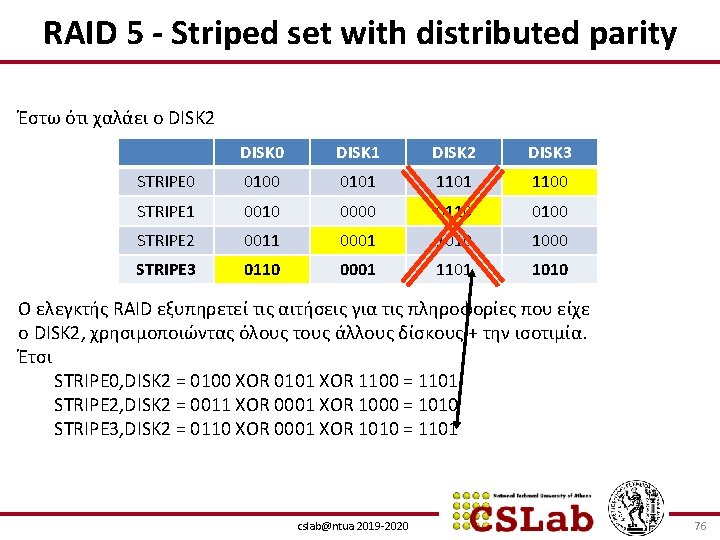

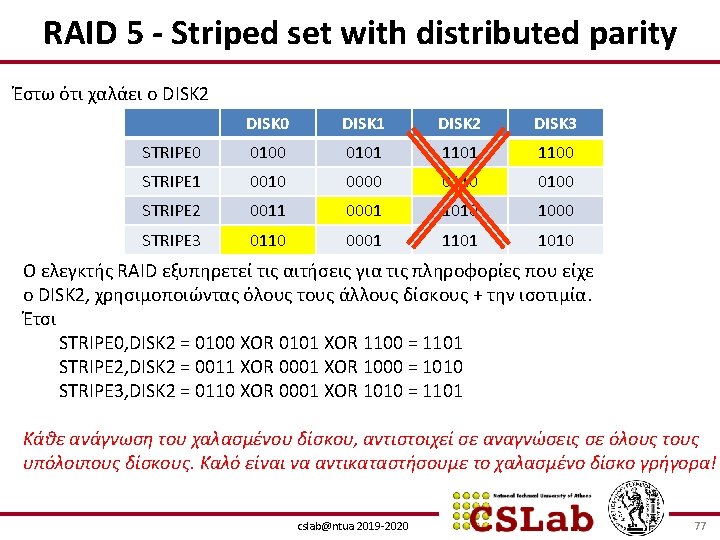

RAID 5 - Striped set with distributed parity Έστω ότι χαλάει ο DISK 2 DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 1100 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 Ο ελεγκτής RAID εξυπηρετεί τις αιτήσεις για τις πληροφορίες που είχε ο DISK 2, χρησιμοποιώντας όλους τους άλλους δίσκους + την ισοτιμία. cslab@ntua 2019 -2020 73

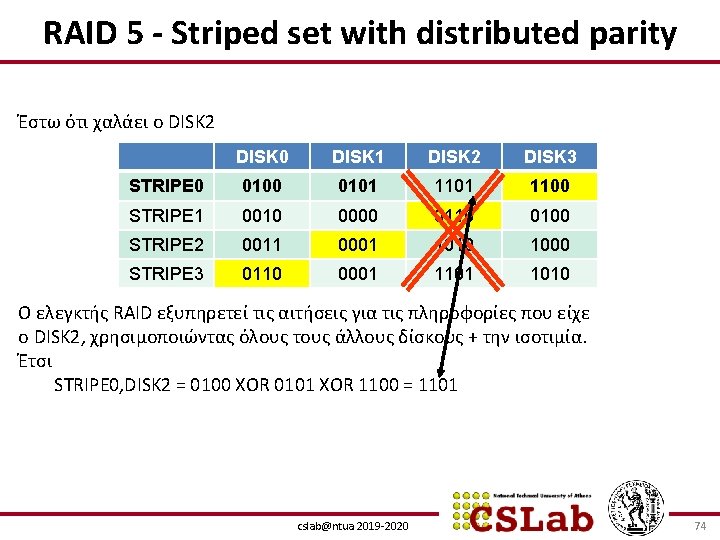

RAID 5 - Striped set with distributed parity Έστω ότι χαλάει ο DISK 2 DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 1100 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 Ο ελεγκτής RAID εξυπηρετεί τις αιτήσεις για τις πληροφορίες που είχε ο DISK 2, χρησιμοποιώντας όλους τους άλλους δίσκους + την ισοτιμία. Έτσι STRIPE 0, DISK 2 = 0100 XOR 0101 XOR 1100 = 1101 cslab@ntua 2019 -2020 74

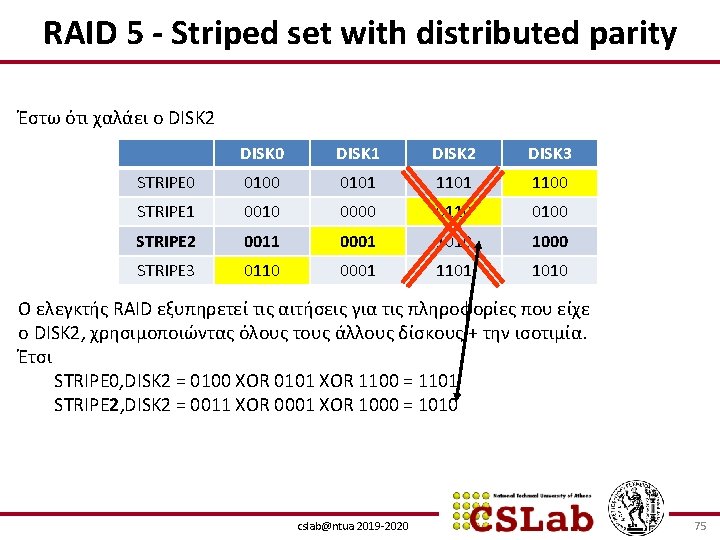

RAID 5 - Striped set with distributed parity Έστω ότι χαλάει ο DISK 2 DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 1100 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 Ο ελεγκτής RAID εξυπηρετεί τις αιτήσεις για τις πληροφορίες που είχε ο DISK 2, χρησιμοποιώντας όλους τους άλλους δίσκους + την ισοτιμία. Έτσι STRIPE 0, DISK 2 = 0100 XOR 0101 XOR 1100 = 1101 STRIPE 2, DISK 2 = 0011 XOR 0001 XOR 1000 = 1010 cslab@ntua 2019 -2020 75

RAID 5 - Striped set with distributed parity Έστω ότι χαλάει ο DISK 2 DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 1100 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 Ο ελεγκτής RAID εξυπηρετεί τις αιτήσεις για τις πληροφορίες που είχε ο DISK 2, χρησιμοποιώντας όλους τους άλλους δίσκους + την ισοτιμία. Έτσι STRIPE 0, DISK 2 = 0100 XOR 0101 XOR 1100 = 1101 STRIPE 2, DISK 2 = 0011 XOR 0001 XOR 1000 = 1010 STRIPE 3, DISK 2 = 0110 XOR 0001 XOR 1010 = 1101 cslab@ntua 2019 -2020 76

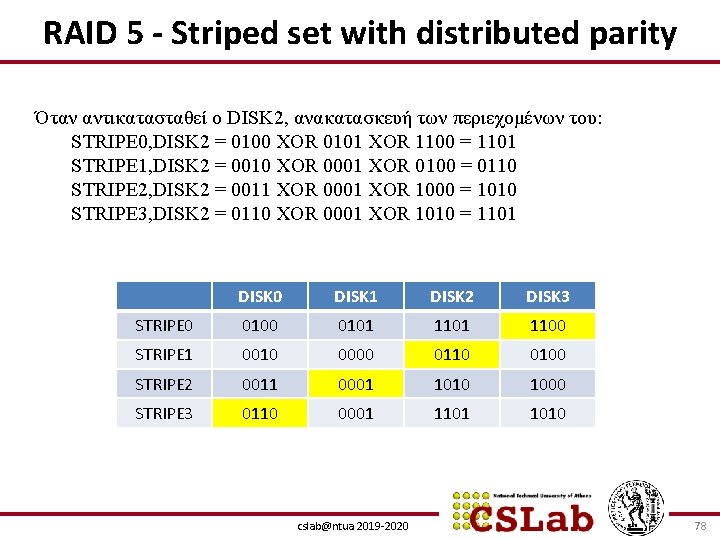

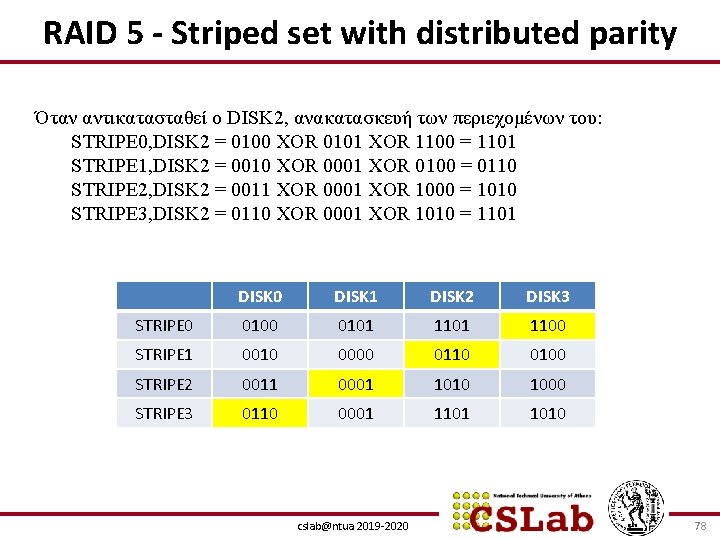

RAID 5 - Striped set with distributed parity Όταν αντικατασταθεί ο DISK 2, ανακατασκευή των περιεχομένων του: STRIPE 0, DISK 2 = 0100 XOR 0101 XOR 1100 = 1101 STRIPE 1, DISK 2 = 0010 XOR 0001 XOR 0100 = 0110 STRIPE 2, DISK 2 = 0011 XOR 0001 XOR 1000 = 1010 STRIPE 3, DISK 2 = 0110 XOR 0001 XOR 1010 = 1101 DISK 0 DISK 1 DISK 2 DISK 3 STRIPE 0 0101 1100 STRIPE 1 0010 0000 0110 0100 STRIPE 2 0011 0001 1010 1000 STRIPE 3 0110 0001 1101 1010 cslab@ntua 2019 -2020 78

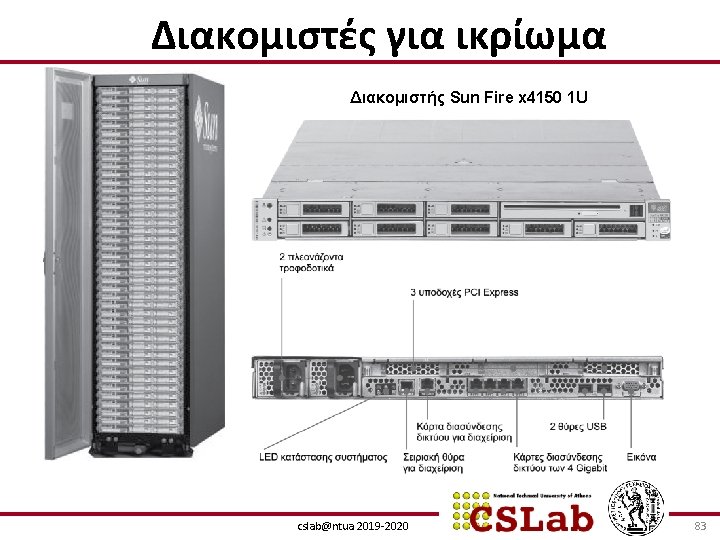

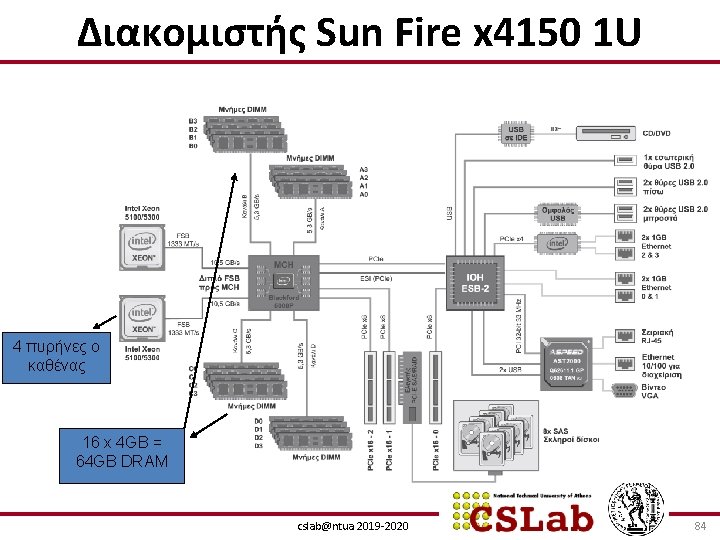

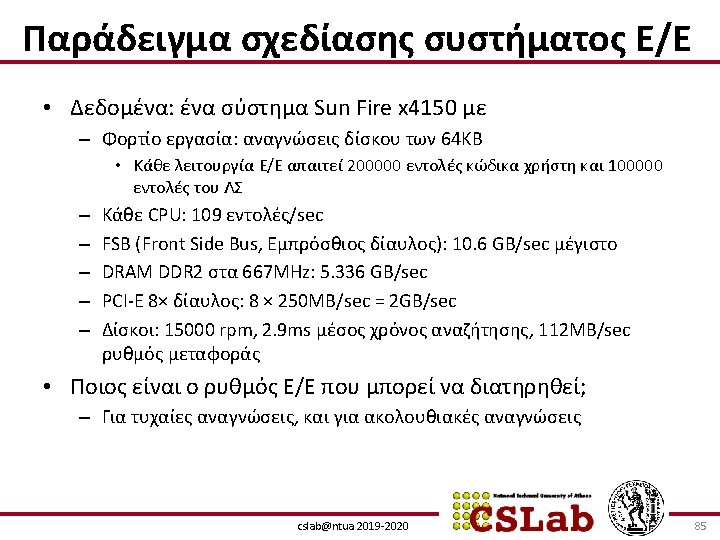

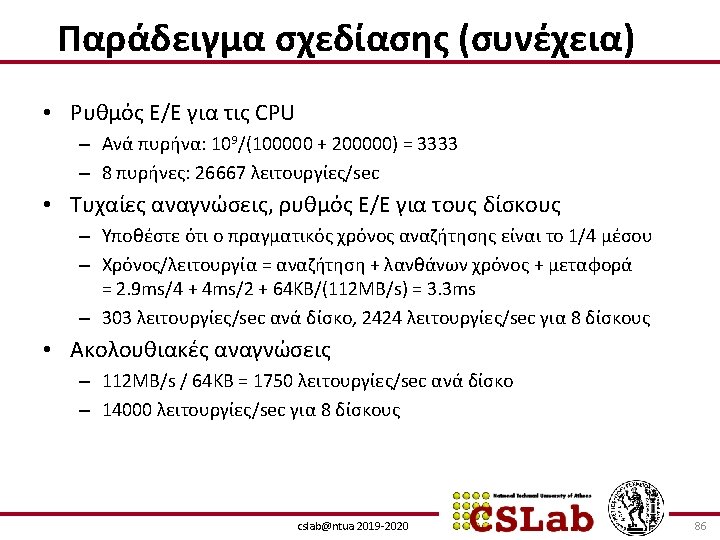

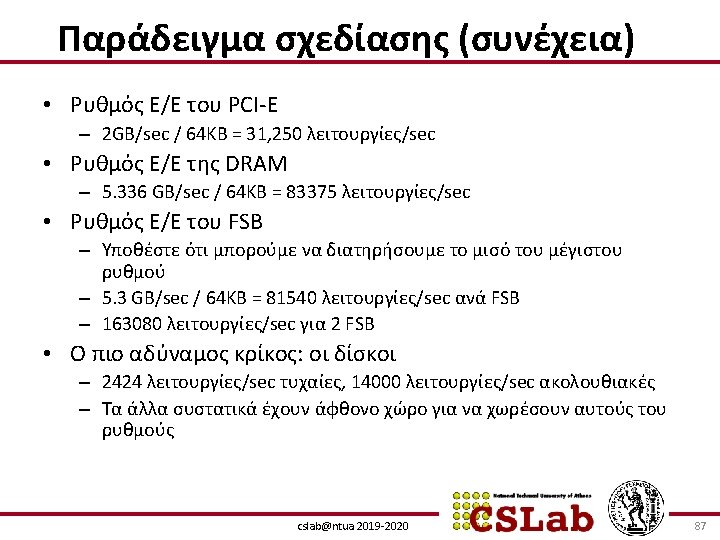

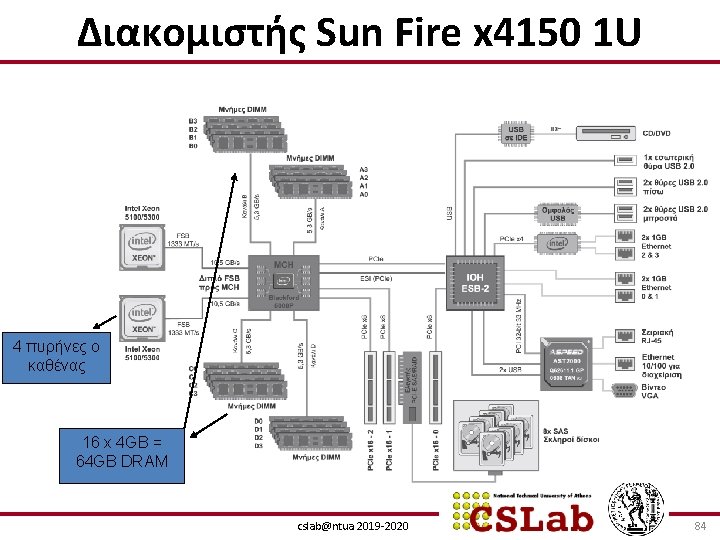

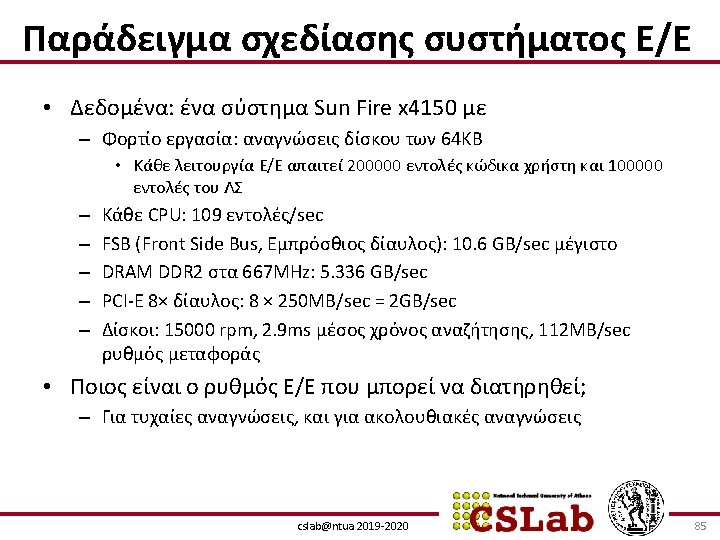

Διακομιστής Sun Fire x 4150 1 U 4 πυρήνες ο καθένας 16 x 4 GB = 64 GB DRAM cslab@ntua 2019 -2020 84

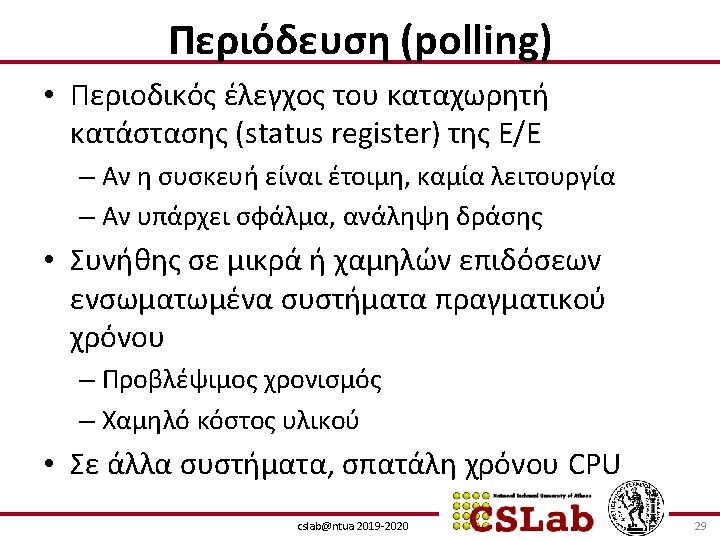

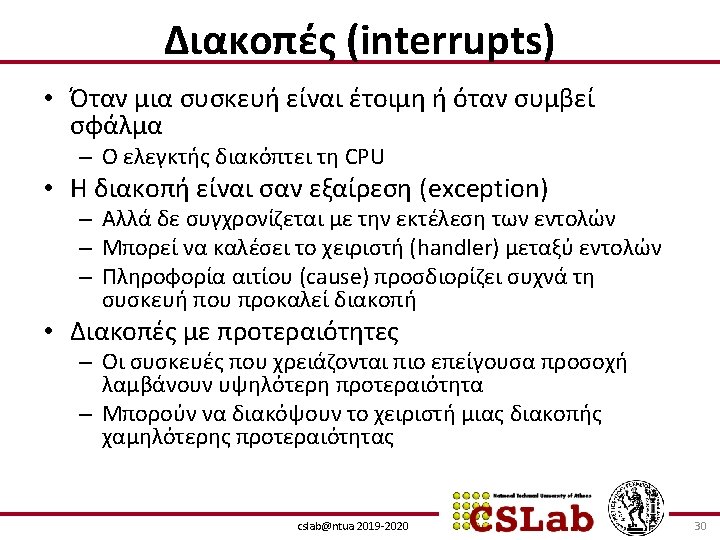

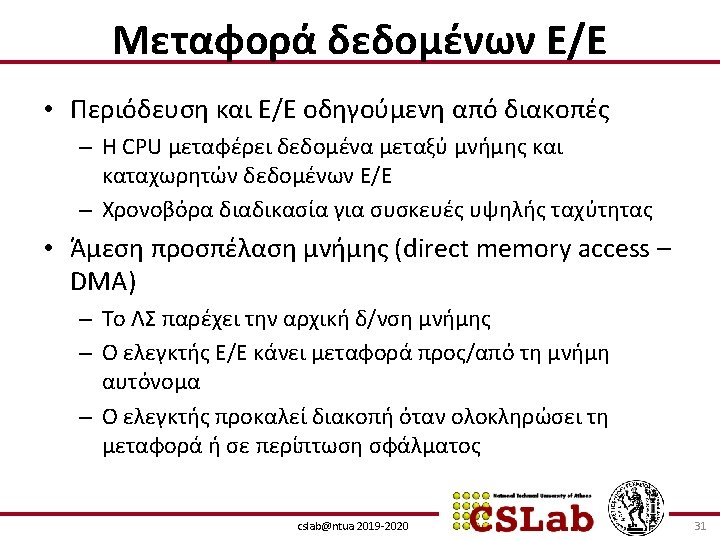

Επιπλέον Υλικό cslab@ntua 2019 -2020 95

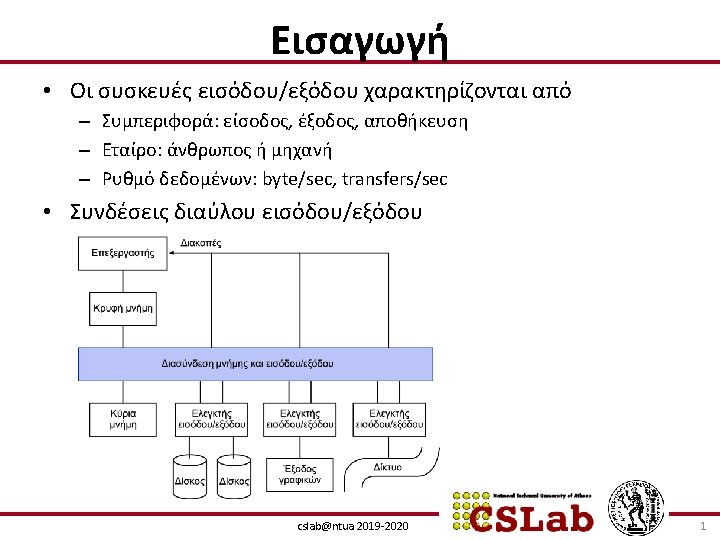

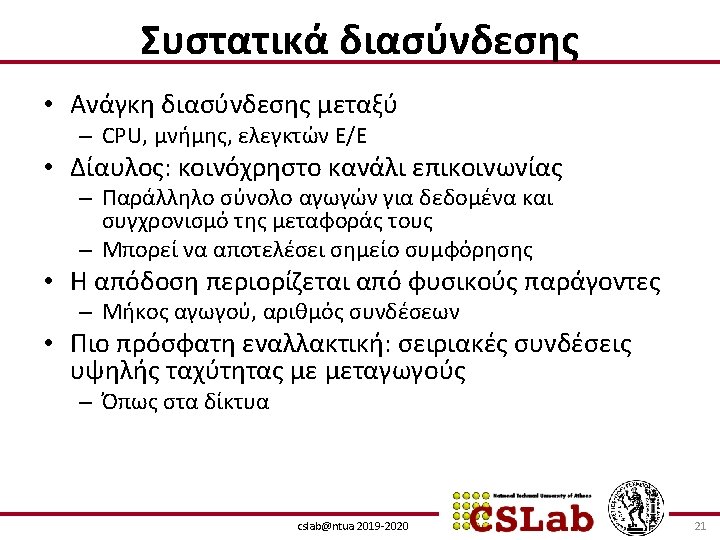

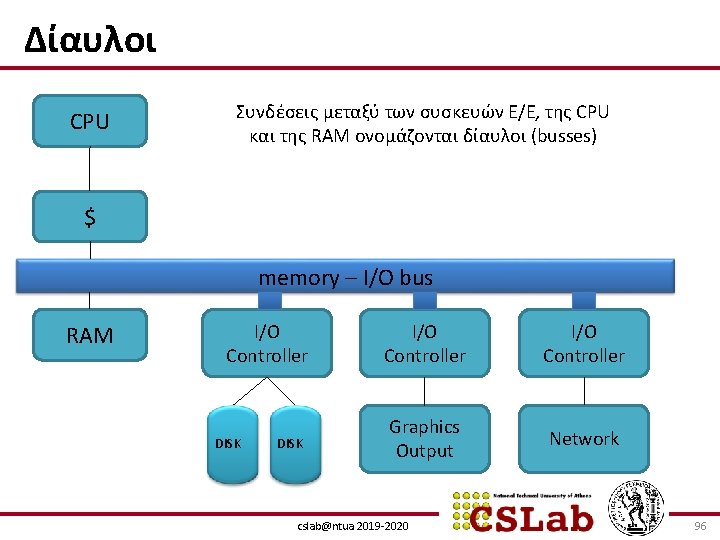

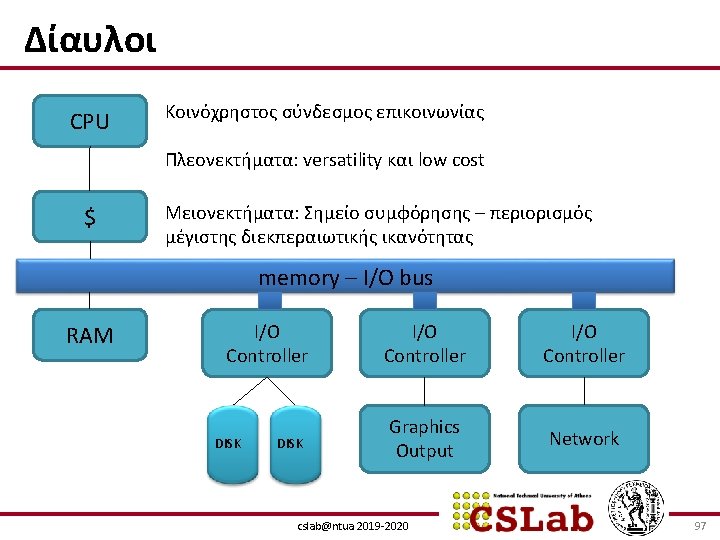

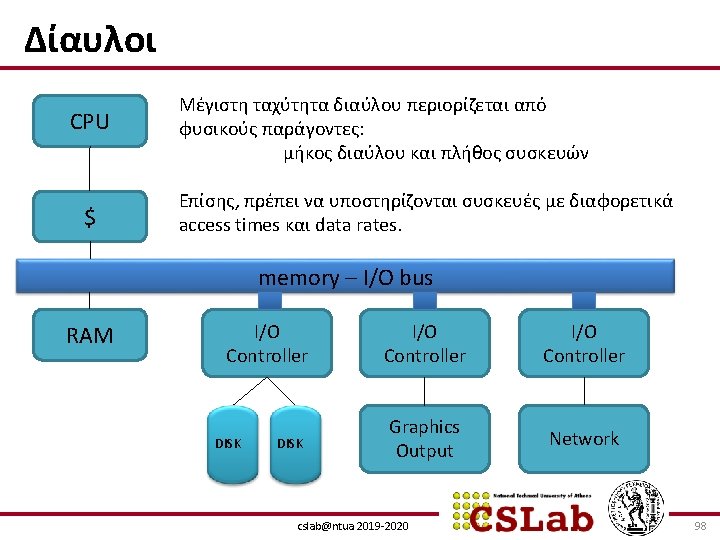

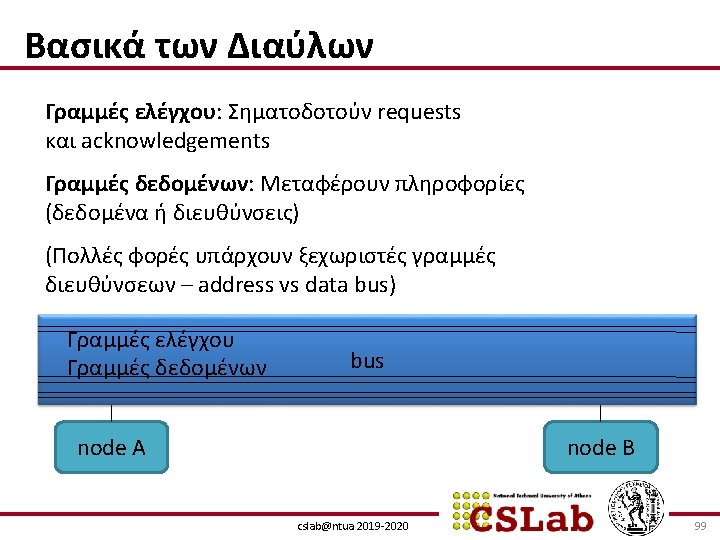

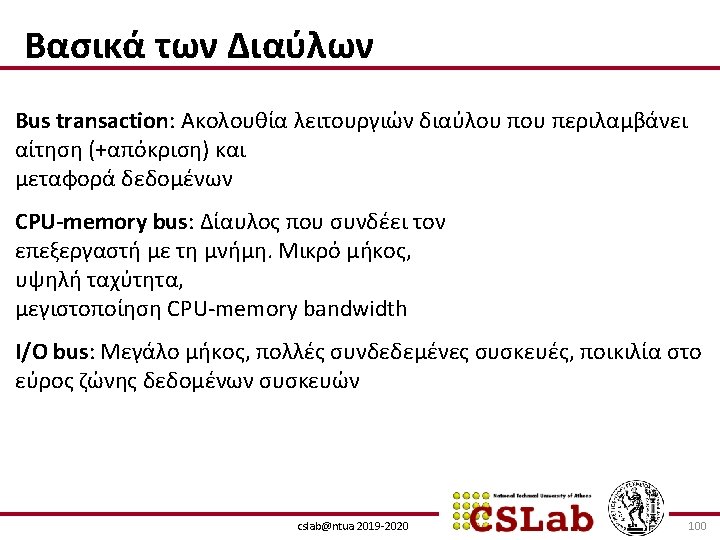

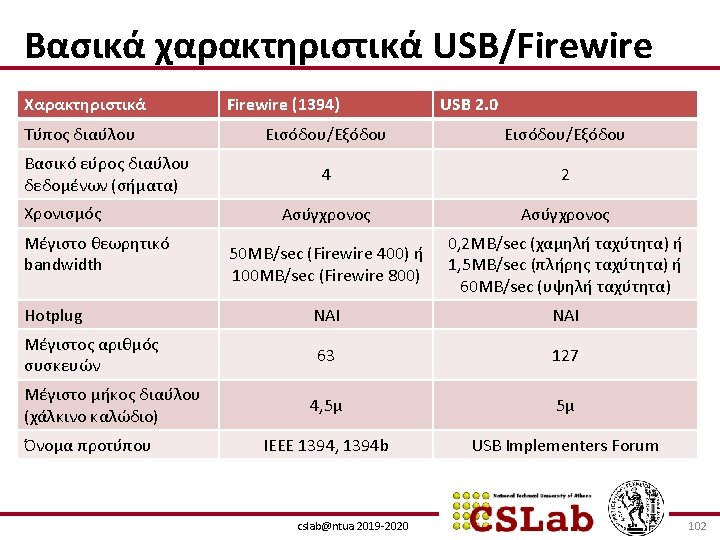

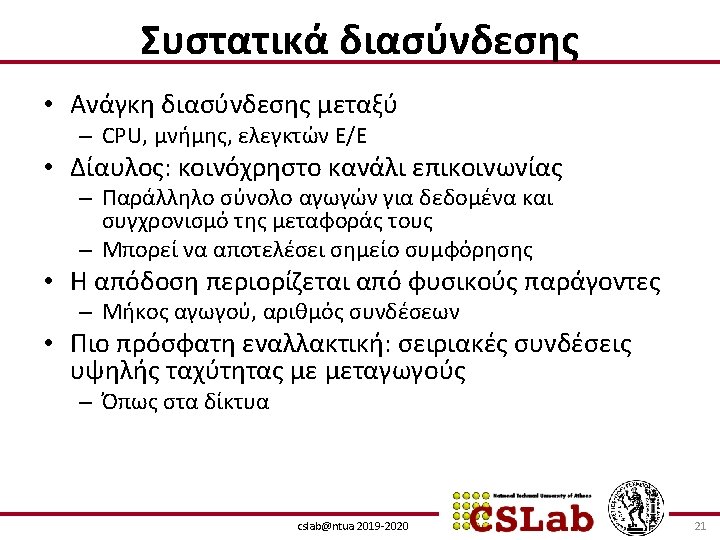

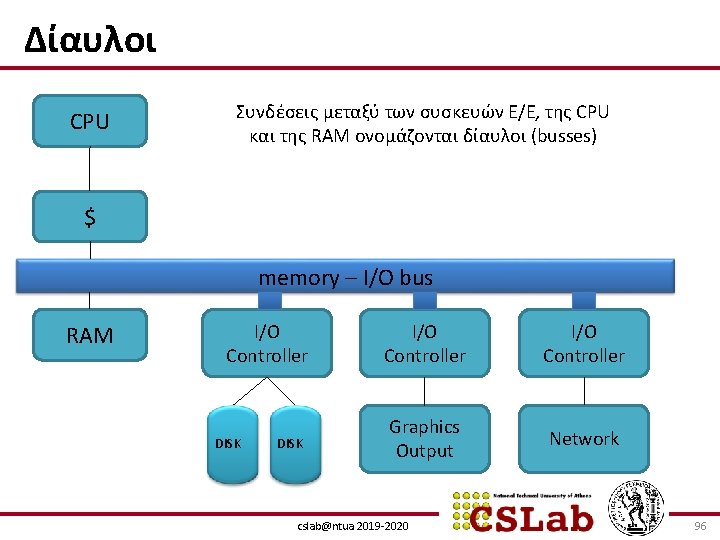

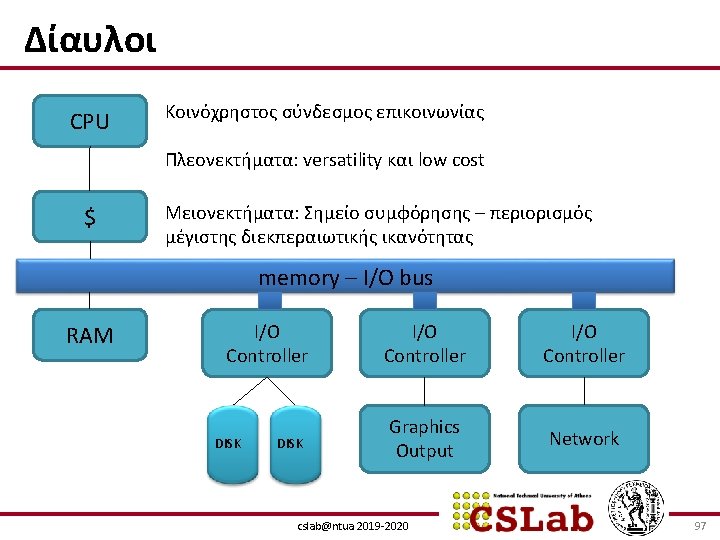

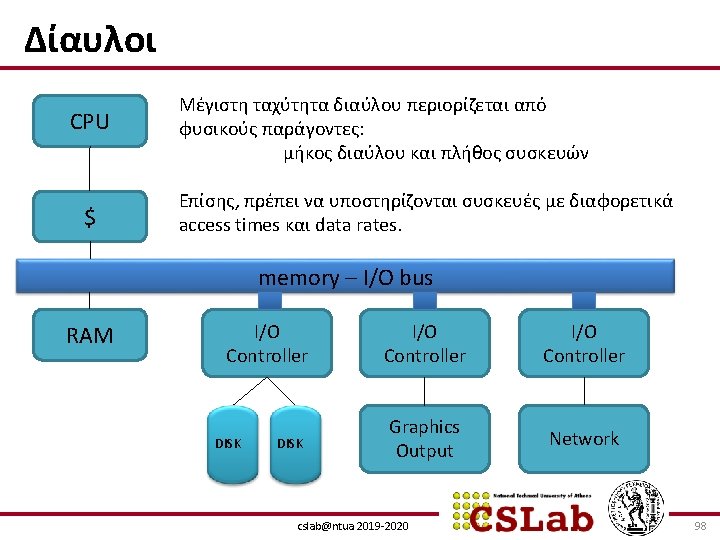

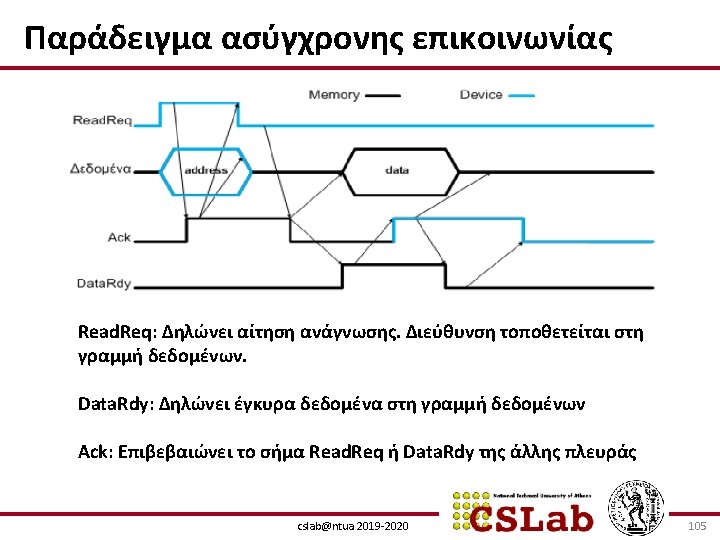

Δίαυλοι CPU Συνδέσεις μεταξύ των συσκευών Ε/Ε, της CPU και της RAM ονομάζονται δίαυλοι (busses) $ memory – I/O bus RAM I/O Controller DISK I/O Controller Graphics Output Network cslab@ntua 2019 -2020 96

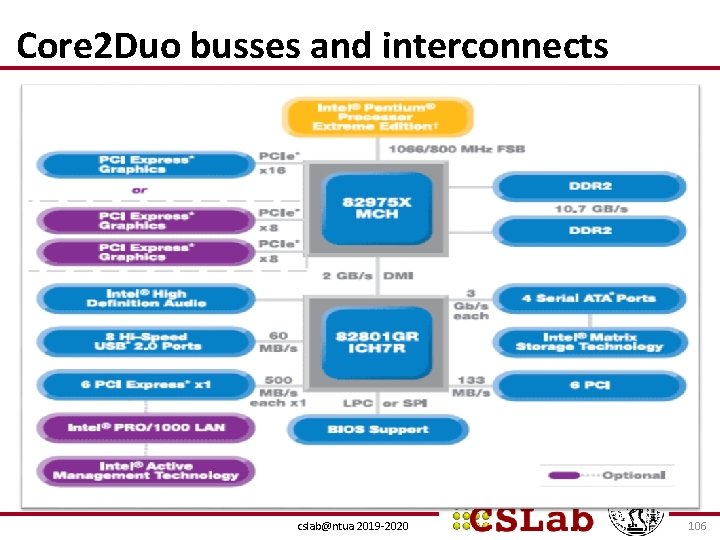

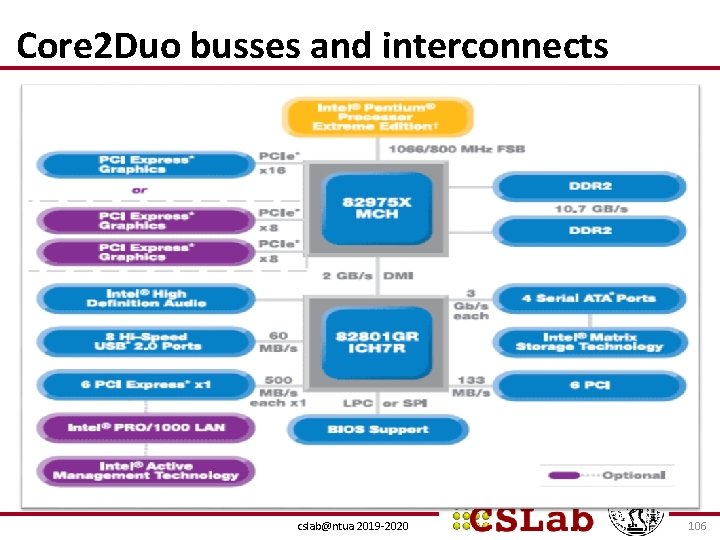

Core 2 Duo busses and interconnects cslab@ntua 2019 -2020 106

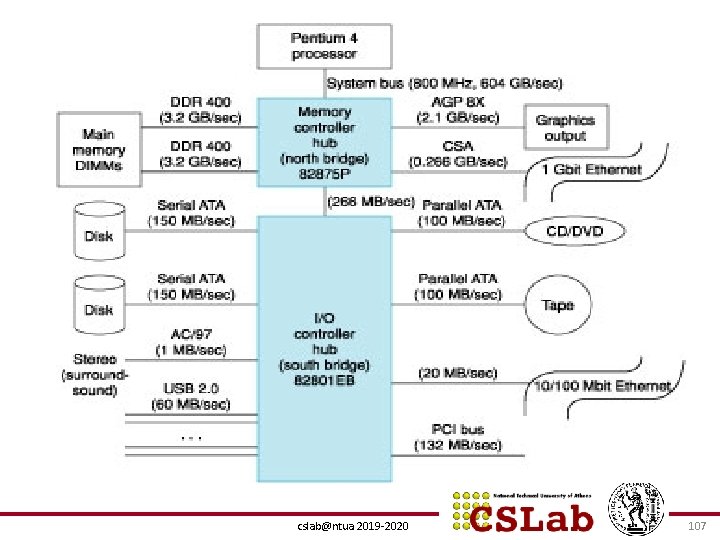

cslab@ntua 2019 -2020 107

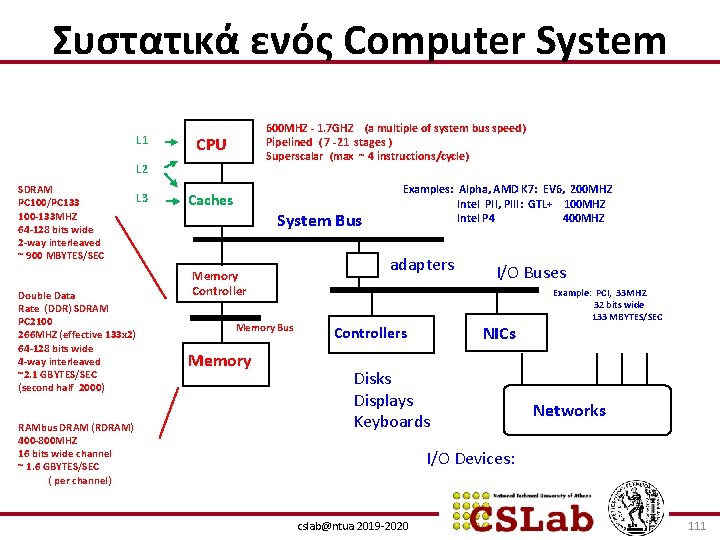

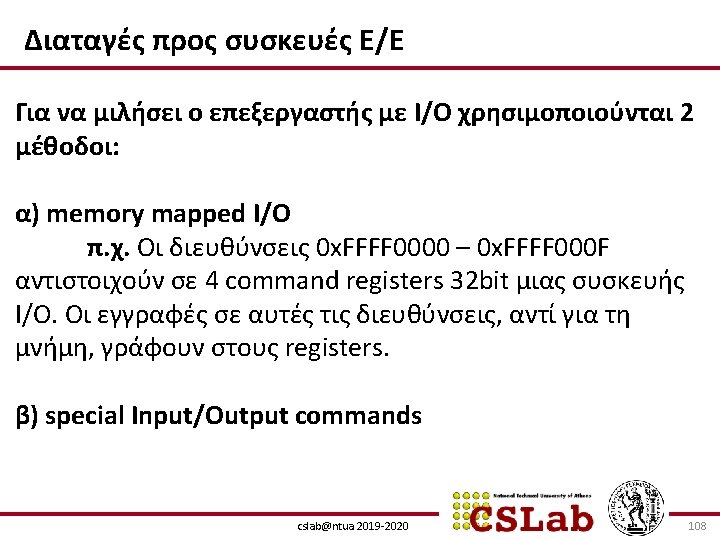

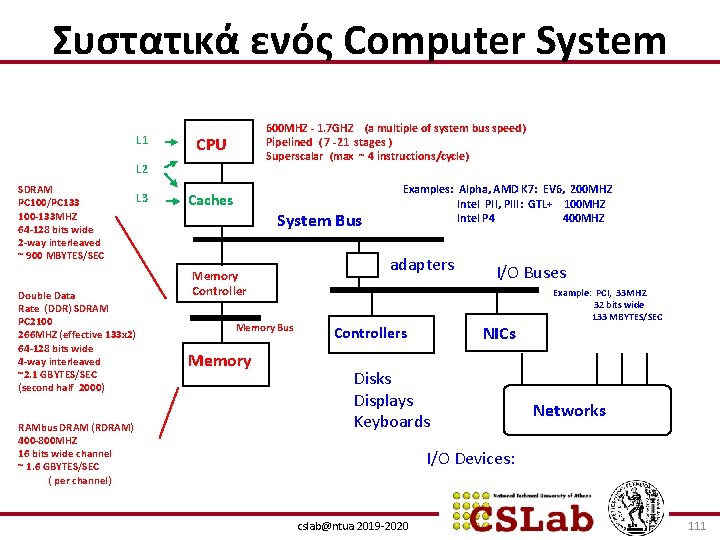

Συστατικά ενός Computer System L 1 600 MHZ - 1. 7 GHZ (a multiple of system bus speed) Pipelined ( 7 -21 stages ) Superscalar (max ~ 4 instructions/cycle) CPU L 2 SDRAM PC 100/PC 133 100 -133 MHZ 64 -128 bits wide 2 -way interleaved ~ 900 MBYTES/SEC Double Data Rate (DDR) SDRAM PC 2100 266 MHZ (effective 133 x 2) 64 -128 bits wide 4 -way interleaved ~2. 1 GBYTES/SEC (second half 2000) RAMbus DRAM (RDRAM) 400 -800 MHZ 16 bits wide channel ~ 1. 6 GBYTES/SEC ( per channel) L 3 Caches System Bus Memory Controller Memory Bus Memory Examples: Alpha, AMD K 7: EV 6, 200 MHZ Intel PII, PIII: GTL+ 100 MHZ Intel P 4 400 MHZ adapters I/O Buses NICs Controllers Disks Displays Keyboards Example: PCI, 33 MHZ 32 bits wide 133 MBYTES/SEC Networks I/O Devices: cslab@ntua 2019 -2020 111

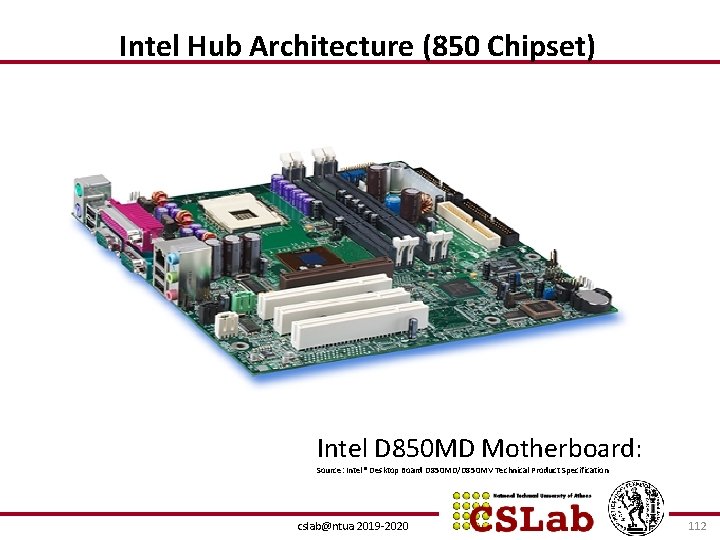

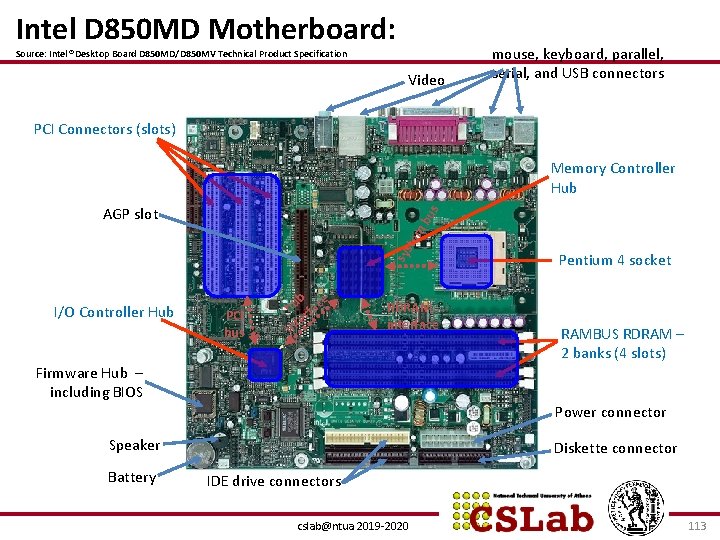

Intel Hub Architecture (850 Chipset) Intel D 850 MD Motherboard: Source: Intel® Desktop Board D 850 MD/D 850 MV Technical Product Specification cslab@ntua 2019 -2020 112

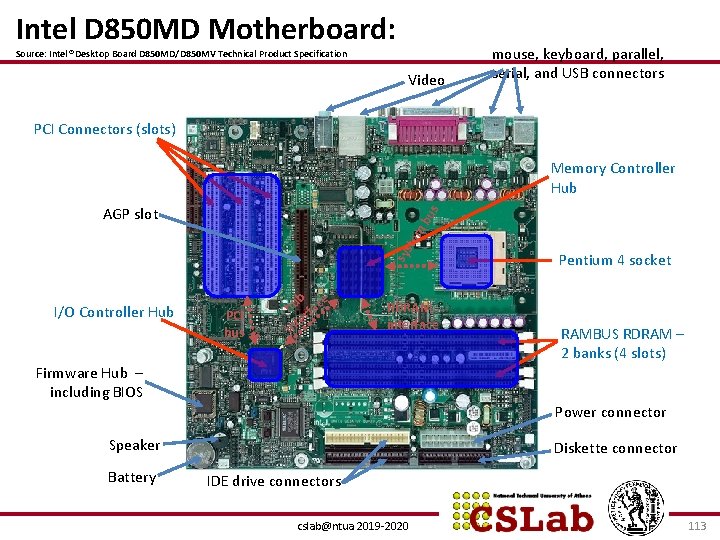

Intel D 850 MD Motherboard: Source: Intel® Desktop Board D 850 MD/D 850 MV Technical Product Specification Video mouse, keyboard, parallel, serial, and USB connectors PCI Connectors (slots) Memory Controller Hub sys tem bu s AGP slot I/O Controller Hub PCI bus b e hu rfac te in RDRAM interface Firmware Hub – including BIOS Pentium 4 socket RAMBUS RDRAM – 2 banks (4 slots) Power connector Speaker Battery Diskette connector IDE drive connectors cslab@ntua 2019 -2020 113

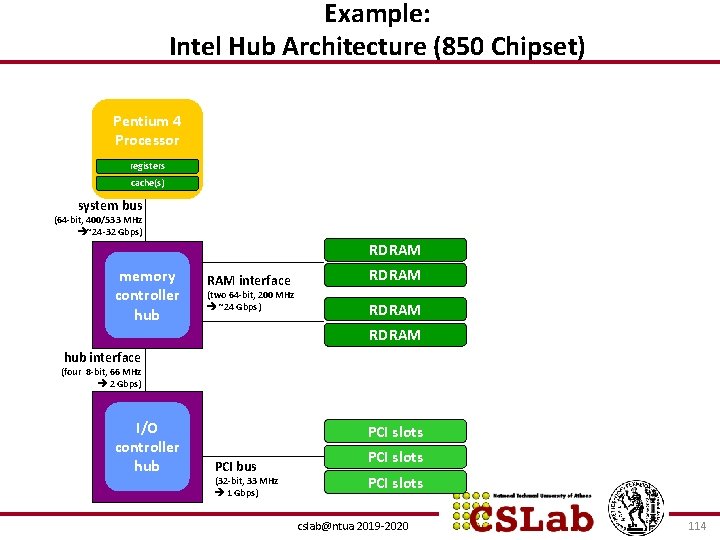

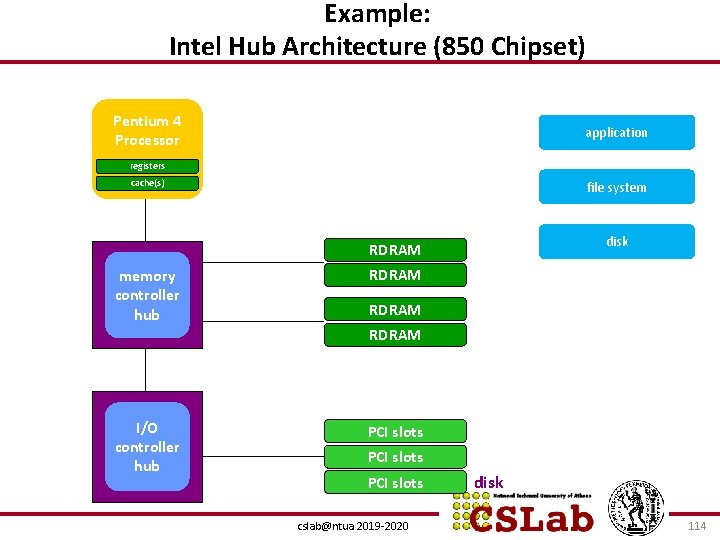

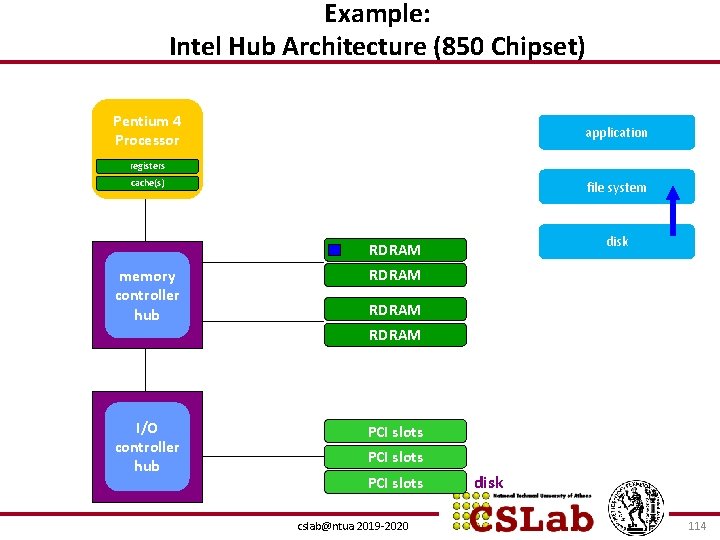

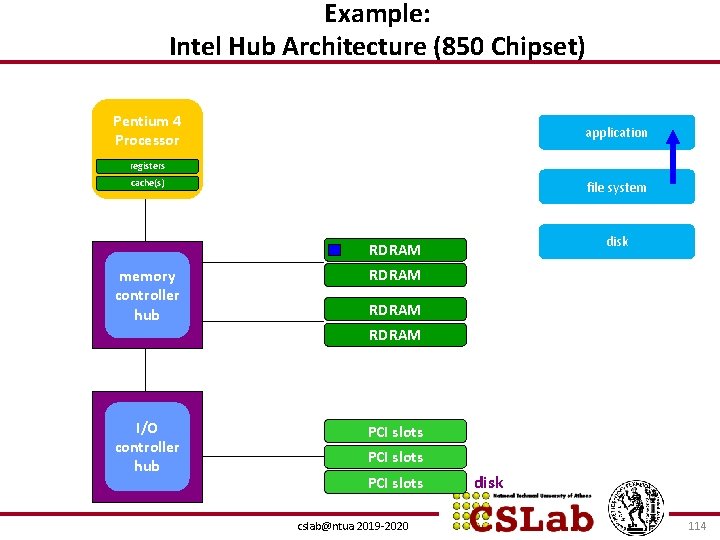

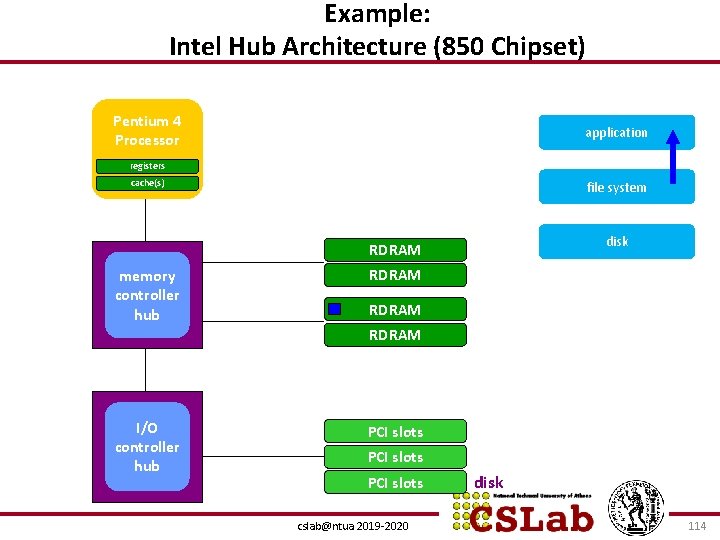

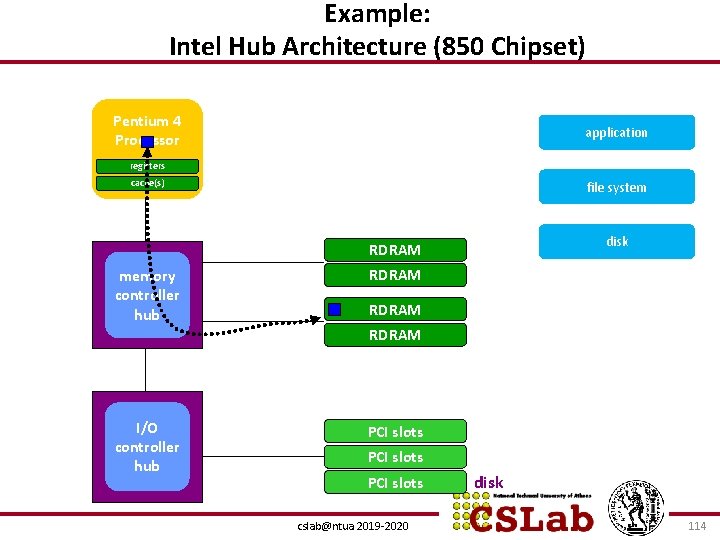

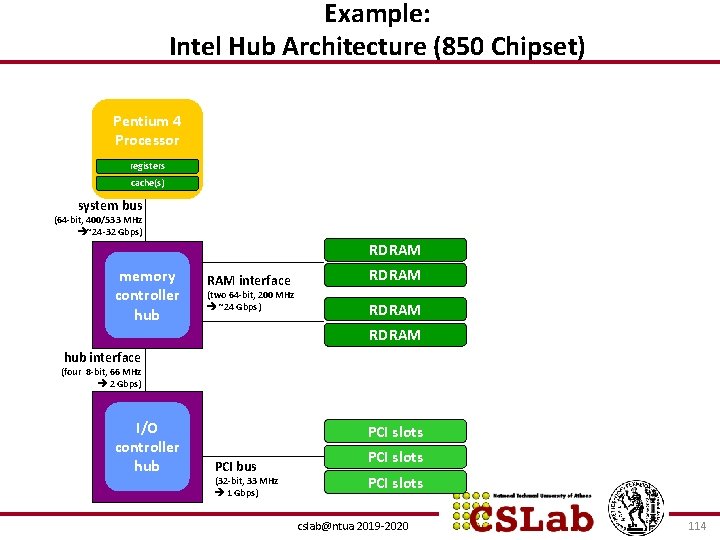

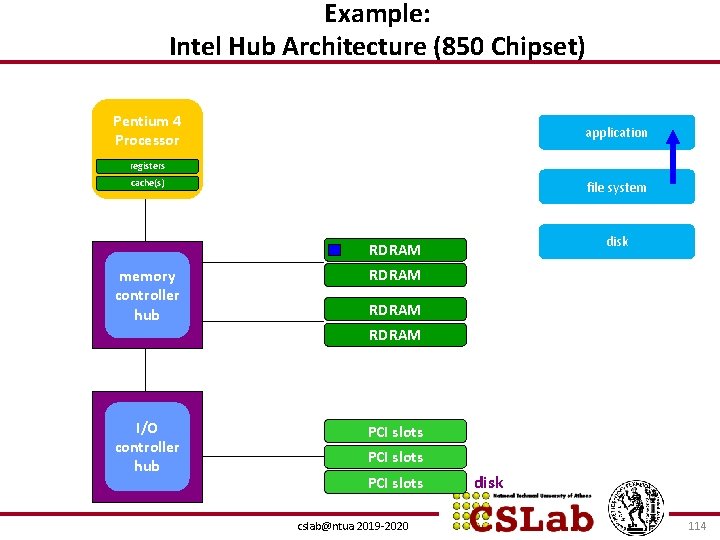

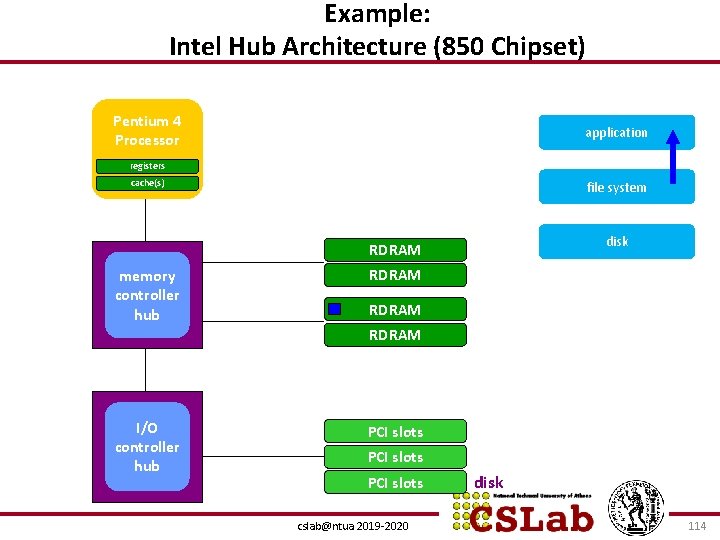

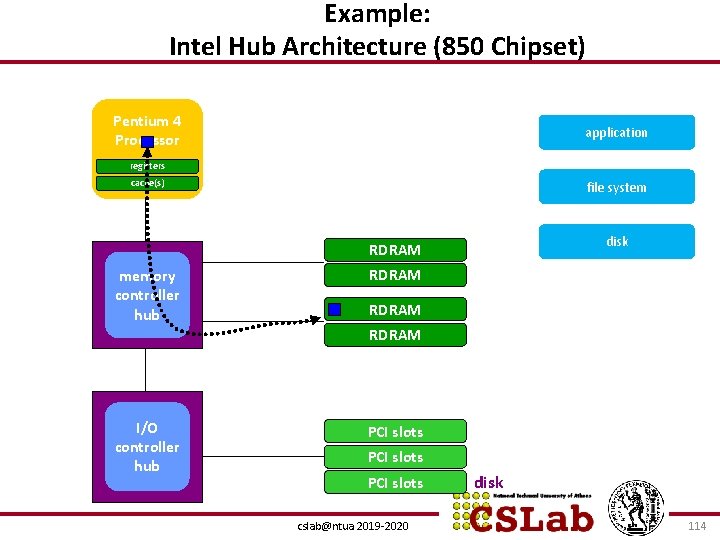

Example: Intel Hub Architecture (850 Chipset) Pentium 4 Processor registers cache(s) system bus (64 -bit, 400/533 MHz ~24 -32 Gbps) RDRAM memory controller hub RAM interface (two 64 -bit, 200 MHz ~24 Gbps) RDRAM hub interface (four 8 -bit, 66 MHz 2 Gbps) I/O controller hub PCI slots PCI bus (32 -bit, 33 MHz 1 Gbps) PCI slots cslab@ntua 2019 -2020 114

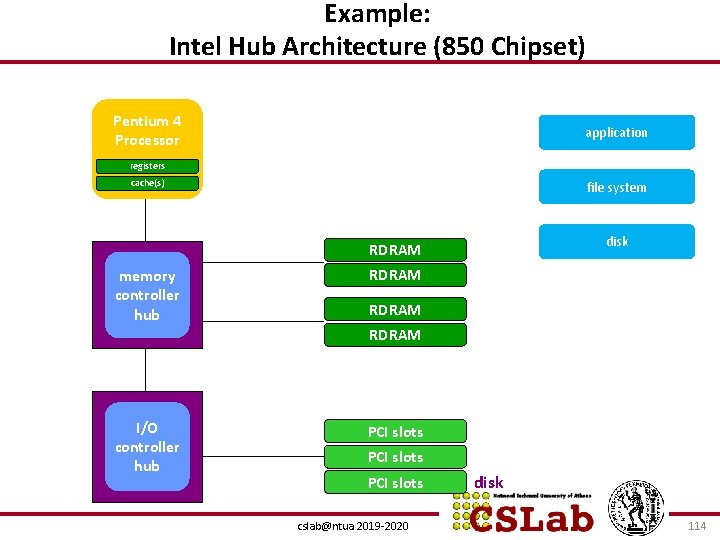

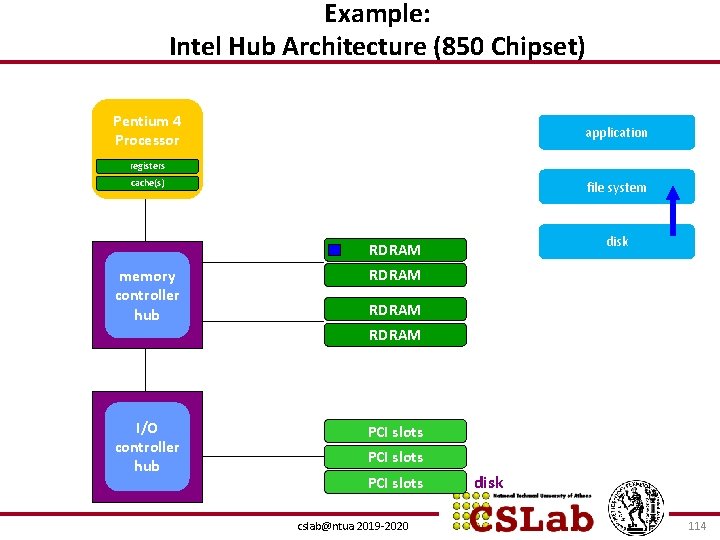

Example: Intel Hub Architecture (850 Chipset) Pentium 4 Processor application registers cache(s) file system disk RDRAM memory controller hub RDRAM I/O controller hub PCI slots cslab@ntua 2019 -2020 disk 114

Example: Intel Hub Architecture (850 Chipset) Pentium 4 Processor application registers cache(s) file system disk RDRAM memory controller hub RDRAM I/O controller hub PCI slots cslab@ntua 2019 -2020 disk 114

Example: Intel Hub Architecture (850 Chipset) Pentium 4 Processor application registers cache(s) file system disk RDRAM memory controller hub RDRAM I/O controller hub PCI slots cslab@ntua 2019 -2020 disk 114

Example: Intel Hub Architecture (850 Chipset) Pentium 4 Processor application registers cache(s) file system disk RDRAM memory controller hub RDRAM I/O controller hub PCI slots cslab@ntua 2019 -2020 disk 114

Example: Intel Hub Architecture (850 Chipset) Pentium 4 Processor application registers cache(s) file system disk RDRAM memory controller hub RDRAM I/O controller hub PCI slots cslab@ntua 2019 -2020 disk 114

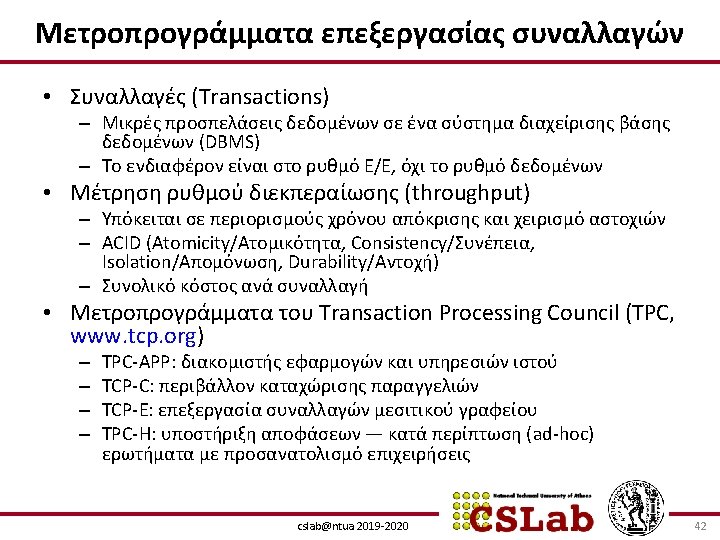

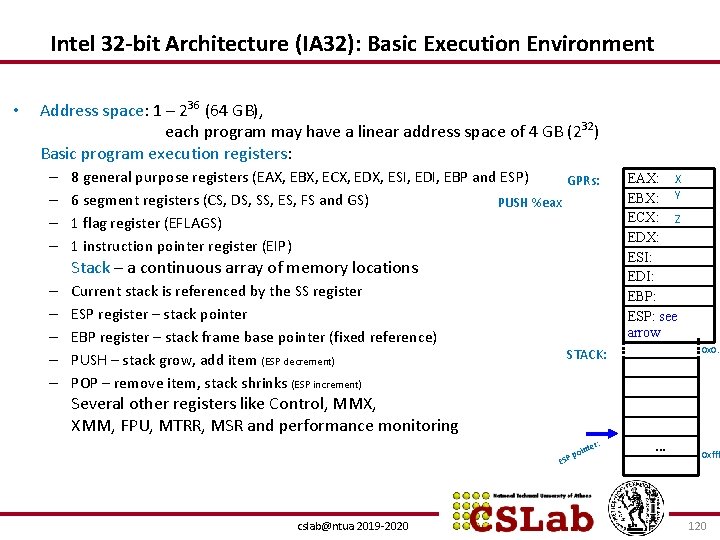

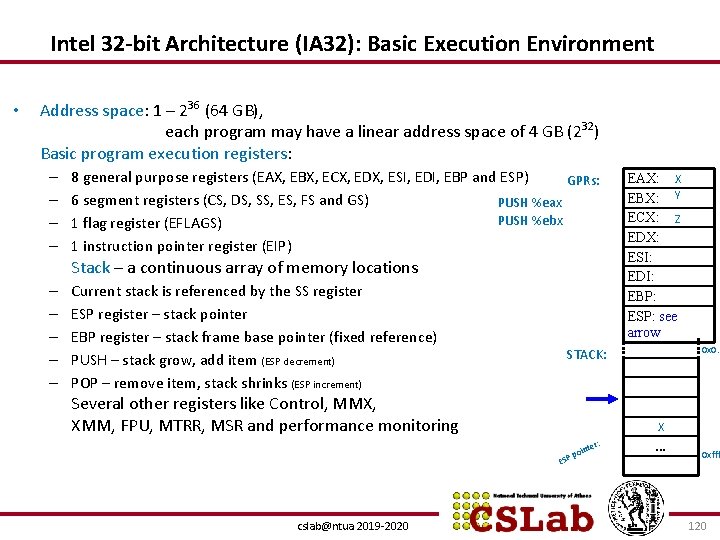

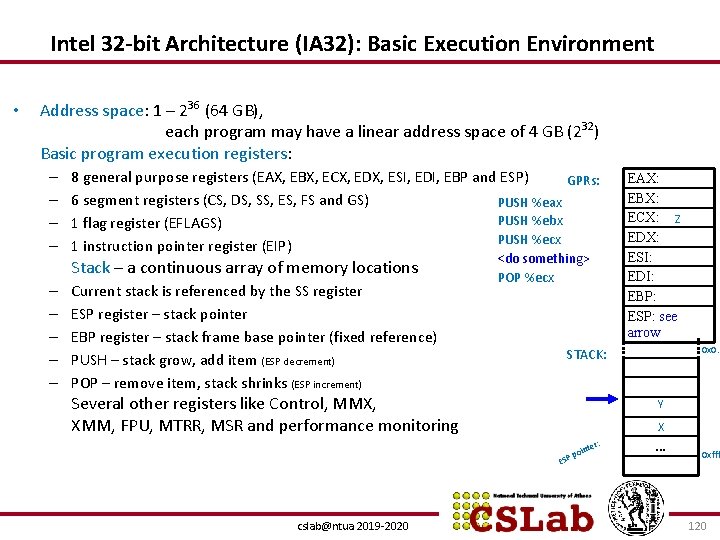

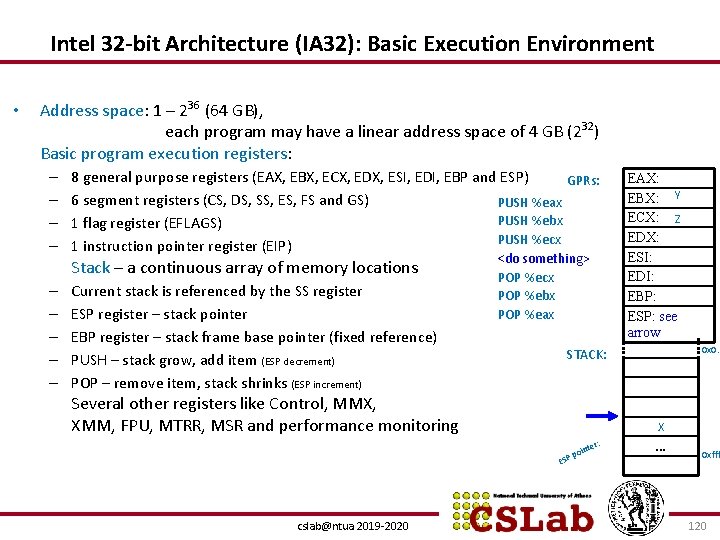

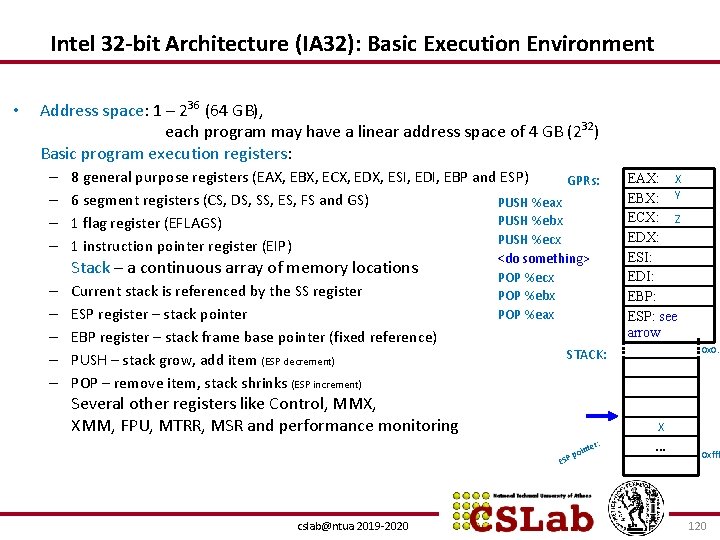

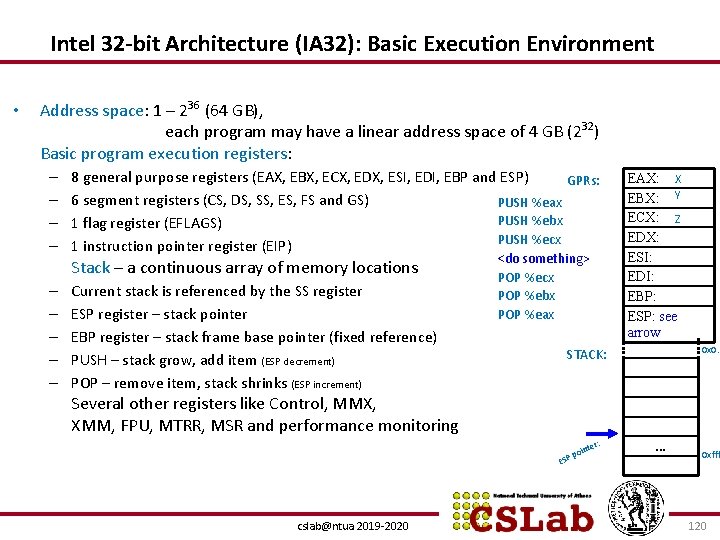

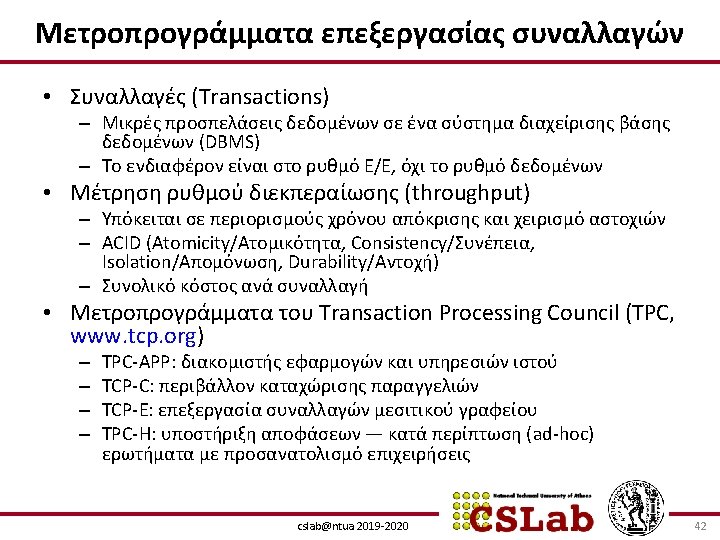

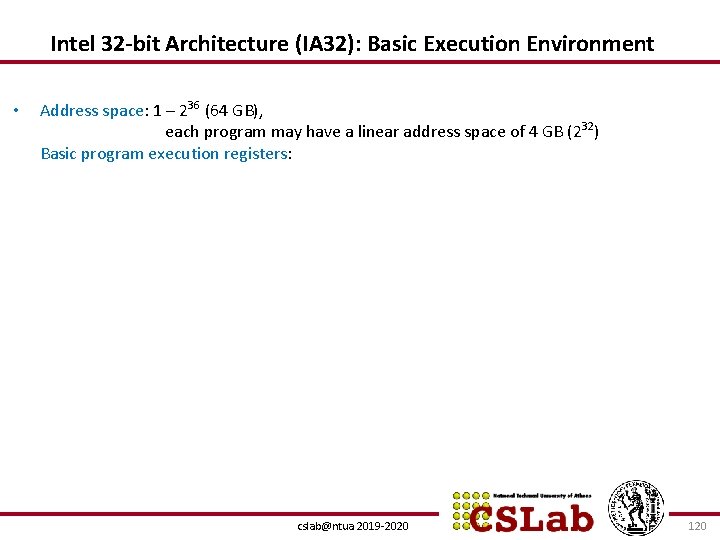

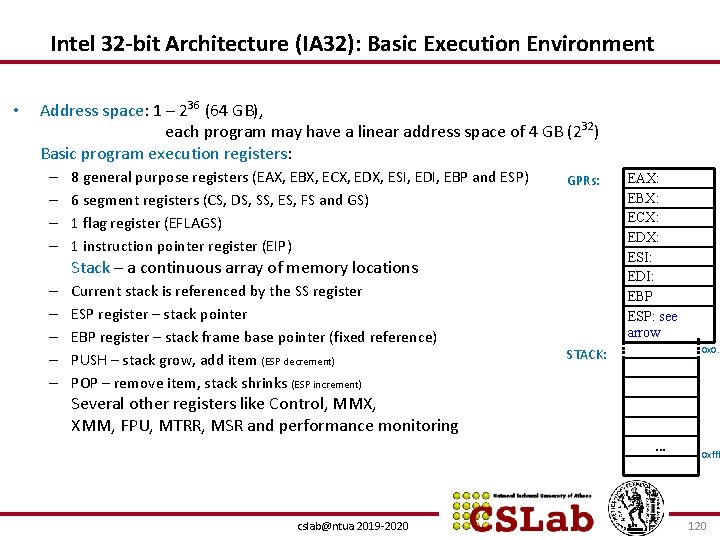

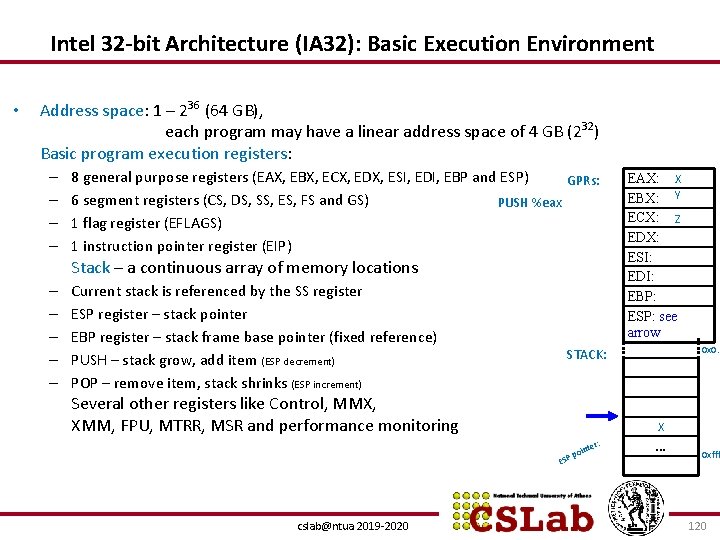

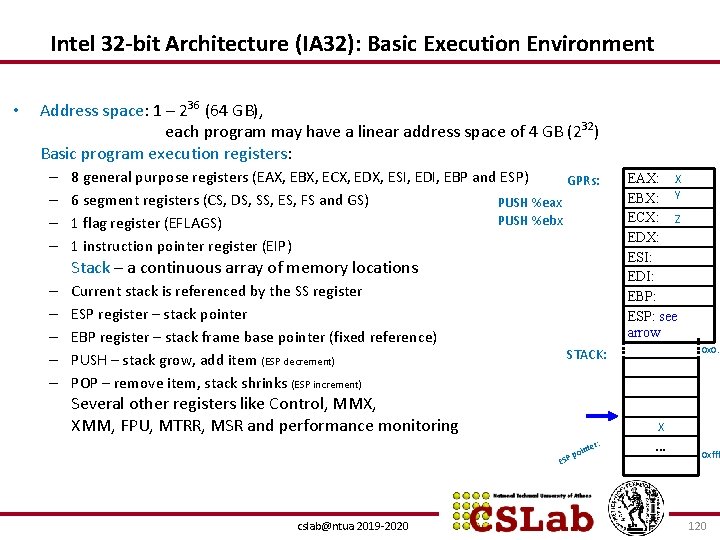

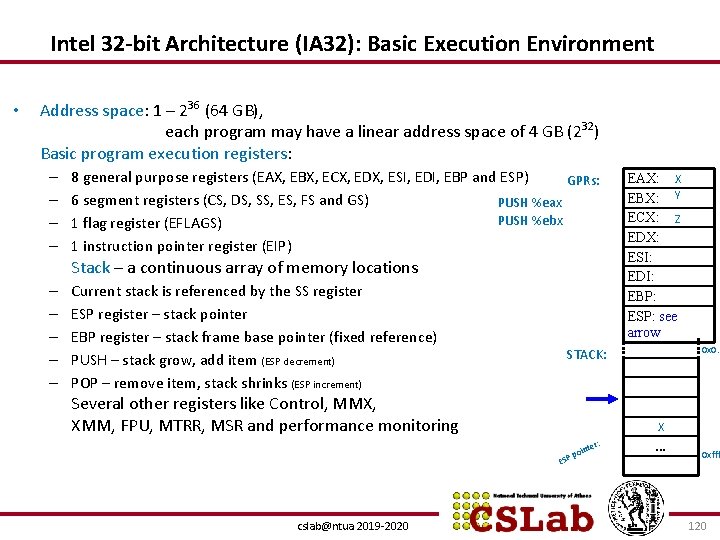

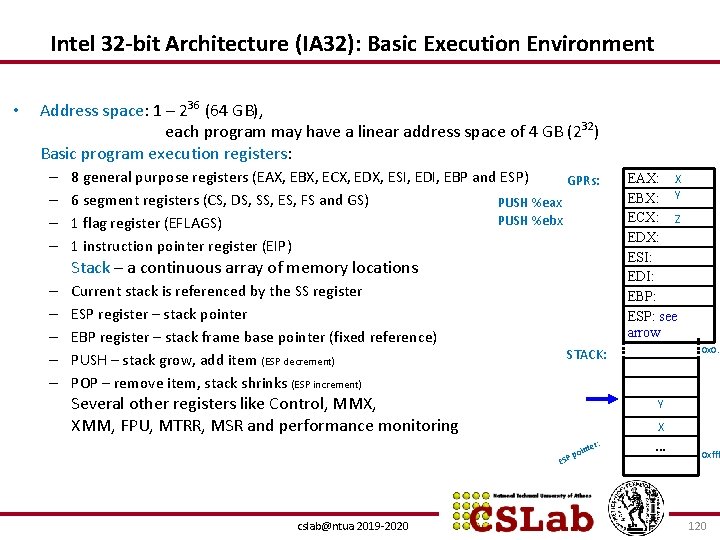

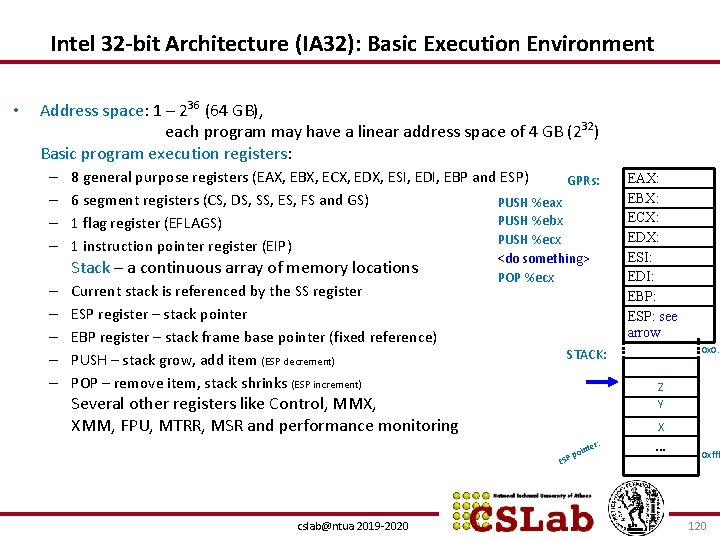

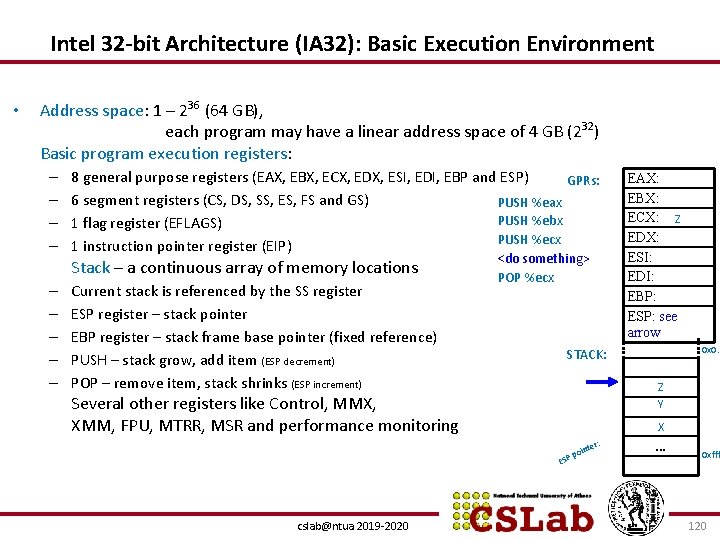

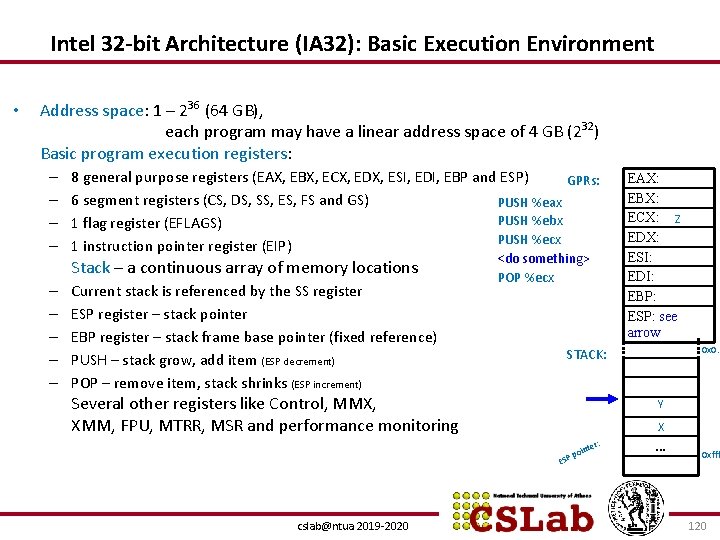

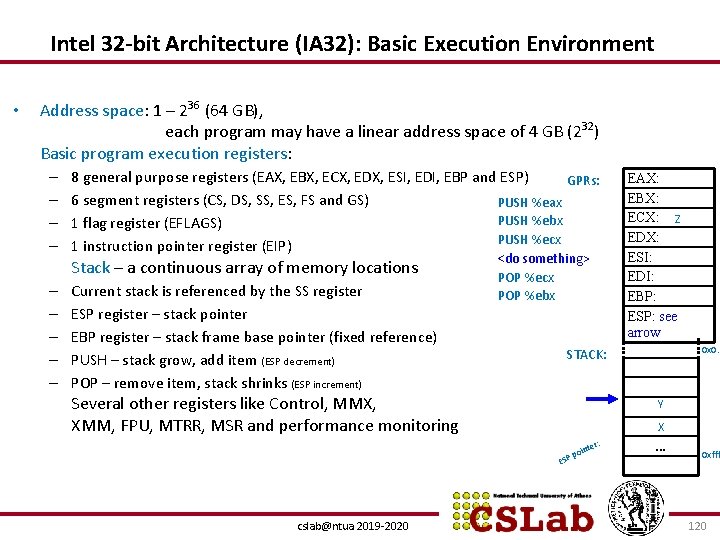

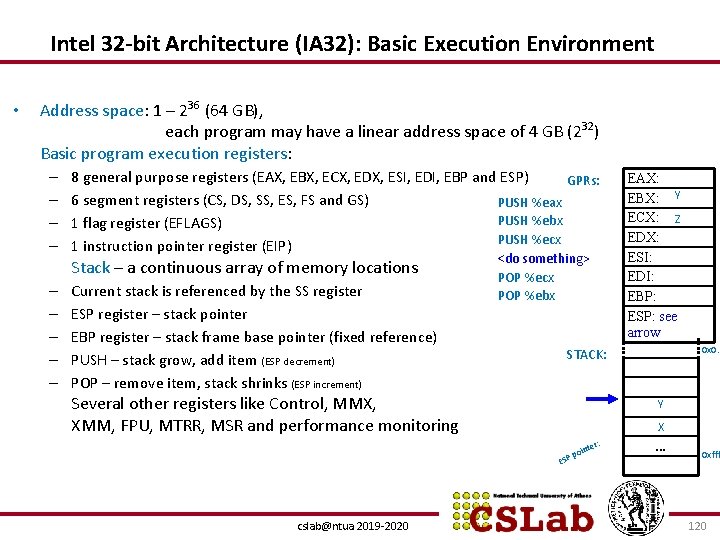

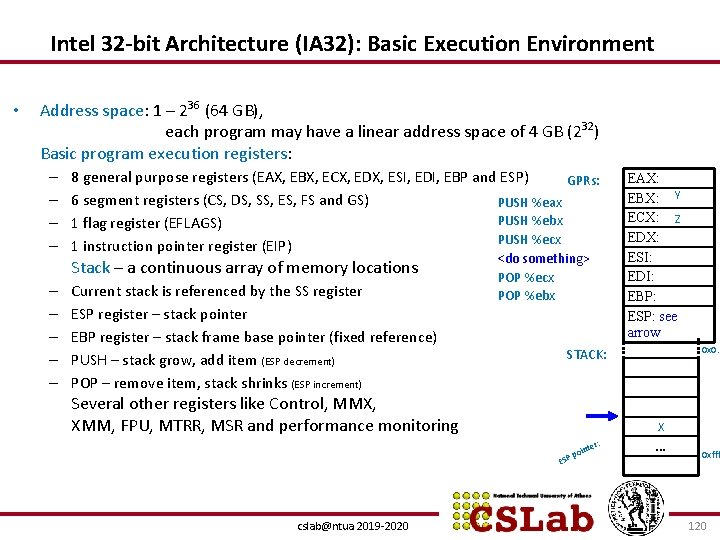

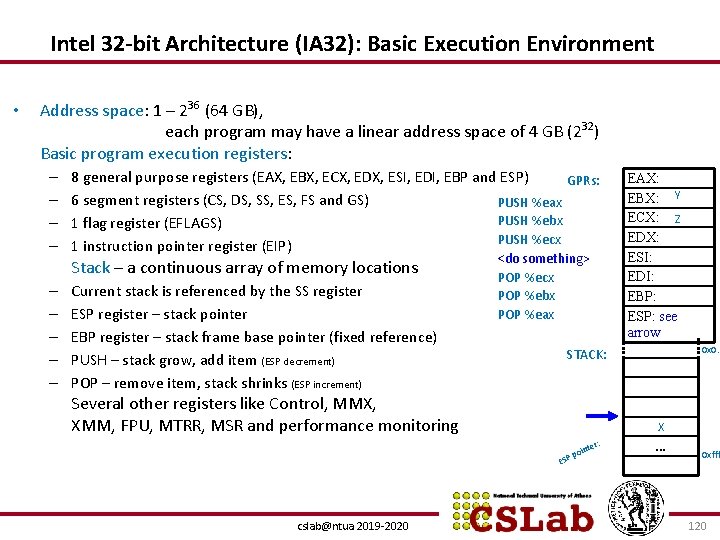

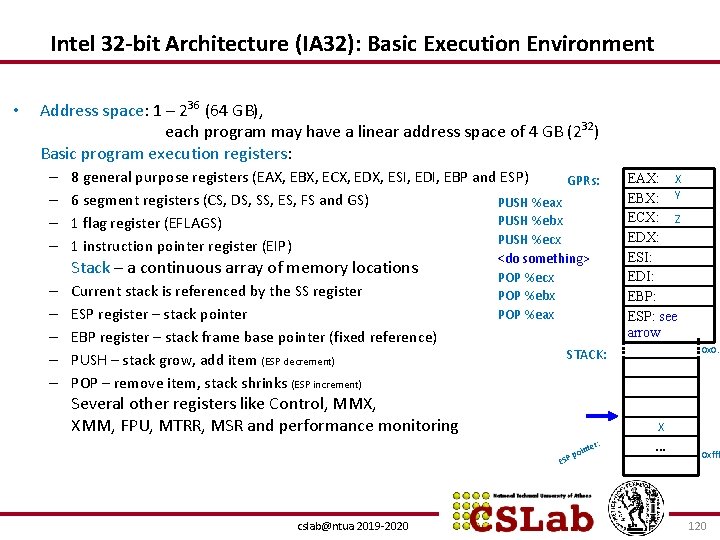

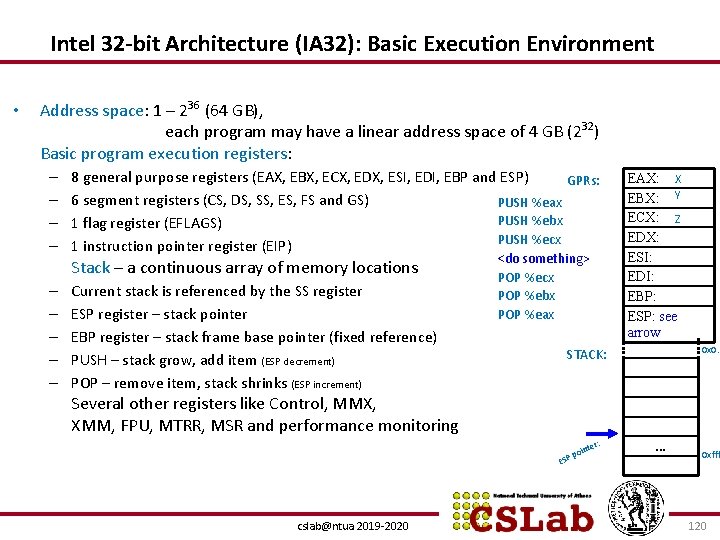

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: cslab@ntua 2019 -2020 120

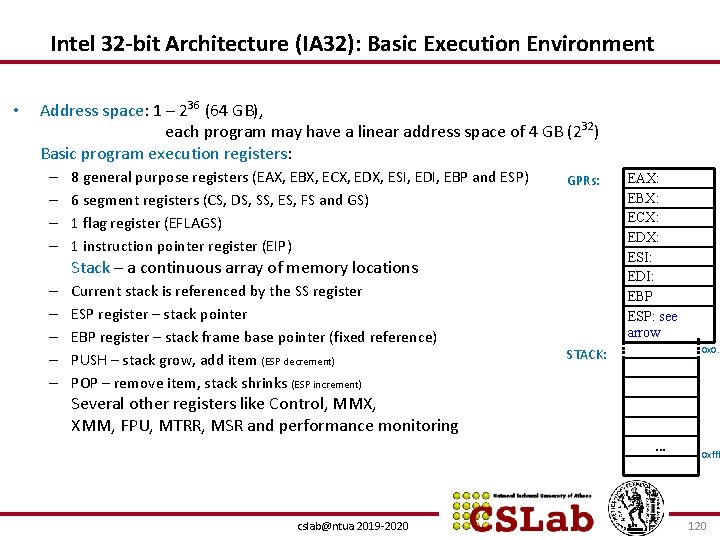

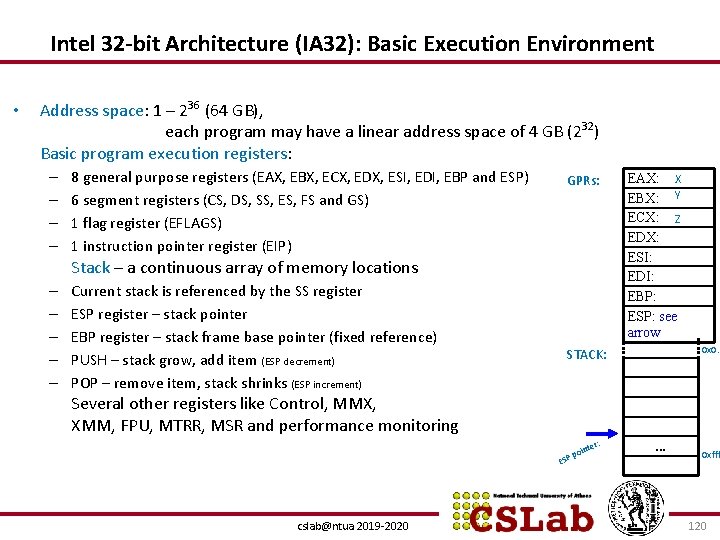

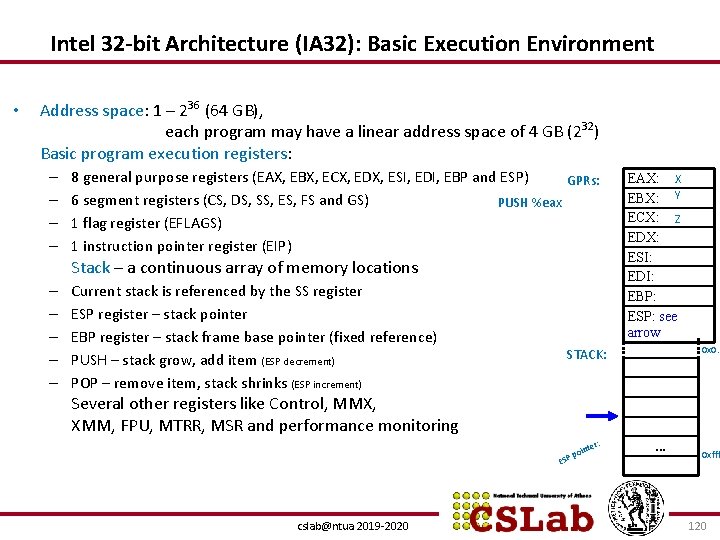

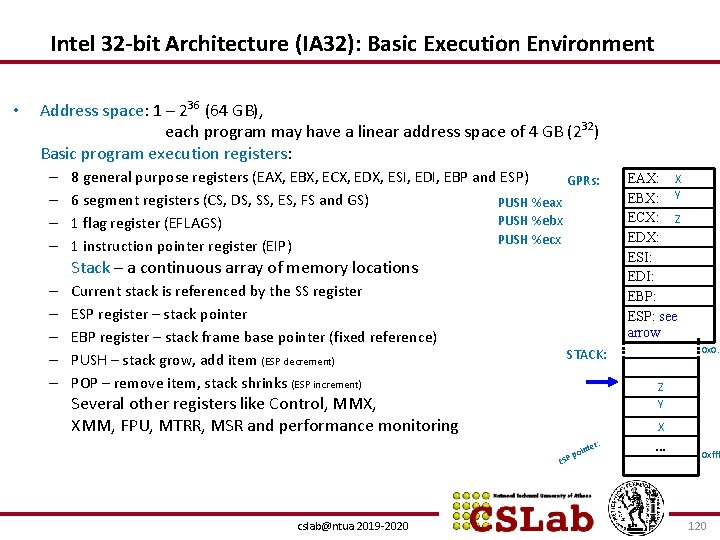

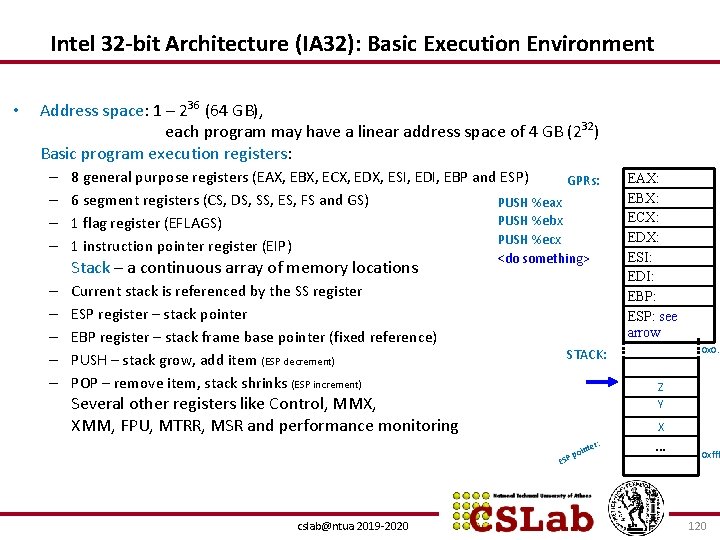

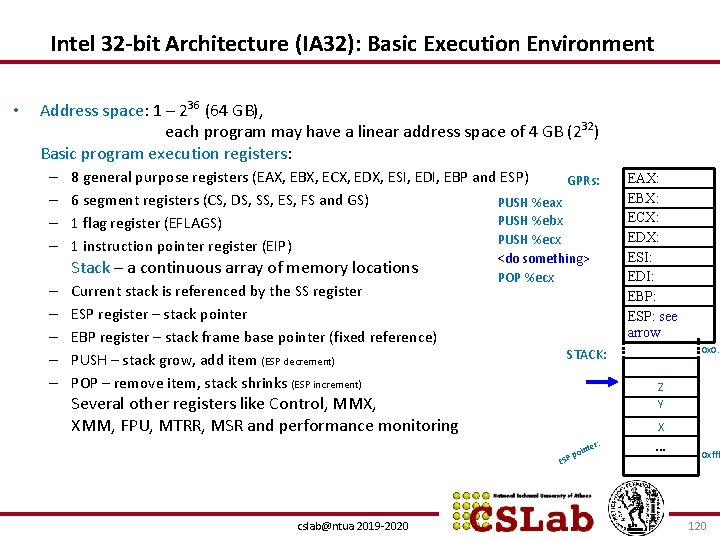

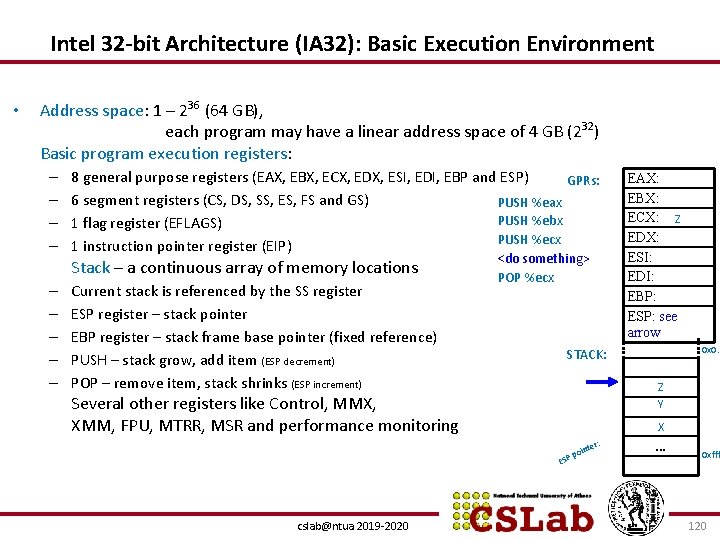

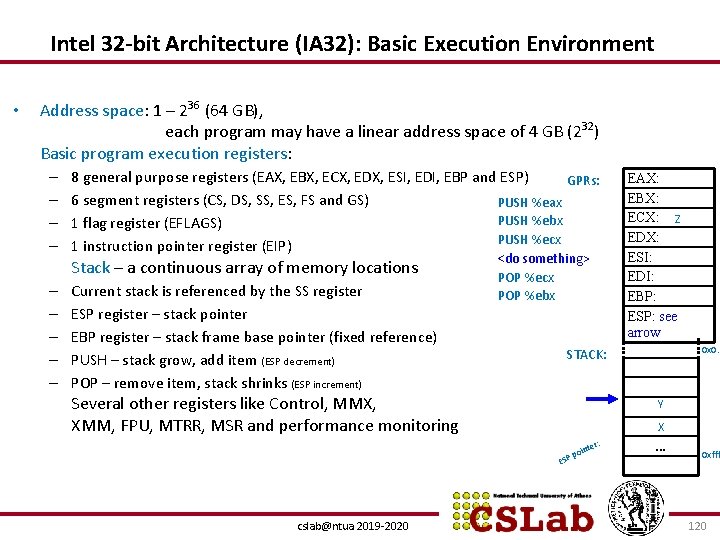

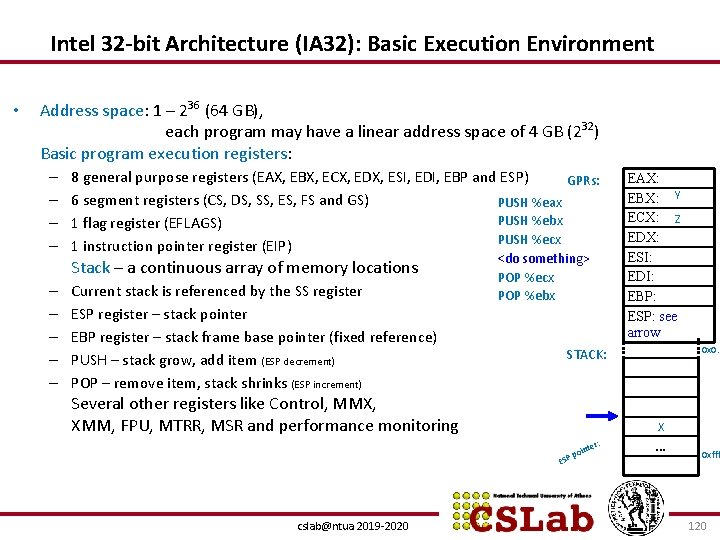

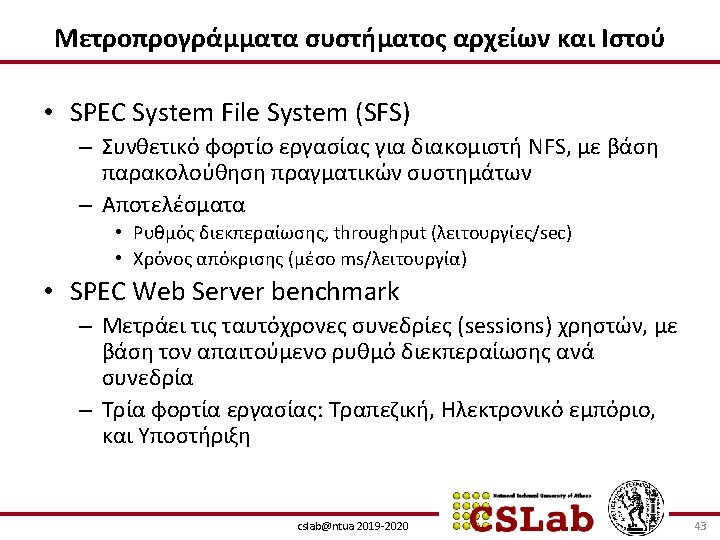

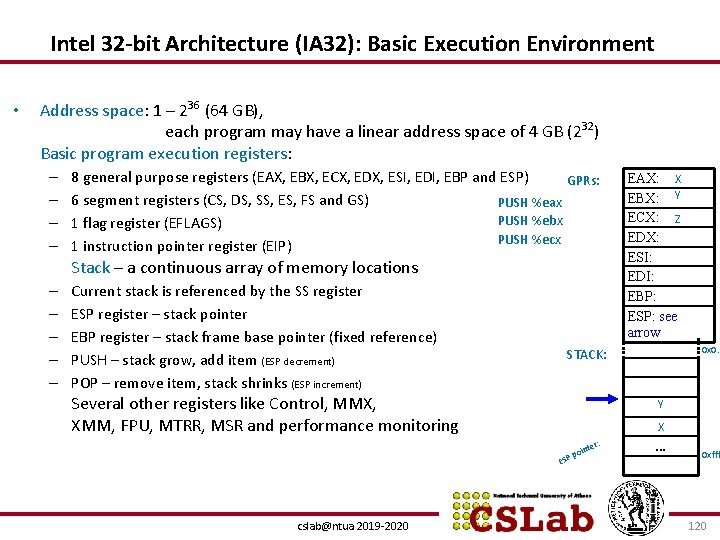

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) 6 segment registers (CS, DS, SS, ES, FS and GS) 1 flag register (EFLAGS) 1 instruction pointer register (EIP) GPRs: Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) EAX: EBX: ECX: EDX: ESI: EDI: EBP: ESP: see arrow 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring. . . cslab@ntua 2019 -2020 0 xfff 120

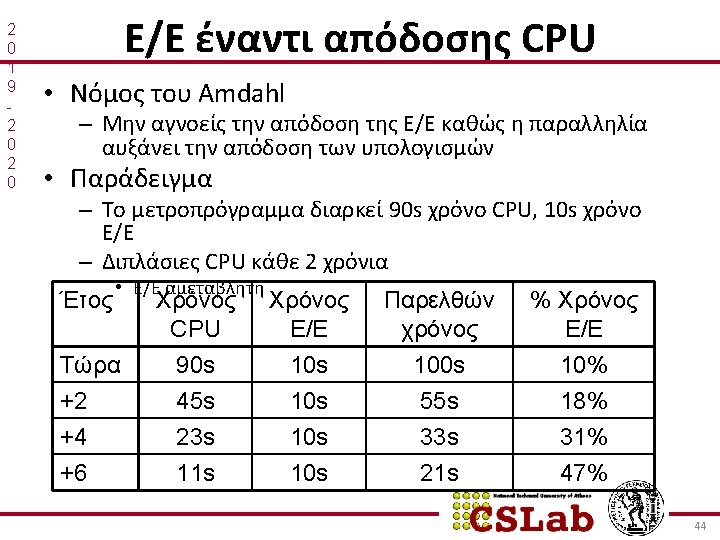

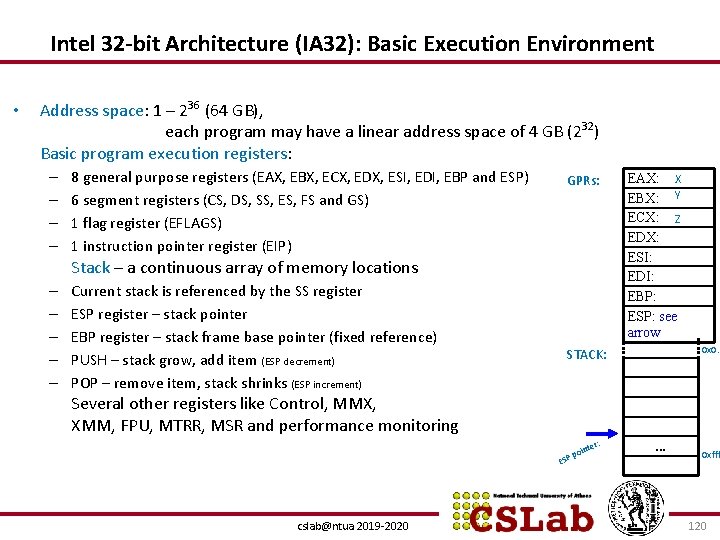

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) 6 segment registers (CS, DS, SS, ES, FS and GS) 1 flag register (EFLAGS) 1 instruction pointer register (EIP) GPRs: Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring ES cslab@ntua 2019 -2020 r: nte oi Pp . . . 0 xfff 120

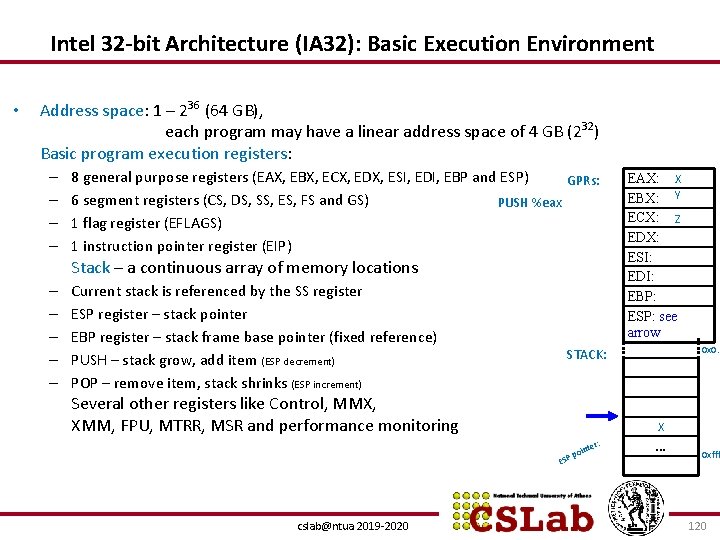

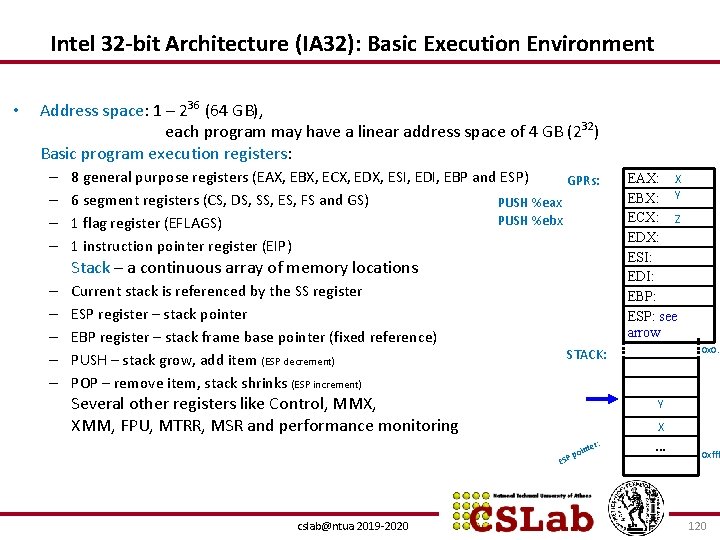

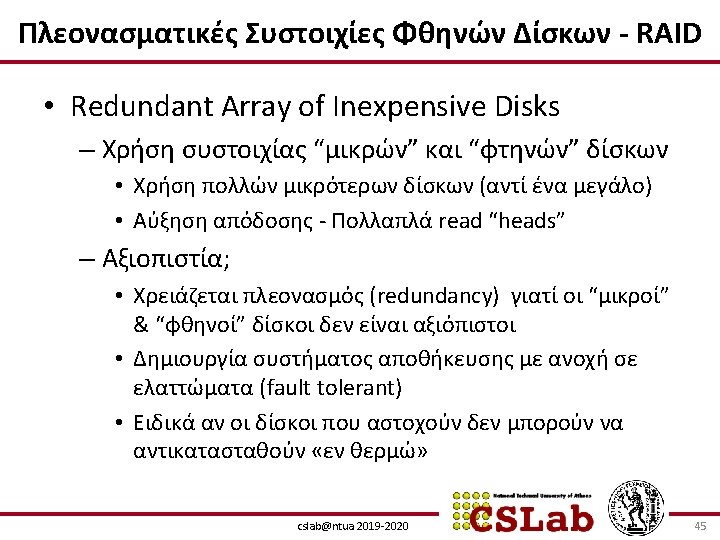

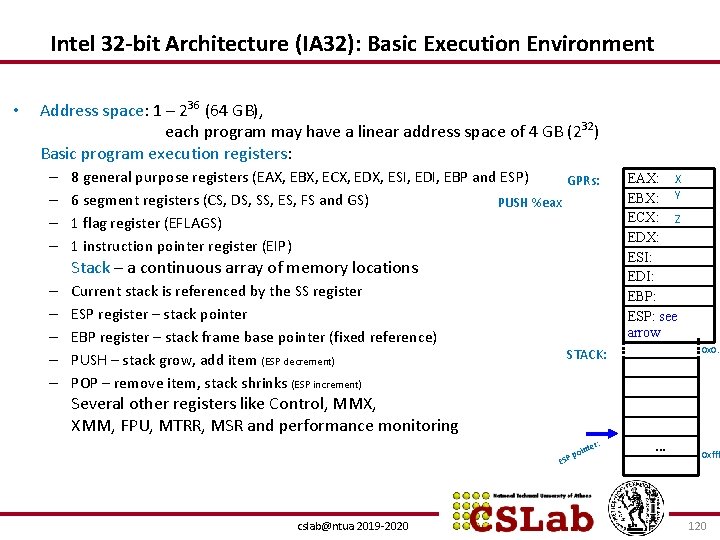

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax 1 flag register (EFLAGS) 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring ES cslab@ntua 2019 -2020 r: nte oi Pp . . . 0 xfff 120

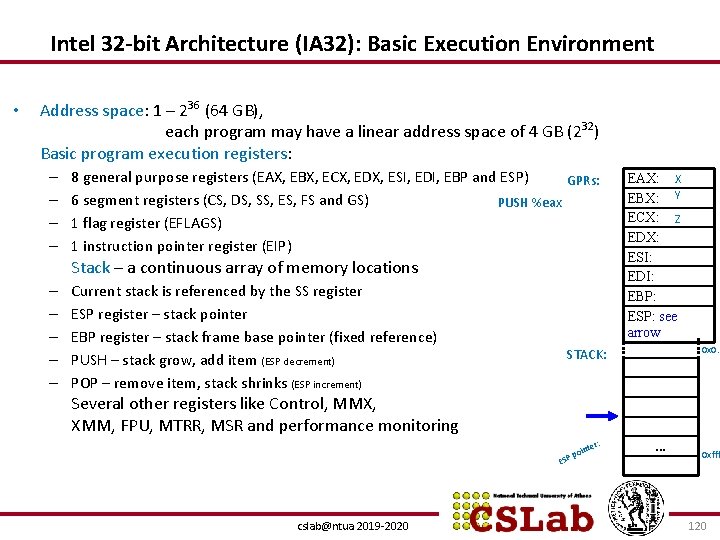

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax 1 flag register (EFLAGS) 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring ES cslab@ntua 2019 -2020 r: nte oi Pp . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax 1 flag register (EFLAGS) 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

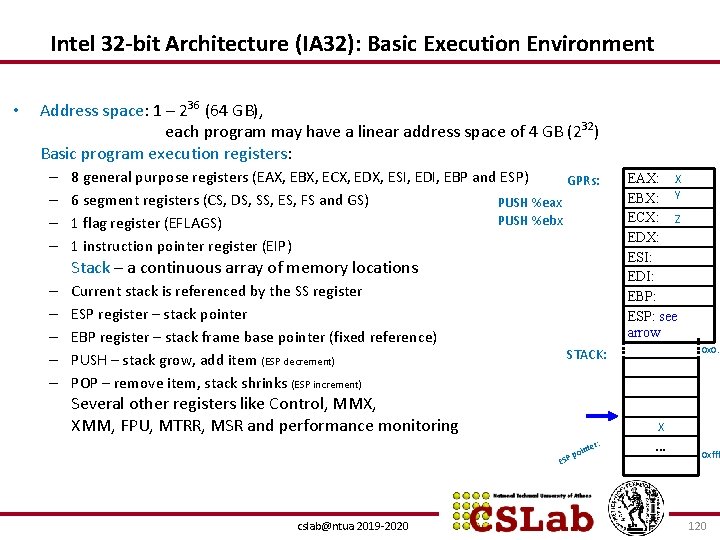

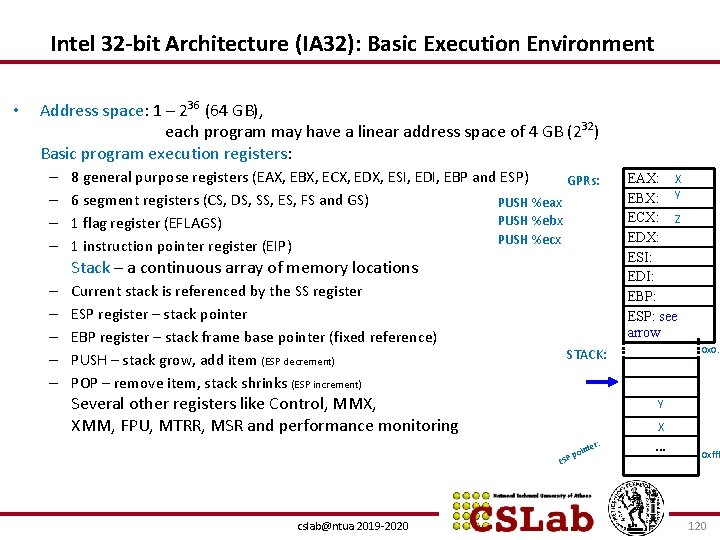

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring Y X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

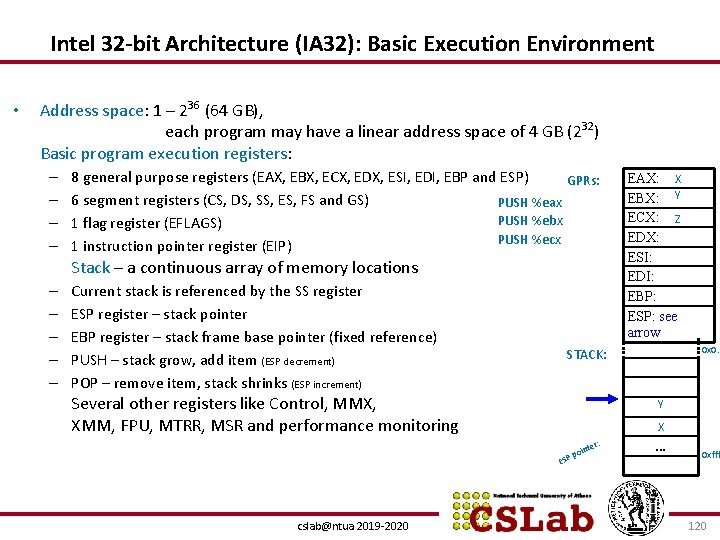

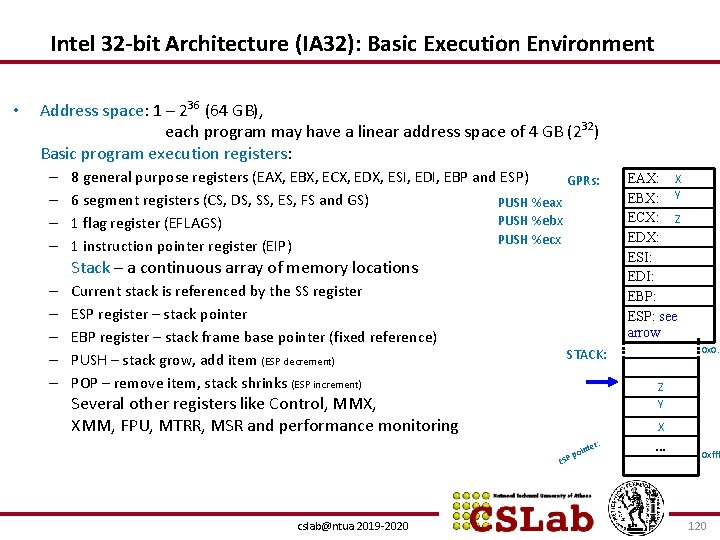

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring Y X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring Y X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

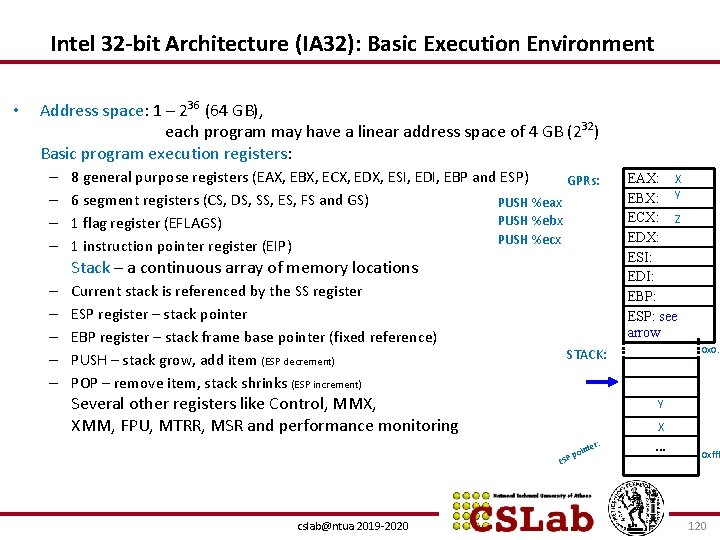

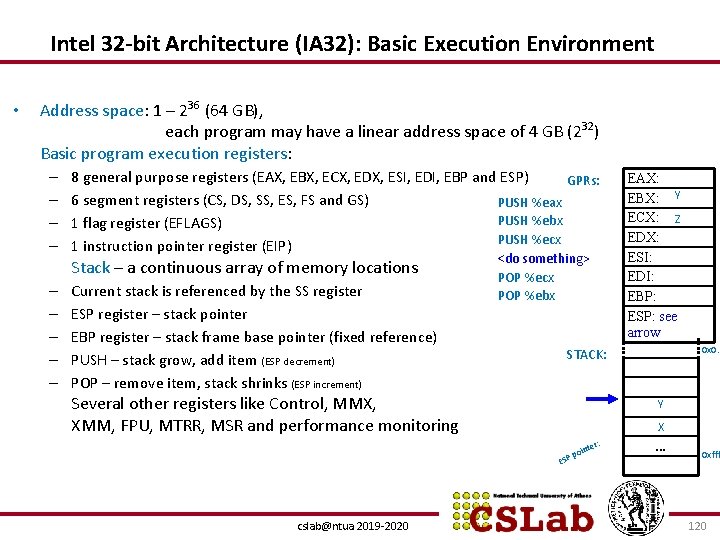

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) 0 x 0. . STACK: Z Y Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

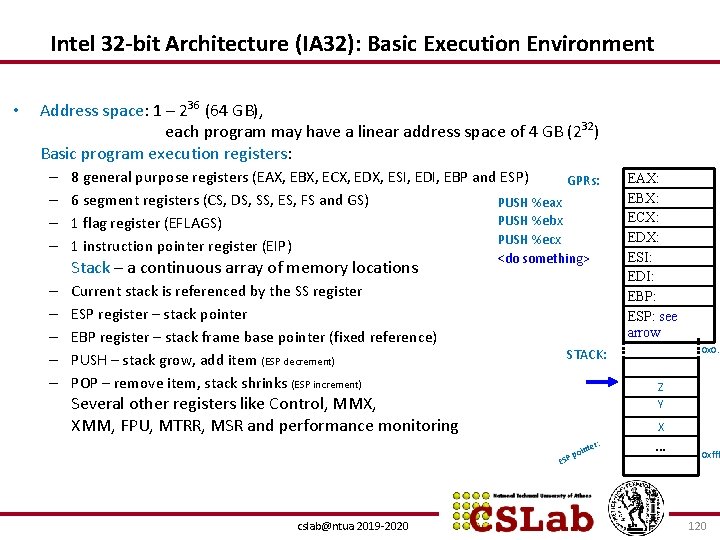

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> 0 x 0. . STACK: Z Y Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: EBX: ECX: EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx 0 x 0. . STACK: Z Y Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: EBX: ECX: EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx 0 x 0. . STACK: Z Y Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: EBX: ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring Y X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: EBX: ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx POP %ebx 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring Y X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: EBX: ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx POP %ebx 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring Y X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx POP %ebx 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx POP %ebx POP %eax 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx POP %ebx POP %eax 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring X ES r: nte oi Pp cslab@ntua 2019 -2020 EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow . . . 0 xfff 120

Intel 32 -bit Architecture (IA 32): Basic Execution Environment • Address space: 1 – 236 (64 GB), each program may have a linear address space of 4 GB (232) Basic program execution registers: – – 8 general purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, EBP and ESP) GPRs: 6 segment registers (CS, DS, SS, ES, FS and GS) PUSH %eax PUSH %ebx 1 flag register (EFLAGS) PUSH %ecx 1 instruction pointer register (EIP) Stack – a continuous array of memory locations – – – Current stack is referenced by the SS register ESP register – stack pointer EBP register – stack frame base pointer (fixed reference) PUSH – stack grow, add item (ESP decrement) POP – remove item, stack shrinks (ESP increment) <do something> POP %ecx POP %ebx POP %eax EAX: X EBX: Y ECX: Z EDX: ESI: EDI: EBP: ESP: see arrow 0 x 0. . STACK: Several other registers like Control, MMX, XMM, FPU, MTRR, MSR and performance monitoring ES cslab@ntua 2019 -2020 r: nte oi Pp . . . 0 xfff 120

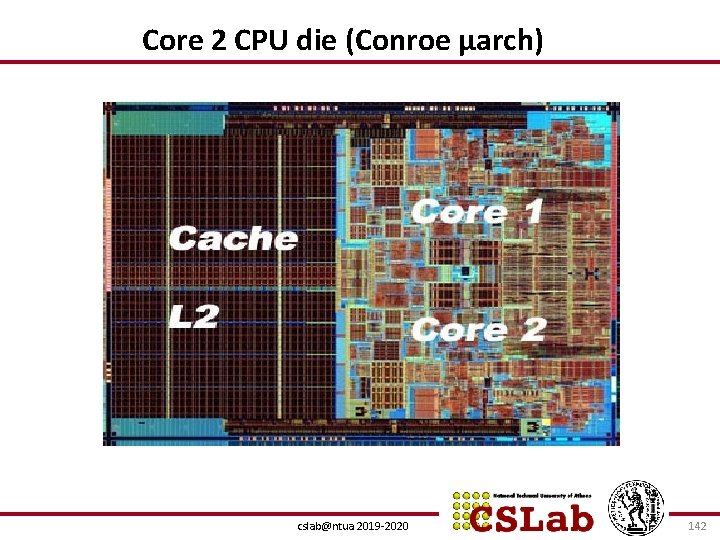

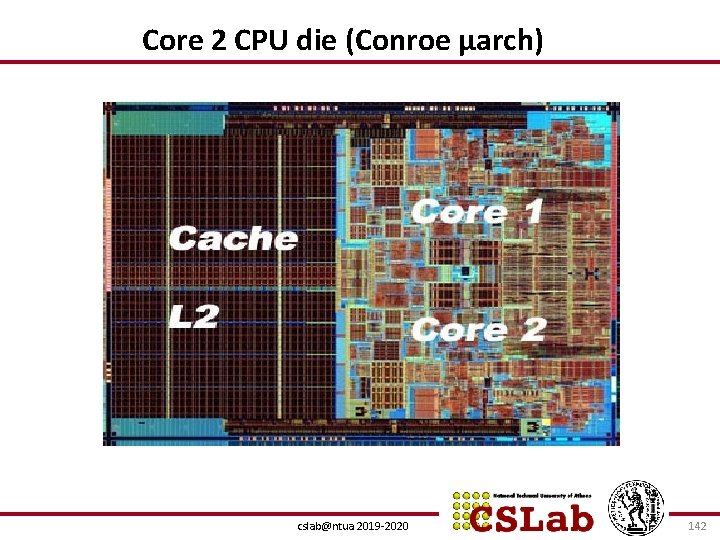

Core 2 CPU die (Conroe μarch) cslab@ntua 2019 -2020 142

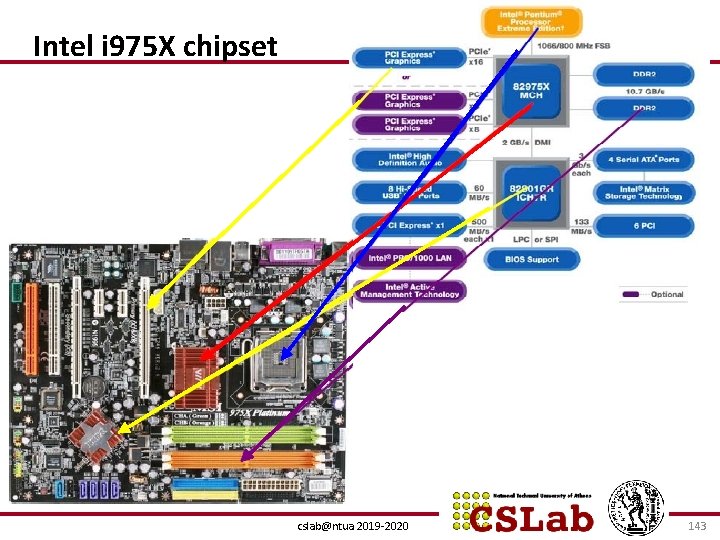

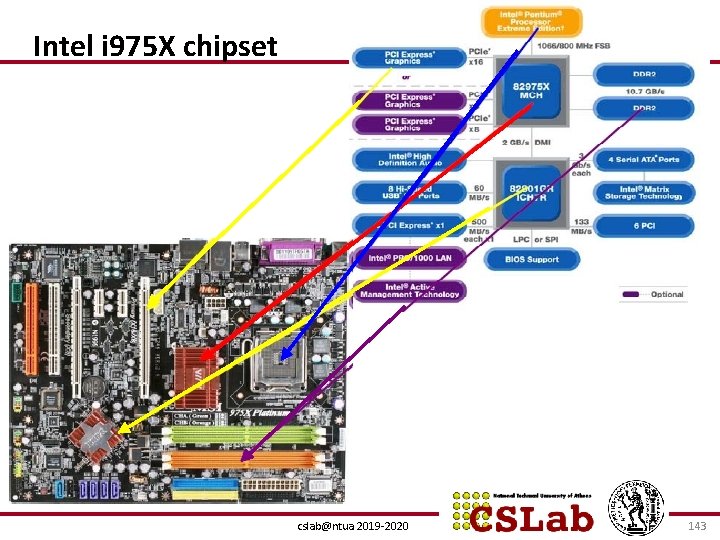

Intel i 975 X chipset cslab@ntua 2019 -2020 143

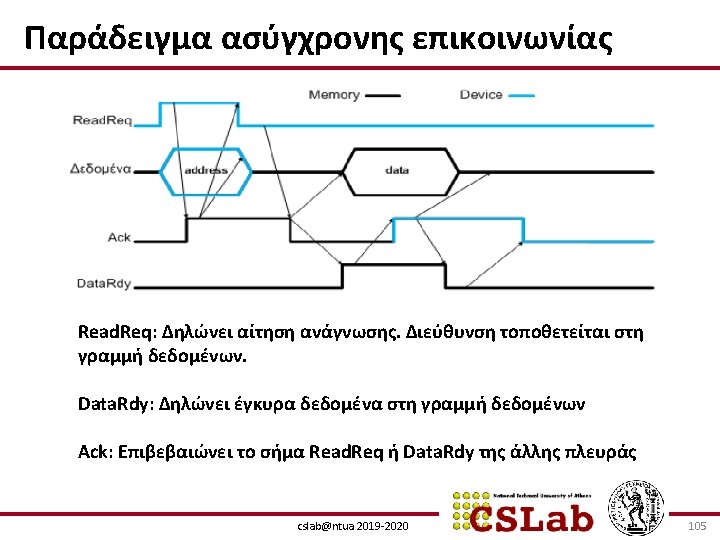

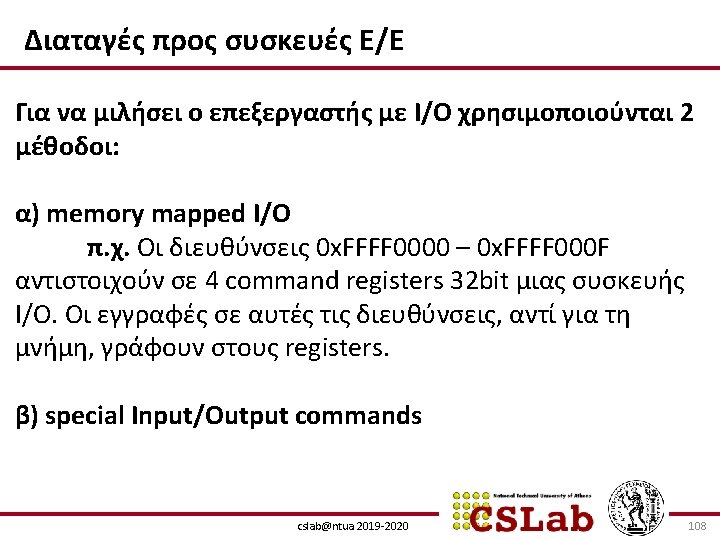

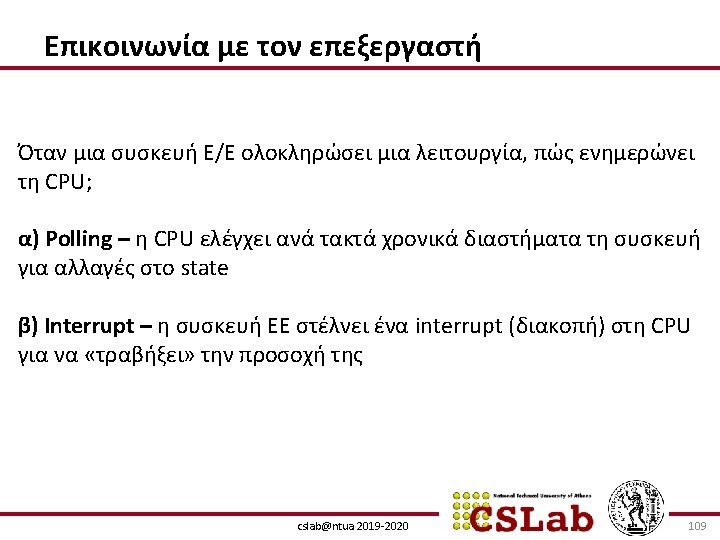

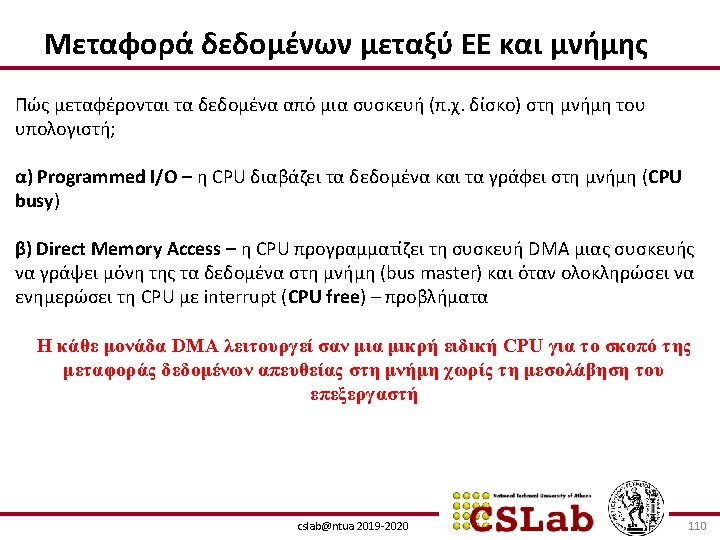

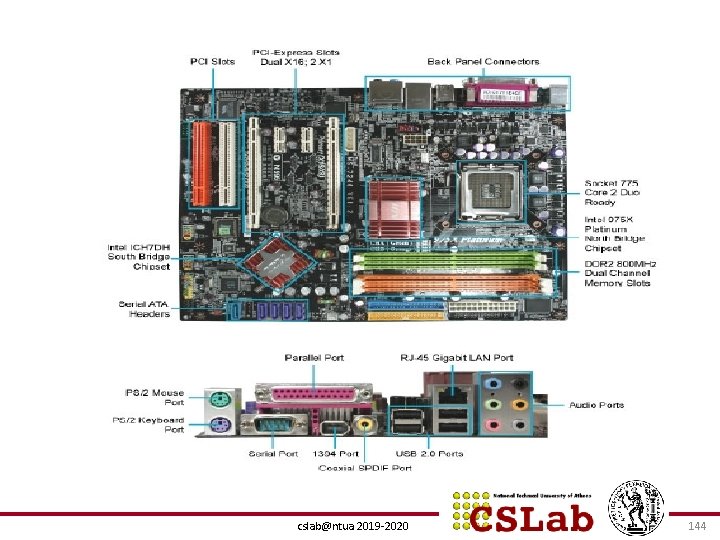

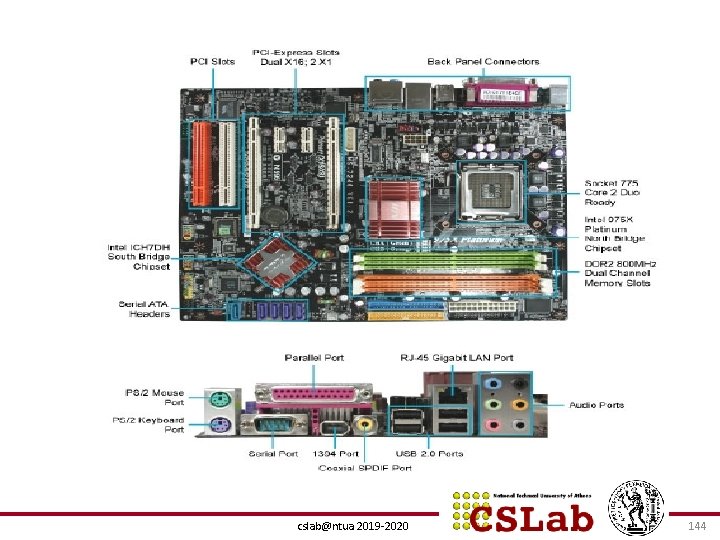

cslab@ntua 2019 -2020 144