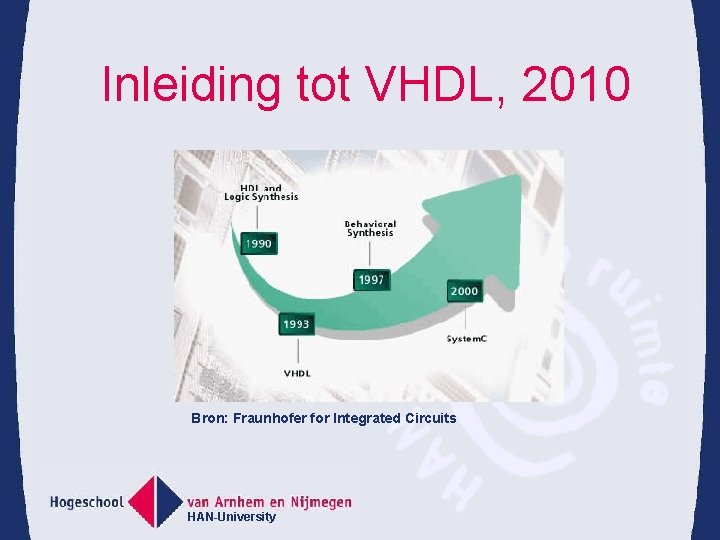

Inleiding tot VHDL 2010 Bron Fraunhofer for Integrated

Inleiding tot VHDL, 2010 Bron: Fraunhofer for Integrated Circuits HAN-University

Waarom de taal VHDL (VHSLI High Description Language? Doel van de Inleiding tot VHDL Boek: Digital System Design, Zwolinski PP: Scholar • Onderwerpen: RTL design flow Basisconcept VHDL Entity en Architectuur Typen Architectuur beschrijvingen Combinaties van typen beschrijvingen: D-Flipflop Testbenches in VHDL HAN-University 2

Waarom de taal VHDL? • Krachtig hulpmiddel bij het ontwerpen van digitale schakelingen: o Vastleggen specificaties ontwerp. o Systematische opdeling van ontwerp. o Taal onafhankelijk van technologie. o Kunt je eigen ontwerpmethoden kiezen: bottom up/top down. o Allerlei ontwerpstrategien zijn mogelijk: syncroon, asyncroon, PLA, poorten. o Het is een IEEE gestandaardiseerde taal o “Leesbare” taal. Lijkt op C++/ • Automatisering: Eletronic Design Automation (EDA) o Synthesis: vertaling van specificaties naar een implementatie in logic gates o Simulatie: checken op goede werking • VHDL staat voor: VHSIC-HDL en dat staat voor: Very High Speed Integrated Circuit High Description Language HAN-University

RTL (Register Transfer Level) Design Flow RTL simulatie VHDL RTL beschrijvingen RTL synthese Structural VHDL Structural simulatie SDF timing information Timing simulatie VHDL testbench EDIF netlist Place and route back annotation Implementatie HAN-University 4

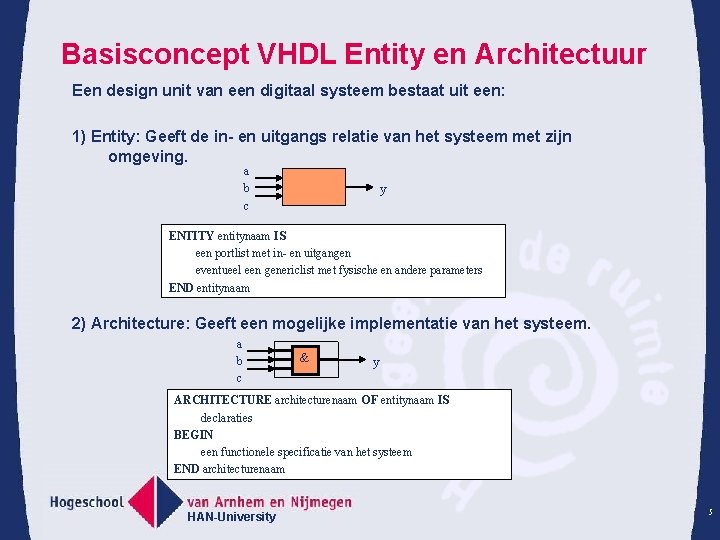

Basisconcept VHDL Entity en Architectuur Een design unit van een digitaal systeem bestaat uit een: 1) Entity: Geeft de in- en uitgangs relatie van het systeem met zijn omgeving. a b c y ENTITY entitynaam IS een portlist met in- en uitgangen eventueel een genericlist met fysische en andere parameters END entitynaam 2) Architecture: Geeft een mogelijke implementatie van het systeem. a b c & y ARCHITECTURE architecturenaam OF entitynaam IS declaraties BEGIN een functionele specificatie van het systeem END architecturenaam HAN-University 5

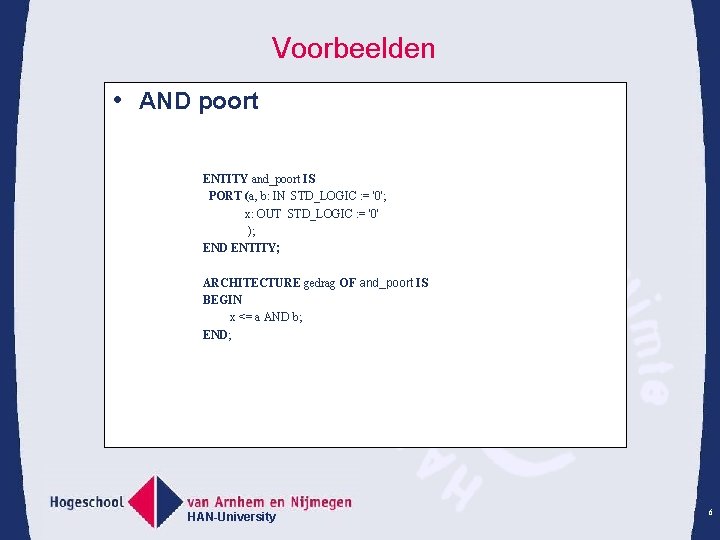

Voorbeelden • AND poort ENTITY and_poort IS PORT (a, b: IN STD_LOGIC : = '0'; x: OUT STD_LOGIC : = '0' ); END ENTITY; ARCHITECTURE gedrag OF and_poort IS BEGIN x <= a AND b; END; HAN-University 6

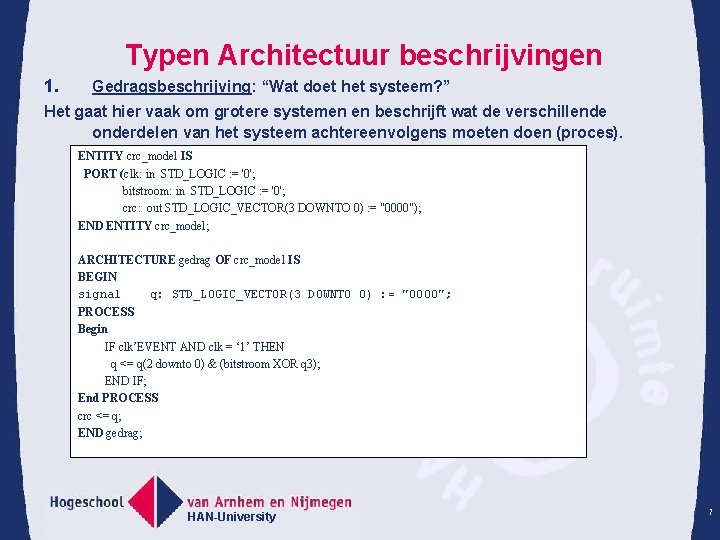

Typen Architectuur beschrijvingen 1. Gedragsbeschrijving: “Wat doet het systeem? ” Het gaat hier vaak om grotere systemen en beschrijft wat de verschillende onderdelen van het systeem achtereenvolgens moeten doen (proces). ENTITY crc_model IS PORT (clk: in STD_LOGIC : = '0'; bitstroom: in STD_LOGIC : = '0'; crc: out STD_LOGIC_VECTOR(3 DOWNTO 0) : = "0000"); END ENTITY crc_model; ARCHITECTURE gedrag OF crc_model IS BEGIN signal q: STD_LOGIC_VECTOR(3 DOWNTO 0) : = "0000"; PROCESS Begin IF clk’EVENT AND clk = ‘ 1’ THEN q <= q(2 downto 0) & (bitstroom XOR q 3); END IF; End PROCESS crc <= q; END gedrag; HAN-University 7

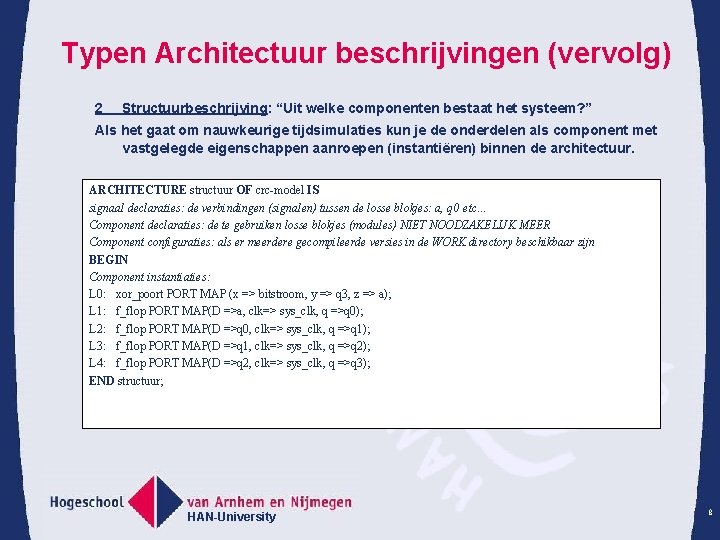

Typen Architectuur beschrijvingen (vervolg) 2 Structuurbeschrijving: “Uit welke componenten bestaat het systeem? ” Als het gaat om nauwkeurige tijdsimulaties kun je de onderdelen als component met vastgelegde eigenschappen aanroepen (instantiëren) binnen de architectuur. ARCHITECTURE structuur OF crc-model IS signaal declaraties: de verbindingen (signalen) tussen de losse blokjes: a, q 0 etc… Component declaraties: de te gebruiken losse blokjes (modules) NIET NOODZAKELIJK MEER Component configuraties: als er meerdere gecompileerde versies in de WORK directory beschikbaar zijn BEGIN Component instantiaties: L 0: xor_poort PORT MAP (x => bitstroom, y => q 3, z => a); L 1: f_flop PORT MAP(D =>a, clk=> sys_clk, q =>q 0); L 2: f_flop PORT MAP(D =>q 0, clk=> sys_clk, q =>q 1); L 3: f_flop PORT MAP(D =>q 1, clk=> sys_clk, q =>q 2); L 4: f_flop PORT MAP(D =>q 2, clk=> sys_clk, q =>q 3); END structuur; HAN-University 8

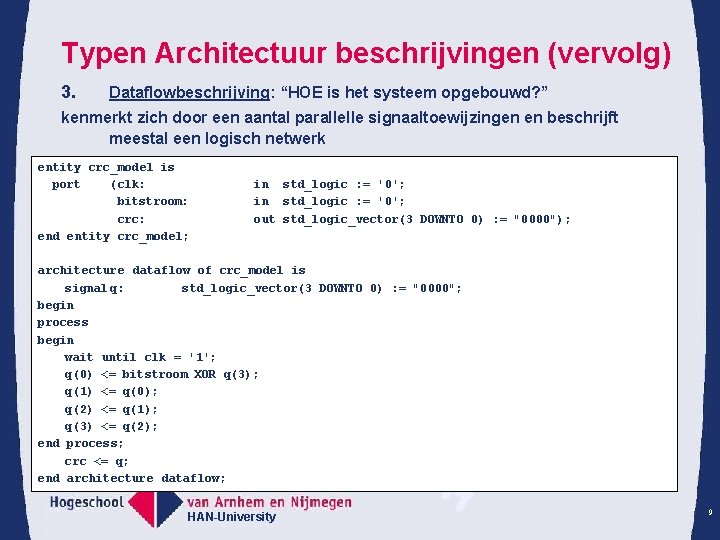

Typen Architectuur beschrijvingen (vervolg) 3. Dataflowbeschrijving: “HOE is het systeem opgebouwd? ” kenmerkt zich door een aantal parallelle signaaltoewijzingen en beschrijft meestal een logisch netwerk entity crc_model is port (clk: bitstroom: crc: end entity crc_model; in std_logic : = '0'; out std_logic_vector(3 DOWNTO 0) : = "0000"); architecture dataflow of crc_model is signal q: std_logic_vector(3 DOWNTO 0) : = "0000"; begin process begin wait until clk = '1'; q(0) <= bitstroom XOR q(3); q(1) <= q(0); q(2) <= q(1); q(3) <= q(2); end process; crc <= q; end architecture dataflow; HAN-University 9

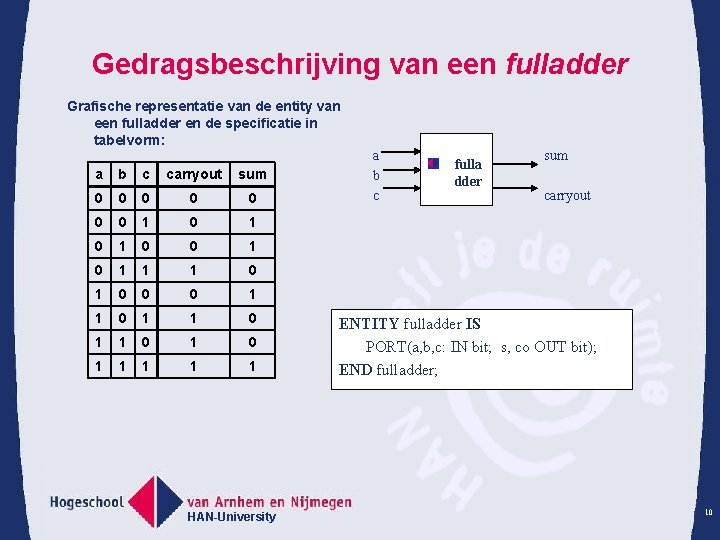

Gedragsbeschrijving van een fulladder Grafische representatie van de entity van een fulladder en de specificatie in tabelvorm: a b c carryout sum 0 0 0 0 1 0 1 0 1 1 1 0 0 0 1 1 0 1 1 1 HAN-University a b c fulla dder sum carryout ENTITY fulladder IS PORT(a, b, c: IN bit; s, co OUT bit); END fulladder; 10

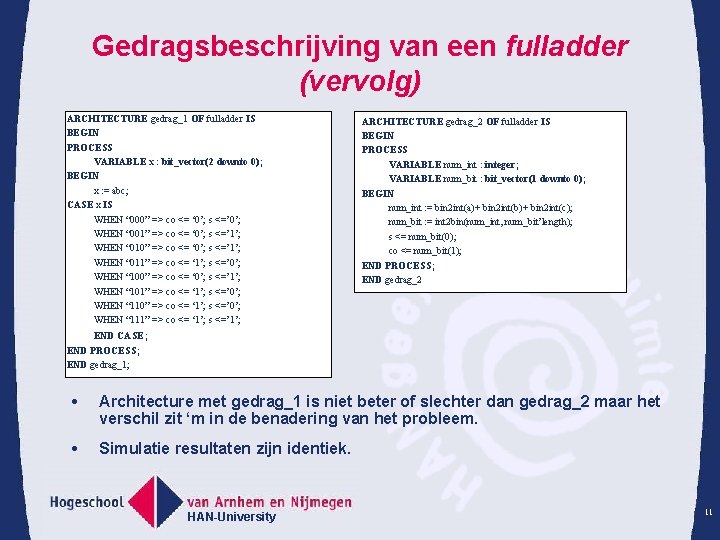

Gedragsbeschrijving van een fulladder (vervolg) ARCHITECTURE gedrag_1 OF fulladder IS BEGIN PROCESS VARIABLE x : bit_vector(2 downto 0); BEGIN x : = abc; CASE x IS WHEN “ 000” => co <= ‘ 0’; s <=’ 0’; WHEN “ 001” => co <= ‘ 0’; s <=’ 1’; WHEN “ 010” => co <= ‘ 0’; s <=’ 1’; WHEN “ 011” => co <= ‘ 1’; s <=’ 0’; WHEN “ 100” => co <= ‘ 0’; s <=’ 1’; WHEN “ 101” => co <= ‘ 1’; s <=’ 0’; WHEN “ 110” => co <= ‘ 1’; s <=’ 0’; WHEN “ 111” => co <= ‘ 1’; s <=’ 1’; ARCHITECTURE gedrag_2 OF fulladder IS BEGIN PROCESS VARIABLE num_int : integer; VARIABLE num_bit : bit_vector(1 downto 0); BEGIN num_int : = bin 2 int(a)+ bin 2 int(b)+ bin 2 int(c); num_bit : = int 2 bin(num_int, num_bit’length); s <= num_bit(0); co <= num_bit(1); END PROCESS; END gedrag_2 END CASE; END PROCESS; END gedrag_1; • Architecture met gedrag_1 is niet beter of slechter dan gedrag_2 maar het verschil zit ‘m in de benadering van het probleem. • Simulatie resultaten zijn identiek. HAN-University 11

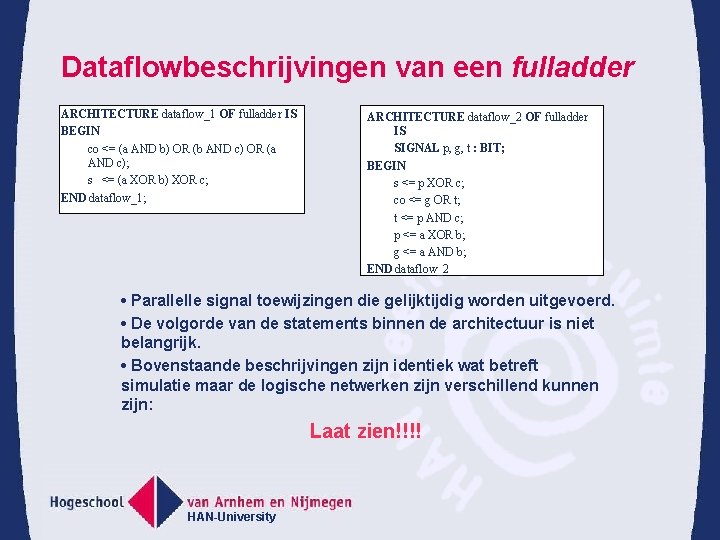

Dataflowbeschrijvingen van een fulladder ARCHITECTURE dataflow_1 OF fulladder IS BEGIN co <= (a AND b) OR (b AND c) OR (a AND c); s <= (a XOR b) XOR c; END dataflow_1; ARCHITECTURE dataflow_2 OF fulladder IS SIGNAL p, g, t : BIT; BEGIN s <= p XOR c; co <= g OR t; t <= p AND c; p <= a XOR b; g <= a AND b; END dataflow_2 • Parallelle signal toewijzingen die gelijktijdig worden uitgevoerd. • De volgorde van de statements binnen de architectuur is niet belangrijk. • Bovenstaande beschrijvingen zijn identiek wat betreft simulatie maar de logische netwerken zijn verschillend kunnen zijn: Laat zien!!!! HAN-University

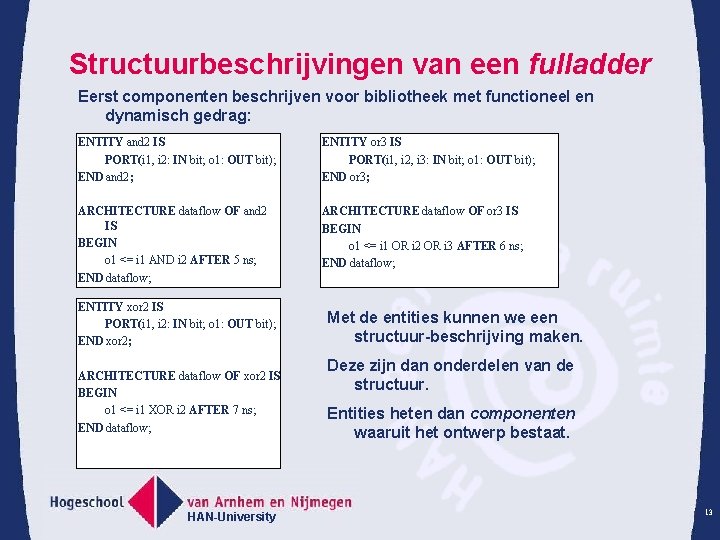

Structuurbeschrijvingen van een fulladder Eerst componenten beschrijven voor bibliotheek met functioneel en dynamisch gedrag: ENTITY and 2 IS PORT(i 1, i 2: IN bit; o 1: OUT bit); END and 2; ENTITY or 3 IS PORT(i 1, i 2, i 3: IN bit; o 1: OUT bit); END or 3; ARCHITECTURE dataflow OF and 2 IS BEGIN o 1 <= i 1 AND i 2 AFTER 5 ns; END dataflow; ARCHITECTURE dataflow OF or 3 IS BEGIN o 1 <= i 1 OR i 2 OR i 3 AFTER 6 ns; END dataflow; ENTITY xor 2 IS PORT(i 1, i 2: IN bit; o 1: OUT bit); END xor 2; ARCHITECTURE dataflow OF xor 2 IS BEGIN o 1 <= i 1 XOR i 2 AFTER 7 ns; END dataflow; HAN-University Met de entities kunnen we een structuur-beschrijving maken. Deze zijn dan onderdelen van de structuur. Entities heten dan componenten waaruit het ontwerp bestaat. 13

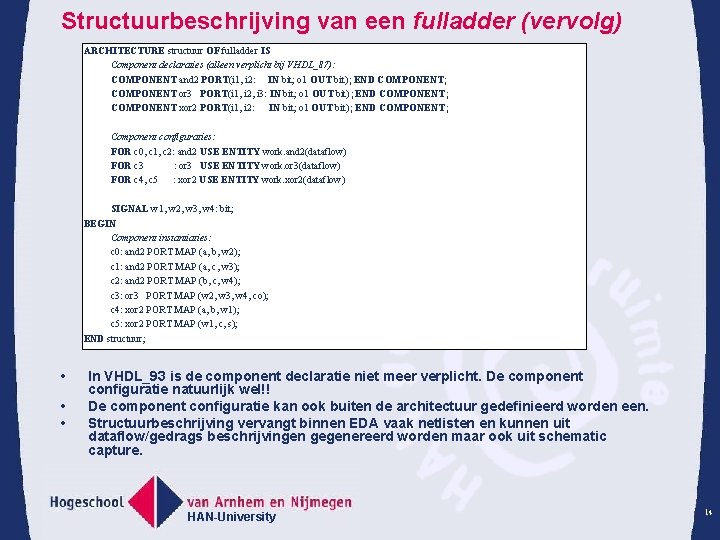

Structuurbeschrijving van een fulladder (vervolg) ARCHITECTURE structuur OF fulladder IS Component declaraties (alleen verplicht bij VHDL_87): COMPONENT and 2 PORT(i 1, i 2: IN bit; o 1 OUT bit); END COMPONENT; COMPONENT or 3 PORT(i 1, i 2, i 3: IN bit; o 1 OUT bit); END COMPONENT; COMPONENT xor 2 PORT(i 1, i 2: IN bit; o 1 OUT bit); END COMPONENT; Component configuraties: FOR c 0, c 1, c 2: and 2 USE ENTITY work. and 2(dataflow) FOR c 3 : or 3 USE ENTITY work. or 3(dataflow) FOR c 4, c 5 : xor 2 USE ENTITY work. xor 2(dataflow) SIGNAL w 1, w 2, w 3, w 4: bit; BEGIN Component instantiaties: c 0: and 2 PORT MAP (a, b, w 2); c 1: and 2 PORT MAP (a, c, w 3); c 2: and 2 PORT MAP (b, c, w 4); c 3: or 3 PORT MAP (w 2, w 3, w 4, co); c 4: xor 2 PORT MAP (a, b, w 1); c 5: xor 2 PORT MAP (w 1, c, s); END structuur; • • • In VHDL_93 is de component declaratie niet meer verplicht. De component configuratie natuurlijk wel!! De component configuratie kan ook buiten de architectuur gedefinieerd worden een. Structuurbeschrijving vervangt binnen EDA vaak netlisten en kunnen uit dataflow/gedrags beschrijvingen gegenereerd worden maar ook uit schematic capture. HAN-University 14

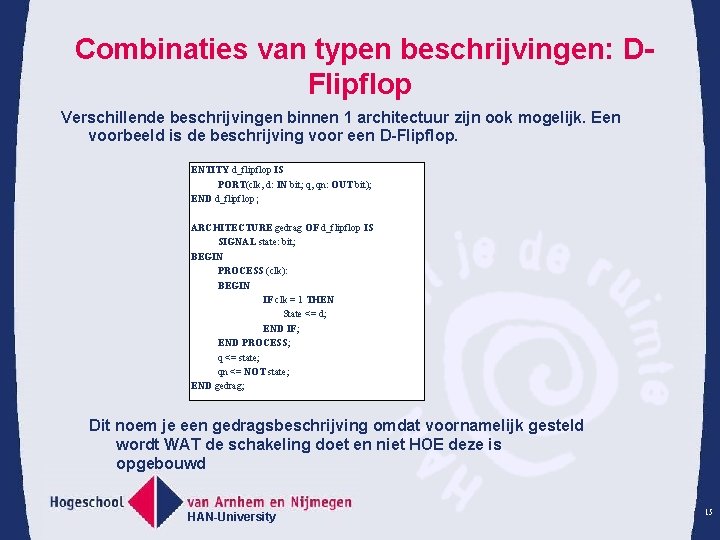

Combinaties van typen beschrijvingen: DFlipflop Verschillende beschrijvingen binnen 1 architectuur zijn ook mogelijk. Een voorbeeld is de beschrijving voor een D-Flipflop. ENTITY d_flipflop IS PORT(clk, d: IN bit; q, qn: OUT bit); END d_flipflop; ARCHITECTURE gedrag OF d_flipflop IS SIGNAL state: bit; BEGIN PROCESS (clk): BEGIN IF clk = 1 THEN State <= d; END IF; END PROCESS; q <= state; qn <= NOT state; END gedrag; Dit noem je een gedragsbeschrijving omdat voornamelijk gesteld wordt WAT de schakeling doet en niet HOE deze is opgebouwd HAN-University 15

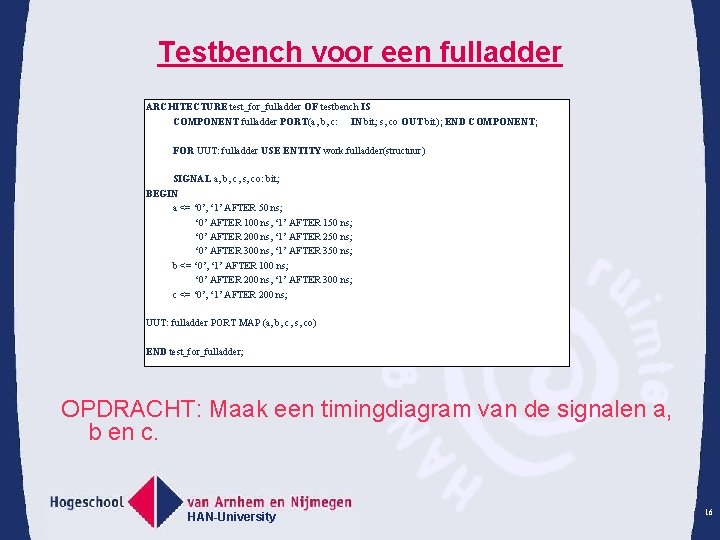

Testbench voor een fulladder ARCHITECTURE test_for_fulladder OF testbench IS COMPONENT fulladder PORT(a, b, c: IN bit; s, co OUT bit); END COMPONENT; FOR UUT: fulladder USE ENTITY work. fulladder(structuur) SIGNAL a, b, c, s, co: bit; BEGIN a <= ‘ 0’, ‘ 1’ AFTER 50 ns; ‘ 0’ AFTER 100 ns, ‘ 1’ AFTER 150 ns; ‘ 0’ AFTER 200 ns, ‘ 1’ AFTER 250 ns; ‘ 0’ AFTER 300 ns, ‘ 1’ AFTER 350 ns; b <= ‘ 0’, ‘ 1’ AFTER 100 ns; ‘ 0’ AFTER 200 ns, ‘ 1’ AFTER 300 ns; c <= ‘ 0’, ‘ 1’ AFTER 200 ns; UUT: fulladder PORT MAP (a, b, c, s, co) END test_for_fulladder; OPDRACHT: Maak een timingdiagram van de signalen a, b en c. HAN-University 16

- Slides: 16