Informatika o peruen Interrupt HW SW 2006 CPU

- Slides: 14

Informatika – o přerušení Interrupt HW, SW 2006

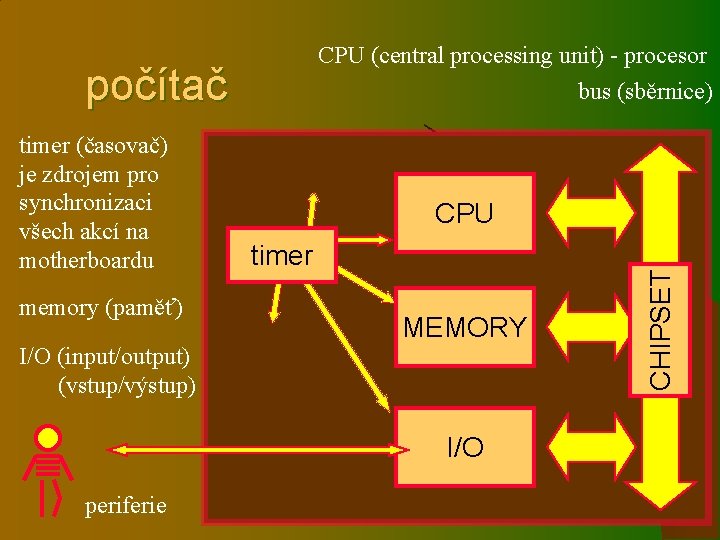

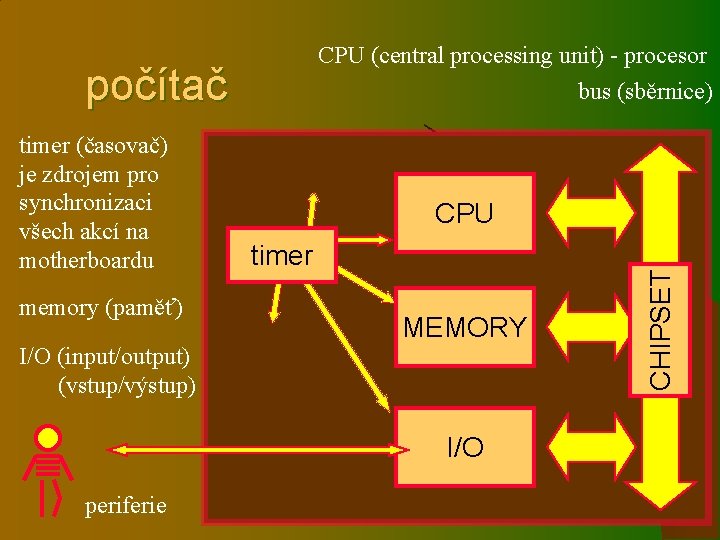

CPU (central processing unit) - procesor bus (sběrnice) počítač memory (paměť) I/O (input/output) (vstup/výstup) CPU timer MEMORY I/O periferie CHIPSET BUS timer (časovač) je zdrojem pro synchronizaci všech akcí na motherboardu

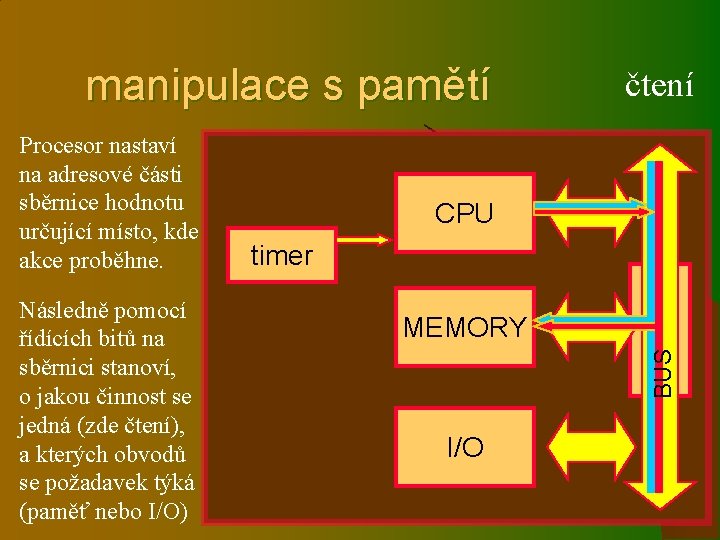

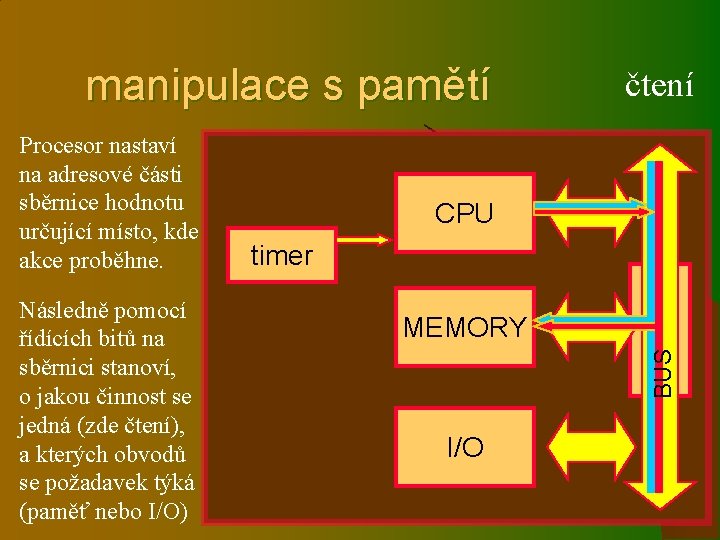

manipulace s pamětí Následně pomocí řídících bitů na sběrnici stanoví, o jakou činnost se jedná (zde čtení), a kterých obvodů se požadavek týká (paměť nebo I/O) CPU timer MEMORY I/O CHIPSET BUS Procesor nastaví na adresové části sběrnice hodnotu určující místo, kde akce proběhne. čtení

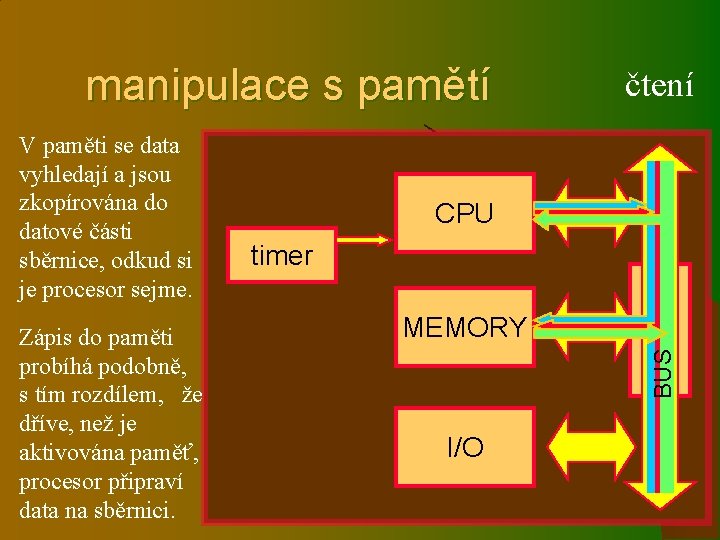

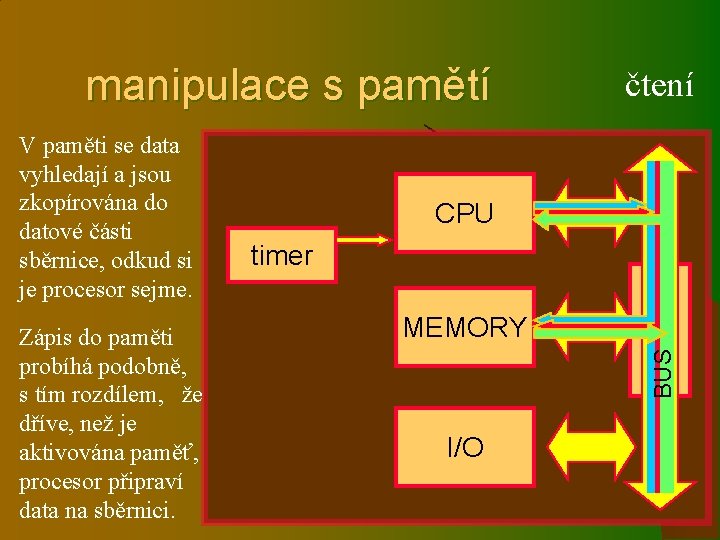

manipulace s pamětí Zápis do paměti probíhá podobně, s tím rozdílem, že dříve, než je aktivována paměť, procesor připraví data na sběrnici. CPU timer MEMORY I/O CHIPSET BUS V paměti se data vyhledají a jsou zkopírována do datové části sběrnice, odkud si je procesor sejme. čtení

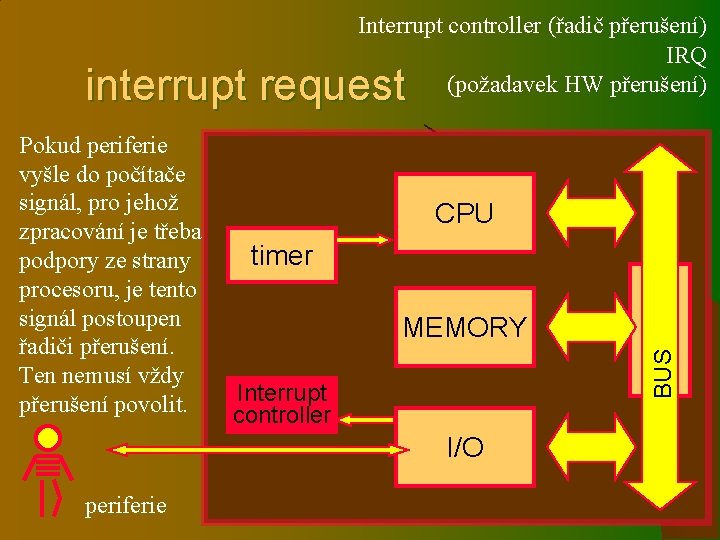

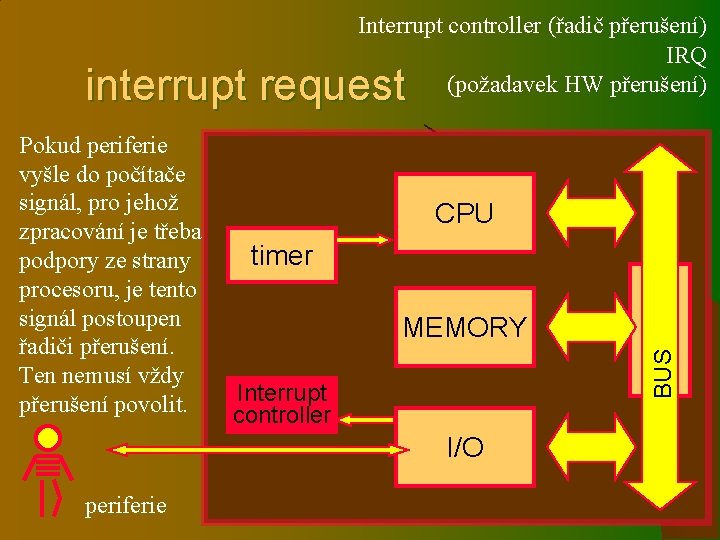

Interrupt controller (řadič přerušení) IRQ (požadavek HW přerušení) interrupt request CPU timer MEMORY Interrupt controller I/O periferie CHIPSET BUS Pokud periferie vyšle do počítače signál, pro jehož zpracování je třeba podpory ze strany procesoru, je tento signál postoupen řadiči přerušení. Ten nemusí vždy přerušení povolit.

interrupt request l l l Chování řadiče definuje procesor zápisem vhodné masky do řadiče. Tak lze prostřednictvím řadiče jednotlivým periferiím přerušení zakázat. Řadič rozlišuje 15 (22…) úrovní hardwarového přerušení lišících se prioritou (nižší úroveň = vyšší priorita). Pokud se přerušení uplatní, odvodí řadič přerušení adresu obslužného programu z dané hardwarové úrovně.

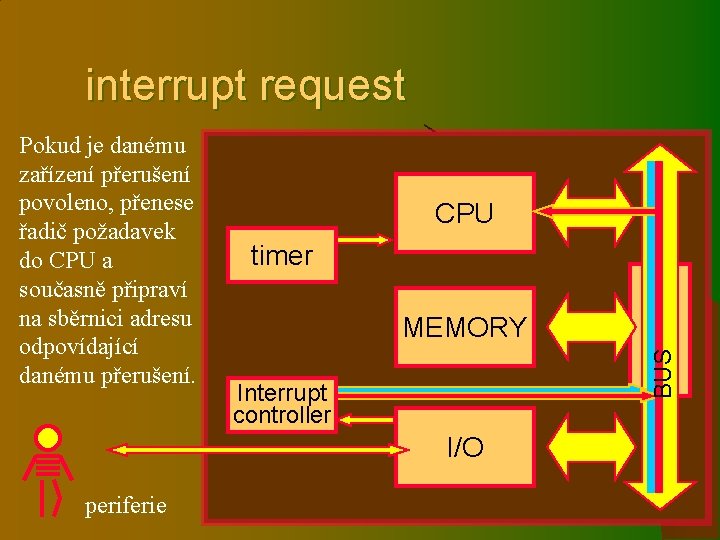

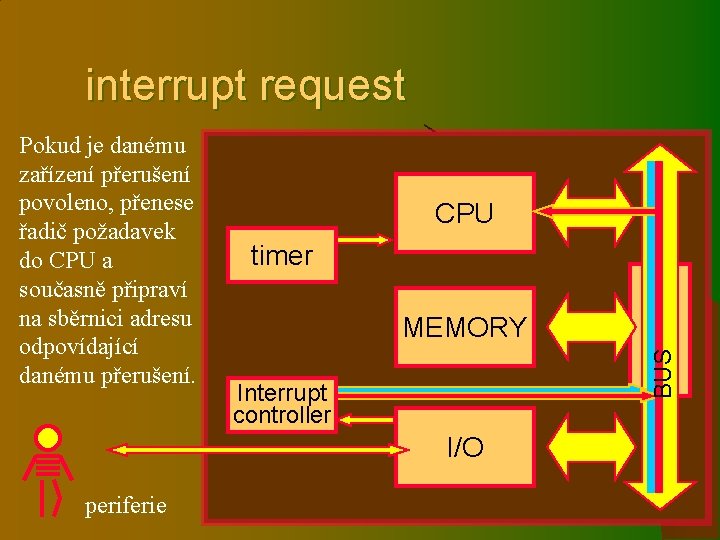

interrupt request CPU timer MEMORY Interrupt controller I/O periferie CHIPSET BUS Pokud je danému zařízení přerušení povoleno, přenese řadič požadavek do CPU a současně připraví na sběrnici adresu odpovídající danému přerušení.

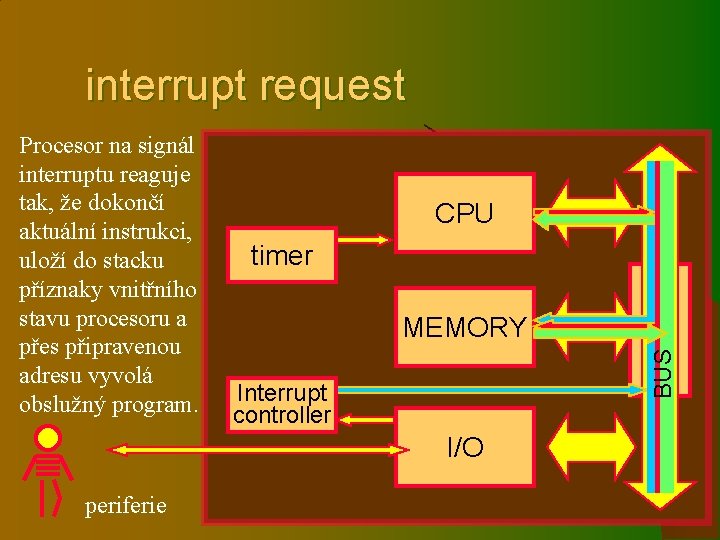

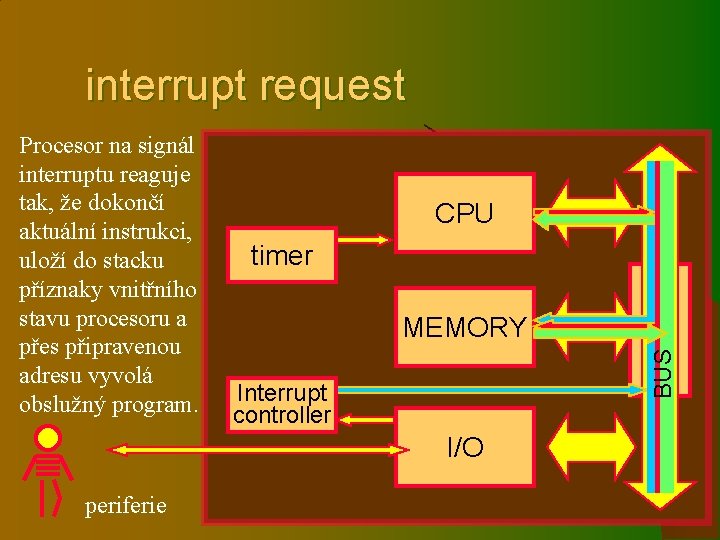

interrupt request CPU timer MEMORY Interrupt controller I/O periferie CHIPSET BUS Procesor na signál interruptu reaguje tak, že dokončí aktuální instrukci, uloží do stacku příznaky vnitřního stavu procesoru a přes připravenou adresu vyvolá obslužný program.

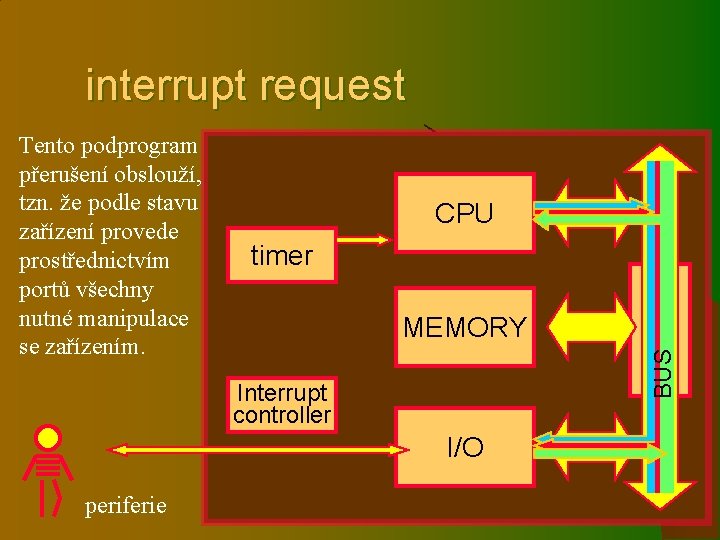

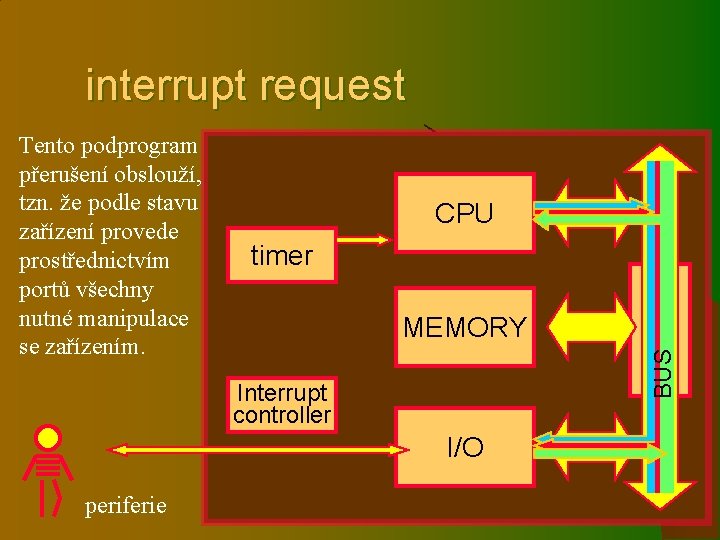

interrupt request CPU timer MEMORY Interrupt controller I/O periferie CHIPSET BUS Tento podprogram přerušení obslouží, tzn. že podle stavu zařízení provede prostřednictvím portů všechny nutné manipulace se zařízením.

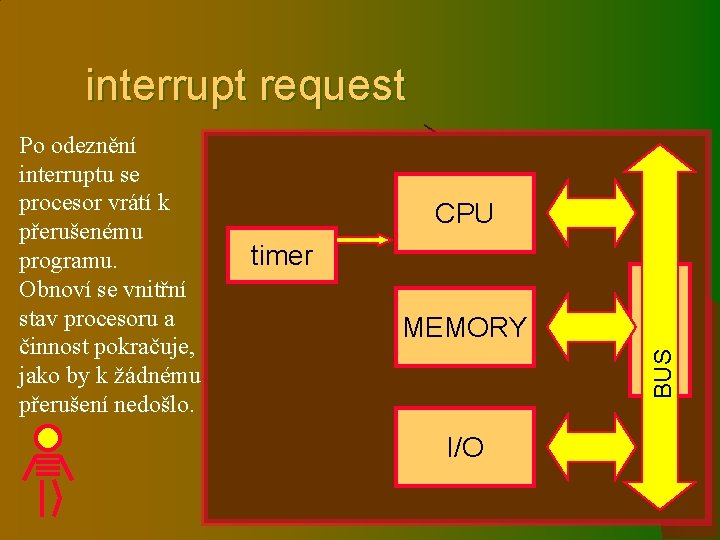

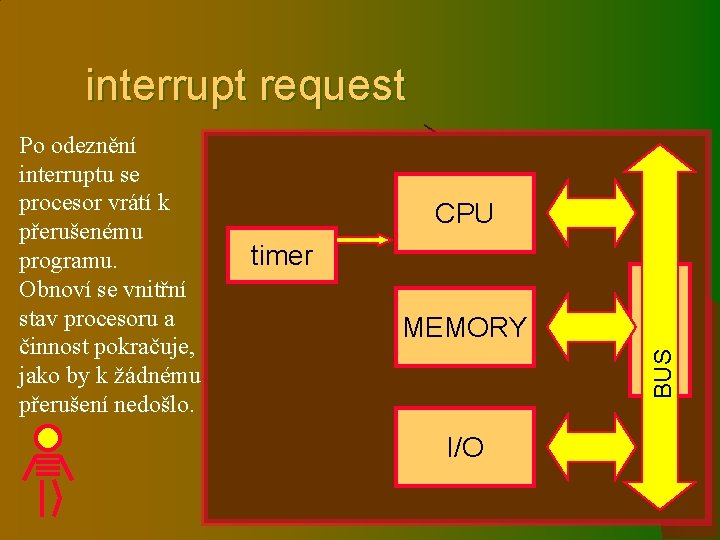

interrupt request CPU timer MEMORY I/O CHIPSET BUS Po odeznění interruptu se procesor vrátí k přerušenému programu. Obnoví se vnitřní stav procesoru a činnost pokračuje, jako by k žádnému přerušení nedošlo.

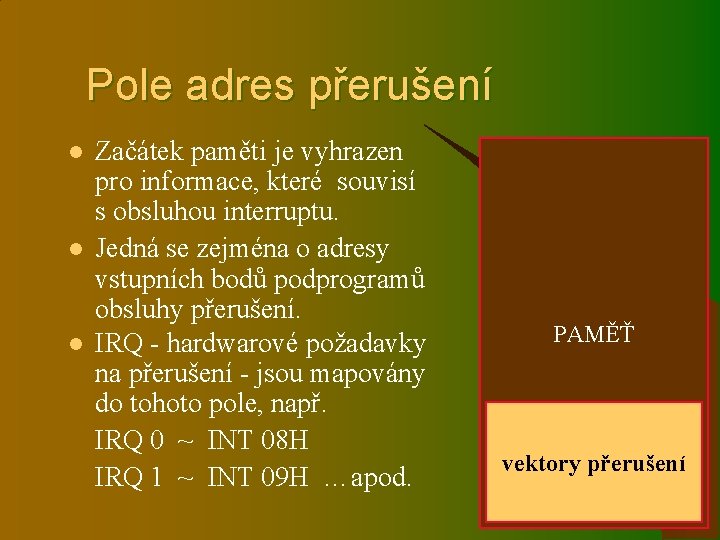

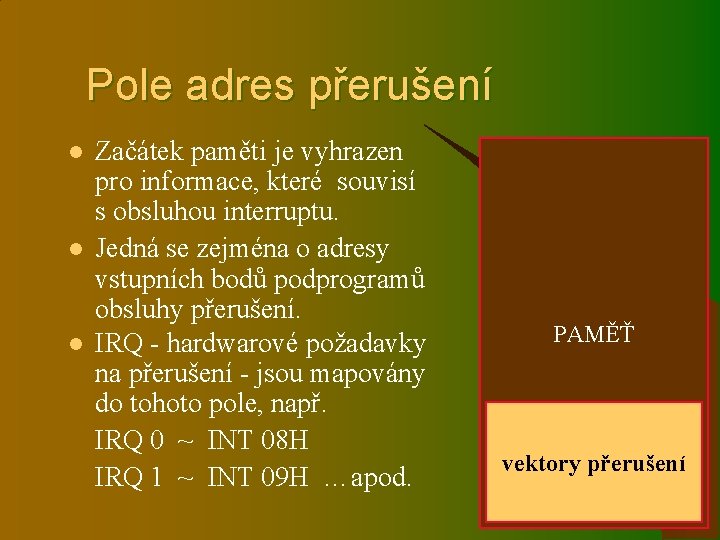

Pole adres přerušení l l l Začátek paměti je vyhrazen pro informace, které souvisí s obsluhou interruptu. Jedná se zejména o adresy vstupních bodů podprogramů obsluhy přerušení. IRQ - hardwarové požadavky na přerušení - jsou mapovány do tohoto pole, např. IRQ 0 ~ INT 08 H IRQ 1 ~ INT 09 H …apod. PAMĚŤ vektory přerušení

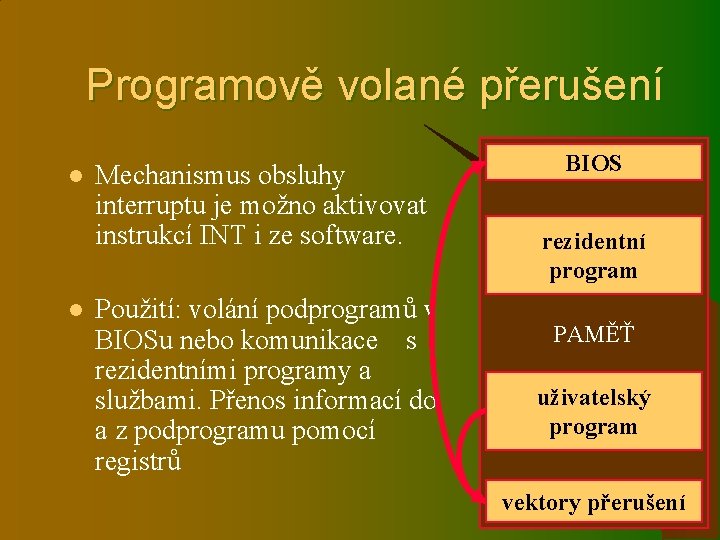

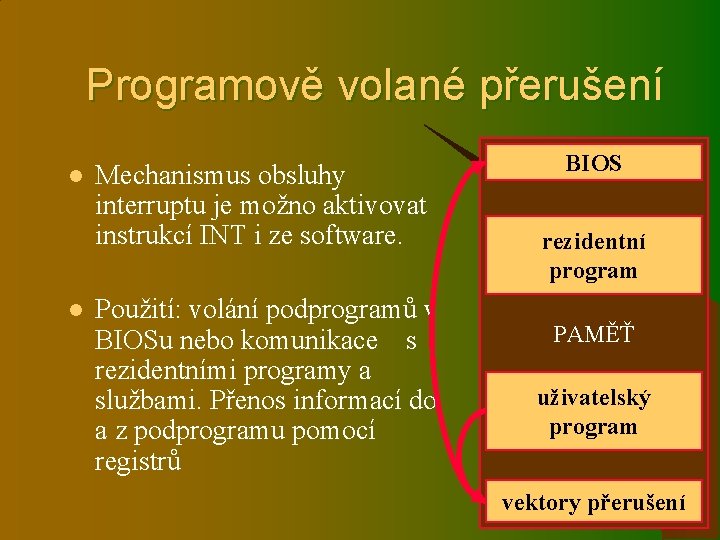

Programově volané přerušení l l Mechanismus obsluhy interruptu je možno aktivovat instrukcí INT i ze software. Použití: volání podprogramů v BIOSu nebo komunikace s rezidentními programy a službami. Přenos informací do a z podprogramu pomocí registrů BIOS rezidentní program PAMĚŤ uživatelský program vektory přerušení

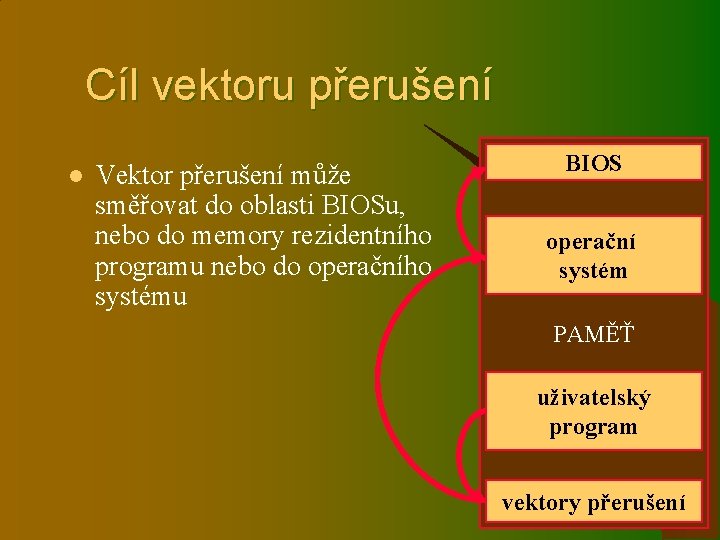

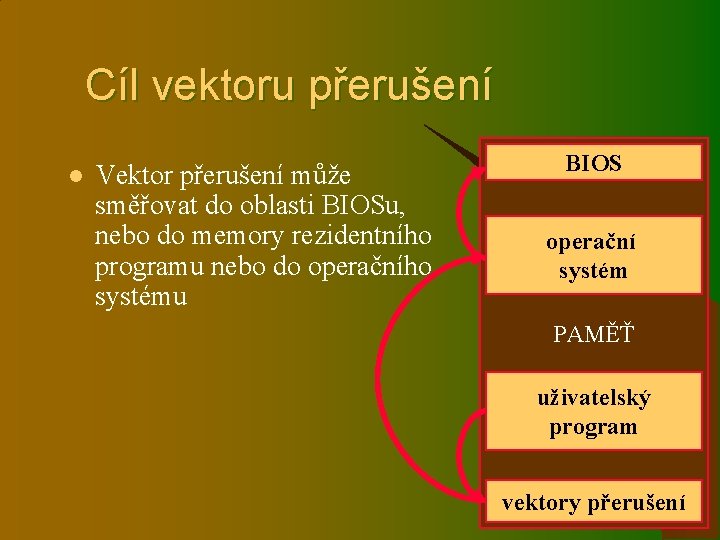

Cíl vektoru přerušení l Vektor přerušení může směřovat do oblasti BIOSu, nebo do memory rezidentního programu nebo do operačního systému BIOS rezidentní operační program systém PAMĚŤ uživatelský program vektory přerušení

dotazy?