Indice Introduccin a los sistemas basados en microprocesador

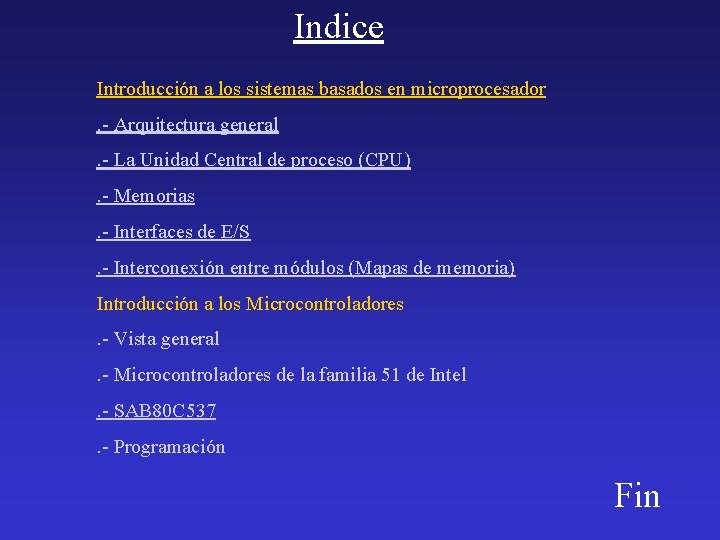

Indice Introducción a los sistemas basados en microprocesador. - Arquitectura general. - La Unidad Central de proceso (CPU). - Memorias. - Interfaces de E/S. - Interconexión entre módulos (Mapas de memoria) Introducción a los Microcontroladores. - Vista general. - Microcontroladores de la familia 51 de Intel. - SAB 80 C 537. - Programación Fin

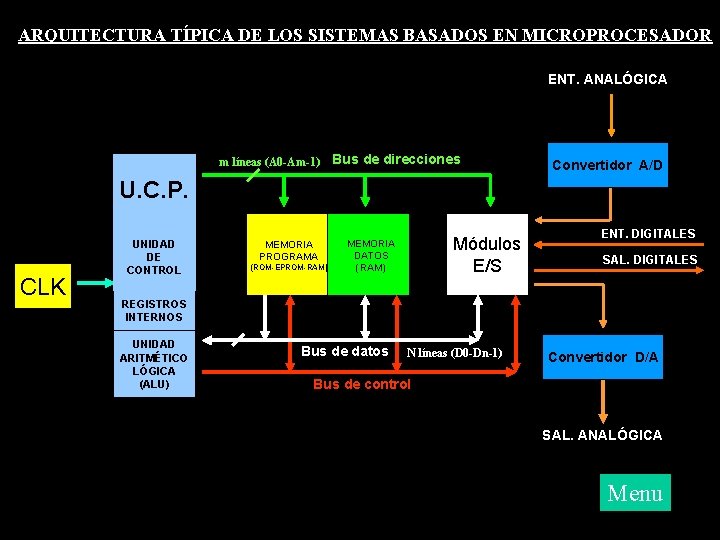

ARQUITECTURA TÍPICA DE LOS SISTEMAS BASADOS EN MICROPROCESADOR ENT. ANALÓGICA m líneas (A 0 -Am-1) Bus de direcciones Convertidor A/D U. C. P. CLK UNIDAD DE CONTROL MEMORIA PROGRAMA (ROM-EPROM-RAM) Módulos E/S MEMORIA DATOS (RAM) ENT. DIGITALES SAL. DIGITALES REGISTROS INTERNOS UNIDAD ARITMÉTICO LÓGICA (ALU) Bus de datos N líneas (D 0 -Dn-1) Convertidor D/A Bus de control SAL. ANALÓGICA Menu

LA UNIDAD CENTRAL DE PROCESO (C. P. U)

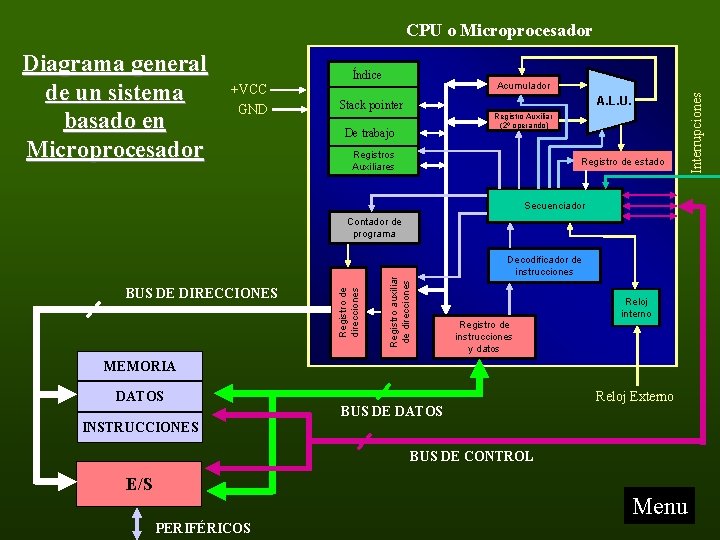

CPU o Microprocesador +VCC GND Índice Acumulador A. L. U. Stack pointer Registro Auxiliar (2º operando) De trabajo Registros Auxiliares Registro de estado Secuenciador Registro auxiliar de direcciones BUS DE DIRECCIONES Registro de direcciones Contador de programa Decodificador de instrucciones Reloj interno Registro de instrucciones y datos MEMORIA DATOS BUS DE DATOS Reloj Externo INSTRUCCIONES BUS DE CONTROL E/S Menu PERIFÉRICOS Interrupciones Diagrama general de un sistema basado en Microprocesador

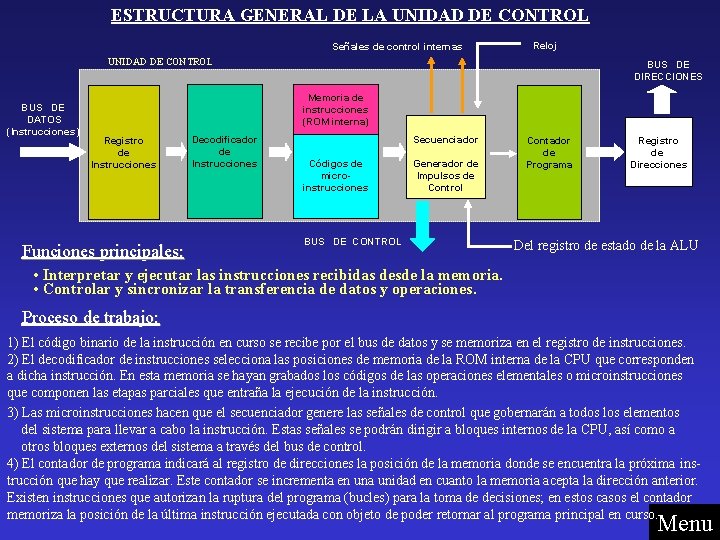

ESTRUCTURA GENERAL DE LA UNIDAD DE CONTROL Señales de control internas Reloj UNIDAD DE CONTROL BUS DE DATOS (Instrucciones) BUS DE DIRECCIONES Memoria de instrucciones (ROM interna) Registro de Instrucciones Funciones principales: Decodificador de Instrucciones Secuenciador Códigos de microinstrucciones Generador de Impulsos de Control BUS DE CONTROL Contador de Programa Registro de Direcciones Del registro de estado de la ALU • Interpretar y ejecutar las instrucciones recibidas desde la memoria. • Controlar y sincronizar la transferencia de datos y operaciones. Proceso de trabajo: 1) El código binario de la instrucción en curso se recibe por el bus de datos y se memoriza en el registro de instrucciones. 2) El decodificador de instrucciones selecciona las posiciones de memoria de la ROM interna de la CPU que corresponden a dicha instrucción. En esta memoria se hayan grabados los códigos de las operaciones elementales o microinstrucciones que componen las etapas parciales que entraña la ejecución de la instrucción. 3) Las microinstrucciones hacen que el secuenciador genere las señales de control que gobernarán a todos los elementos del sistema para llevar a cabo la instrucción. Estas señales se podrán dirigir a bloques internos de la CPU, así como a otros bloques externos del sistema a través del bus de control. 4) El contador de programa indicará al registro de direcciones la posición de la memoria donde se encuentra la próxima instrucción que hay que realizar. Este contador se incrementa en una unidad en cuanto la memoria acepta la dirección anterior. Existen instrucciones que autorizan la ruptura del programa (bucles) para la toma de decisiones; en estos casos el contador memoriza la posición de la última instrucción ejecutada con objeto de poder retornar al programa principal en curso. Menu

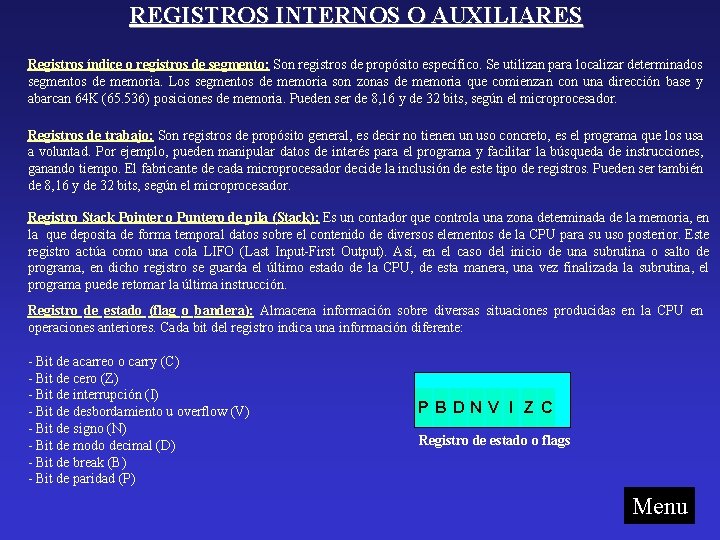

REGISTROS INTERNOS O AUXILIARES Registros índice o registros de segmento: Son registros de propósito específico. Se utilizan para localizar determinados segmentos de memoria. Los segmentos de memoria son zonas de memoria que comienzan con una dirección base y abarcan 64 K (65. 536) posiciones de memoria. Pueden ser de 8, 16 y de 32 bits, según el microprocesador. Registros de trabajo: Son registros de propósito general, es decir no tienen un uso concreto, es el programa que los usa a voluntad. Por ejemplo, pueden manipular datos de interés para el programa y facilitar la búsqueda de instrucciones, ganando tiempo. El fabricante de cada microprocesador decide la inclusión de este tipo de registros. Pueden ser también de 8, 16 y de 32 bits, según el microprocesador. Registro Stack Pointer o Puntero de pila (Stack): Es un contador que controla una zona determinada de la memoria, en la que deposita de forma temporal datos sobre el contenido de diversos elementos de la CPU para su uso posterior. Este registro actúa como una cola LIFO (Last Input-First Output). Así, en el caso del inicio de una subrutina o salto de programa, en dicho registro se guarda el último estado de la CPU, de esta manera, una vez finalizada la subrutina, el programa puede retomar la última instrucción. Registro de estado (flag o bandera): Almacena información sobre diversas situaciones producidas en la CPU en operaciones anteriores. Cada bit del registro indica una información diferente: - Bit de acarreo o carry (C) - Bit de cero (Z) - Bit de interrupción (I) - Bit de desbordamiento u overflow (V) - Bit de signo (N) - Bit de modo decimal (D) - Bit de break (B) - Bit de paridad (P) P BDN V I Z C Registro de estado o flags Menu

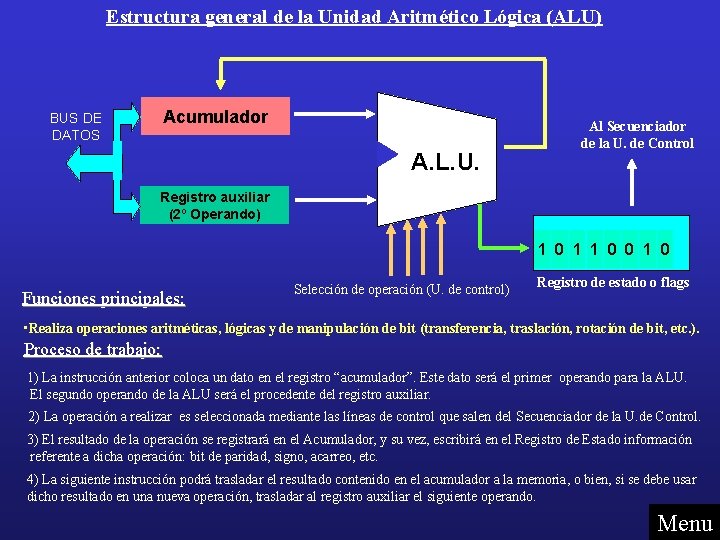

Estructura general de la Unidad Aritmético Lógica (ALU) Acumulador BUS DE DATOS A. L. U. Al Secuenciador de la U. de Control Registro auxiliar (2º Operando) 1 0 1 1 0 0 1 0 Funciones principales: Selección de operación (U. de control) Registro de estado o flags • Realiza operaciones aritméticas, lógicas y de manipulación de bit (transferencia, traslación, rotación de bit, etc. ). Proceso de trabajo: 1) La instrucción anterior coloca un dato en el registro “acumulador”. Este dato será el primer operando para la ALU. El segundo operando de la ALU será el procedente del registro auxiliar. 2) La operación a realizar es seleccionada mediante las líneas de control que salen del Secuenciador de la U. de Control. 3) El resultado de la operación se registrará en el Acumulador, y su vez, escribirá en el Registro de Estado información referente a dicha operación: bit de paridad, signo, acarreo, etc. 4) La siguiente instrucción podrá trasladar el resultado contenido en el acumulador a la memoria, o bien, si se debe usar dicho resultado en una nueva operación, trasladar al registro auxiliar el siguiente operando. Menu

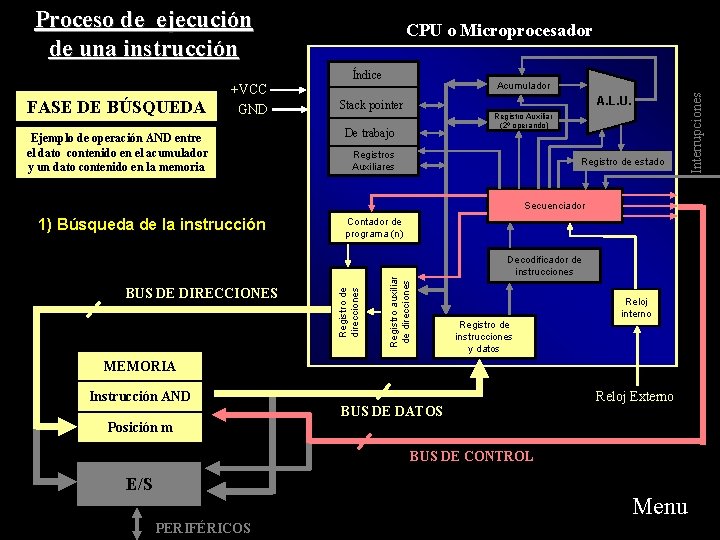

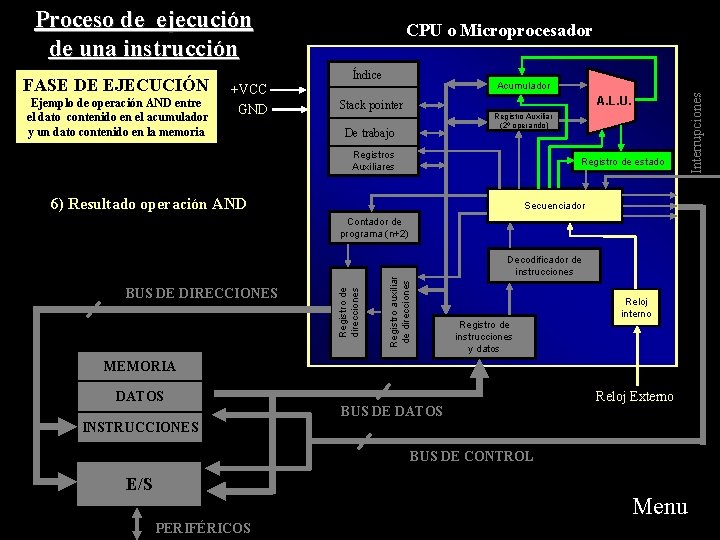

Proceso de ejecución de una instrucción Ejemplo de operación AND entre el dato contenido en el acumulador y un dato contenido en la memoria Índice Acumulador A. L. U. Stack pointer Registro Auxiliar (2º operando) De trabajo Registros Auxiliares Registro de estado Secuenciador Registro auxiliar de direcciones BUS DE DIRECCIONES Contador de programa (n) Registro de direcciones 1) Búsqueda de la instrucción Decodificador de instrucciones Reloj interno Registro de instrucciones y datos MEMORIA Instrucción AND BUS DE DATOS Reloj Externo Posición m BUS DE CONTROL E/S Menu PERIFÉRICOS Interrupciones FASE DE BÚSQUEDA +VCC GND CPU o Microprocesador

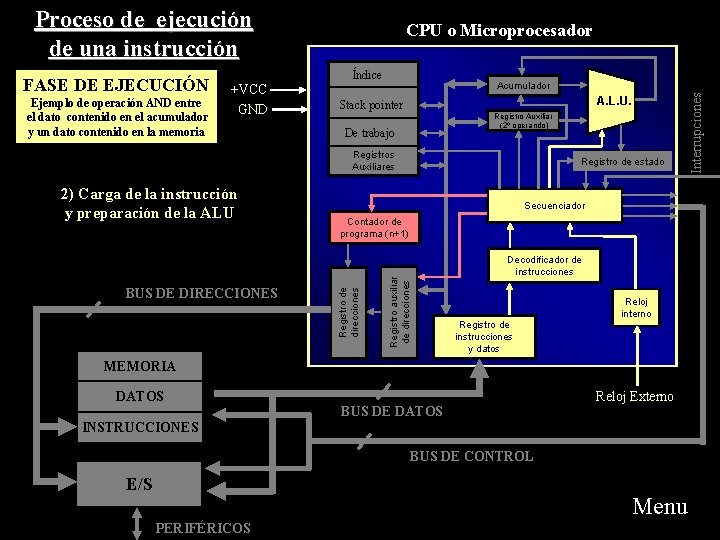

Proceso de ejecución de una instrucción Ejemplo de operación AND entre el dato contenido en el acumulador y un dato contenido en la memoria +VCC GND Índice Acumulador A. L. U. Stack pointer Registro Auxiliar (2º operando) De trabajo Registros Auxiliares Contador de programa (n+1) Registro auxiliar de direcciones BUS DE DIRECCIONES Secuenciador Registro de direcciones 2) Carga de la instrucción y preparación de la ALU Registro de estado Decodificador de instrucciones Reloj interno Registro de instrucciones y datos MEMORIA DATOS BUS DE DATOS Reloj Externo INSTRUCCIONES BUS DE CONTROL E/S Menu PERIFÉRICOS Interrupciones FASE DE EJECUCIÓN CPU o Microprocesador

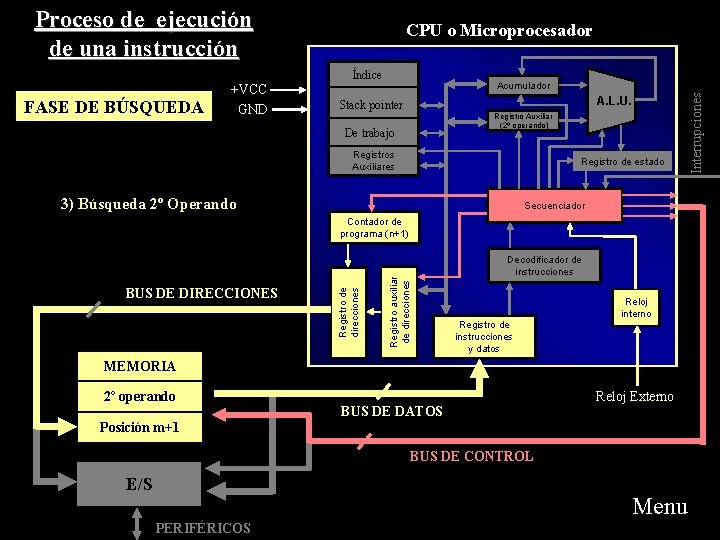

Proceso de ejecución de una instrucción Índice Acumulador A. L. U. Stack pointer Registro Auxiliar (2º operando) De trabajo Registros Auxiliares Registro de estado 3) Búsqueda 2º Operando Secuenciador Registro auxiliar de direcciones BUS DE DIRECCIONES Registro de direcciones Contador de programa (n+1) Decodificador de instrucciones Reloj interno Registro de instrucciones y datos MEMORIA 2º operando BUS DE DATOS Reloj Externo Posición m+1 BUS DE CONTROL E/S Menu PERIFÉRICOS Interrupciones FASE DE BÚSQUEDA +VCC GND CPU o Microprocesador

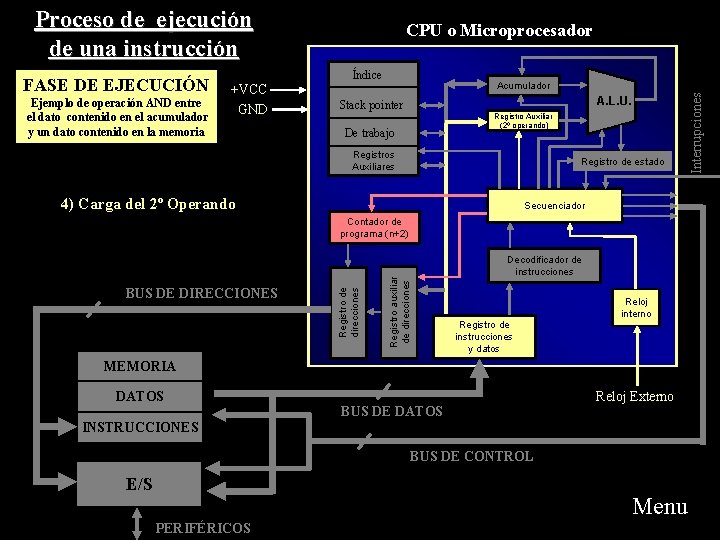

Proceso de ejecución de una instrucción Ejemplo de operación AND entre el dato contenido en el acumulador y un dato contenido en la memoria +VCC GND Índice Acumulador A. L. U. Stack pointer Registro Auxiliar (2º operando) De trabajo Registros Auxiliares Registro de estado 4) Carga del 2º Operando Secuenciador Registro auxiliar de direcciones BUS DE DIRECCIONES Registro de direcciones Contador de programa (n+2) Decodificador de instrucciones Reloj interno Registro de instrucciones y datos MEMORIA DATOS BUS DE DATOS Reloj Externo INSTRUCCIONES BUS DE CONTROL E/S Menu PERIFÉRICOS Interrupciones FASE DE EJECUCIÓN CPU o Microprocesador

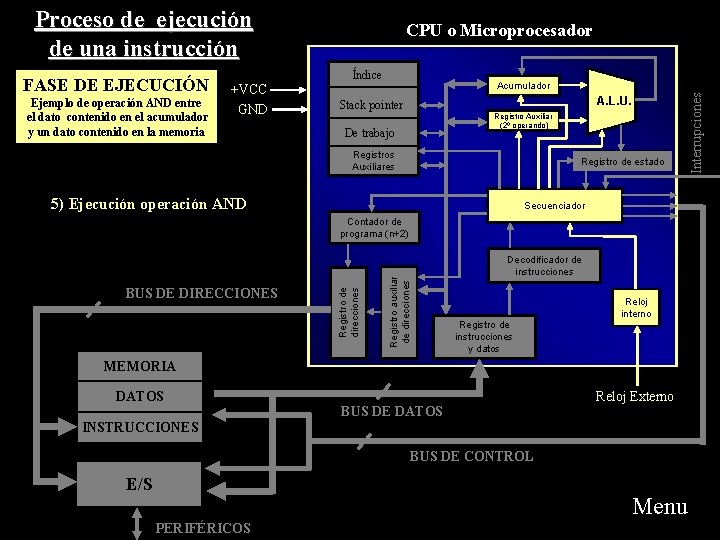

Proceso de ejecución de una instrucción Ejemplo de operación AND entre el dato contenido en el acumulador y un dato contenido en la memoria +VCC GND Índice Acumulador A. L. U. Stack pointer Registro Auxiliar (2º operando) De trabajo Registros Auxiliares Registro de estado 5) Ejecución operación AND Secuenciador Registro auxiliar de direcciones BUS DE DIRECCIONES Registro de direcciones Contador de programa (n+2) Decodificador de instrucciones Reloj interno Registro de instrucciones y datos MEMORIA DATOS BUS DE DATOS Reloj Externo INSTRUCCIONES BUS DE CONTROL E/S Menu PERIFÉRICOS Interrupciones FASE DE EJECUCIÓN CPU o Microprocesador

Proceso de ejecución de una instrucción Ejemplo de operación AND entre el dato contenido en el acumulador y un dato contenido en la memoria +VCC GND Índice Acumulador A. L. U. Stack pointer Registro Auxiliar (2º operando) De trabajo Registros Auxiliares Registro de estado 6) Resultado operación AND Secuenciador Registro auxiliar de direcciones BUS DE DIRECCIONES Registro de direcciones Contador de programa (n+2) Decodificador de instrucciones Reloj interno Registro de instrucciones y datos MEMORIA DATOS BUS DE DATOS Reloj Externo INSTRUCCIONES BUS DE CONTROL E/S Menu PERIFÉRICOS Interrupciones FASE DE EJECUCIÓN CPU o Microprocesador

LA MEMORIA

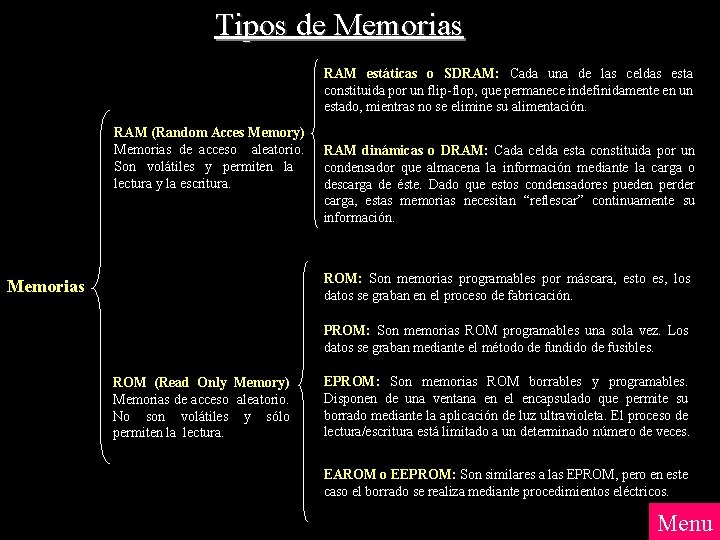

Tipos de Memorias RAM estáticas o SDRAM: Cada una de las celdas esta constituida por un flip-flop, que permanece indefinidamente en un estado, mientras no se elimine su alimentación. RAM (Random Acces Memory) Memorias de acceso aleatorio. Son volátiles y permiten la lectura y la escritura. RAM dinámicas o DRAM: Cada celda esta constituida por un condensador que almacena la información mediante la carga o descarga de éste. Dado que estos condensadores pueden perder carga, estas memorias necesitan “reflescar” continuamente su información. ROM: Son memorias programables por máscara, esto es, los datos se graban en el proceso de fabricación. Memorias PROM: Son memorias ROM programables una sola vez. Los datos se graban mediante el método de fundido de fusibles. ROM (Read Only Memory) Memorias de acceso aleatorio. No son volátiles y sólo permiten la lectura. EPROM: Son memorias ROM borrables y programables. Disponen de una ventana en el encapsulado que permite su borrado mediante la aplicación de luz ultravioleta. El proceso de lectura/escritura está limitado a un determinado número de veces. EAROM o EEPROM: Son similares a las EPROM, pero en este caso el borrado se realiza mediante procedimientos eléctricos. Menu

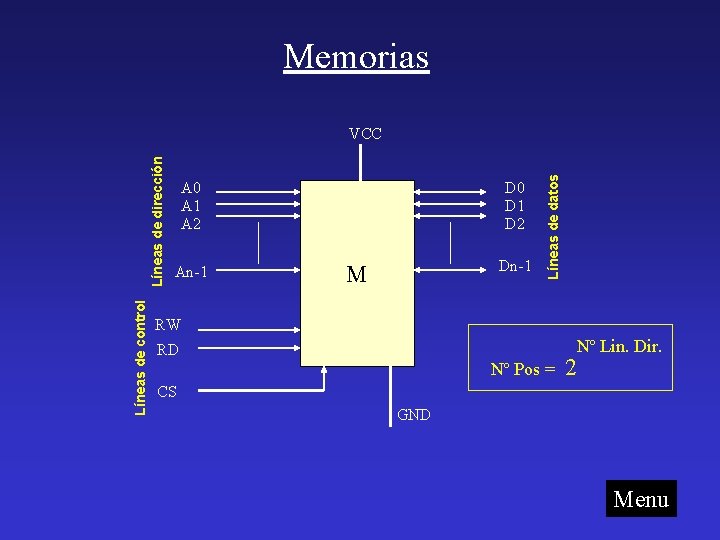

Memorias Líneas de control A 0 A 1 A 2 An-1 D 0 D 1 D 2 Dn-1 M Líneas de datos Líneas de dirección VCC RW RD Nº Pos = 2 Nº Lin. Dir. CS GND Menu

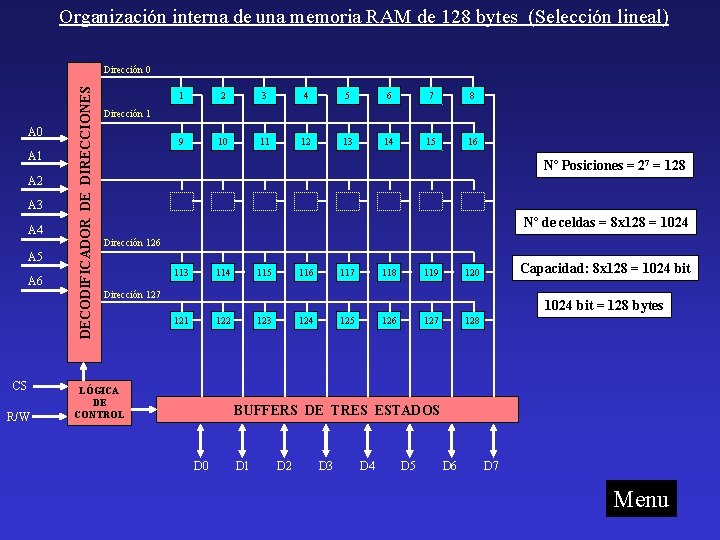

Organización interna de una memoria RAM de 128 bytes (Selección lineal) A 0 A 1 A 2 A 3 A 4 A 5 A 6 CS R/W DECODIFICADOR DE DIRECCIONES Dirección 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Dirección 1 Nº Posiciones = 27 = 128 Nº de celdas = 8 x 128 = 1024 Dirección 126 113 114 115 116 117 118 119 Capacidad: 8 x 128 = 1024 bit 120 Dirección 127 1024 bit = 128 bytes 121 122 LÓGICA DE CONTROL 123 124 125 126 127 128 BUFFERS DE TRES ESTADOS D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Menu

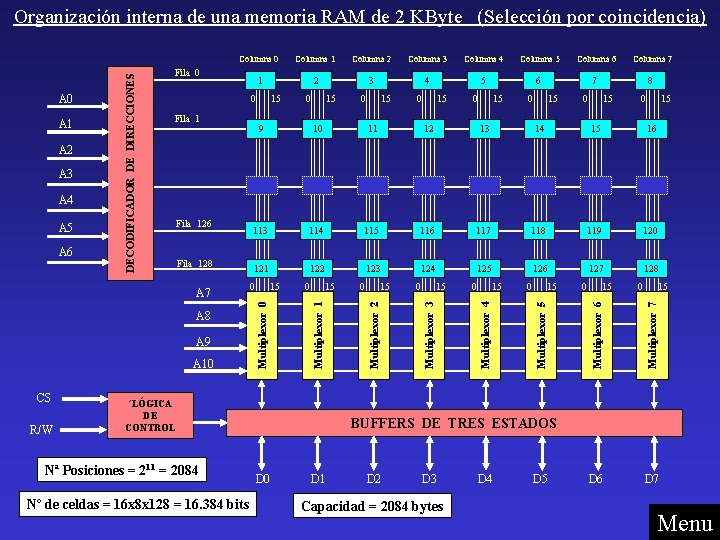

Columna 6 Columna 7 1 2 3 4 5 6 7 8 Fila 0 0 Fila 128 A 7 A 8 A 9 A 10 CS R/W 0 15 Nº de celdas = 16 x 8 x 128 = 16. 384 bits 15 0 15 0 15 9 10 11 12 13 14 15 16 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 0 15 ´LÓGICA DE CONTROL Nª Posiciones = 211 = 2084 0 0 15 0 15 Multiplexor 7 Fila 126 15 Multiplexor 6 A 6 Columna 5 Multiplexor 5 A 5 Columna 4 Multiplexor 4 A 4 Columna 3 Multiplexor 3 A 3 Columna 2 Multiplexor 2 A 2 Columna 1 Multiplexor 1 A 1 Columna 0 Multiplexor 0 A 0 DECODIFICADOR DE DIRECCIONES Organización interna de una memoria RAM de 2 KByte (Selección por coincidencia) D 6 D 7 BUFFERS DE TRES ESTADOS D 0 D 1 D 2 D 3 Capacidad = 2084 bytes D 4 D 5 Menu

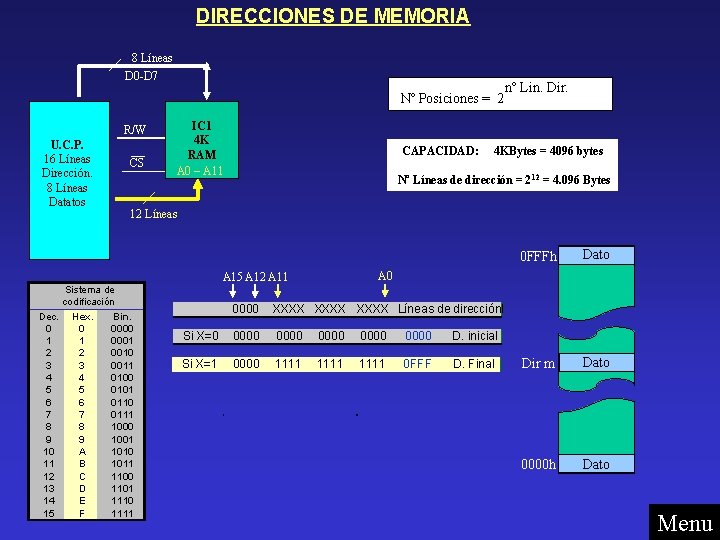

DIRECCIONES DE MEMORIA 8 Líneas D 0 -D 7 Nº Posiciones = 2 R/W U. C. P. 16 Líneas Dirección. 8 Líneas Datatos CS IC 1 4 K RAM A 0 – A 11 CAPACIDAD: 4 KBytes = 4096 bytes Nº Líneas de dirección = 212 = 4. 096 Bytes 12 Líneas Sistema de codificación Hex. Bin. 0 0000 1 0001 2 0010 3 0011 4 0100 5 0101 6 0110 7 0111 8 1000 9 1001 A 1010 B 1011 C 1100 D 1101 E 1110 F 1111 0 FFFh Dato Dir m Dato 0000 h Dato A 0 A 15 A 12 A 11 Dec. 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 nº Lin. Dir. 0000 XXXX Líneas de direcciónl Si X=0 0000 0000 D. inicial Si X=1 0000 1111 0 FFF D. Final Menu

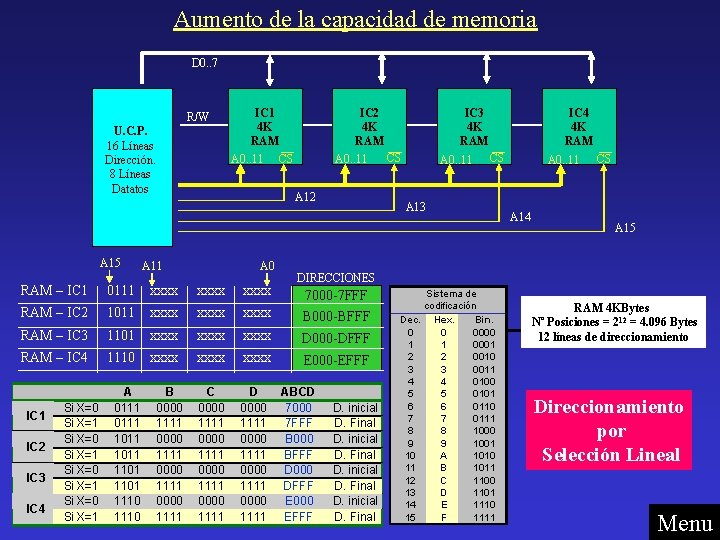

Aumento de la capacidad de memoria D 0. . 7 R/W U. C. P. 16 Líneas Dirección. 8 Líneas Datatos A 15 IC 1 4 K RAM A 0. . 11 CS IC 2 4 K RAM CS A 0. . 11 A 12 A 11 A 0 xxxx RAM – IC 2 1011 xxxx 7000 -7 FFF B 000 -BFFF RAM – IC 3 1101 xxxx D 000 -DFFF RAM – IC 4 1110 xxxx E 000 -EFFF C 0000 1111 D 0000 1111 IC 1 IC 2 IC 3 IC 4 Si X=0 Si X=1 CS A 0. . 11 A 14 CS A 15 DIRECCIONES 0111 B 0000 1111 A 0. . 11 IC 4 4 K RAM A 13 RAM – IC 1 A 0111 1011 1101 1110 IC 3 4 K RAM ABCD 7000 7 FFF B 000 BFFF D 000 DFFF E 000 EFFF D. inicial D. Final Dec. 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Sistema de codificación Hex. Bin. 0 0000 1 0001 2 0010 3 0011 4 0100 5 0101 6 0110 7 0111 8 1000 9 1001 A 1010 B 1011 C 1100 D 1101 E 1110 F 1111 RAM 4 KBytes Nº Posiciones = 212 = 4. 096 Bytes 12 líneas de direccionamiento Direccionamiento por Selección Lineal Menu

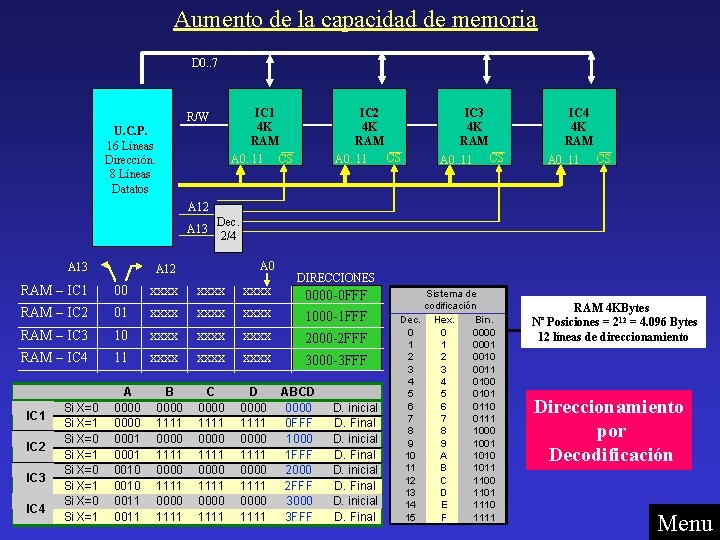

Aumento de la capacidad de memoria D 0. . 7 IC 1 4 K RAM A 0. . 11 CS R/W U. C. P. 16 Líneas Dirección. 8 Líneas Datatos IC 2 4 K RAM CS A 0. . 11 IC 3 4 K RAM A 0. . 11 IC 4 4 K RAM CS A 0. . 11 CS A 12 A 13 Dec. 2/4 A 0 A 12 DIRECCIONES RAM – IC 1 00 xxxx RAM – IC 2 01 xxxx 0000 -0 FFF 1000 -1 FFF RAM – IC 3 10 xxxx 2000 -2 FFF RAM – IC 4 11 xxxx 3000 -3 FFF C 0000 1111 D 0000 1111 IC 1 IC 2 IC 3 IC 4 Si X=0 Si X=1 A 0000 0001 0010 0011 B 0000 1111 ABCD 0000 0 FFF 1000 1 FFF 2000 2 FFF 3000 3 FFF D. inicial D. Final Dec. 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Sistema de codificación Hex. Bin. 0 0000 1 0001 2 0010 3 0011 4 0100 5 0101 6 0110 7 0111 8 1000 9 1001 A 1010 B 1011 C 1100 D 1101 E 1110 F 1111 RAM 4 KBytes Nº Posiciones = 212 = 4. 096 Bytes 12 líneas de direccionamiento Direccionamiento por Decodificación Menu

Unidades de E/S (interfaces o puertos de E/S)

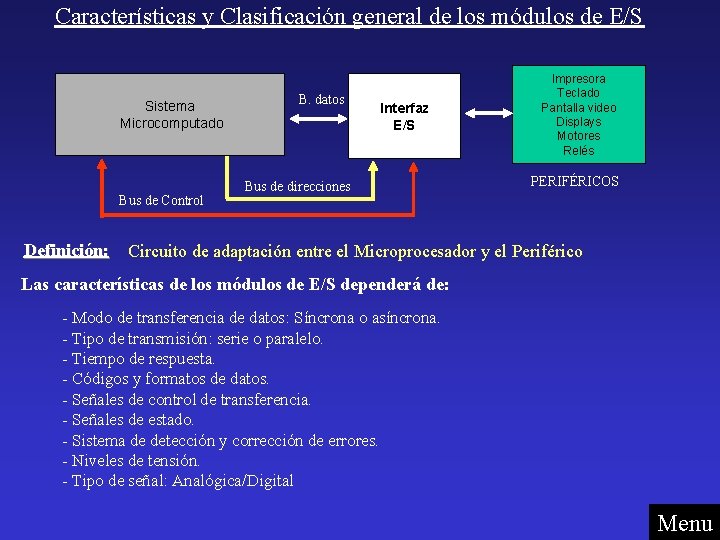

Características y Clasificación general de los módulos de E/S Sistema Microcomputado Bus de Control Definición: B. datos Interfaz E/S Bus de direcciones Impresora Teclado Pantalla video Displays Motores Relés PERIFÉRICOS Circuito de adaptación entre el Microprocesador y el Periférico Las características de los módulos de E/S dependerá de: - Modo de transferencia de datos: Síncrona o asíncrona. - Tipo de transmisión: serie o paralelo. - Tiempo de respuesta. - Códigos y formatos de datos. - Señales de control de transferencia. - Señales de estado. - Sistema de detección y corrección de errores. - Niveles de tensión. - Tipo de señal: Analógica/Digital Menu

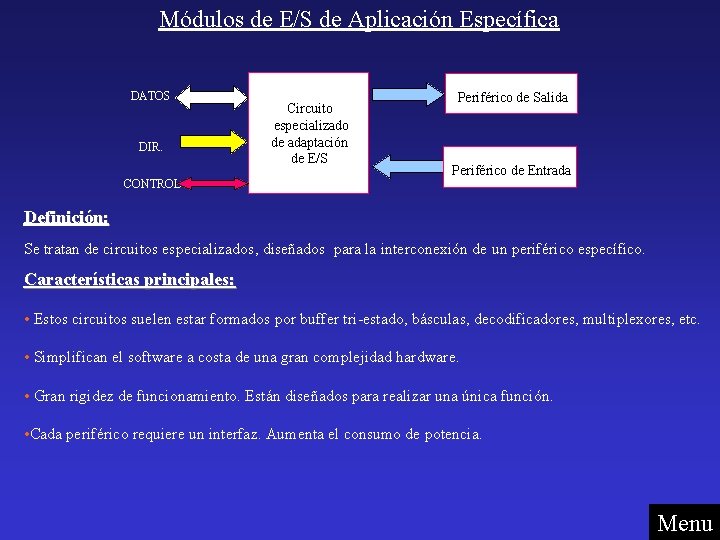

Módulos de E/S de Aplicación Específica DATOS DIR. CONTROL Circuito especializado de adaptación de E/S Periférico de Salida Periférico de Entrada Definición: Se tratan de circuitos especializados, diseñados para la interconexión de un periférico específico. Características principales: • Estos circuitos suelen estar formados por buffer tri-estado, básculas, decodificadores, multiplexores, etc. • Simplifican el software a costa de una gran complejidad hardware. • Gran rigidez de funcionamiento. Están diseñados para realizar una única función. • Cada periférico requiere un interfaz. Aumenta el consumo de potencia. Menu

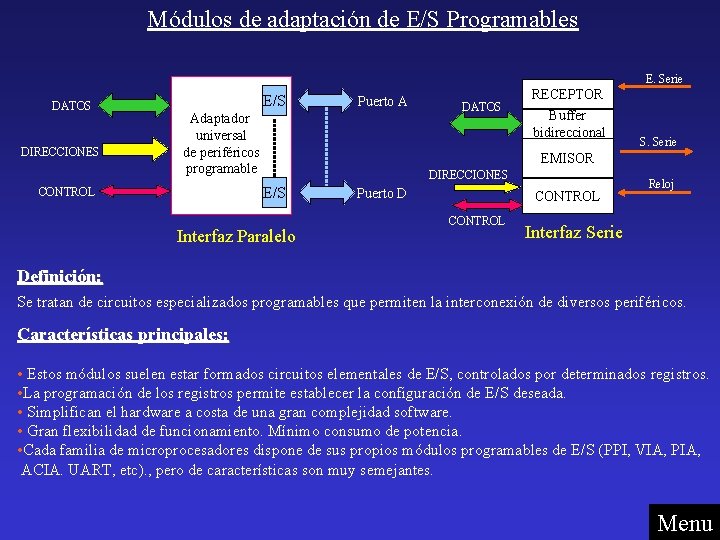

Módulos de adaptación de E/S Programables E. Serie DATOS DIRECCIONES E/S Puerto A Adaptador universal de periféricos programable RECEPTOR Buffer bidireccional S. Serie EMISOR DIRECCIONES E/S CONTROL DATOS Interfaz Paralelo Puerto D CONTROL Reloj Interfaz Serie Definición: Se tratan de circuitos especializados programables que permiten la interconexión de diversos periféricos. Características principales: • Estos módulos suelen estar formados circuitos elementales de E/S, controlados por determinados registros. • La programación de los registros permite establecer la configuración de E/S deseada. • Simplifican el hardware a costa de una gran complejidad software. • Gran flexibilidad de funcionamiento. Mínimo consumo de potencia. • Cada familia de microprocesadores dispone de sus propios módulos programables de E/S (PPI, VIA, PIA, ACIA. UART, etc). , pero de características son muy semejantes. Menu

Interconexión de módulos a la CPU

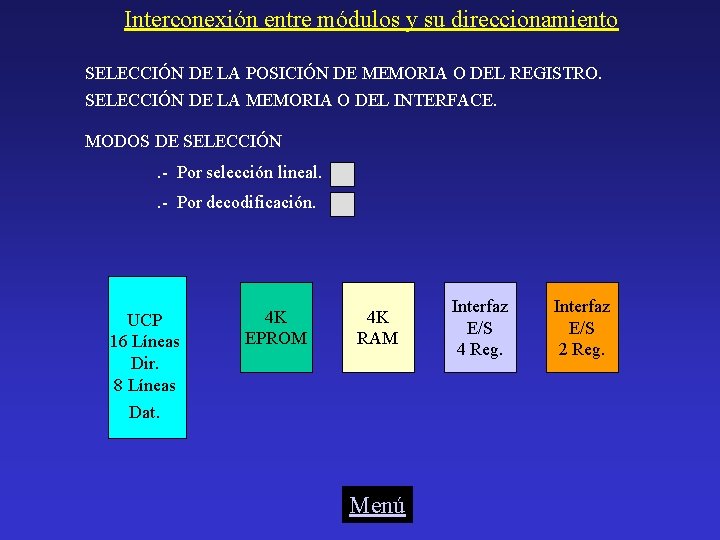

Interconexión entre módulos y su direccionamiento SELECCIÓN DE LA POSICIÓN DE MEMORIA O DEL REGISTRO. SELECCIÓN DE LA MEMORIA O DEL INTERFACE. MODOS DE SELECCIÓN. - Por selección lineal. . - Por decodificación. UCP 16 Líneas Dir. 8 Líneas 4 K EPROM 4 K RAM Dat. Menú Interfaz E/S 4 Reg. Interfaz E/S 2 Reg.

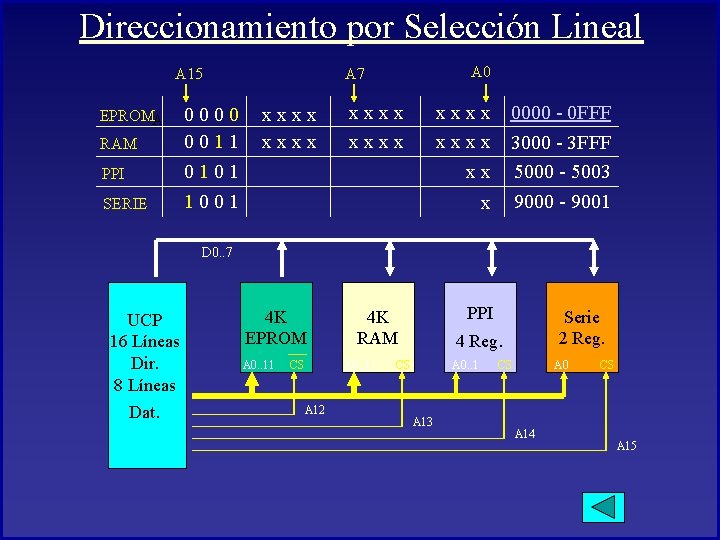

Direccionamiento por Selección Lineal A 15 EPROMA RAM PPI SERIE 0000 0011 0101 1001 A 0 A 7 xxxx x x 0000 - 0 FFF x x 3000 - 3 FFF x x 5000 - 5003 x 9000 - 9001 D 0. . 7 UCP 16 Líneas Dir. 8 Líneas Dat. 4 K EPROM A 0. . 11 CS A 0. . 11 A 12 PPI 4 K RAM Serie 2 Reg. 4 Reg. CS A 0. . 1 A 13 CS A 0 A 14 CS A 15

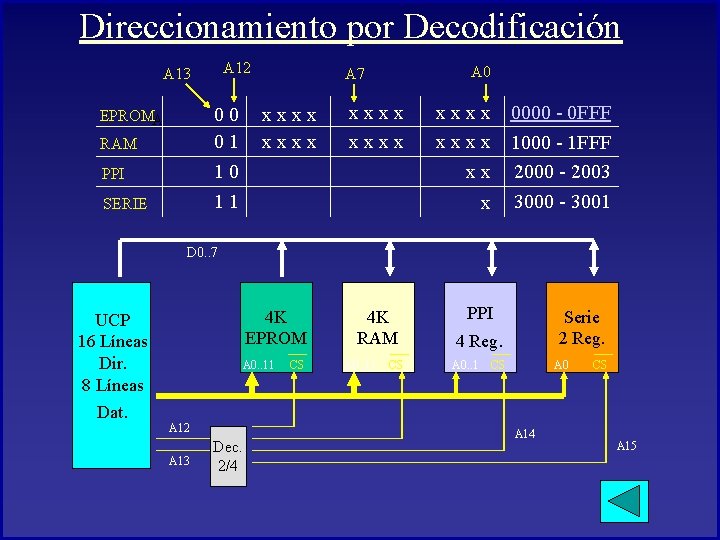

Direccionamiento por Decodificación A 12 A 13 00 01 10 11 EPROMA RAM PPI SERIE A 0 A 7 xxxx x x 0000 - 0 FFF x x 1000 - 1 FFF x x 2000 - 2003 x 3000 - 3001 D 0. . 7 4 K EPROM UCP 16 Líneas Dir. 8 Líneas Dat. A 0. . 11 A 12 A 13 Dec. 2/4 CS 4 K RAM A 0. . 11 CS PPI Serie 2 Reg. 4 Reg. A 0. . 1 CS A 0 A 14 CS A 15

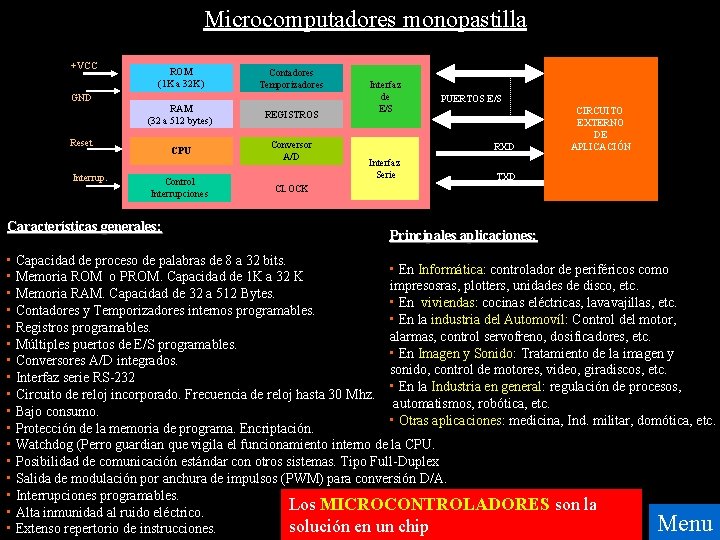

Microcomputadores monopastilla +VCC GND ROM (1 K a 32 K) RAM (32 a 512 bytes) REGISTROS CPU Conversor A/D Reset Interrup. Contadores Temporizadores Control Interrupciones Características generales: Interfaz de E/S PUERTOS E/S RXD Interfaz Serie CIRCUITO EXTERNO DE APLICACIÓN TXD CLOCK Principales aplicaciones: • Capacidad de proceso de palabras de 8 a 32 bits. • En Informática: controlador de periféricos como • Memoria ROM o PROM. Capacidad de 1 K a 32 K impresosras, plotters, unidades de disco, etc. • Memoria RAM. Capacidad de 32 a 512 Bytes. • En viviendas: cocinas eléctricas, lavavajillas, etc. • Contadores y Temporizadores internos programables. • En la industria del Automovíl: Control del motor, • Registros programables. alarmas, control servofreno, dosificadores, etc. • Múltiples puertos de E/S programables. • En Imagen y Sonido: Tratamiento de la imagen y • Conversores A/D integrados. sonido, control de motores, video, giradiscos, etc. • Interfaz serie RS-232 • En la Industria en general: regulación de procesos, • Circuito de reloj incorporado. Frecuencia de reloj hasta 30 Mhz. automatismos, robótica, etc. • Bajo consumo. • Otras aplicaciones: medicina, Ind. militar, domótica, etc. • Protección de la memoria de programa. Encriptación. • Watchdog (Perro guardian que vigila el funcionamiento interno de la CPU. • Posibilidad de comunicación estándar con otros sistemas. Tipo Full-Duplex • Salida de modulación por anchura de impulsos (PWM) para conversión D/A. • Interrupciones programables. Los MICROCONTROLADORES son la • Alta inmunidad al ruido eléctrico. solución en un chip • Extenso repertorio de instrucciones. Menu

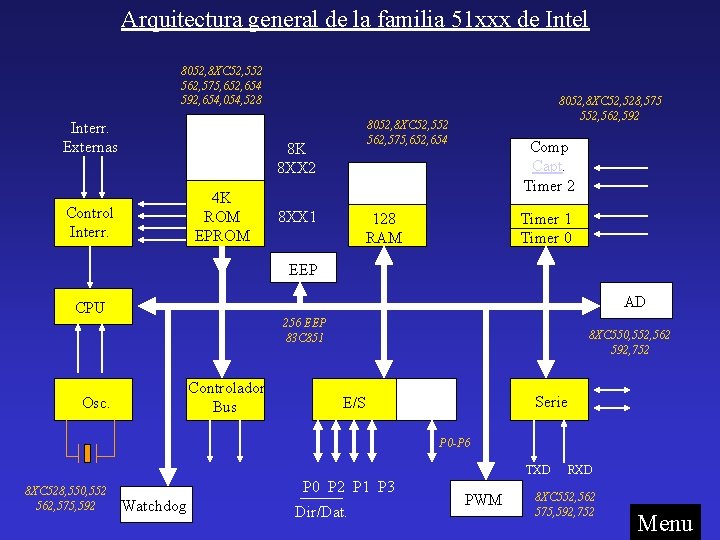

Arquitectura general de la familia 51 xxx de Intel 8052, 8 XC 52, 552 562, 575, 652, 654 592, 654, 054, 528 Interr. Externas 8052, 8 XC 52, 552 562, 575, 652, 654 8 K 8 XX 2 4 K ROM EPROM Control Interr. 8052, 8 XC 52, 528, 575 552, 562, 592 8 XX 1 Comp Capt. Timer 2 128 RAM Timer 1 Timer 0 EEP AD CPU 256 EEP 83 C 851 Controlador Bus Osc. 8 XC 550, 552, 562 592, 752 Serie E/S P 0 -P 6 TXD 8 XC 528, 550, 552 562, 575, 592 P 0 P 2 P 1 P 3 Watchdog Dir/Dat. PWM RXD 8 XC 552, 562 575, 592, 752 Menu

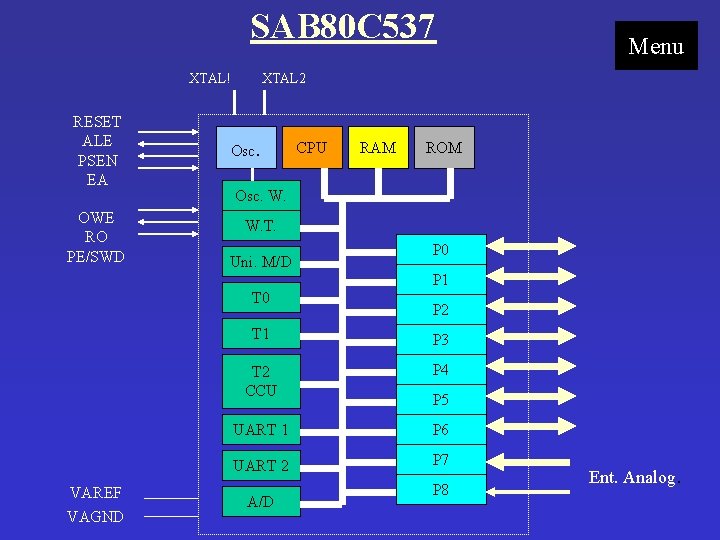

SAB 80 C 537 XTAL! RESET ALE PSEN EA OWE RO PE/SWD Menu XTAL 2 Osc. CPU RAM ROM Osc. W. W. T. Uni. M/D P 0 P 1 T 0 VAREF VAGND P 2 T 1 P 3 T 2 CCU P 4 UART 1 P 6 UART 2 P 7 A/D P 5 P 8 Ent. Analog.

Menu

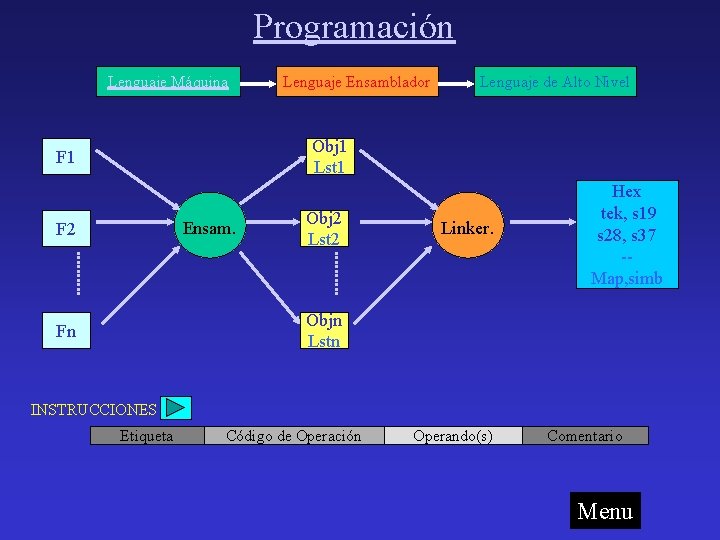

Programación Lenguaje Máquina Lenguaje Ensamblador Lenguaje de Alto Nivel Obj 1 Lst 1 F 1 Ensam. F 2 Obj 2 Lst 2 Linker. Hex tek, s 19 s 28, s 37 -Map, simb Objn Lstn Fn INSTRUCCIONES Etiqueta Código de Operación Operando(s) Comentario Menu

Menu

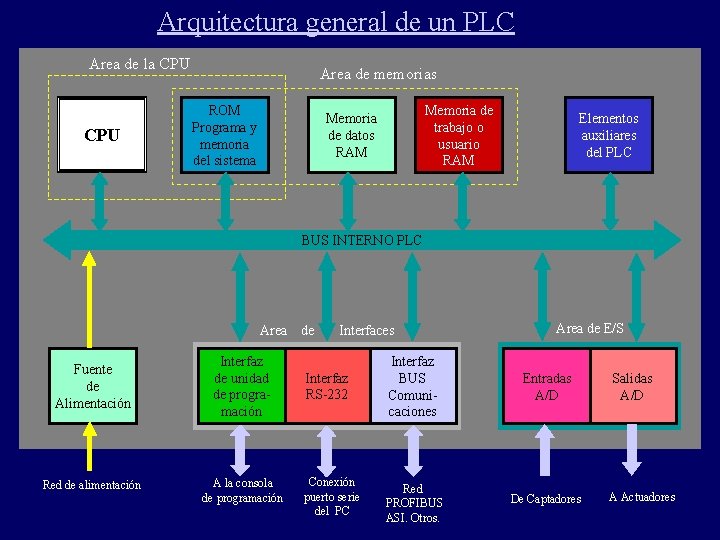

Arquitectura general de un PLC Area de la CPU Area de memorias ROM Programa y memoria del sistema Memoria de trabajo o usuario RAM Memoria de datos RAM Elementos auxiliares del PLC BUS INTERNO PLC Area Fuente de Alimentación Interfaz de unidad de programación Red de alimentación A la consola de programación de Interfaces Interfaz RS-232 Conexión puerto serie del PC Area de E/S Interfaz BUS Comunicaciones Entradas A/D Red PROFIBUS ASI. Otros. De Captadores Salidas A/D A Actuadores

- Slides: 39