Improvement of CT Slice Image Reconstruction Speed Using

- Slides: 14

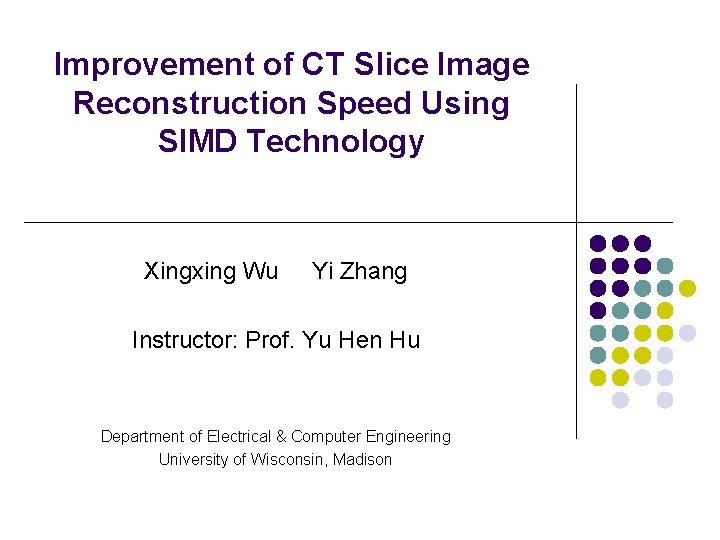

Improvement of CT Slice Image Reconstruction Speed Using SIMD Technology Xingxing Wu Yi Zhang Instructor: Prof. Yu Hen Hu Department of Electrical & Computer Engineering University of Wisconsin, Madison

Motivation l l l CT Slice Image Reconstruction is a very important part which will affect the reconstructed image quality and scanning speed CT Slice Image Reconstruction is very timeconsuming Traditional methods for speedup: l l l Specially designed hardware Parallel algorithm running on super computer Explore a new method: SIMD implementation

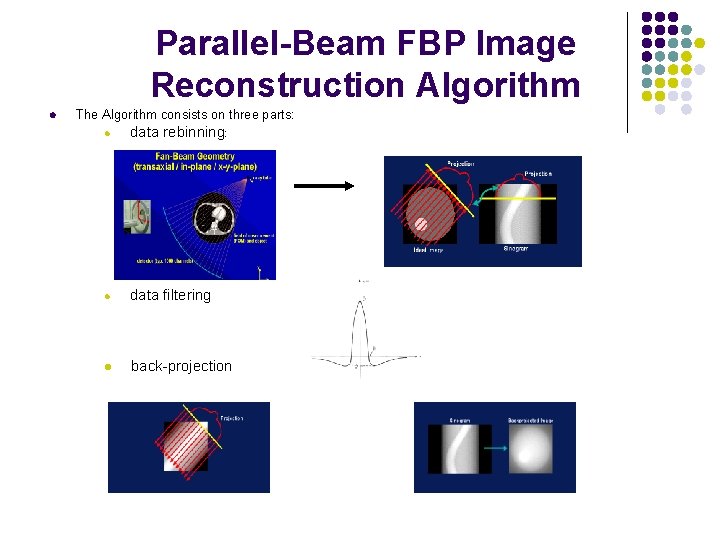

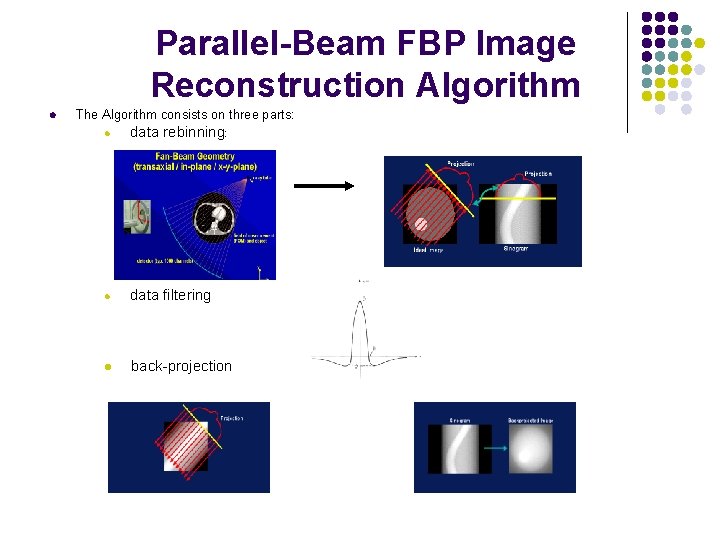

Parallel-Beam FBP Image Reconstruction Algorithm l The Algorithm consists on three parts: l data rebinning: l data filtering l back-projection

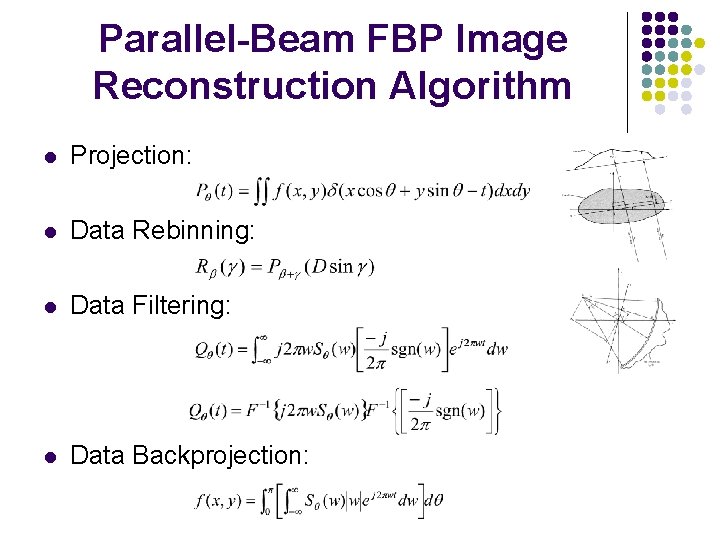

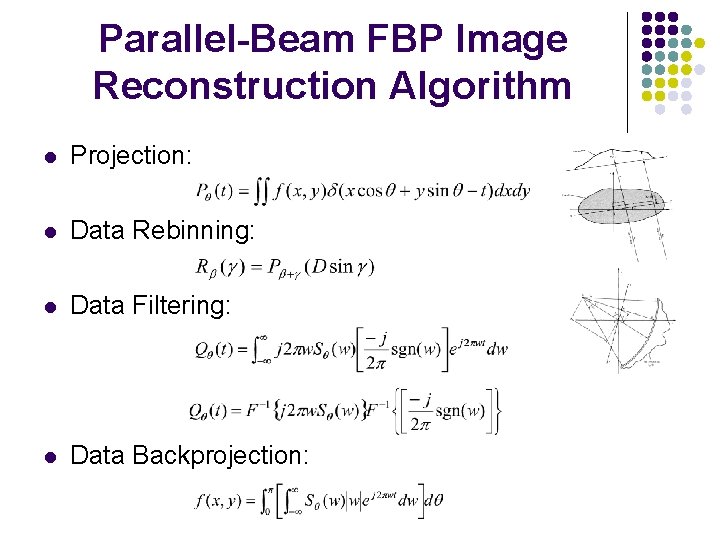

Parallel-Beam FBP Image Reconstruction Algorithm l Projection: l Data Rebinning: l Data Filtering: l Data Backprojection:

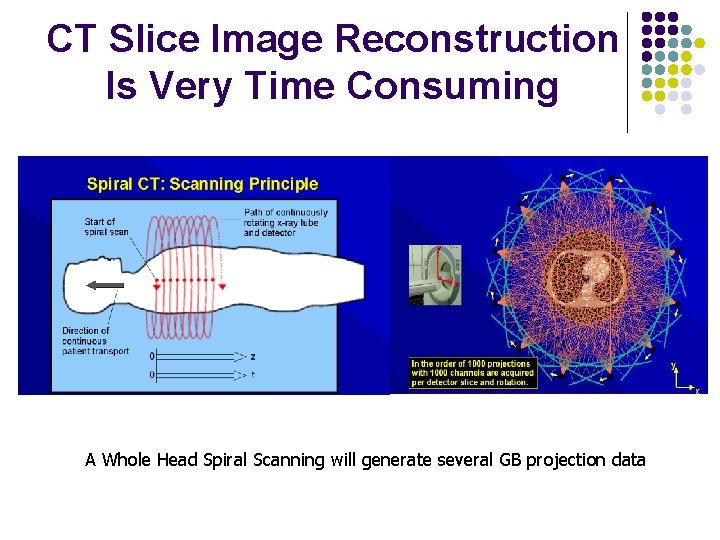

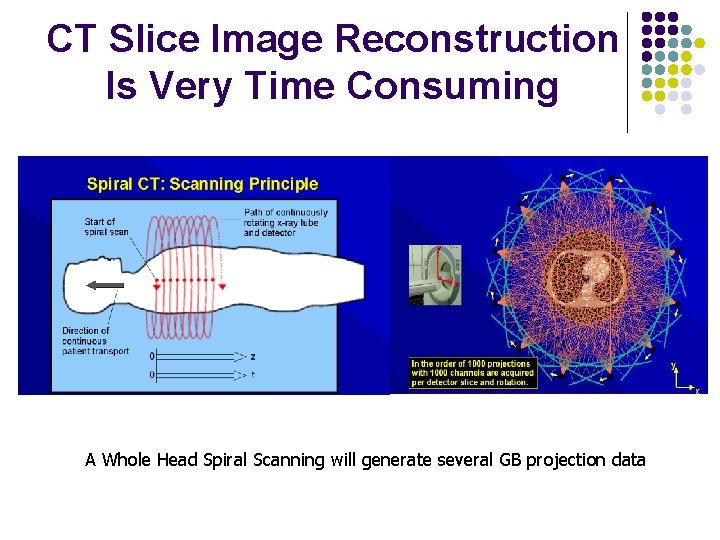

CT Slice Image Reconstruction Is Very Time Consuming A Whole Head Spiral Scanning will generate several GB projection data

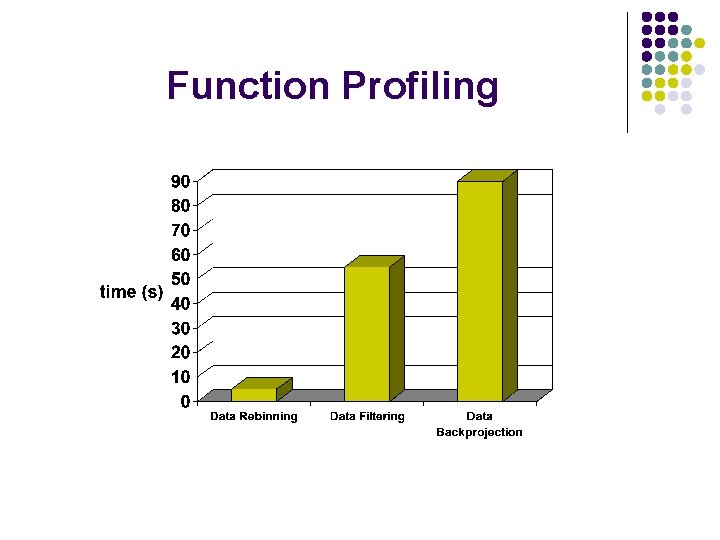

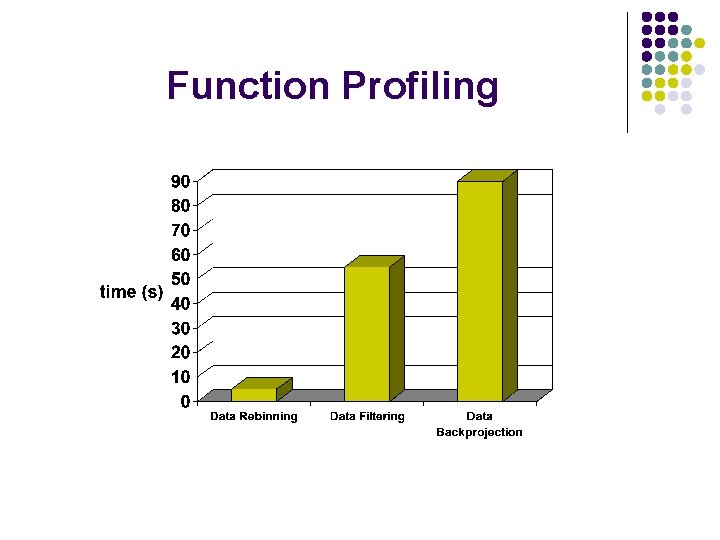

Function Profiling

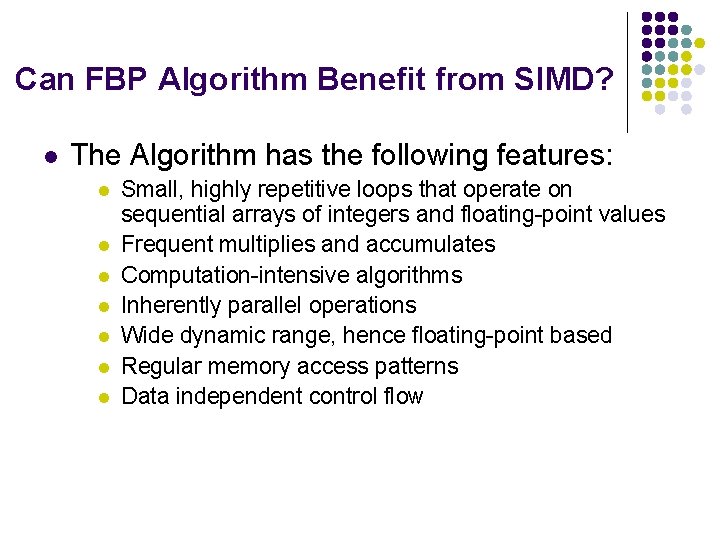

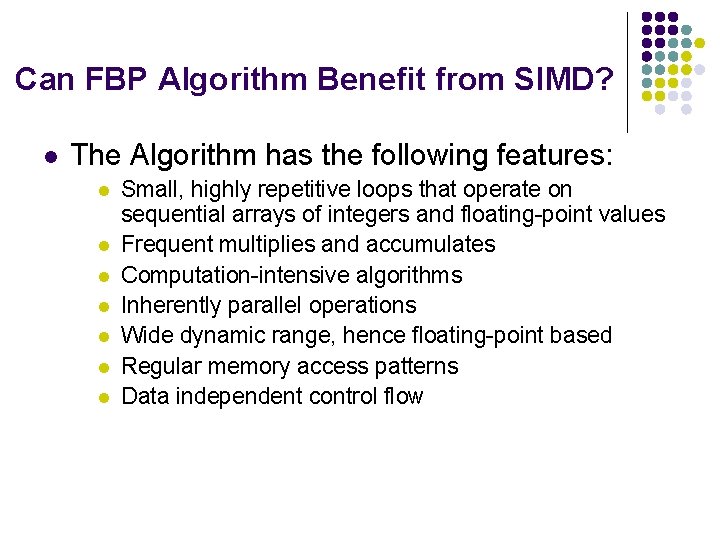

Can FBP Algorithm Benefit from SIMD? l The Algorithm has the following features: l l l l Small, highly repetitive loops that operate on sequential arrays of integers and floating-point values Frequent multiplies and accumulates Computation-intensive algorithms Inherently parallel operations Wide dynamic range, hence floating-point based Regular memory access patterns Data independent control flow

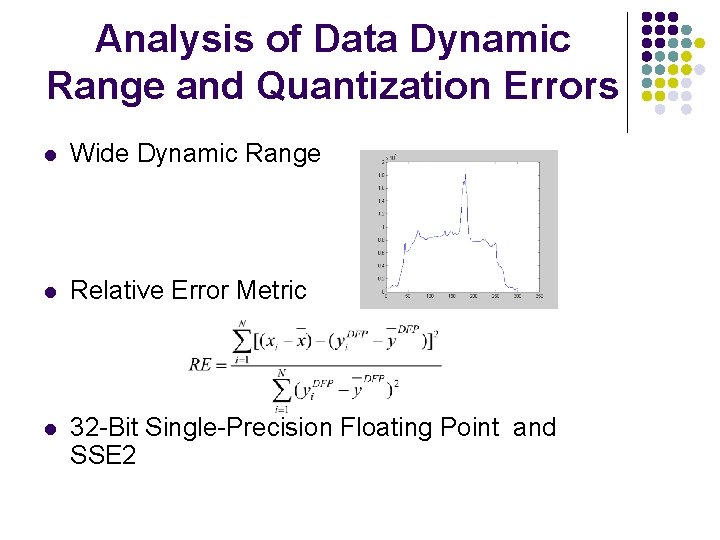

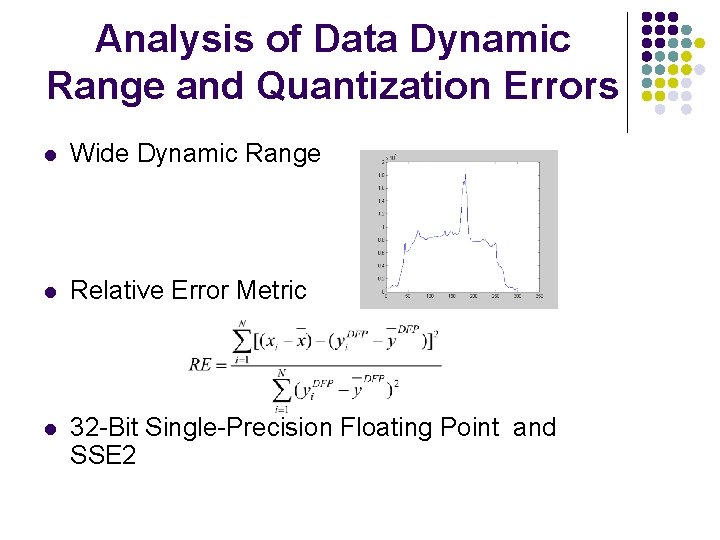

Analysis of Data Dynamic Range and Quantization Errors l Wide Dynamic Range l Relative Error Metric l 32 -Bit Single-Precision Floating Point and SSE 2

Updated Algorithm to Fit SIMD l Update the algorithm to eliminate some conditional branches l Reduce the on-the-fly calculations which are not suitable for the SIMD implementation

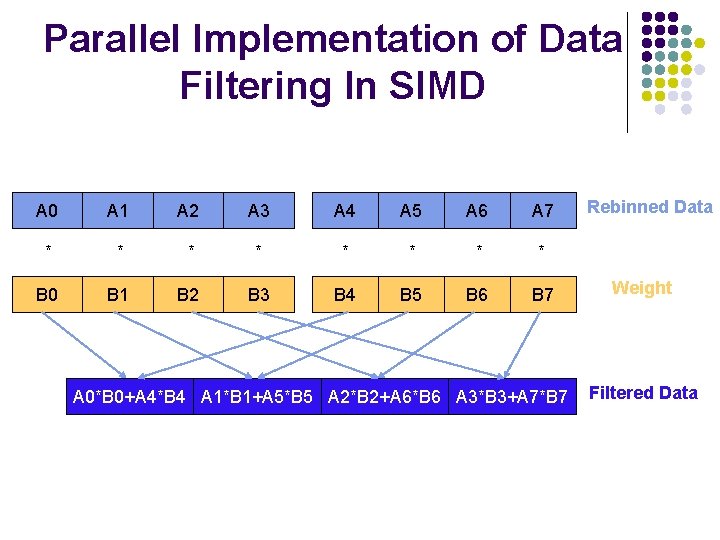

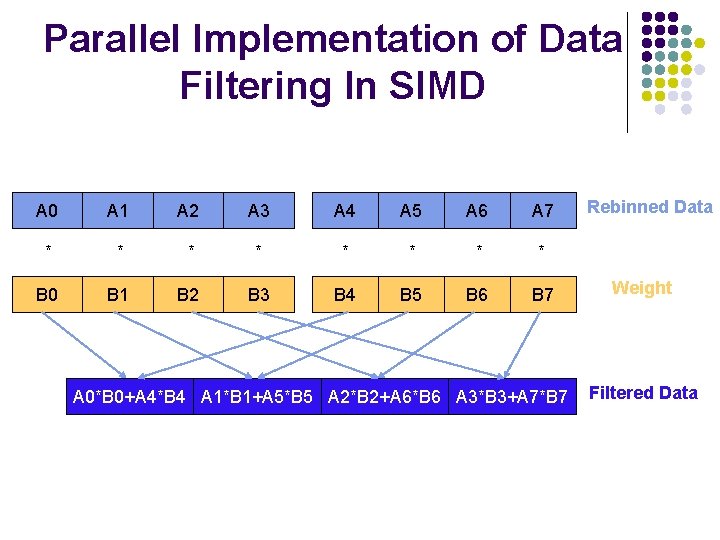

Parallel Implementation of Data Filtering In SIMD A 0 A 1 A 2 A 3 A 4 A 5 A 6 A 7 * * * * B 0 B 1 B 2 B 3 B 4 B 5 B 6 B 7 A 0*B 0+A 4*B 4 A 1*B 1+A 5*B 5 A 2*B 2+A 6*B 6 A 3*B 3+A 7*B 7 Rebinned Data Weight Filtered Data

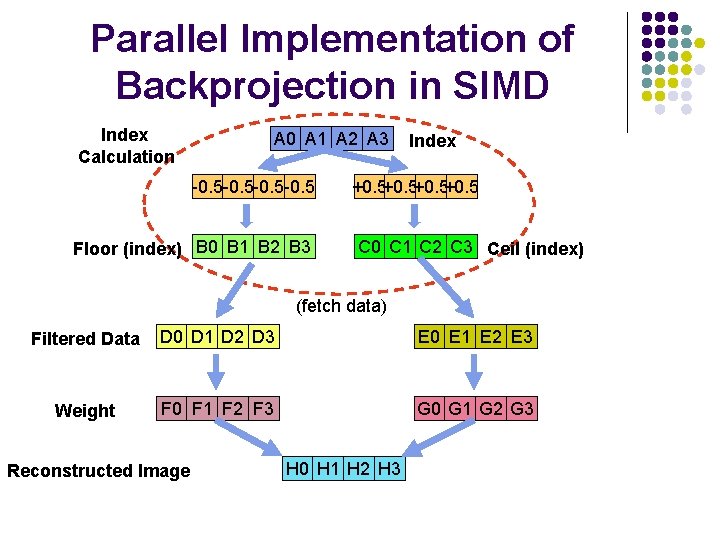

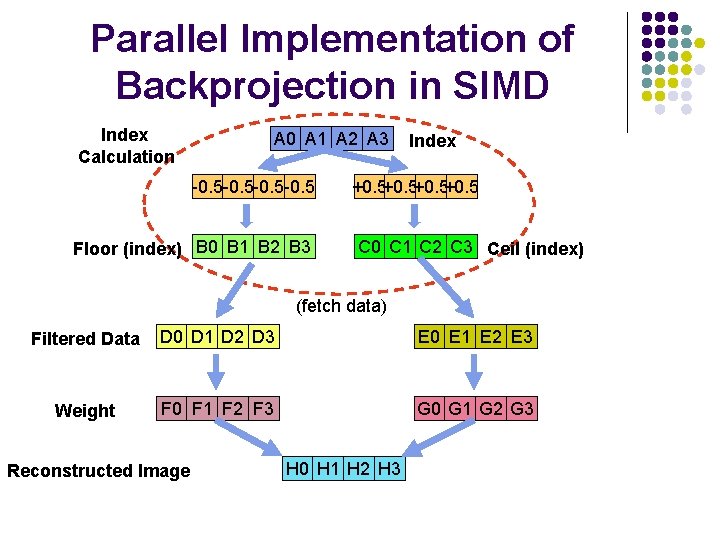

Parallel Implementation of Backprojection in SIMD Index Calculation A 0 A 1 A 2 A 3 -0. 5 -0. 5 Floor (index) B 0 B 1 B 2 B 3 Index +0. 5+0. 5 C 0 C 1 C 2 C 3 Ceil (index) (fetch data) Filtered Data D 0 D 1 D 2 D 3 E 0 E 1 E 2 E 3 Weight F 0 F 1 F 2 F 3 G 0 G 1 G 2 G 3 Reconstructed Image H 0 H 1 H 2 H 3

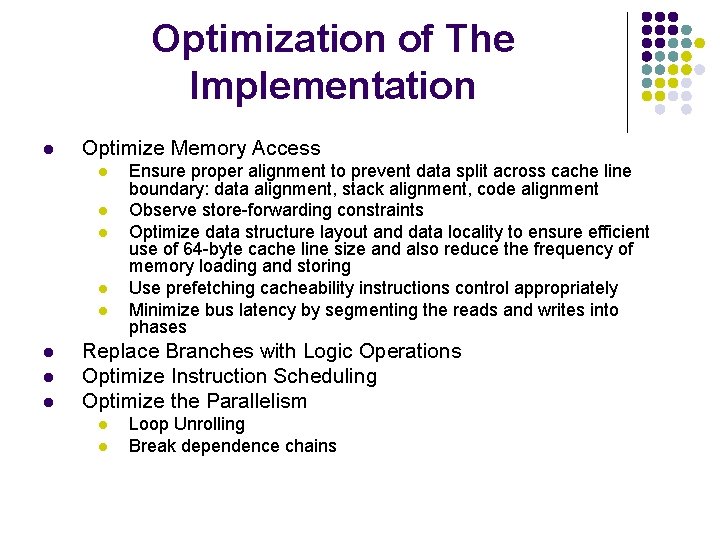

Optimization of The Implementation l Optimize Memory Access l l l l Ensure proper alignment to prevent data split across cache line boundary: data alignment, stack alignment, code alignment Observe store-forwarding constraints Optimize data structure layout and data locality to ensure efficient use of 64 -byte cache line size and also reduce the frequency of memory loading and storing Use prefetching cacheability instructions control appropriately Minimize bus latency by segmenting the reads and writes into phases Replace Branches with Logic Operations Optimize Instruction Scheduling Optimize the Parallelism l l Loop Unrolling Break dependence chains

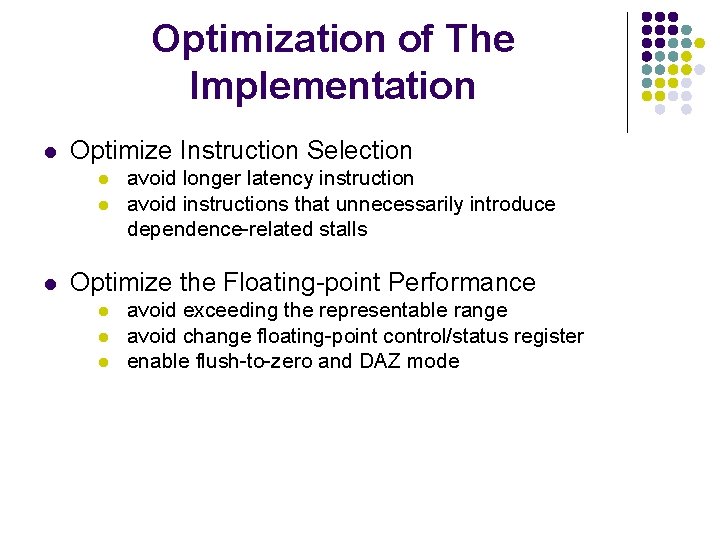

Optimization of The Implementation l Optimize Instruction Selection l l l avoid longer latency instruction avoid instructions that unnecessarily introduce dependence-related stalls Optimize the Floating-point Performance l l l avoid exceeding the representable range avoid change floating-point control/status register enable flush-to-zero and DAZ mode

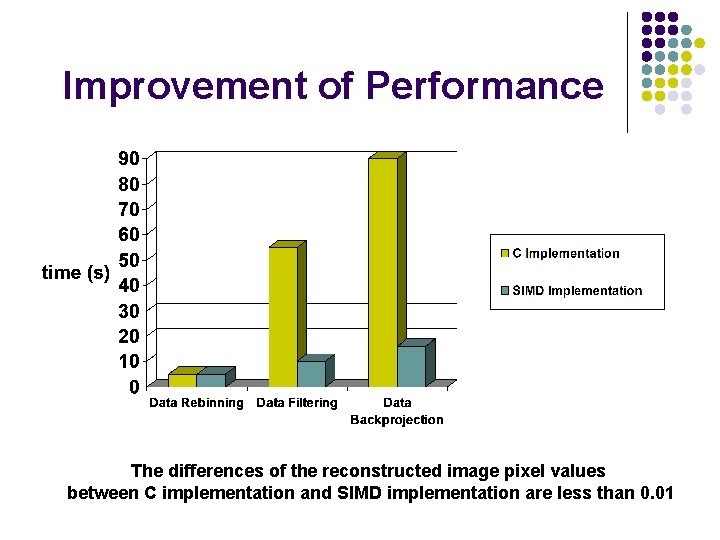

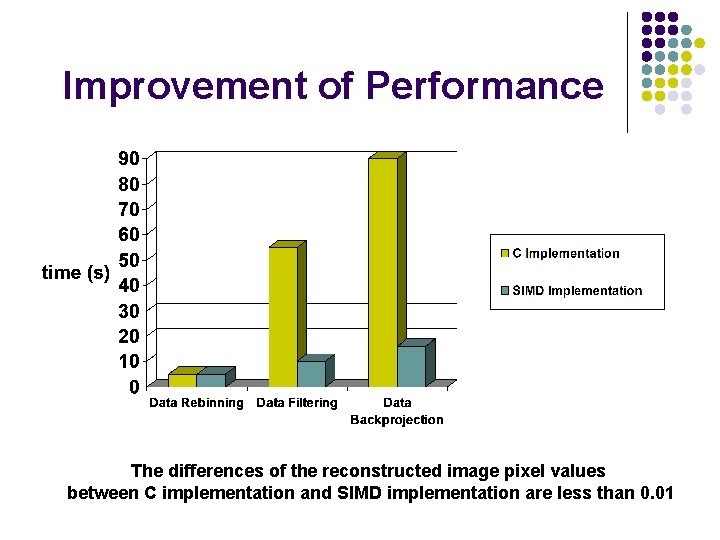

Improvement of Performance The differences of the reconstructed image pixel values between C implementation and SIMD implementation are less than 0. 01