Improvement of Accuracy in Pipelined ADC by methods

Improvement of Accuracy in Pipelined ADC by methods of Calibration Techniques • Presented by : Daniel Chung • Course : ECE 1352 F • Professor : Khoman Phang

Presentation Outline • Introduction to Pipelined A/D converters • Why is Calibration Technique of interest • Performance Limitations • Evolution of Digital Calibration • Future challenges • Conclusion 2

Pipeline ADCs • High resolution and high speed at the same time. • Processing rate = 1 sample per cycle. • Sample-hold amplifier at the input. • Latency = N. N clock cycles to process each input signal. • Compact area and efficient power dissipation • Switch capacitor implementation in CMOS technologies. Capability for high-precision sampling and charge transfer. 3

![Pipeline ADCs Figure 1: N-bit pipeline ADC with 1 -bit/stage resolution. [5] 4 Pipeline ADCs Figure 1: N-bit pipeline ADC with 1 -bit/stage resolution. [5] 4](http://slidetodoc.com/presentation_image_h/2e7fdddcf4c0c33951e65db4c9ed8c8e/image-4.jpg)

Pipeline ADCs Figure 1: N-bit pipeline ADC with 1 -bit/stage resolution. [5] 4

Performance Limitations • Resolution • Quantization error • ENOB – Effective number of bits. Commonly used metric for characterizing the performance of non-ideal quantizers. • INL – Integral Nonlinearity Error • DNL – Differential Nonlinearity Error. • Monotonicity. 5

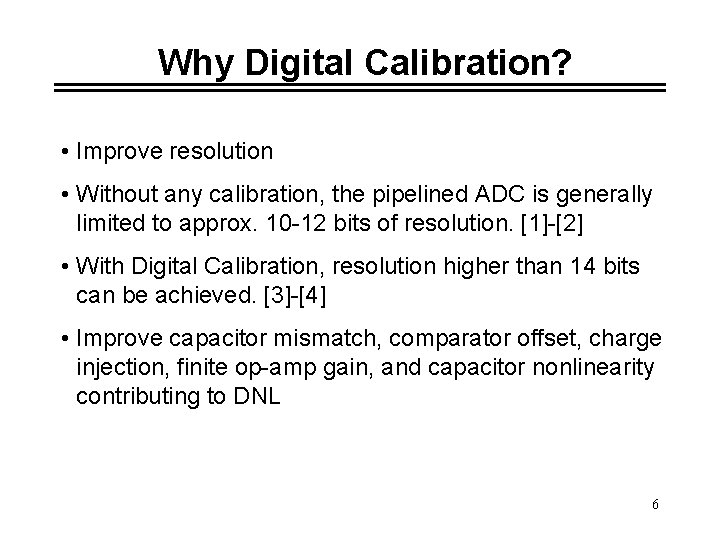

Why Digital Calibration? • Improve resolution • Without any calibration, the pipelined ADC is generally limited to approx. 10 -12 bits of resolution. [1]-[2] • With Digital Calibration, resolution higher than 14 bits can be achieved. [3]-[4] • Improve capacitor mismatch, comparator offset, charge injection, finite op-amp gain, and capacitor nonlinearity contributing to DNL 6

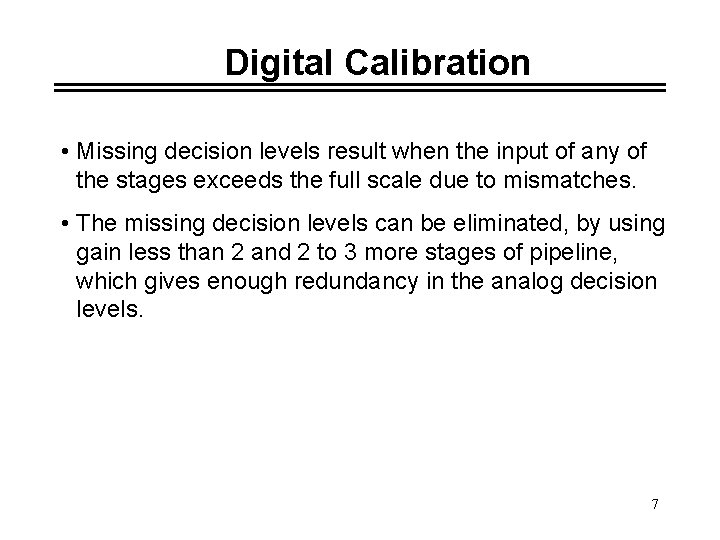

Digital Calibration • Missing decision levels result when the input of any of the stages exceeds the full scale due to mismatches. • The missing decision levels can be eliminated, by using gain less than 2 and 2 to 3 more stages of pipeline, which gives enough redundancy in the analog decision levels. 7

![Digital Calibration Figure 2: Digital Calibration applied to Stage 11. [4] 8 Digital Calibration Figure 2: Digital Calibration applied to Stage 11. [4] 8](http://slidetodoc.com/presentation_image_h/2e7fdddcf4c0c33951e65db4c9ed8c8e/image-8.jpg)

Digital Calibration Figure 2: Digital Calibration applied to Stage 11. [4] 8

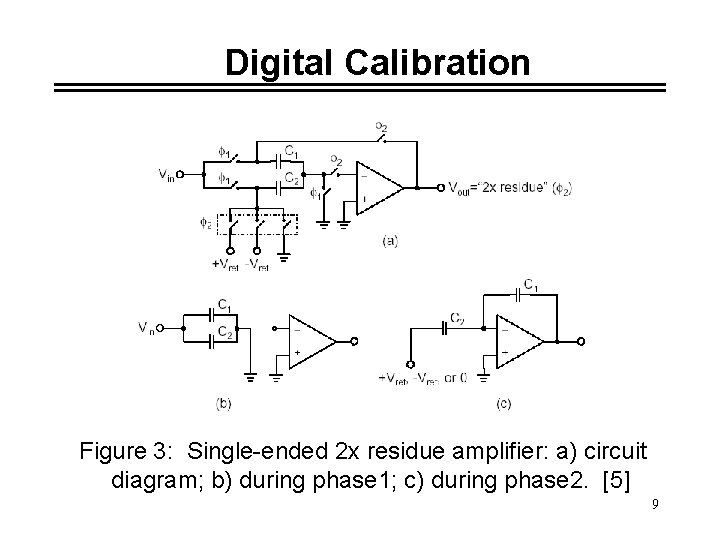

Digital Calibration Figure 3: Single-ended 2 x residue amplifier: a) circuit diagram; b) during phase 1; c) during phase 2. [5] 9

![Digital Calibration Figure 4: Digital Calibration. [4] 10 Digital Calibration Figure 4: Digital Calibration. [4] 10](http://slidetodoc.com/presentation_image_h/2e7fdddcf4c0c33951e65db4c9ed8c8e/image-10.jpg)

Digital Calibration Figure 4: Digital Calibration. [4] 10

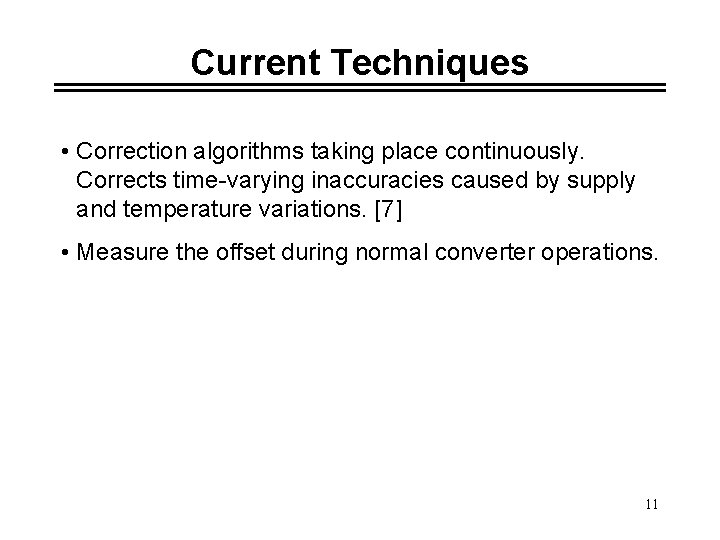

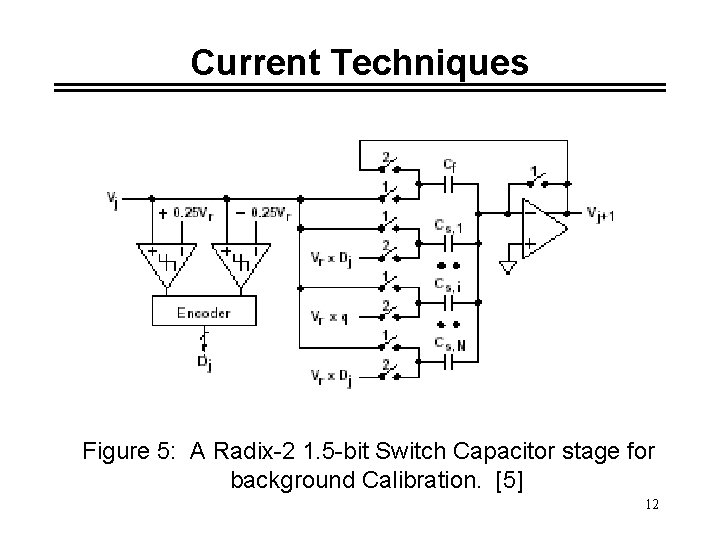

Current Techniques • Correction algorithms taking place continuously. Corrects time-varying inaccuracies caused by supply and temperature variations. [7] • Measure the offset during normal converter operations. 11

Current Techniques Figure 5: A Radix-2 1. 5 -bit Switch Capacitor stage for background Calibration. [5] 12

PRO / CON • PRO • Improve accuracy and resolution compared to not having any calibration circuits. • With calibration techniques, resolution can be improved significantly. • CON • Additional Area. • Complexity of the circuit increases. 13

Future Challenges • With newer processes, better capacitor matching is required. • Minimize the usage of additional circuitry. Further optimization in techniques should improve area utilization and reduce power consumption. 14

Conclusion • Digital self-calibration technique based on radix < 2 applied to a pipeline ADC was discussed. • This technique accounts for capacitor mismatch, comparator offset, finite op-amp gain, and for DNL error contributed by circuit nonlinearities. • Original Digital Calibration techniques executed calibration procedures at the initial turn-on stages. However, more recent methods use continuous calibration techniques, to compensate for the constant variations in supply and temperature. 15

![References [1] S. H. Lewis, H. S. Fetterman, G. F. Gross, R. Ramachandran, and References [1] S. H. Lewis, H. S. Fetterman, G. F. Gross, R. Ramachandran, and](http://slidetodoc.com/presentation_image_h/2e7fdddcf4c0c33951e65db4c9ed8c8e/image-16.jpg)

References [1] S. H. Lewis, H. S. Fetterman, G. F. Gross, R. Ramachandran, and T. R. Viswanathan, “A 10 -b 20 Msample/s analog-to-digital converter, ” IEEE J. Solid. State Circuits, vol. 27, pp. 351 -358, Mar. 1992. [2] T. Byunghak and P. R. Gray, “A 10 -b 20 -Msample/s 35 -m. W pipeline A/D converter, ” IEEE J. Solid-State Circuits, vol. 30, pp. 166 -172, Mar. 1995. [3] M. K. Mayes and S. W. Chin, “A 200 -m. W 1 Msample/s 16 -b, pipelined A/D converter with on-chip 32 -b microcontroller, ” IEEE J. Solid-State Circuits, vol. 31, pp. 1862 -1872, Dec. 1996. 16

![References [4] A. N. Karanicolas, H. S. Lee and K. L. Bacrania, “A 15 References [4] A. N. Karanicolas, H. S. Lee and K. L. Bacrania, “A 15](http://slidetodoc.com/presentation_image_h/2e7fdddcf4c0c33951e65db4c9ed8c8e/image-17.jpg)

References [4] A. N. Karanicolas, H. S. Lee and K. L. Bacrania, “A 15 -b 1 -Msample/s digitally self-calibrated pipeline ADC, ” IEEE J. Solid-State Circuits, vol. 28, pp. 1207 -1215, Dec. 1993. [5] U. Moon, J. Steensgaard, and G. Temes, “Digital techniques for improving the accuracy of data converters, “IEEE Comm. Magazine, pp. 136 -143, Oct. 1999. [6] H. C. Liu, Z. M. Lee, J. T. Wu, “A Digital background calibration technique for pipelined analog-to-digital converters, ” IEEE, pp. I-881 - I-884, 2003. 17

![References [7] U. Moon and B. Song, “Background digital calibration techniques for pipelined ADCs, References [7] U. Moon and B. Song, “Background digital calibration techniques for pipelined ADCs,](http://slidetodoc.com/presentation_image_h/2e7fdddcf4c0c33951e65db4c9ed8c8e/image-18.jpg)

References [7] U. Moon and B. Song, “Background digital calibration techniques for pipelined ADCs, ” IEEE Trans. Circuits Syst. II, pp. 102 -109, Feb. 1997. [8] H. S. Lee, D. A. Hodges and P. R. Gray, “A selfcalibrating 15 -bit CMOS A/D converter, ” IEEE J. of Solid-State Circuits, vol. 19, pp. 813 -819, Dec. 1984. [9] D. A. Johns, K. Martin, “Analog Integrated Circuit Design. ” John Wiley & Sons, Inc. New York, 1997. [10] W. Law, J. Guo, C. T. Peach, W. J. Helms, and D. J. Allstot, “A Monotonic Digital Calibration Technique for Pipelined Data Converters, ” ISCAS 2003, Vol. 1, pp. I 873 -I 876, 25 -28 May 2003. 18

Questions? 19

- Slides: 19