Implementing ISO 26262 Compliant AI SystemsonChip with Arteris

- Slides: 22

Implementing ISO 26262 Compliant AI Systems-on-Chip with Arteris IP DESIGN & REUSE IP-SOC DAYS 2019 12 SEPTEMBER 2019, SHANGHAI, CHINA WILLIAM TSENG Field Applications Engineering Manager, Arteris IP

Agenda 1 Arteris IP No. C & ISO 26262 Leadership 2 AI/ML So. C Development using No. C Technology 3 AI/ML So. Cs and ISO 26262 Compliance 4 Conclusion 12 September 2019 Copyright © Arteris IP 2019 2

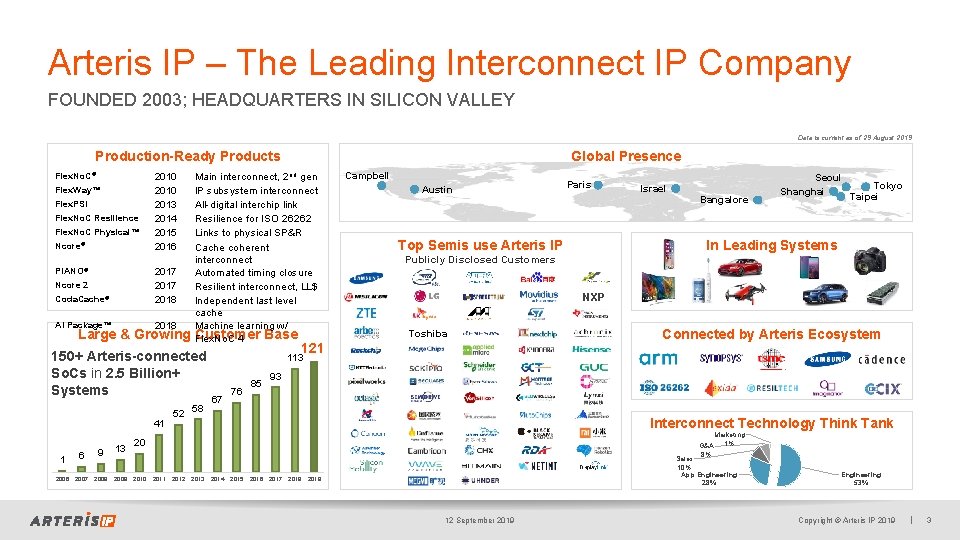

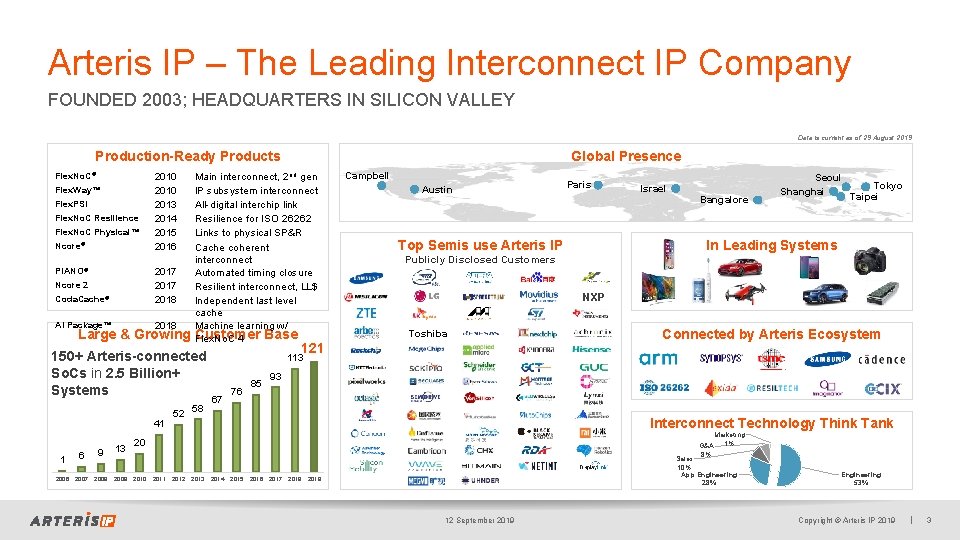

Arteris IP – The Leading Interconnect IP Company FOUNDED 2003; HEADQUARTERS IN SILICON VALLEY Data is current as of 29 August 2019 Global Presence Production-Ready Products Flex. No. C® Flex. Way™ Flex. PSI Flex. No. C Resilience Flex. No. C Physical™ Ncore® PIANO® 2010 2013 2014 2015 2016 Coda. Cache® 2017 2018 AI Package™ 2018 Ncore 2 Large & Growing Main interconnect, 2 nd gen IP subsystem interconnect All-digital interchip link Resilience for ISO 26262 Links to physical SP&R Cache coherent interconnect Automated timing closure Resilient interconnect, LL$ Independent last level cache Machine learning w/ Customer Base Flex. No. C 4 150+ Arteris-connected So. Cs in 2. 5 Billion+ Systems 41 1 2006 6 9 2007 2008 13 2009 52 58 Campbell Austin Top Semis use Arteris IP Israel Bangalore 2012 Tokyo Taipei In Leading Systems NXP Toshiba 121 Connected by Arteris Ecosystem 113 67 76 85 93 Interconnect Technology Think Tank G&A 8% 2011 Seoul Shanghai Publicly Disclosed Customers 20 2010 Paris 2013 2014 2015 2016 2017 2018 Marketing 1% Sales 10% App Engineering 28% 2019 12 September 2019 Engineering 53% Copyright © Arteris IP 2019 3

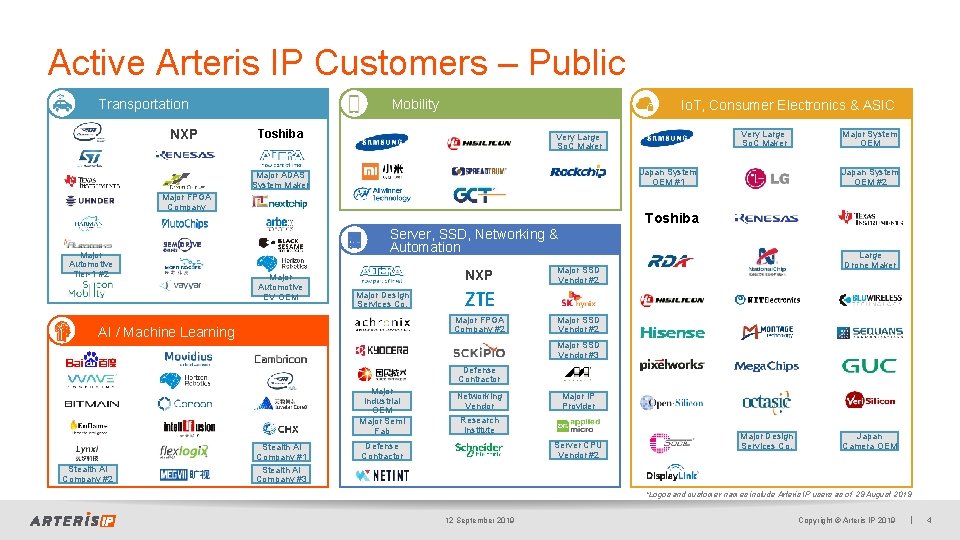

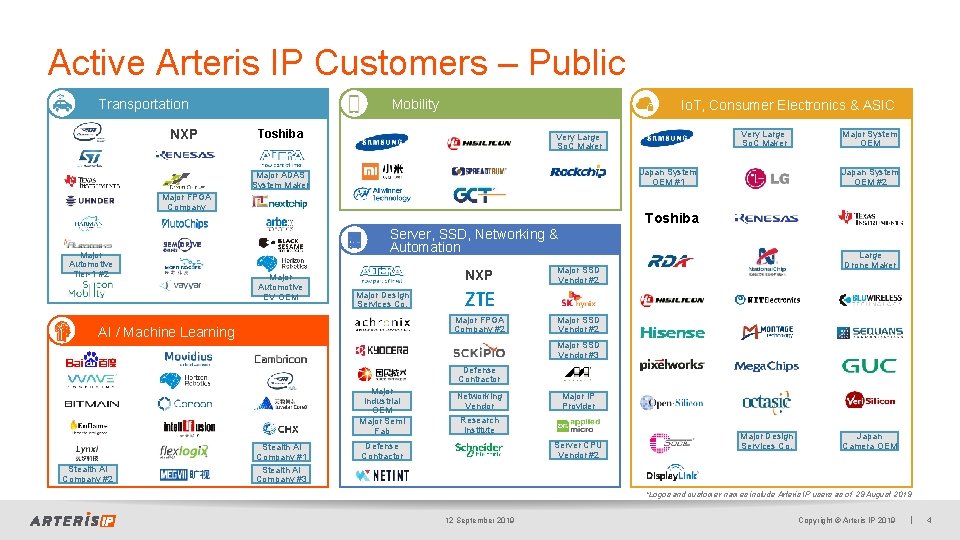

Active Arteris IP Customers – Public Transportation NXP Mobility Io. T, Consumer Electronics & ASIC Toshiba Japan System OEM #1 Major ADAS System Maker Major FPGA Company Major Automotive Tier-1 #2 Very Large So. C Maker Major System OEM Japan System OEM #2 Toshiba Server, SSD, Networking & Automation Major Automotive EV OEM NXP Major SSD Vendor #2 Major FPGA Company #2 Major SSD Vendor #2 Large Drone Maker Major Design Services Co. AI / Machine Learning Major SSD Vendor #3 Defense Contractor Major Industrial OEM Major Semi Fab Stealth AI Company #2 Stealth AI Company #1 Stealth AI Company #3 Networking Vendor Major IP Provider Research Institute Server CPU Vendor #2 Defense Contractor Major Design Services Co. Japan Camera OEM *Logos and customer names include Arteris IP users as of 29 August 2019 12 September 2019 Copyright © Arteris IP 2019 4

ISO 26262 and Automotive Functional Safety • Arteris IP is an ISO 26262 working group member and contributed to writing the 2 nd Edition (2018) specification • Initial ADAS So. Cs were ISO 26262 ASIL B classification • Mainstream ADAS So. Cs now aim to attain ASIL D classification 12 September 2019 Copyright © Arteris IP 2019 5

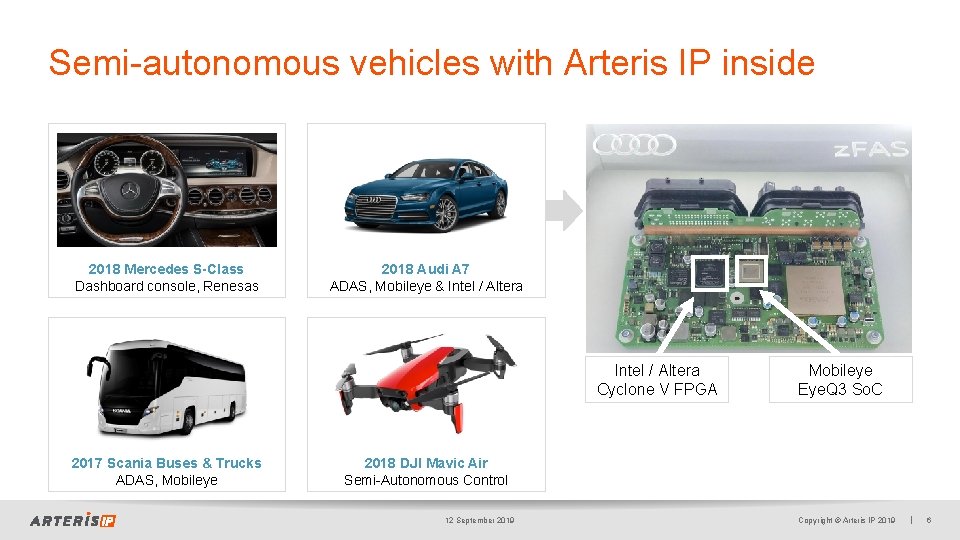

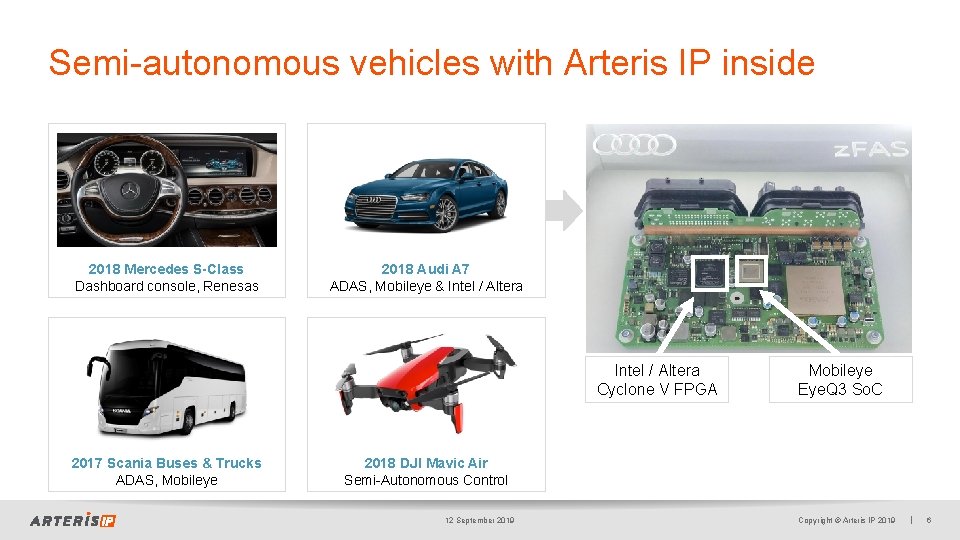

Semi-autonomous vehicles with Arteris IP inside 2018 Mercedes S-Class Dashboard console, Renesas 2018 Audi A 7 ADAS, Mobileye & Intel / Altera Cyclone V FPGA 2017 Scania Buses & Trucks ADAS, Mobileye Eye. Q 3 So. C 2018 DJI Mavic Air Semi-Autonomous Control 12 September 2019 Copyright © Arteris IP 2019 6

AI/ML So. C Development using No. C Technology 12 September 2019 Copyright © Arteris IP 2019 7

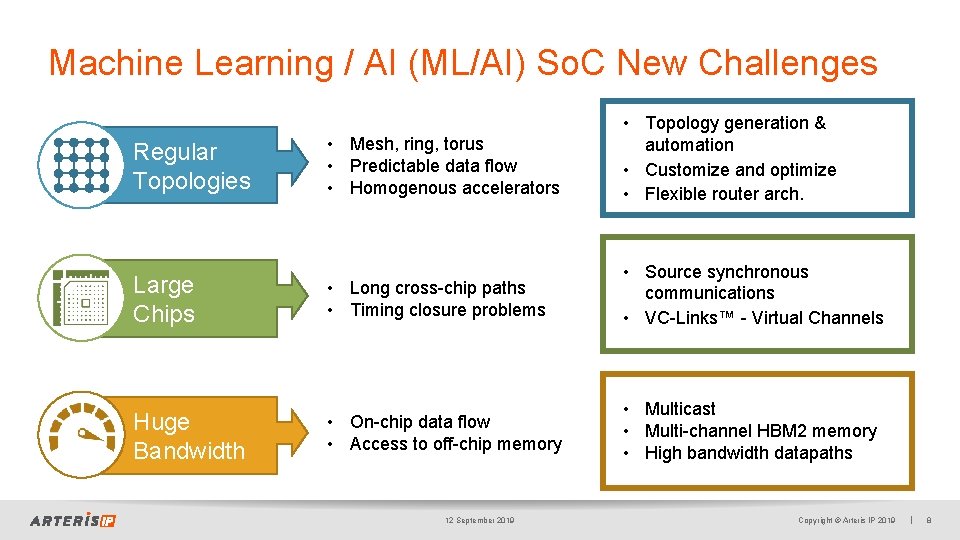

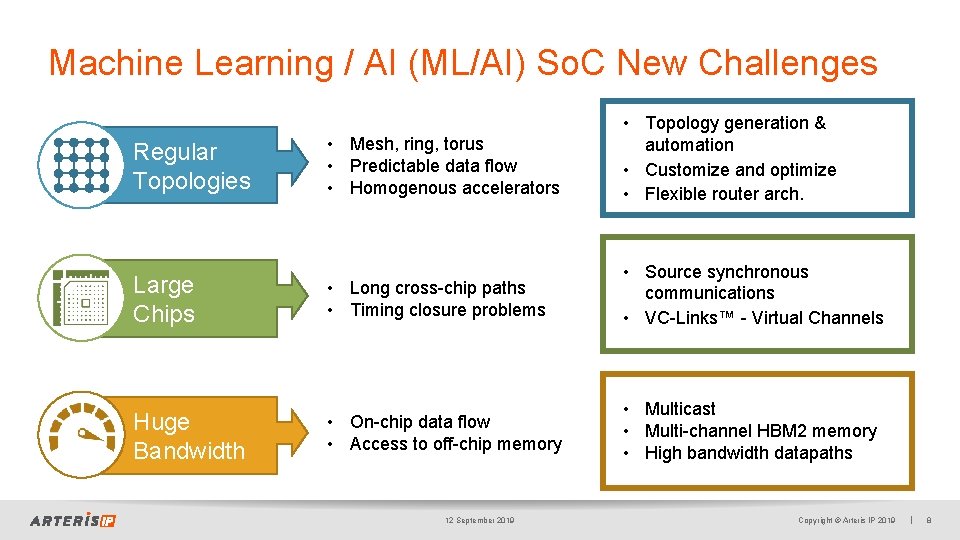

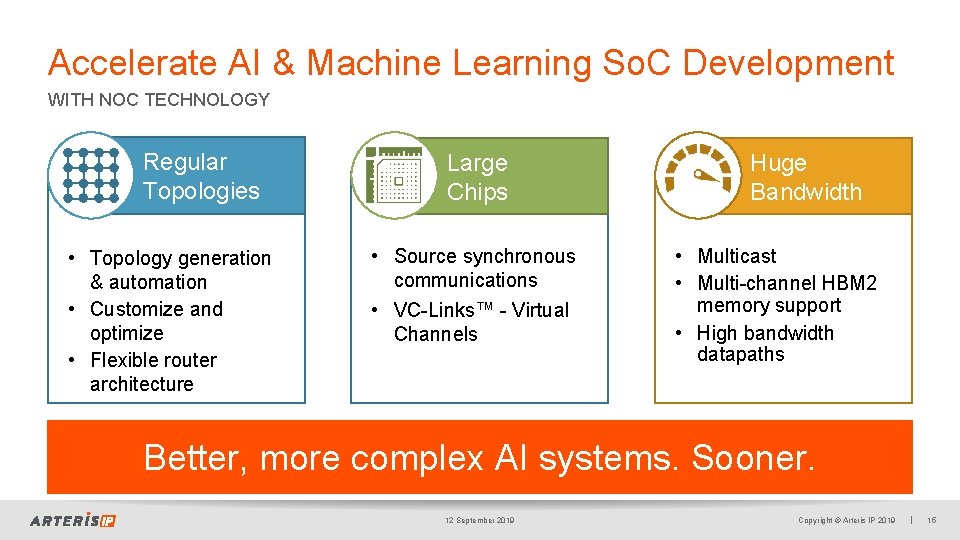

Machine Learning / AI (ML/AI) So. C New Challenges Regular Topologies Large Chips Huge Bandwidth • Mesh, ring, torus • Predictable data flow • Homogenous accelerators • Topology generation & automation • Customize and optimize • Flexible router arch. • Long cross-chip paths • Timing closure problems • Source synchronous communications • VC-Links™ - Virtual Channels • On-chip data flow • Access to off-chip memory • Multicast • Multi-channel HBM 2 memory • High bandwidth datapaths 12 September 2019 Copyright © Arteris IP 2019 8

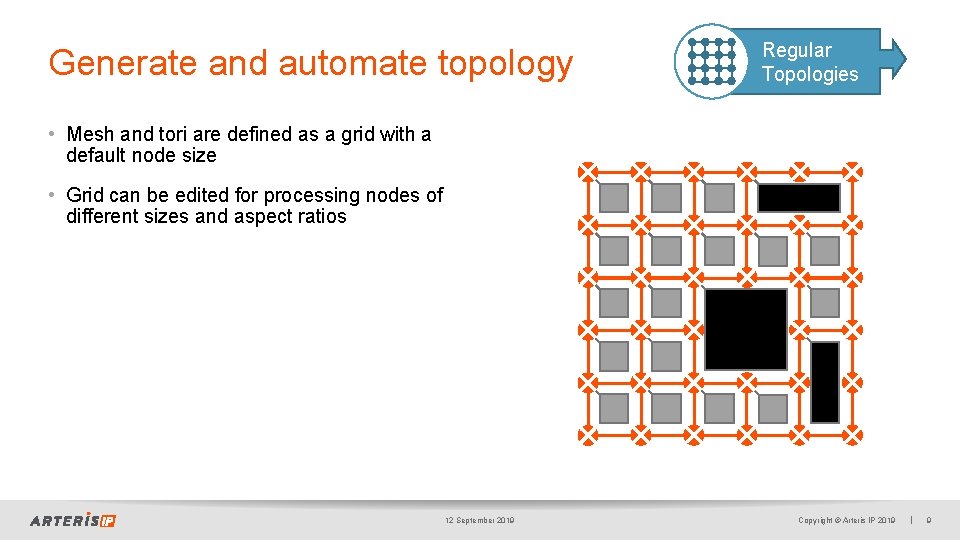

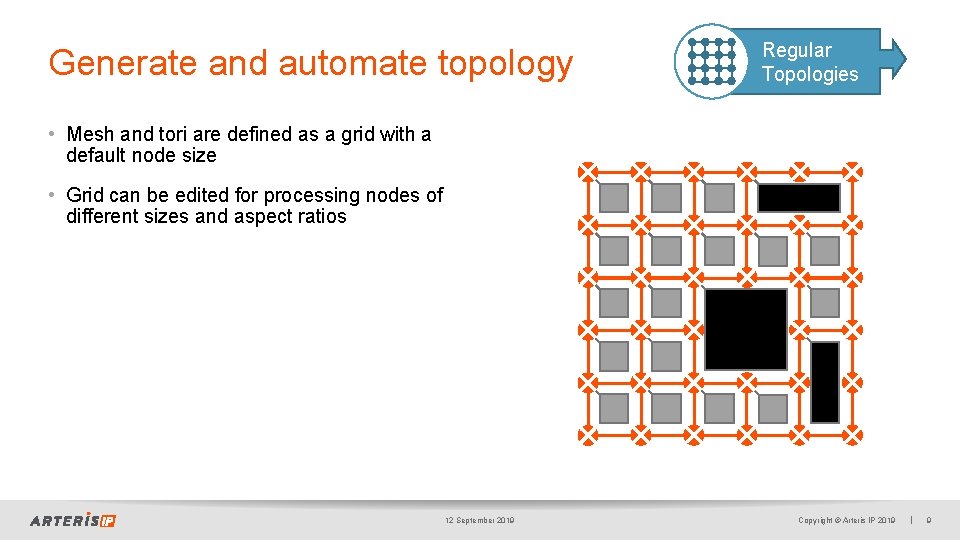

Generate and automate topology Regular Topologies • Mesh and tori are defined as a grid with a default node size • Grid can be edited for processing nodes of different sizes and aspect ratios 12 September 2019 Copyright © Arteris IP 2019 9

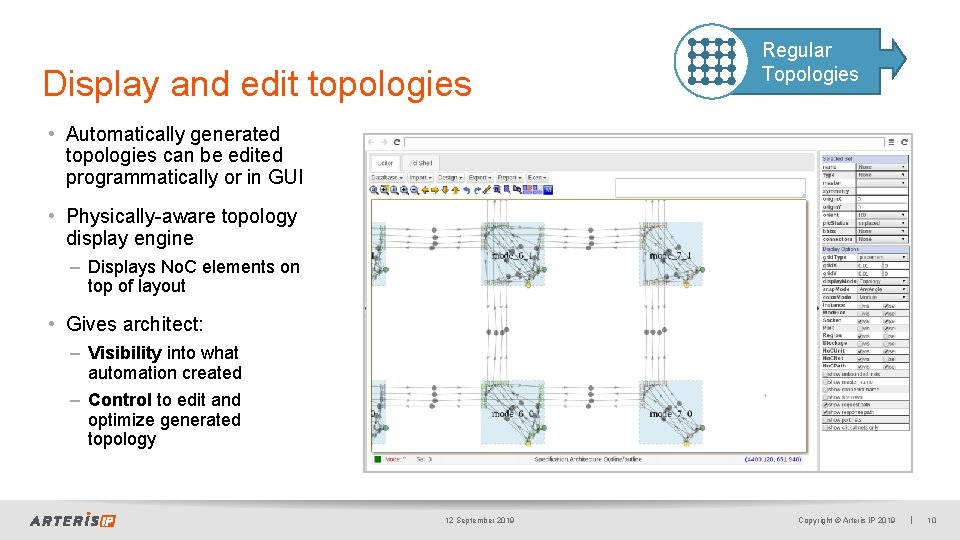

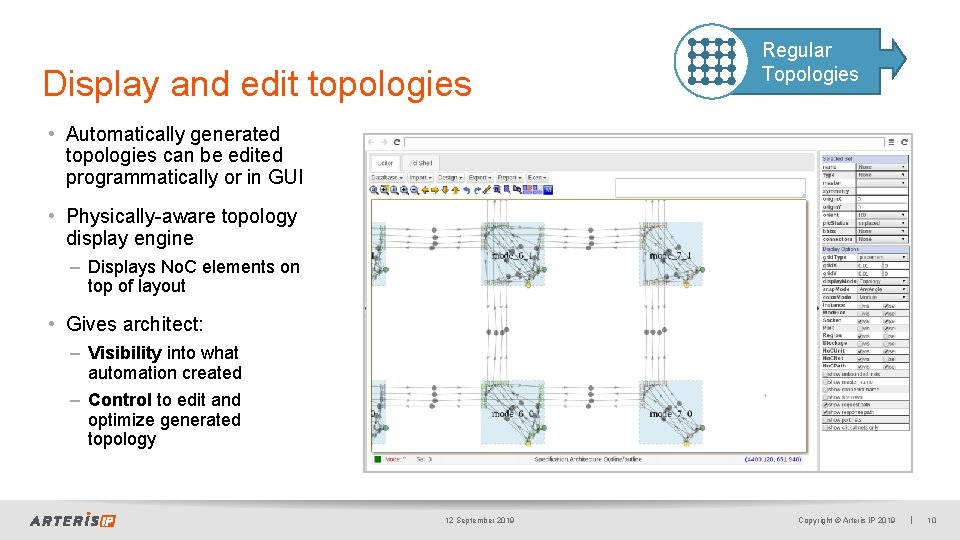

Display and edit topologies Regular Topologies • Automatically generated topologies can be edited programmatically or in GUI • Physically-aware topology display engine – Displays No. C elements on top of layout • Gives architect: – Visibility into what automation created – Control to edit and optimize generated topology 12 September 2019 Copyright © Arteris IP 2019 10

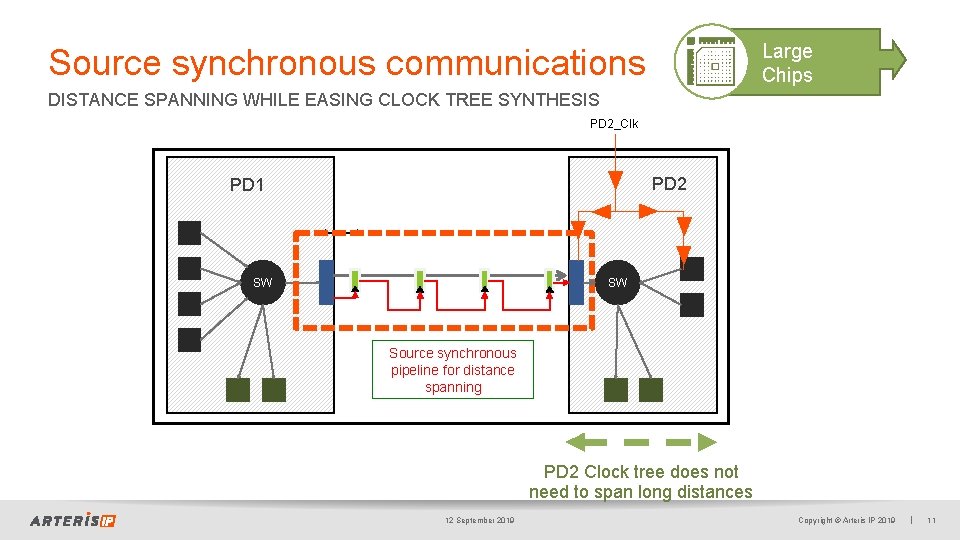

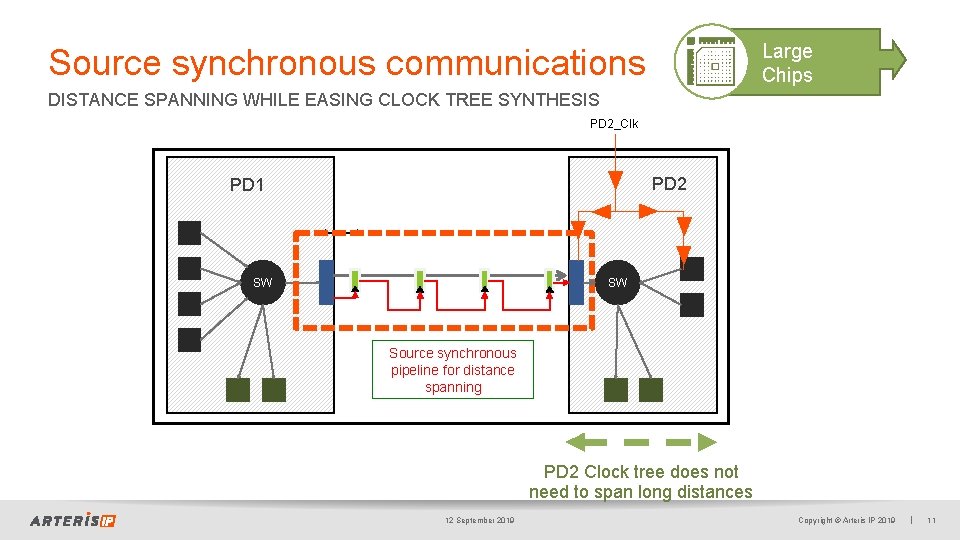

Large Chips Source synchronous communications DISTANCE SPANNING WHILE EASING CLOCK TREE SYNTHESIS PD 2_Clk PD 2 PD 1 SW SW Source synchronous pipeline for distance spanning PD 2 Clock tree does not need to span long distances 12 September 2019 Copyright © Arteris IP 2019 11

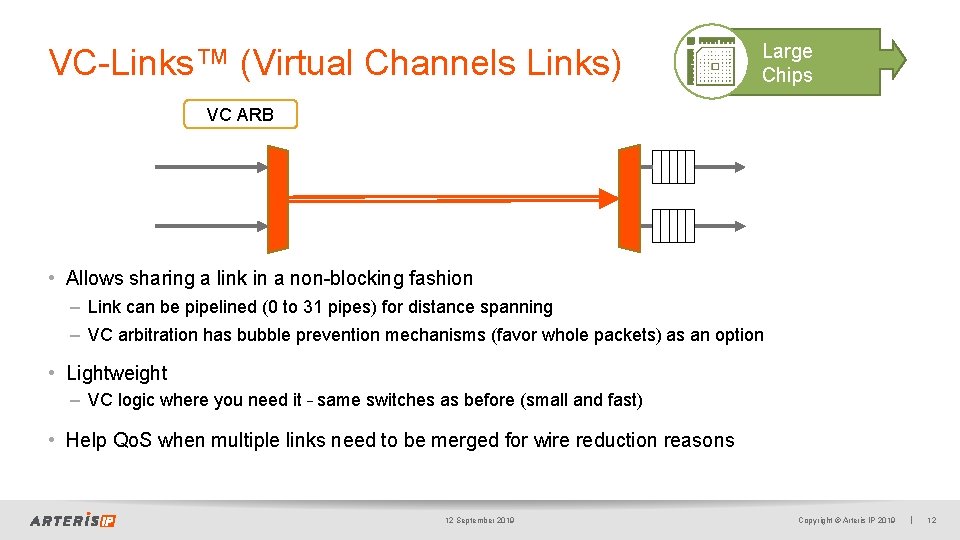

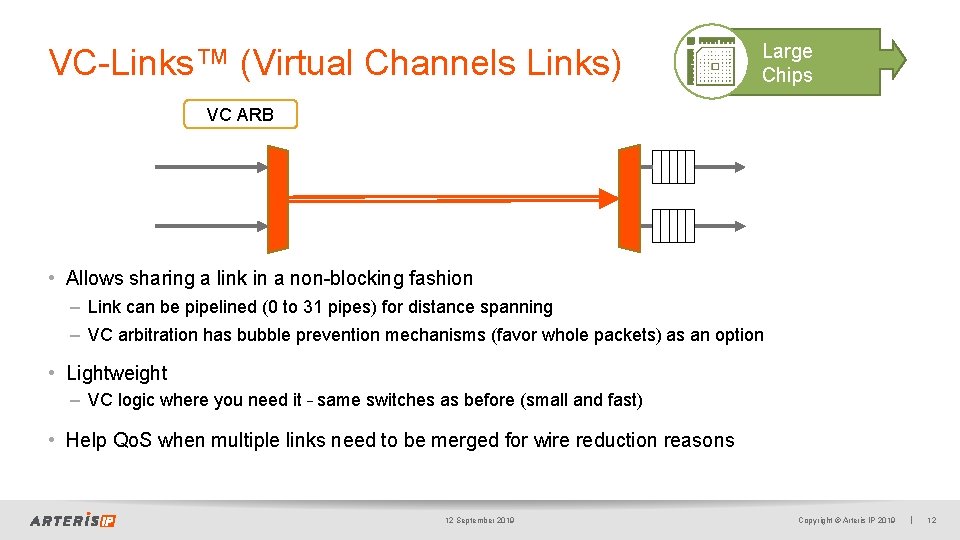

VC-Links™ (Virtual Channels Links) Large Chips VC ARB • Allows sharing a link in a non-blocking fashion – Link can be pipelined (0 to 31 pipes) for distance spanning – VC arbitration has bubble prevention mechanisms (favor whole packets) as an option • Lightweight – VC logic where you need it – same switches as before (small and fast) • Help Qo. S when multiple links need to be merged for wire reduction reasons 12 September 2019 Copyright © Arteris IP 2019 12

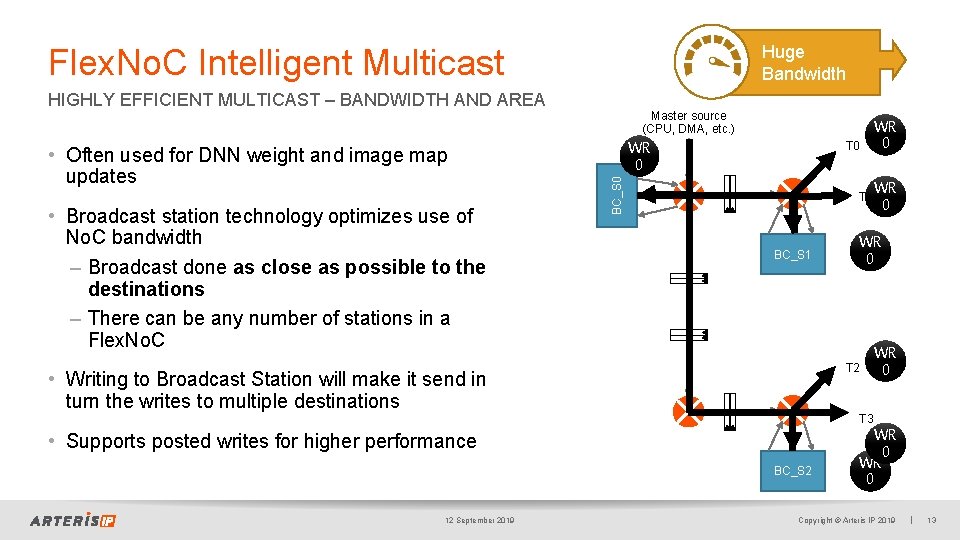

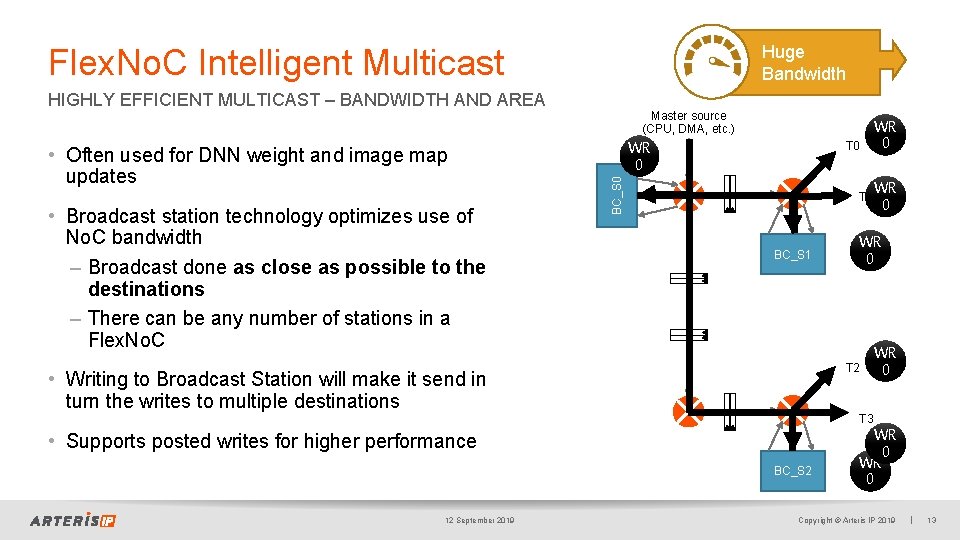

Huge Bandwidth Flex. No. C Intelligent Multicast HIGHLY EFFICIENT MULTICAST – BANDWIDTH AND AREA • Broadcast station technology optimizes use of No. C bandwidth – Broadcast done as close as possible to the destinations – There can be any number of stations in a Flex. No. C WR 0 T 0 BC_S 0 • Often used for DNN weight and image map updates Master source (CPU, DMA, etc. ) T 1 BC_S 1 WR 0 T 3 • Supports posted writes for higher performance BC_S 2 12 September 2019 WR 0 T 2 • Writing to Broadcast Station will make it send in turn the writes to multiple destinations WR 0 Copyright © Arteris IP 2019 13

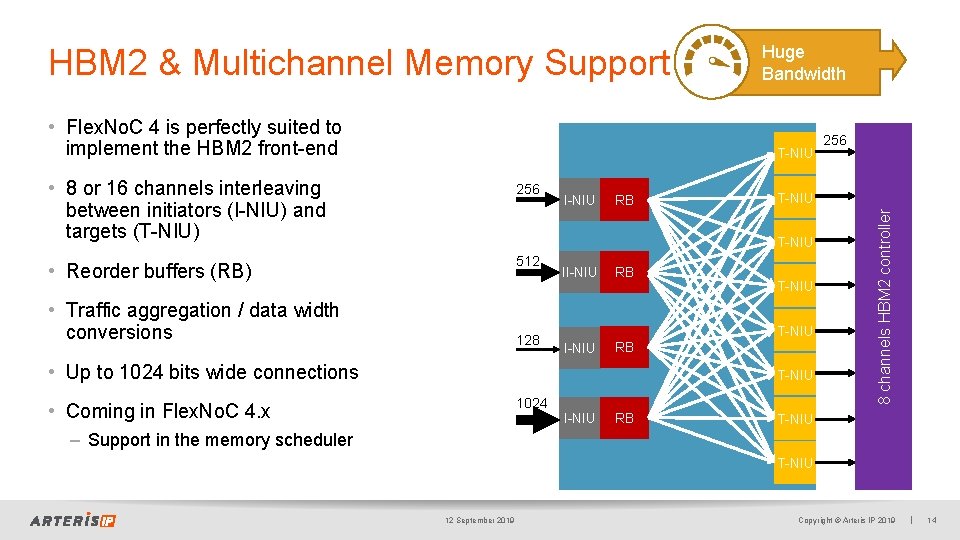

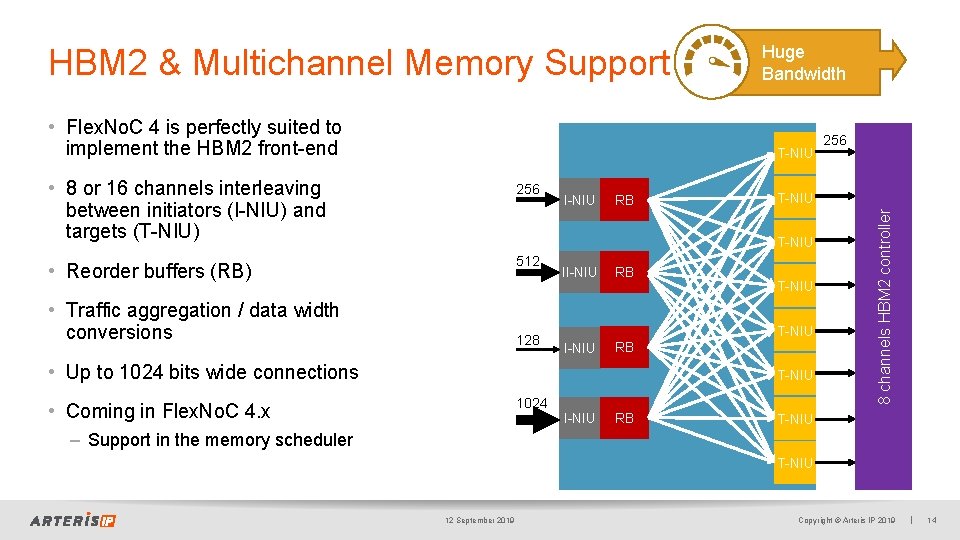

• Flex. No. C 4 is perfectly suited to implement the HBM 2 front-end T-NIU • 8 or 16 channels interleaving between initiators (I-NIU) and targets (T-NIU) 256 • Reorder buffers (RB) 512 I-NIU RB T-NIU • Traffic aggregation / data width conversions 128 II-NIU RB T-NIU I-NIU RB • Up to 1024 bits wide connections T-NIU 1024 • Coming in Flex. No. C 4. x I-NIU RB 256 8 channels HBM 2 controller HBM 2 & Multichannel Memory Support Huge Bandwidth T-NIU – Support in the memory scheduler T-NIU 12 September 2019 Copyright © Arteris IP 2019 14

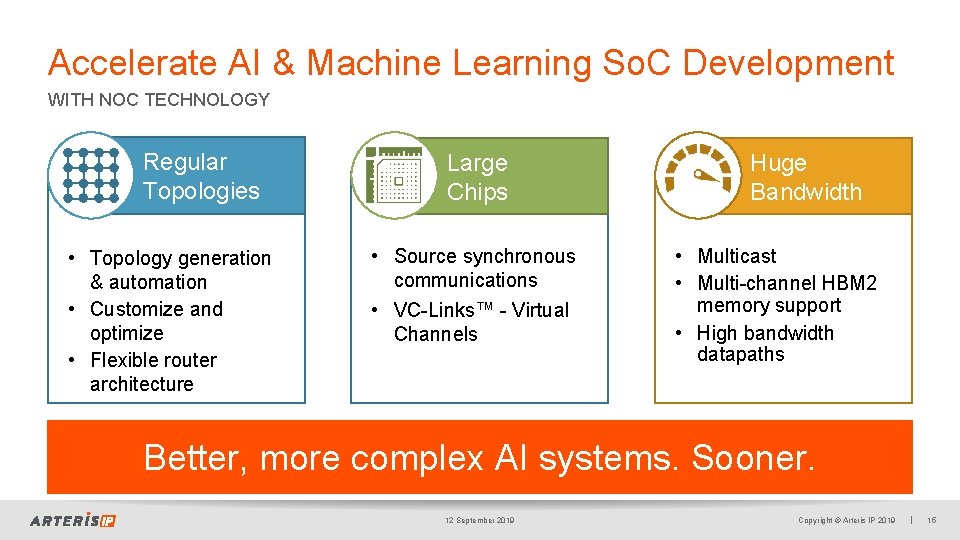

Accelerate AI & Machine Learning So. C Development WITH NOC TECHNOLOGY Regular Topologies • Topology generation & automation • Customize and optimize • Flexible router architecture Large Chips • Source synchronous communications • VC-Links™ - Virtual Channels Huge Bandwidth • Multicast • Multi-channel HBM 2 memory support • High bandwidth datapaths Better, more complex AI systems. Sooner. 12 September 2019 Copyright © Arteris IP 2019 15

AI/ML So. Cs and ISO 26262 Compliance 12 September 2019 Copyright © Arteris IP 2019 16

Challenges for ISO 26262 -compliant AI So. Cs Whether using own AI IP subsystem or 3 rd Party AI IP • Hardware integration is only the first part – Transaction protocols, performance modeling, verification • ISO 26262 processes, analyses, deliverables and work products are key! – IP, whether internally developed or commercial, must be developed using quality processes – Hardware requires safety mechanisms and diagnostic capability (especially for ASIL B, C and D) – Analyses (DFA, FMEDA, etc. ) and validation measures (including Fault Injection) 12 September 2019 Copyright © Arteris IP 2019 17

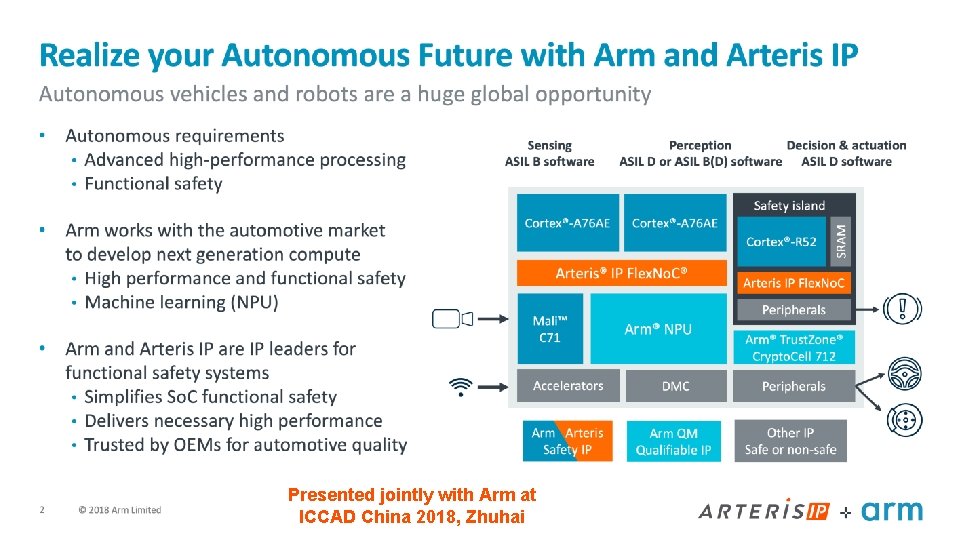

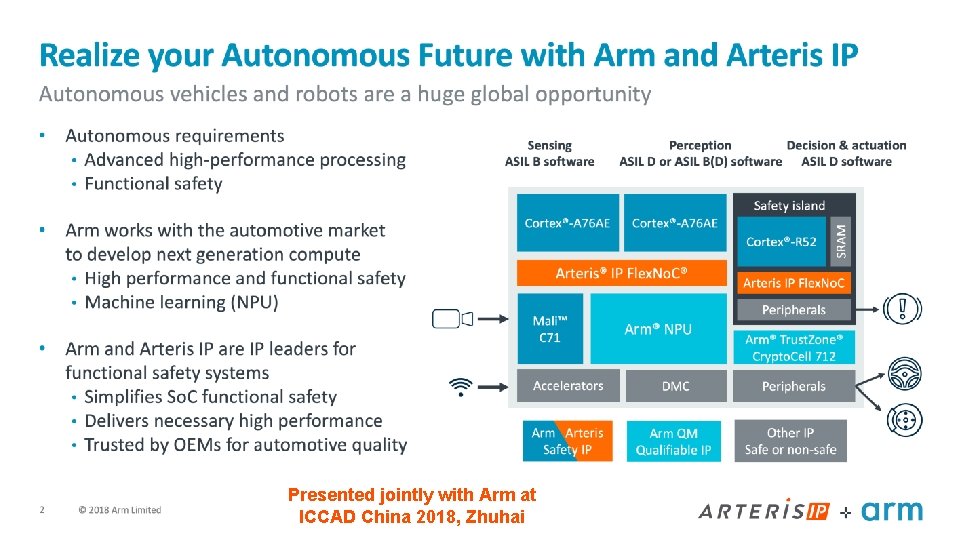

Presented jointly with Arm at 12 September 2019 ICCAD China 2018, Zhuhai Copyright © Arteris IP 2019 18

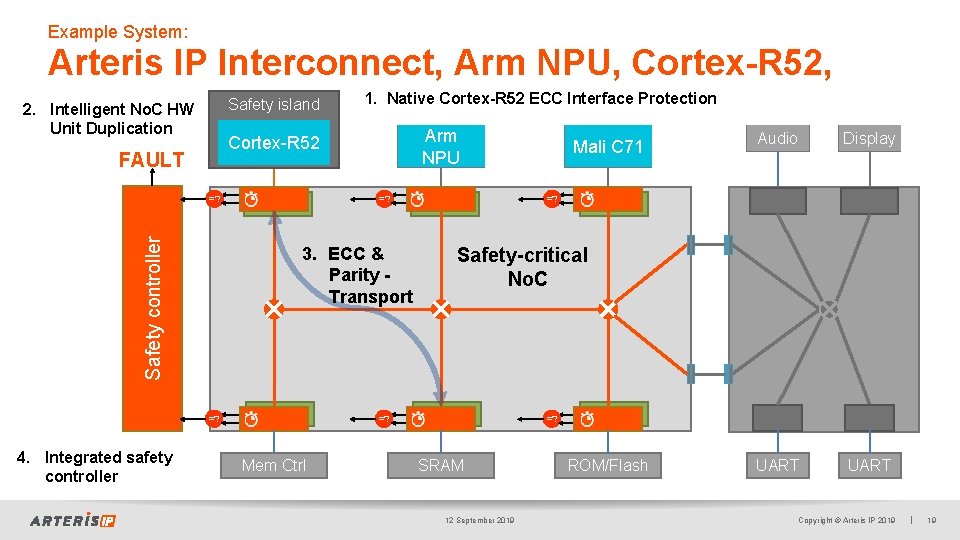

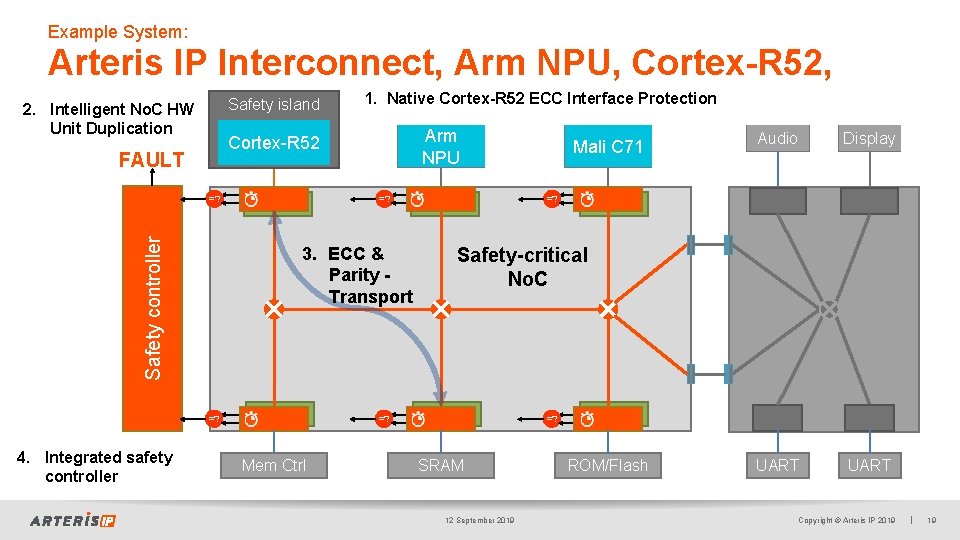

Example System: Arteris IP Interconnect, Arm NPU, Cortex-R 52, Safety island 2. Intelligent No. C HW Unit Duplication Arm AI NPU Cortex-R 52 FAULT Safety controller =? 3. ECC & Parity Transport =? 4. Integrated safety controller 1. Native Cortex-R 52 ECC Interface Protection Audio Display UART =? Safety-critical No. C =? Mem Ctrl Mali OD C 71 =? SRAM 12 September 2019 ROM/Flash Copyright © Arteris IP 2019 19

Conclusion 12 September 2019 Copyright © Arteris IP 2019 20

No. C technology enables ISO 26262 -compliant AI So. Cs 1. No. C interconnect technology is used a. b. Within AI/ML hardware processing subsystems To manage dataflow between multiple AI/ML subsystems 2. Managing AI/ML dataflow requires specialized No. C technologies a. b. c. Regular topologies for large scale designs Source synchronous and virtual channel communications for long distances Multicast and HBM 2 support for high bandwidth 3. All must be developed with safety in mind a. Processes, analyses (DFA, FMEDA, etc. ), deliverables, work products Implementing AI/ML in ISO 26262 -compliant systems requires Technology, Experience and Trust! 12 September 2019 Copyright © Arteris IP 2019 21

12 September 2019 Copyright © Arteris IP 2019 22