Implementation of VariableBlock Size Motion Estimation Algorithm Using

Implementation of Variable-Block. Size Motion Estimation Algorithm Using Systolic Array Architecture Yen-Ting Lin Wei-Jen Chen

Outline n n n Motion estimation algorithms( Full Search Block Matching Algorithm) Systolic array architecture for motion estimation algorithms Implementations

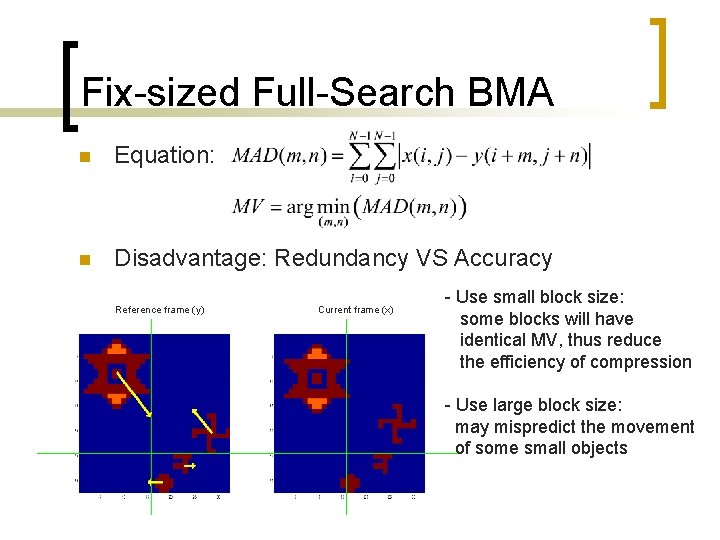

Fix-sized Full-Search BMA n Equation: n Disadvantage: Redundancy VS Accuracy Reference frame (y) Current frame (x) - Use small block size: some blocks will have identical MV, thus reduce the efficiency of compression - Use large block size: may mispredict the movement of some small objects

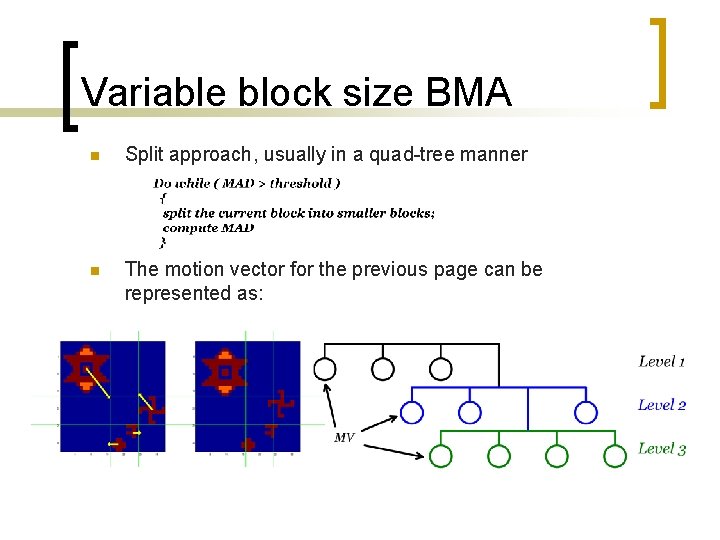

Variable block size BMA n Split approach, usually in a quad-tree manner n The motion vector for the previous page can be represented as:

![Systolic array mapping for 4 x 4 full-search BMA [Yeo and Hu] n n Systolic array mapping for 4 x 4 full-search BMA [Yeo and Hu] n n](http://slidetodoc.com/presentation_image/ffbb444b53dfcb3a682e81edff60aa7e/image-5.jpg)

Systolic array mapping for 4 x 4 full-search BMA [Yeo and Hu] n n Write down the 6 level do loop algorithm Reformatted into a three level nested do loops Localize the indexes of the inner loop indexes Project the 3 -dim array two times into 1 -dim systolic array

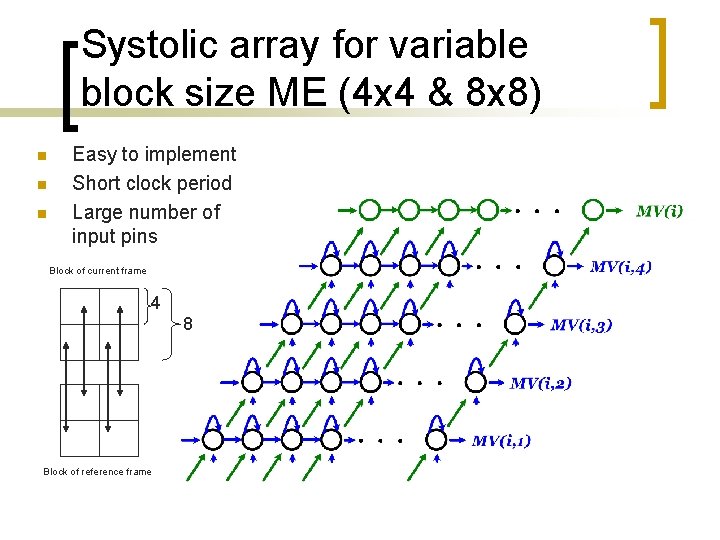

Systolic array for variable block size ME (4 x 4 & 8 x 8) n n n Easy to implement Short clock period Large number of input pins Block of current frame 4 8 Block of reference frame

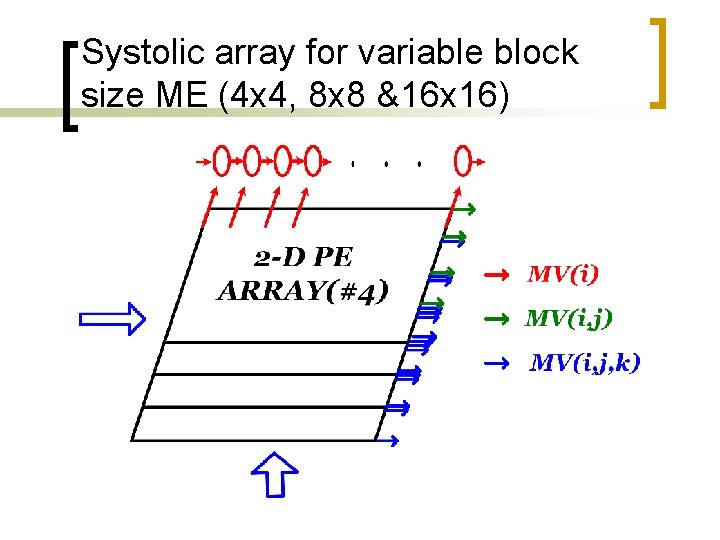

Systolic array for variable block size ME (4 x 4, 8 x 8 &16 x 16)

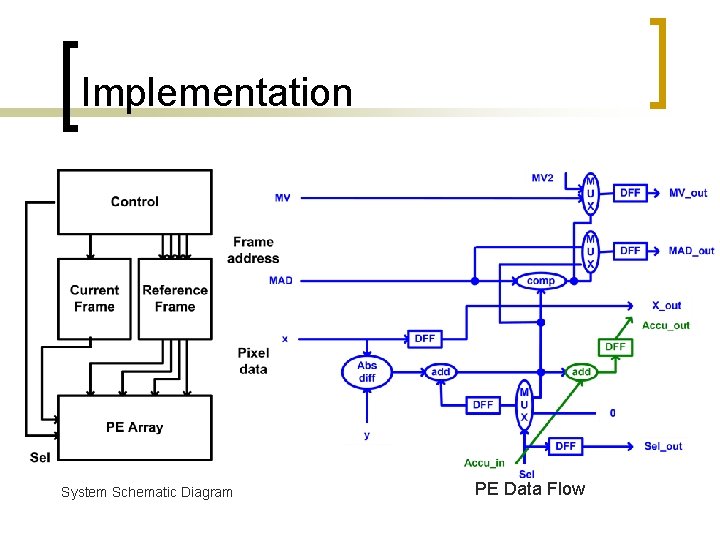

Implementation System Schematic Diagram PE Data Flow

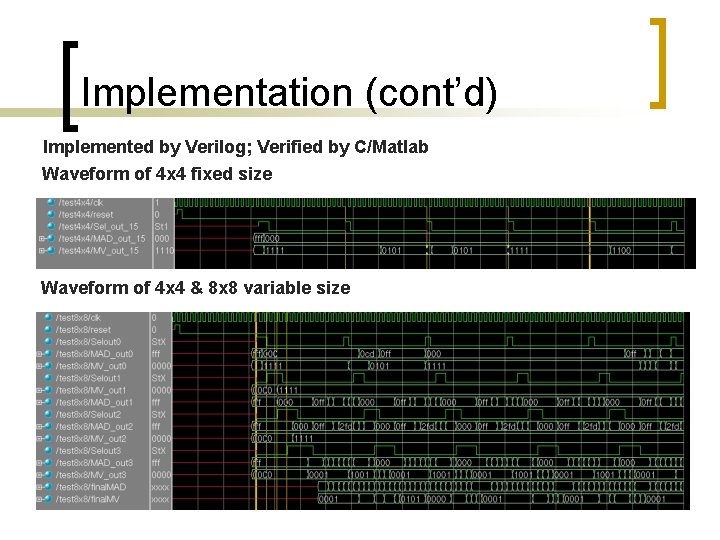

Implementation (cont’d) Implemented by Verilog; Verified by C/Matlab Waveform of 4 x 4 fixed size Waveform of 4 x 4 & 8 x 8 variable size

- Slides: 9