Implementation Of A Lower Level Architecture For The

- Slides: 43

Implementation Of A Lower Level Architecture For The Sombrero Single Address Space Operating System Donald White Arizona State University 08/11/2005 Donald White Thesis Defense Arizona State University

Outline • • • Introduction Development Environment Lower Level Sombrero Architecture Interrupt Processing Architecture Device Driver Architecture Protocol Component Architecture Sombrero Protocol Description Standard Library Contributions and Conclusions Future Work 08/11/2005 Donald White Thesis Defense Arizona State University 2

Introduction • Sombrero is an unconventional OS – Single Address Space – Object Orientation • Current implementation does not always exploit the Sombrero paradigm shift • Design choices based on intuition rather than measurement • Implementation sometimes reflects expediency 08/11/2005 Donald White Thesis Defense Arizona State University 3

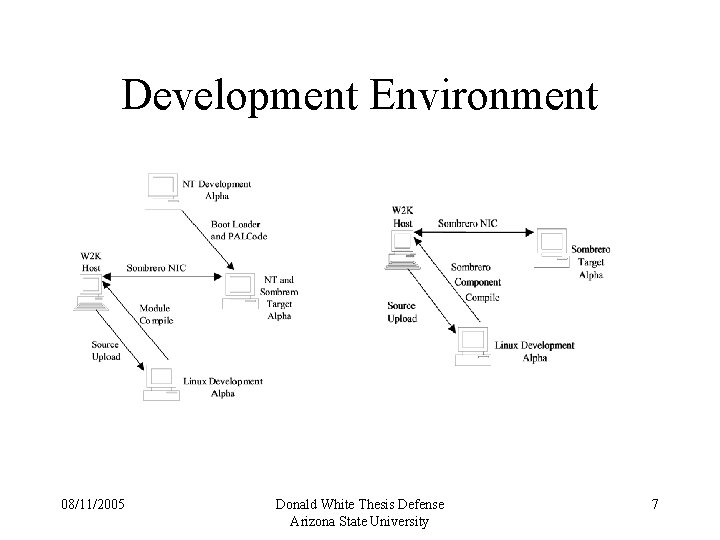

Development Environment • Boot Loader – Replace ARC SDK with gcc • PALCode – Replace EBSDK with gcc • Tools – Object Strip – ARCDOS – SOSRMAKE 08/11/2005 Donald White Thesis Defense Arizona State University 4

Development Environment • Ethereal – Open Source Protocol Analyzer – Plug-in Dissector for Sombrero Protocols • Revision Control – Subversion – Apache with Web. DAV – Tortise. SVN – SSL for Controlled Access 08/11/2005 Donald White Thesis Defense Arizona State University 5

Development Environment • Simplified Configuration with Enhanced Boot Loader – PCI Bus Scan to find Network Card – UART Driver and Input-Output Library – Real Time Clock – Address Resolution Protocol Support 08/11/2005 Donald White Thesis Defense Arizona State University 6

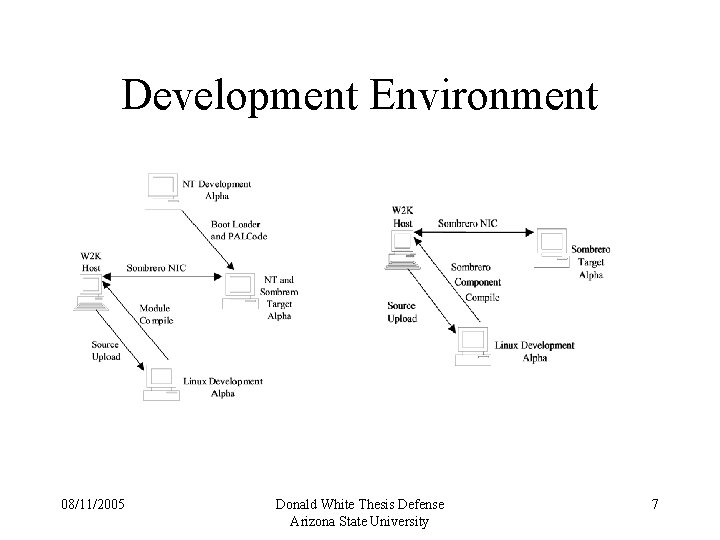

Development Environment 08/11/2005 Donald White Thesis Defense Arizona State University 7

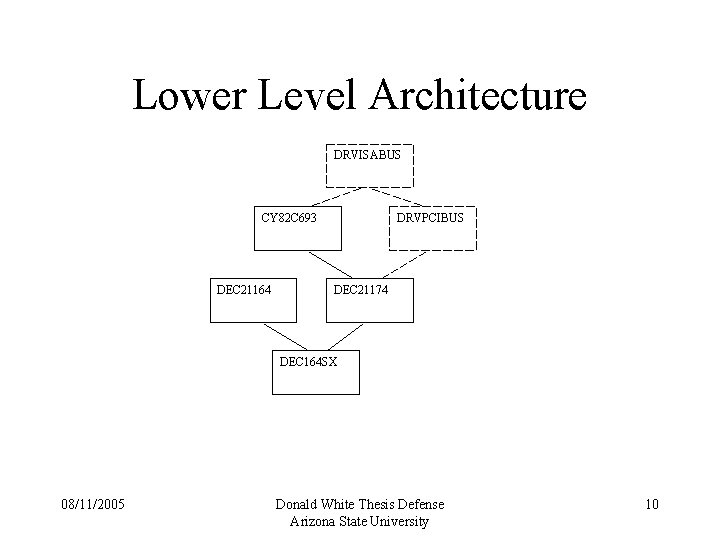

Lower Level Architecture • Design Approach – Exploit Sombrero Object Oriented Nature – Represent Hardware Components as Software Objects – Implement Abstract Objects using Concrete Objects 08/11/2005 Donald White Thesis Defense Arizona State University 8

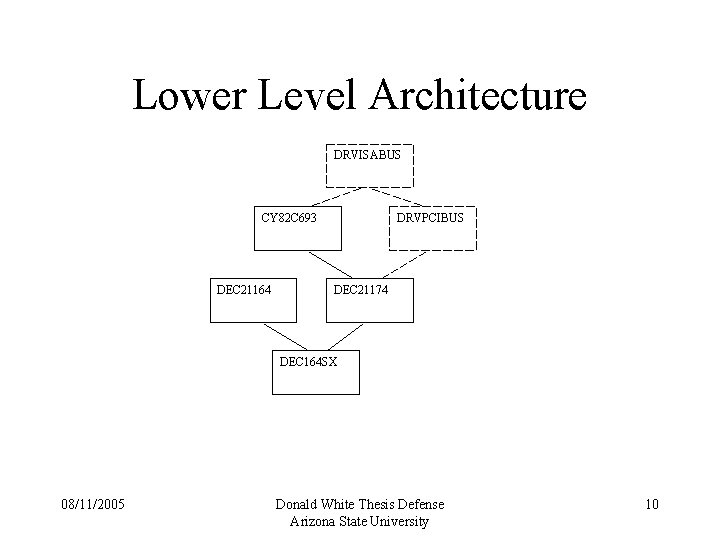

Lower Level Architecture • • Mainboard - DEC 164 SX Processor - DEC 21164 System Core Logic - DEC 21174 ISA Bus Controller - CY 82 C 693 08/11/2005 Donald White Thesis Defense Arizona State University 9

Lower Level Architecture DRVISABUS CY 82 C 693 DEC 21164 DRVPCIBUS DEC 21174 DEC 164 SX 08/11/2005 Donald White Thesis Defense Arizona State University 10

Lower Level Architecture • Mainboard Services – map_irq • Maps PCI device and function to system IRQ – map_irq_to_ipl • Maps system IRQ to interrupt priority level 08/11/2005 Donald White Thesis Defense Arizona State University 11

Lower Level Architecture • Processor Services – read_ICSR – write_ICSR – read_MCSR – write_MCSR – read_amask 08/11/2005 Donald White Thesis Defense Arizona State University 12

Lower Level Architecture • System Core Logic Services – start_timer – enable_irq – disable_irq – get_isa_interrupt – pci_cfg_io_setup – pci_cfg_io_status 08/11/2005 Donald White Thesis Defense Arizona State University 13

Lower Level Architecture • ISA Bus Controller Services – init 8259 as – enable_isa_irq – disable_isa_irq – ack_isa_irq – set_irq_trigger_mode 08/11/2005 Donald White Thesis Defense Arizona State University 14

Interrupt Processing Architecture • Interrupt as Synchronization Object – sparse three dimensional matrix <IPL, IRQ, GPD> – SOSInterrupt provides thread registration and deregistration services – PALCode provides thread blocking and unblocking 08/11/2005 Donald White Thesis Defense Arizona State University 15

Interrupt Processing Architecture • PALCode Services – block interrupt thread • • promotion block and demote block and switch demotion – schedule interrupt thread • dispatch of interrupt to appropriate thread – unblock interrupt thread • supports wakeup on time expiration 08/11/2005 Donald White Thesis Defense Arizona State University 16

Interrupt Processing Architecture • Interrupt Thread Models – Active Model • device driver loops blocking and servicing interrupts – Passive Model • device driver uses calling thread 08/11/2005 Donald White Thesis Defense Arizona State University 17

Interrupt Thread Architecture • Observations – May increase latency when interrupt thread also performs “bottom half” processing – Active model requires one thread per device – Passive model may have different threads for transmit and receive sides of a device – Multiplexed interrupts may require a demultiplexing software layer 08/11/2005 Donald White Thesis Defense Arizona State University 18

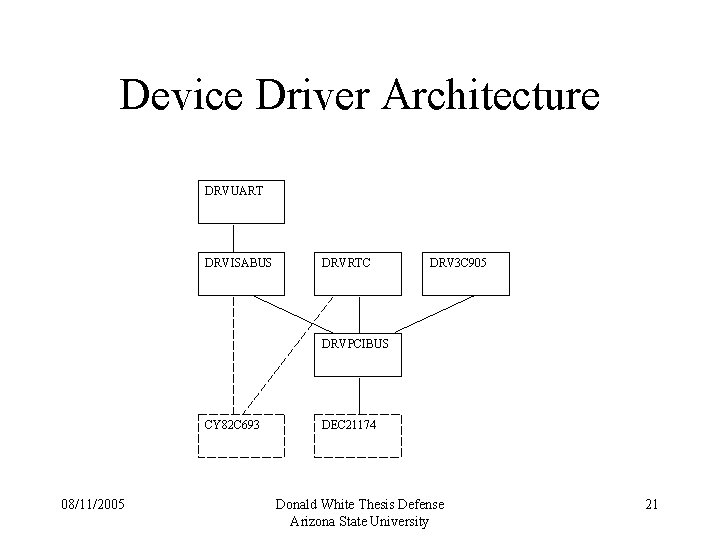

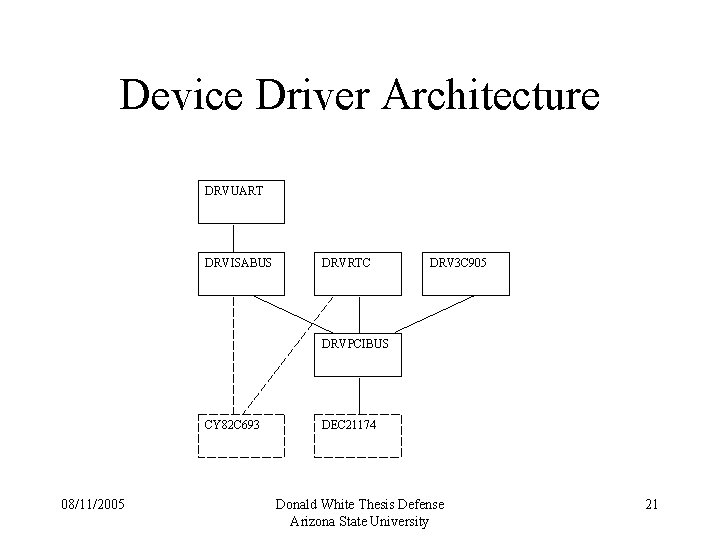

Device Driver Architecture • Infrastructure Objects – PCI Bus - DRVPCIBUS • • support for drivers for PCI bus attached devices uses system core logic services performs PCI enumeration validates device resource assignments – ISA Bus - DRVISABUS • support for drivers for ISA bus attached devices • uses PCI bus and ISA bus controller services 08/11/2005 Donald White Thesis Defense Arizona State University 19

Device Driver Architecture • Device Objects – Network Interface Card - DRV 3 C 905 • Ethernet interface – Real Time Clock - DRVRTC • provides wall-clock time – Serial Port - DRVUART • asynchronous character input and output 08/11/2005 Donald White Thesis Defense Arizona State University 20

Device Driver Architecture DRVUART DRVISABUS DRVRTC DRV 3 C 905 DRVPCIBUS CY 82 C 693 08/11/2005 DEC 21174 Donald White Thesis Defense Arizona State University 21

Device Driver Architecture • PCI Bus – Passive model driver – Services • reserve_device – transfers control of device to driver • PCI configuration address space access • PCI input-output address space access 08/11/2005 Donald White Thesis Defense Arizona State University 22

Device Driver Architecture • ISA Bus – Passive model driver • Demultiplexes ISA Interrupts • Handles ISA bus controller interactions – Services • register_isa_irq • unregister_isa_irq • wait_for_interrupt 08/11/2005 Donald White Thesis Defense Arizona State University 23

Device Driver Architecture • Network Interface Card – Passive model driver – Services • DRV 3 C 905 Send – waits for a free ring buffer if necessary – copies the contents of a buffer chain into a ring buffer • DRV 3 C 905 Receive – waits for a full ring buffer if necessary – copies the contents of a ring buffer into a buffer chain • Get. MACAddress – returns Ethernet address 08/11/2005 Donald White Thesis Defense Arizona State University 24

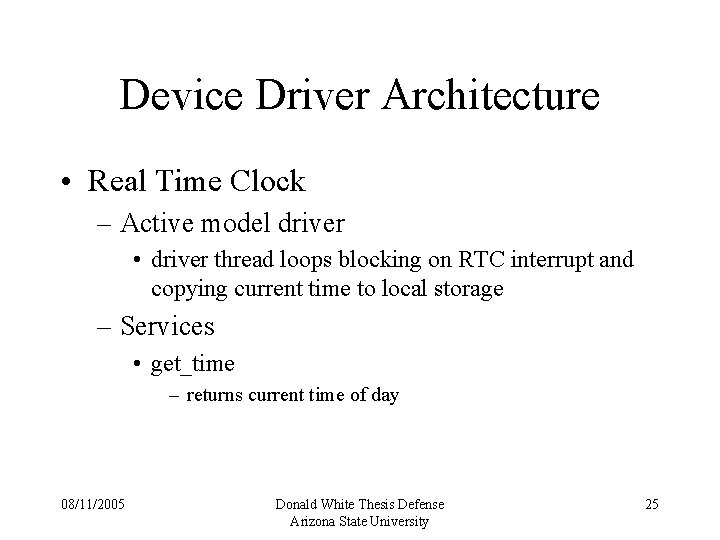

Device Driver Architecture • Real Time Clock – Active model driver • driver thread loops blocking on RTC interrupt and copying current time to local storage – Services • get_time – returns current time of day 08/11/2005 Donald White Thesis Defense Arizona State University 25

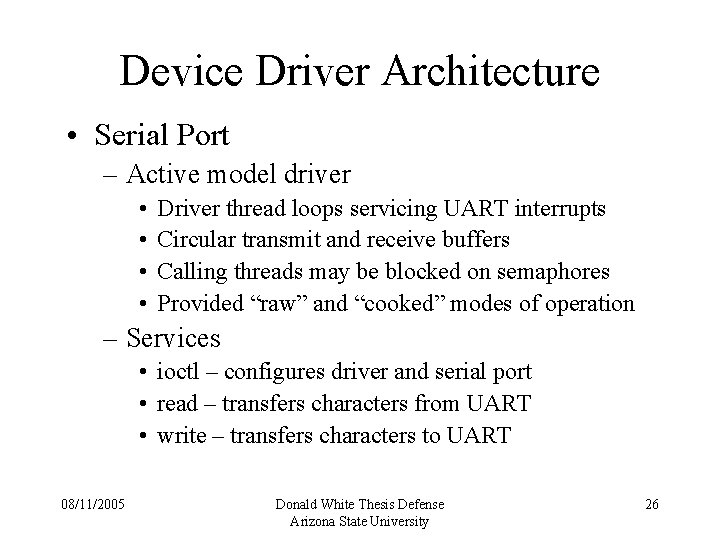

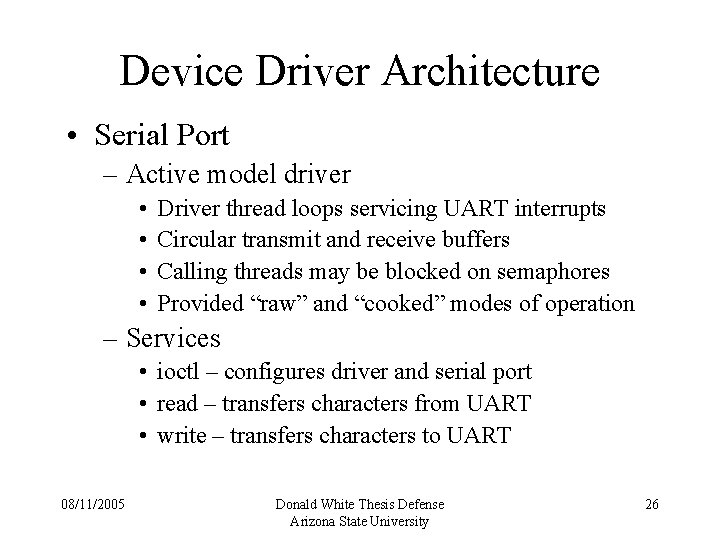

Device Driver Architecture • Serial Port – Active model driver • • Driver thread loops servicing UART interrupts Circular transmit and receive buffers Calling threads may be blocked on semaphores Provided “raw” and “cooked” modes of operation – Services • ioctl – configures driver and serial port • read – transfers characters from UART • write – transfers characters to UART 08/11/2005 Donald White Thesis Defense Arizona State University 26

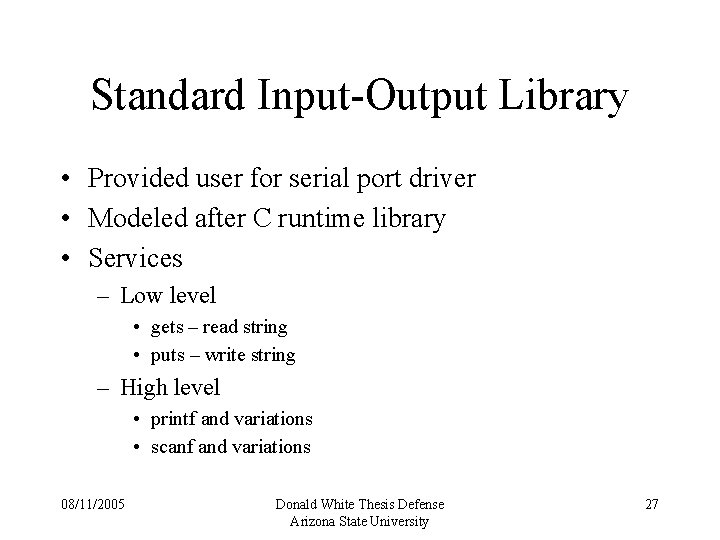

Standard Input-Output Library • Provided user for serial port driver • Modeled after C runtime library • Services – Low level • gets – read string • puts – write string – High level • printf and variations • scanf and variations 08/11/2005 Donald White Thesis Defense Arizona State University 27

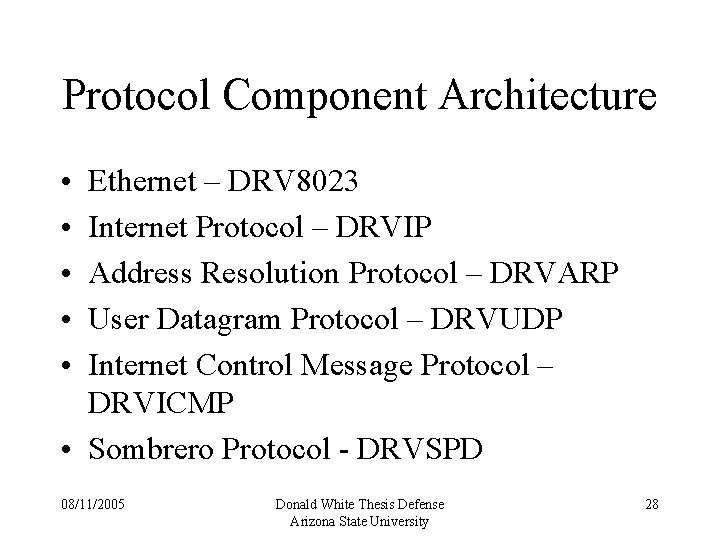

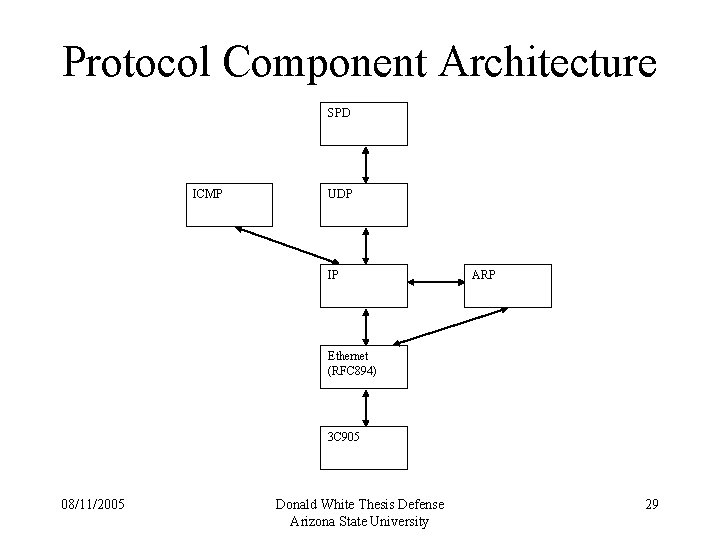

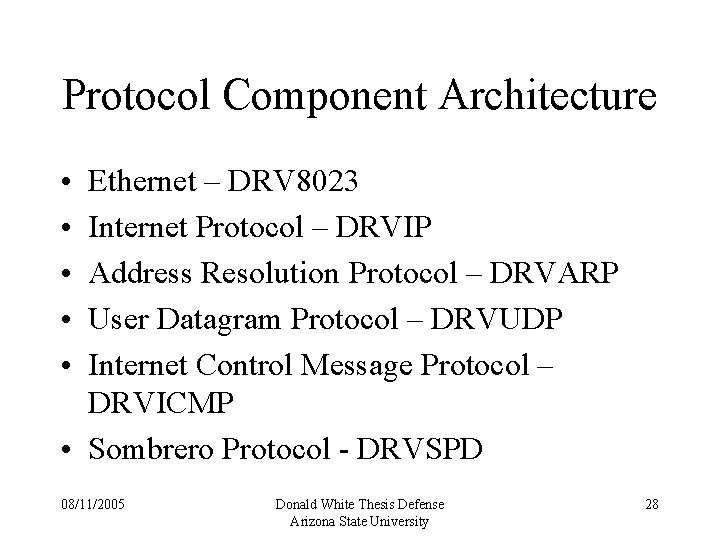

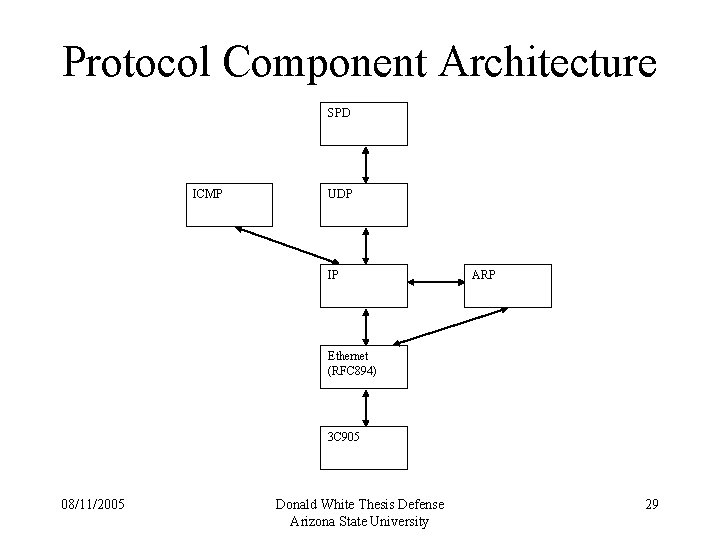

Protocol Component Architecture • • • Ethernet – DRV 8023 Internet Protocol – DRVIP Address Resolution Protocol – DRVARP User Datagram Protocol – DRVUDP Internet Control Message Protocol – DRVICMP • Sombrero Protocol - DRVSPD 08/11/2005 Donald White Thesis Defense Arizona State University 28

Protocol Component Architecture SPD ICMP UDP IP ARP Ethernet (RFC 894) 3 C 905 08/11/2005 Donald White Thesis Defense Arizona State University 29

Protocol Component Architecture • DRV 8023 – Passive Model Driver – Provides RFC 894 Ethernet framing – Services • Ether. Send – adds framing and calls lower layer • Ether. Recv – removes framing and based on frame type switches to correct thread and returns to appropriate higher layer • Get. Mac. Address – returns local Ethernet address 08/11/2005 Donald White Thesis Defense Arizona State University 30

Protocol Component Architecture • DRVIP – Passive model driver – Minimal Internet Protocol Implementation – Services • IPIn – adds packet header and calls lower layer • IPOut – removes header and based on protocol switches to correct thread and returns to appropriate higher layer 08/11/2005 Donald White Thesis Defense Arizona State University 31

Protocol Component Architecture • DRVARP – Active model driver • daemon thread started during protocol stack initialization • responds to ARP requests – Services • Net. MACLookup – returns Ethernet address corresponding to an IP address – generates ARP request if necessary 08/11/2005 Donald White Thesis Defense Arizona State University 32

Protocol Component Architecture • DRVUDP – Passive model driver – Minimal User Datagram Protocol implementation – Services • UDPIn – adds datagram header and calls lower layer • UDPOut – removes datagram header and based on destination port switches to correct thread and returns to appropriate higher layer 08/11/2005 Donald White Thesis Defense Arizona State University 33

Protocol Component Architecture • DRVICMP – Active model driver • daemon thread started during protocol stack initialization • responds to echo requests (pings) – Services • none 08/11/2005 Donald White Thesis Defense Arizona State University 34

Protocol Component Architecture • DRVSPD – Passive model driver – Implements Sombrero protocols for communication with host system 08/11/2005 Donald White Thesis Defense Arizona State University 35

Protocol Component Architecture – Services • Msg. To. Host – adds message header and calls lower layer output service – calls lower layer input service to receive acknowledgement • Wait. For. Msg. From. Host – allocates message header buffer and calls lower layer input service – sends acknowledgement • Msg. From. Host. Timer • Data. To. Host • Data. From. Host 08/11/2005 Donald White Thesis Defense Arizona State University 36

Sombrero Protocol Description • Protocol stack assembly – Components register with SOSBroker during system construction – Components resolve dependencies during system initialization 08/11/2005 Donald White Thesis Defense Arizona State University 37

Sombrero Protocol Description • Message protocol – Transparent transfer of messages up to 1024 octets – Stop-and-wait protocol – Acknowledgement timer to trigger retransmission 08/11/2005 Donald White Thesis Defense Arizona State University 38

Sombrero Protocol Description • Burst protocol – Transparent transfer of large virtual address regions – Retransmit-N protocol – 8 megabyte bursts of up to 8192 fragments containing up to 1024 octets – Acknowledgement bitmap following burst 08/11/2005 Donald White Thesis Defense Arizona State University 39

Sombrero Protocol Description • Evaluation – Send side of protocol stack realized Sombrero potential for reduced context switching through use of passive service model – Receive side of protocol stack showed degraded performance after addition of ARP and ICMP components due to increased thread switching and data movement 08/11/2005 Donald White Thesis Defense Arizona State University 40

Sombrero Protocol Description • Evaluation continued – Observations of equilibrium condition during which message transfers fail to progress • Receiving thread cannot get control at appropriate layer before desired message is discarded – Implementation weaknesses • potential buffer overflow in burst protocol • data leakage between threads • unnecessary data movement 08/11/2005 Donald White Thesis Defense Arizona State University 41

Contributions and Conclusions • Provided future researchers with an improved development environment • Documented previously undocumented features of Sombrero design and implementation • Provided a lower-level architecture implementation for Sombrero • Demonstrated successful application of Sombrero interrupt processing architecture • Identified architectural weaknesses in Sombrero protocol stack 08/11/2005 Donald White Thesis Defense Arizona State University 42

Future Work • • • Preliminary loader using DHCP and TFTP Minimally intrusive trace facility Cross platform development tools Add PALCode Validity Checker to toolkit Object representation of physical memory ATA over Ethernet client driver to support persistent storage 08/11/2005 Donald White Thesis Defense Arizona State University 43