Implementation of a Low Leakage Standard Cell Library

Implementation of a Low Leakage Standard Cell Library based on materials from UMC 65 nm technology Theodoros Simopoulos Comp. Engineering & Informatics University of Patras Greece Themistokles Haniotakis Comp. Engineering & Informatics University of Patras Greece George Alexiou Comp. Engineering & Informatics University of Patras Greece simopoulos@ceid. upatras. gr haniotak@ceid. upatras. gr alexiou@ceid. upatras. gr

CEID STD LIB There are others Reasons to implement a Standard Cell Library 1. To have the know how 2. To alter the layout 3. Able to implement custom cells

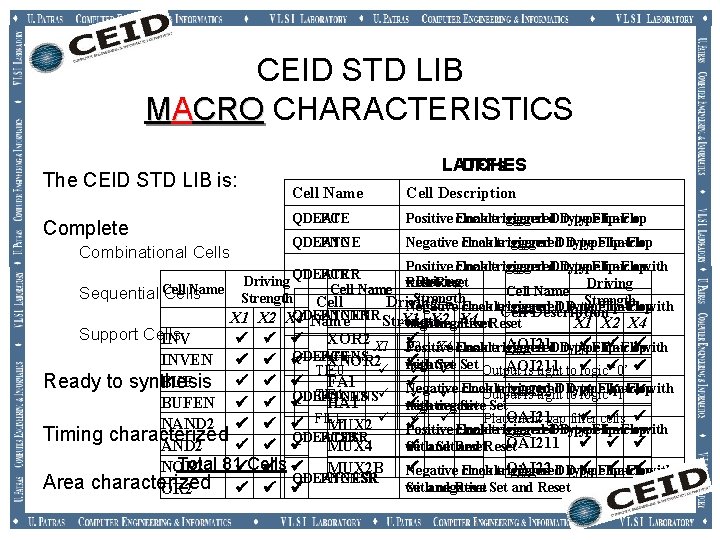

CEID STD LIB MACRO CHARACTERISTICS The CEID STD LIB is: Complete Combinational Cells LATCHES DFFs Cell Name Cell Description QDLATE QDFFC Positive clock Enable triggered DD type Flip-Flop Latch QDLATNE QDFFNC Negative clock Enable triggered DD type Flip-Flop Latch Positive clock Enable triggered DD type Flip-Flop Latch with QDFFCR QDLATER Driving Reset Driving Name Cell Name with Cell Name Sequential Cells Strength Cell Driving Negative clock Enable triggered DD type Flip-Flop Latch with Cell Description QDLATNENR QDFFNCNR X 1 X 2 X 4 Name X 1 X 2 X 4 Strength X 1 X 2 X 4 negative with negative Reset Support Cells INV ü ü ü XOR 2 X 1 QDLATENS QDFFCS INVEN ü ü ü XNOR 2 TIE 0 ü BUF ü ü ü FA 1 Ready to synthesis TIE 1 ü QDLATNENS QDFFNCNS BUFEN ü ü ü HA 1 NAND 2 ü ü ü FILL MUX 2 ü Timing characterized QDLATESR QDFFCSR AND 2 ü ü ü MUX 4 Total 81üCells NOR 2 ü ü MUX 2 B QDLATNESR QDFFNCNSR Area characterized OR 2 ü ü AOI 21 D Dtype ü Flip-Flop ü üwith X 2 X 4 clock Positive Enable triggered type Latch ü negative with AOI 211 is tight to ü logicü‘ 0’ ü ü Set Output ü Negative Enable triggered DD type Flip-Flop Latch AOI 22 ü ü Output is tight to logic ‘ 1’ ü with ü ü clock ü negative with negative Set OAI 21 gap filler ü cells ü ü Placement ü ü ü Positive clock Enable triggered DD type Flip-Flop Latch with OAI 211 ü ü ü Set and with Set. Reset and Reset ü OAI 22 ü ü ü with ü Negative clock Enable triggered DD type Flip-Flop Latch Set and with negative Reset Set and Reset

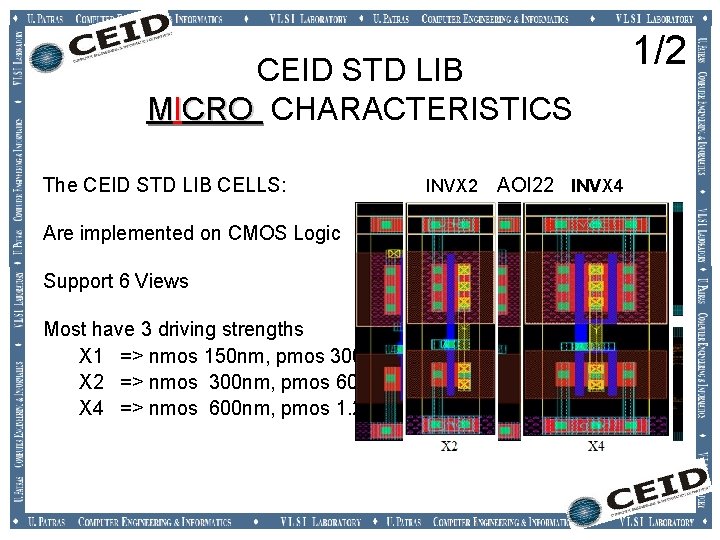

CEID STD LIB MICRO CHARACTERISTICS The CEID STD LIB CELLS: Are implemented on CMOS Logic Support 6 Views Most have 3 driving strengths X 1 => nmos 150 nm, pmos 300 nm X 2 => nmos 300 nm, pmos 600 nm X 4 => nmos 600 nm, pmos 1. 2 um INVX 2 INVX 4 AOI 22 INV X 1 1/2

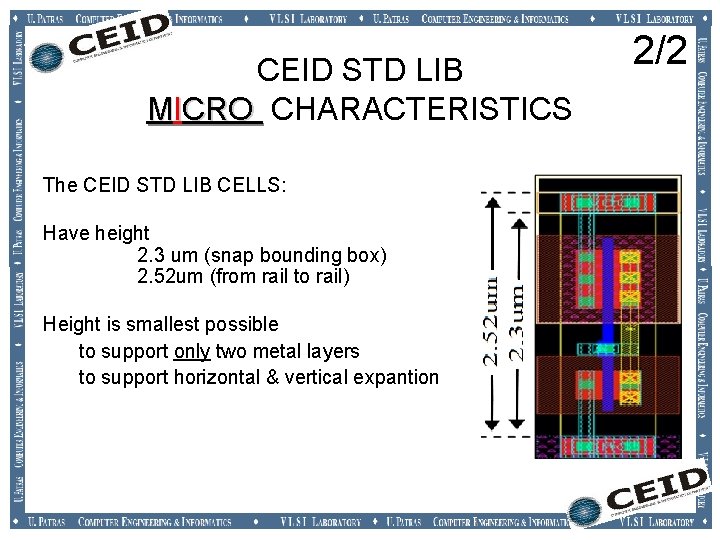

CEID STD LIB MICRO CHARACTERISTICS The CEID STD LIB CELLS: Have height 2. 3 um (snap bounding box) 2. 52 um (from rail to rail) Height is smallest possible to support only two metal layers to support horizontal & vertical expantion 2/2

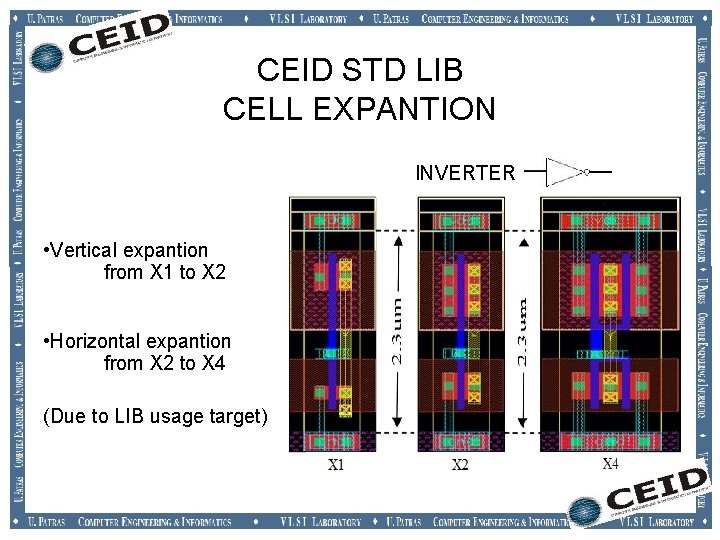

CEID STD LIB CELL EXPANTION INVERTER • Vertical expantion from X 1 to X 2 • Horizontal expantion from X 2 to X 4 (Due to LIB usage target)

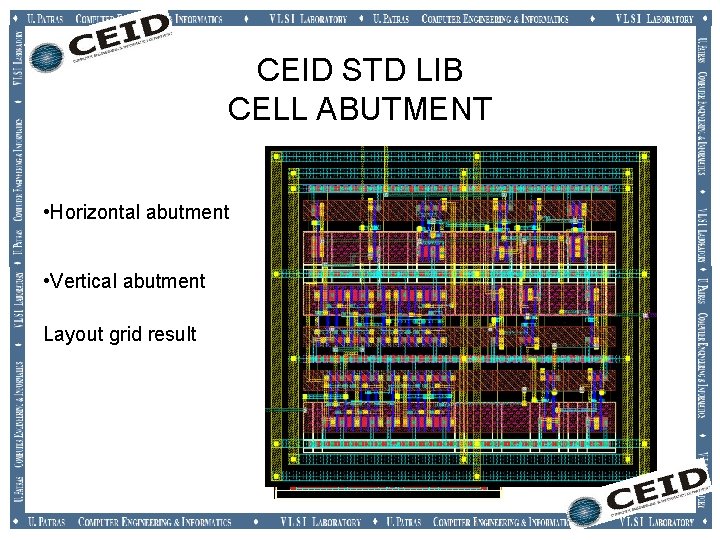

CEID STD LIB CELL ABUTMENT • Horizontal abutment • Vertical abutment Layout grid result 0. 14 um (1 pitch = 28 nm)

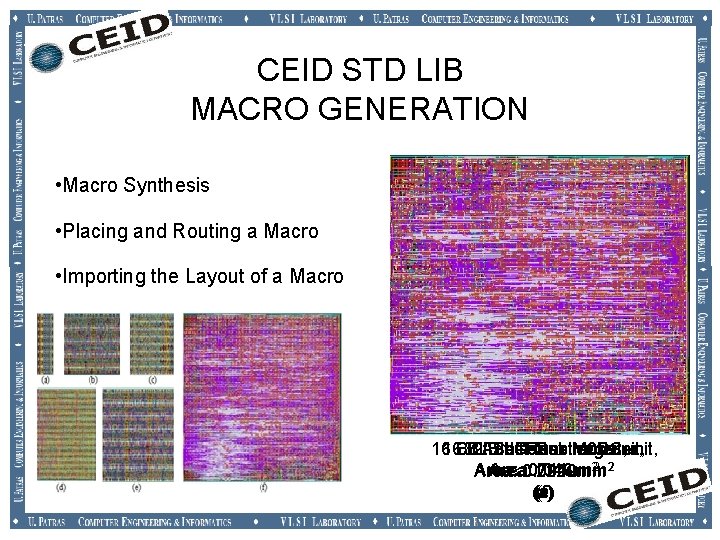

CEID STD LIB MACRO GENERATION • Macro Synthesis • Placing and Routing a Macro • Importing the Layout of a Macro 1616 Bit unit, 32 Bit Cortex M 0 DS, Shift functions unit, Bit. Adder-Subtracter Set-Reset register, 22 2 744 um 0. 046 mm Area: 0. 0012 mm 222 um (c) (f) (e) (a)

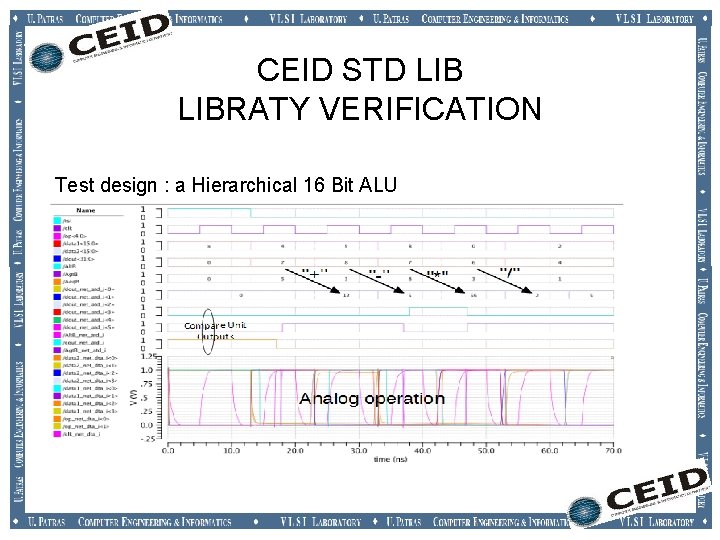

CEID STD LIBRATY VERIFICATION Test design : a Hierarchical 16 Bit ALU

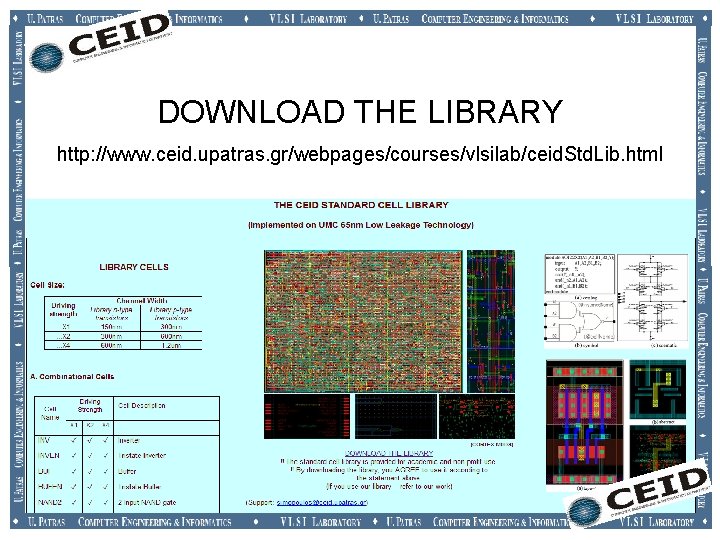

DOWNLOAD THE LIBRARY http: //www. ceid. upatras. gr/webpages/courses/vlsilab/ceid. Std. Lib. html

OUR FUTURE WORK 1. Second Variation • Cells expands only horizontaly • More metal levels inserted • v 2 Lib targets projects 2. A Memory Library is on the way (First results are estimated)

- Slides: 11