Implementation Example DSP based Adaptive Array Antenna System

Implementation Example - DSP based Adaptive Array Antenna System Fire Tom Wada Professor, Information Engineering, Univ. of the Ryukyus 9/13/2021 System Arch 2007 (Fire Tom Wada) 1

DSP based Adaptive Array Antenna System n n DSP based AAA System for OFDM receiver is shown as a implementation example. The System is composed of three parts. 1. 2. 3. 9/13/2021 OFDM demodulator Adaptive Array Antenna DSP System Arch 2007 (Fire Tom Wada) 2

OUTLINE 1. 2. 3. 4. ISDB-T abstract OFDM demodulator Adaptive Array Antenna System Design 9/13/2021 System Arch 2007 (Fire Tom Wada) 3

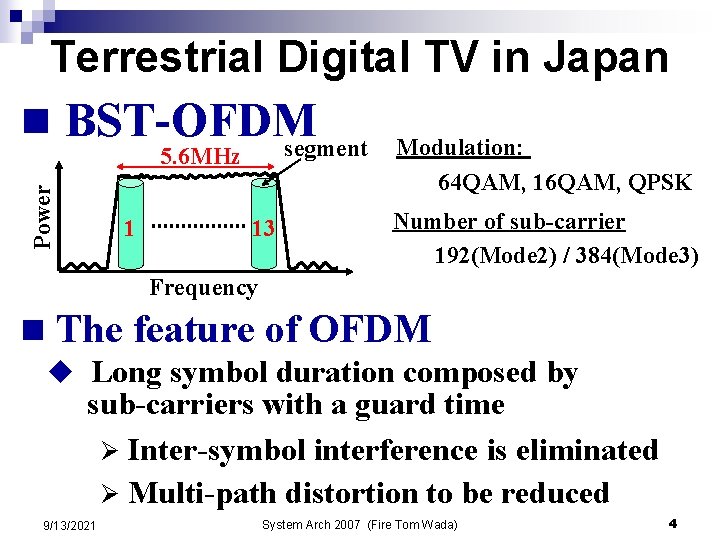

Terrestrial Digital TV in Japan n BST-OFDM segment Power 5. 6 MHz 1 13 Modulation: 64 QAM, 16 QAM, QPSK Number of sub-carrier 192(Mode 2) / 384(Mode 3) Frequency n The feature of OFDM u Long symbol duration composed by sub-carriers with a guard time Ø Inter-symbol interference is eliminated Ø Multi-path distortion to be reduced 9/13/2021 System Arch 2007 (Fire Tom Wada) 4

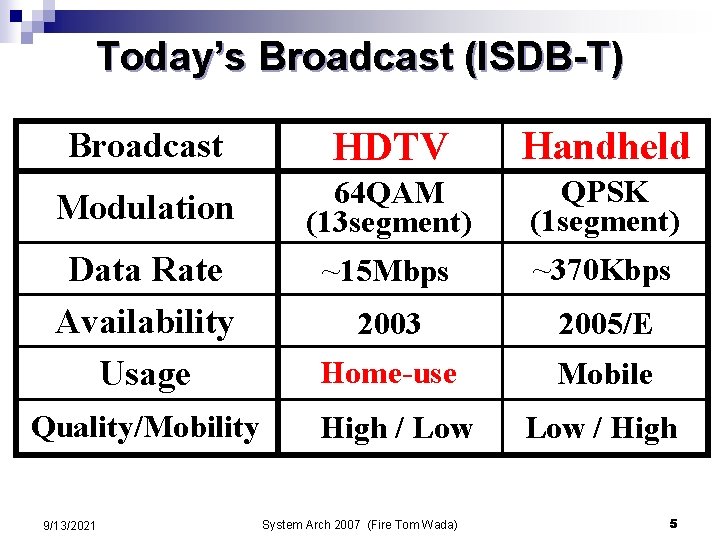

Today’s Broadcast (ISDB-T) Broadcast HDTV Handheld Modulation 64 QAM (13 segment) QPSK (1 segment) Data Rate Availability Usage ~15 Mbps ~370 Kbps 2003 2005/E Home-use Mobile Quality/Mobility High / Low / High 9/13/2021 System Arch 2007 (Fire Tom Wada) 5

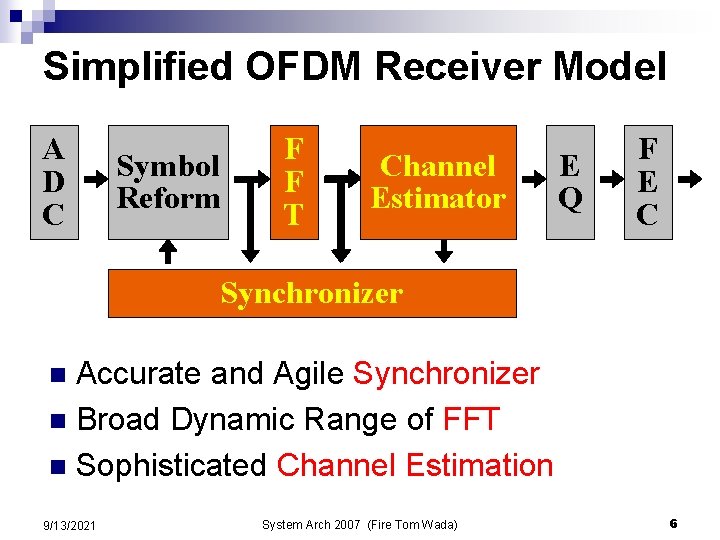

Simplified OFDM Receiver Model A D C Symbol Reform F F T Channel Estimator E Q F E C Synchronizer Accurate and Agile Synchronizer n Broad Dynamic Range of FFT n Sophisticated Channel Estimation n 9/13/2021 System Arch 2007 (Fire Tom Wada) 6

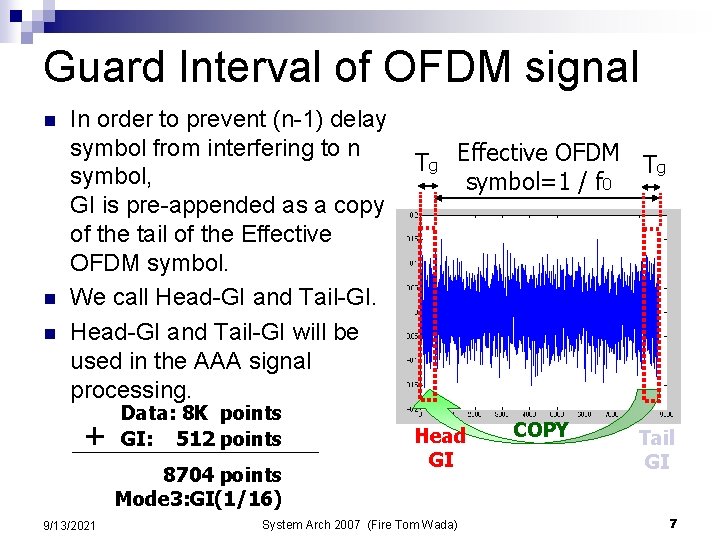

Guard Interval of OFDM signal n n n In order to prevent (n-1) delay symbol from interfering to n symbol, GI is pre-appended as a copy of the tail of the Effective OFDM symbol. We call Head-GI and Tail-GI will be used in the AAA signal processing. + Data: 8 K points GI: 512 points 8704 points Mode 3: GI(1/16) 9/13/2021 Tg Effective OFDM Tg symbol=1 / f 0 Head GI System Arch 2007 (Fire Tom Wada) COPY Tail GI 7

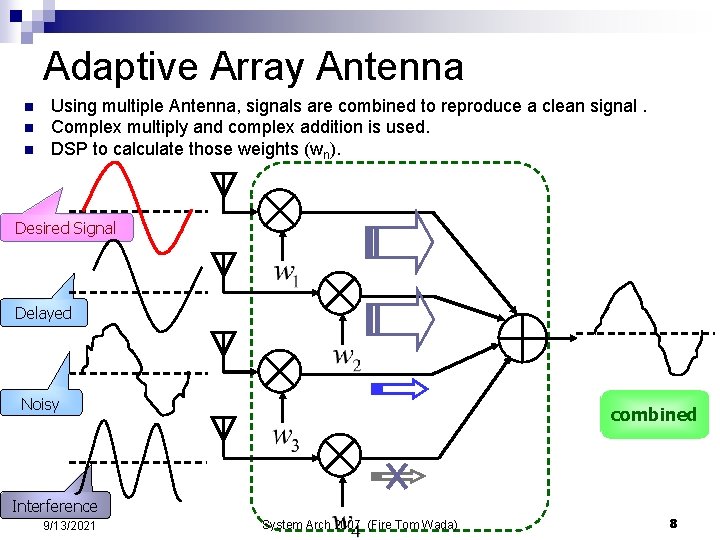

Adaptive Array Antenna n n n Using multiple Antenna, signals are combined to reproduce a clean signal. Complex multiply and complex addition is used. DSP to calculate those weights (wn). Desired Signal Delayed ? Noisy combined Interference 9/13/2021 System Arch 2007 (Fire Tom Wada) 8

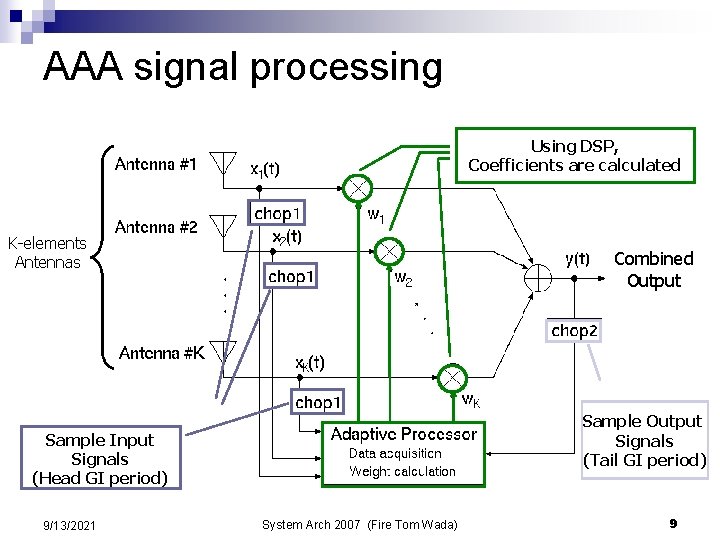

AAA signal processing Using DSP, Coefficients are calculated K-elements Antennas Combined Output Sample Output Signals (Tail GI period) Sample Input Signals (Head GI period) 9/13/2021 System Arch 2007 (Fire Tom Wada) 9

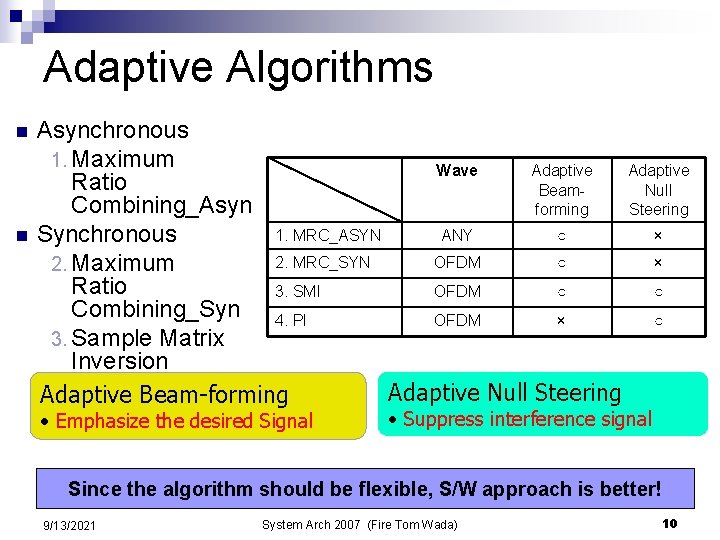

Adaptive Algorithms n n Asynchronous 1. Maximum Wave Adaptive Ratio Beam. Null Combining_Asyn forming Steering 1. MRC_ASYN ANY ○ × Synchronous 2. MRC_SYN OFDM ○ × 2. Maximum Ratio 3. SMI OFDM ○ ○ Combining_Syn 4. PI OFDM × ○ 3. Sample Matrix Inversion 4. Power. Beam-forming Adaptive Null Steering Adaptive Inversion • Suppress interference signal • Emphasize the desired Signal Since the algorithm should be flexible, S/W approach is better! 9/13/2021 System Arch 2007 (Fire Tom Wada) 10

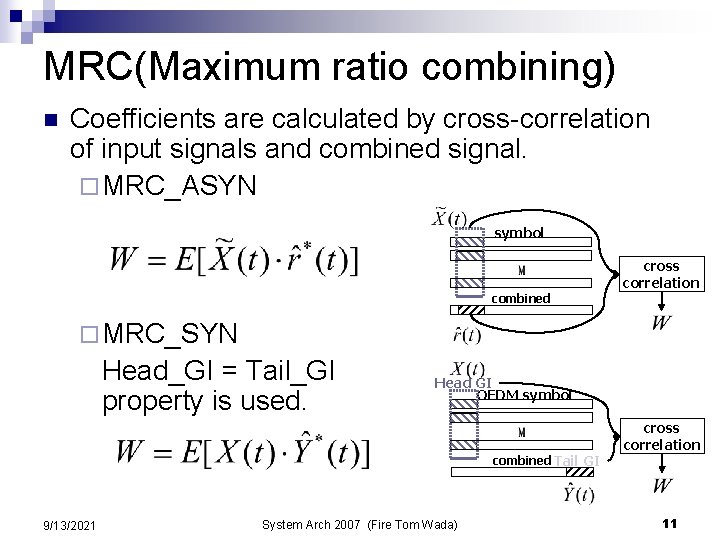

MRC(Maximum ratio combining) n Coefficients are calculated by cross-correlation of input signals and combined signal. ¨ MRC_ASYN symbol combined cross correlation ¨ MRC_SYN Head_GI = Tail_GI property is used. Head GI OFDM symbol combined Tail GI 9/13/2021 System Arch 2007 (Fire Tom Wada) cross correlation 11

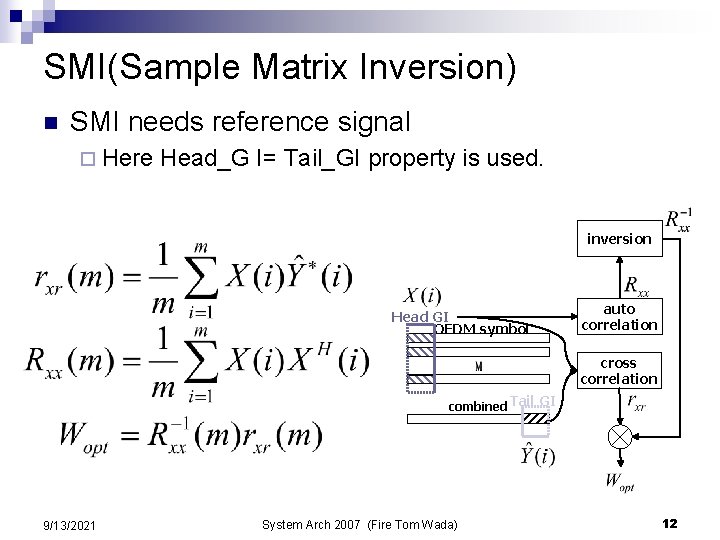

SMI(Sample Matrix Inversion) n SMI needs reference signal ¨ Here Head_G I= Tail_GI property is used. inversion Head GI OFDM symbol auto correlation cross correlation combined Tail GI 9/13/2021 System Arch 2007 (Fire Tom Wada) 12

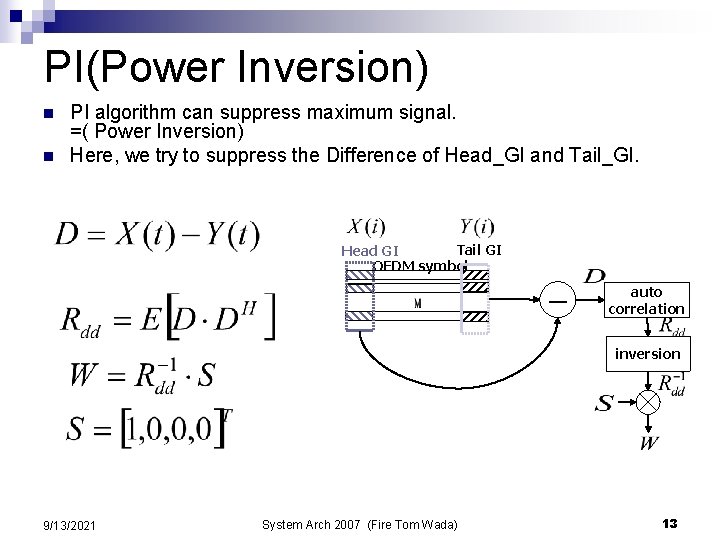

PI(Power Inversion) n n PI algorithm can suppress maximum signal. =( Power Inversion) Here, we try to suppress the Difference of Head_GI and Tail_GI. Tail GI Head GI OFDM symbol - auto correlation inversion 9/13/2021 System Arch 2007 (Fire Tom Wada) 13

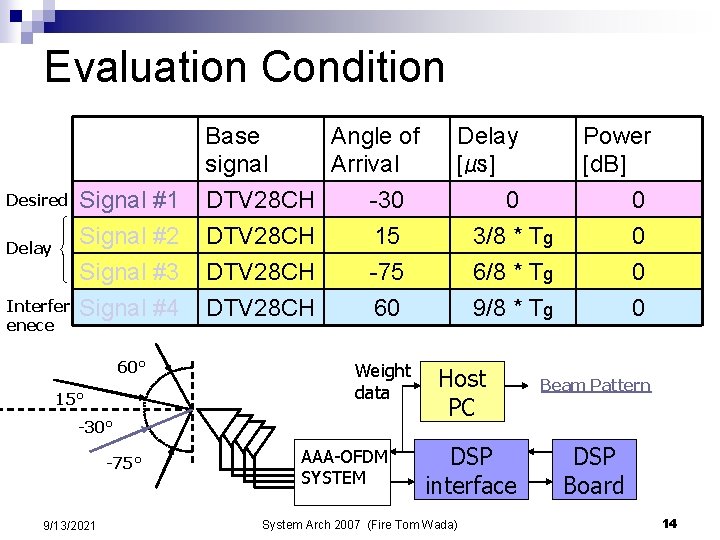

Evaluation Condition Desired Delay Interfer enece Signal #1 Signal #2 Signal #3 Signal #4 60° 15° Base Angle of signal Arrival DTV 28 CH -30 DTV 28 CH 15 DTV 28 CH -75 DTV 28 CH 60 Weight data -30° -75° 9/13/2021 AAA-OFDM SYSTEM Delay [㎲] 0 3/8 * Tg 6/8 * Tg 9/8 * Tg Host PC DSP interface System Arch 2007 (Fire Tom Wada) Power [d. B] 0 0 Beam Pattern DSP Board 14

![MATLAB Simulation [MRC_ASYN, MRC_SYN)] Adaptive Beam-forming MRC_ASYN 9/13/2021 MRC_SYN System Arch 2007 (Fire Tom MATLAB Simulation [MRC_ASYN, MRC_SYN)] Adaptive Beam-forming MRC_ASYN 9/13/2021 MRC_SYN System Arch 2007 (Fire Tom](http://slidetodoc.com/presentation_image_h2/a444ffddc4e65ec3a2956709dd020160/image-15.jpg)

MATLAB Simulation [MRC_ASYN, MRC_SYN)] Adaptive Beam-forming MRC_ASYN 9/13/2021 MRC_SYN System Arch 2007 (Fire Tom Wada) 15

![MATLAB Simulation [SMI, PI] Adaptive Beam-forming Adaptive Null Steering SMI 9/13/2021 PI System Arch MATLAB Simulation [SMI, PI] Adaptive Beam-forming Adaptive Null Steering SMI 9/13/2021 PI System Arch](http://slidetodoc.com/presentation_image_h2/a444ffddc4e65ec3a2956709dd020160/image-16.jpg)

MATLAB Simulation [SMI, PI] Adaptive Beam-forming Adaptive Null Steering SMI 9/13/2021 PI System Arch 2007 (Fire Tom Wada) 16

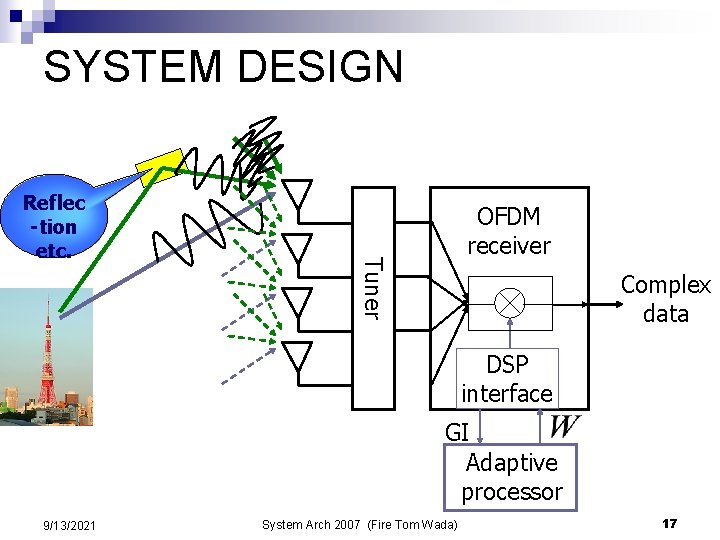

SYSTEM DESIGN OFDM receiver Tuner Reflec -tion etc. Complex data DSP interface GI Adaptive processor 9/13/2021 System Arch 2007 (Fire Tom Wada) 17

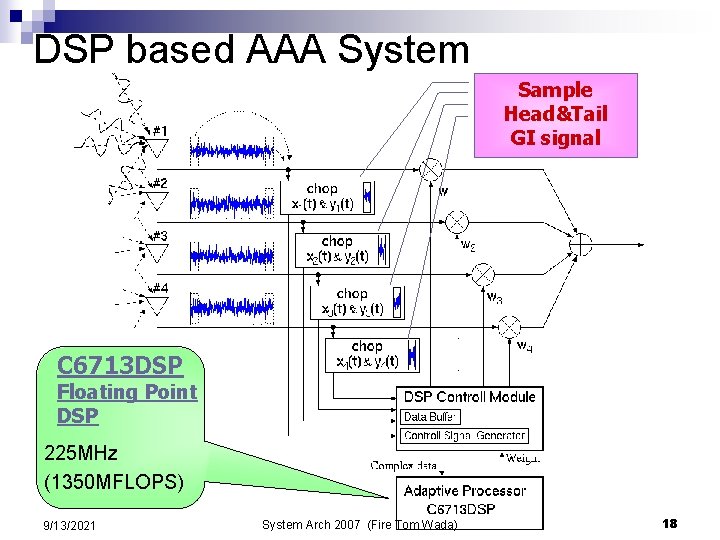

DSP based AAA System Sample Head&Tail GI signal C 6713 DSP Floating Point DSP 225 MHz (1350 MFLOPS) 9/13/2021 System Arch 2007 (Fire Tom Wada) 18

![TMS 320 C 6713 DSP [Texas Instruments Inc, Floating point DSP] 512 points * TMS 320 C 6713 DSP [Texas Instruments Inc, Floating point DSP] 512 points *](http://slidetodoc.com/presentation_image_h2/a444ffddc4e65ec3a2956709dd020160/image-19.jpg)

TMS 320 C 6713 DSP [Texas Instruments Inc, Floating point DSP] 512 points * 4 branches C 6713 DSP n n Head GI 225 MHz (1350 MFLOPS) Internal Memory Tail GI EMIF Program Area: 4 KB Data Area: 4 KB SRAM: 192 KB Peripheral n n 32 bit EMIF GPIO 9/13/2021 Host PC System Arch 2007 (Fire Tom Wada) GPIO EXT_HWI[1 -3] DSP_RUN DSP_VALID 19

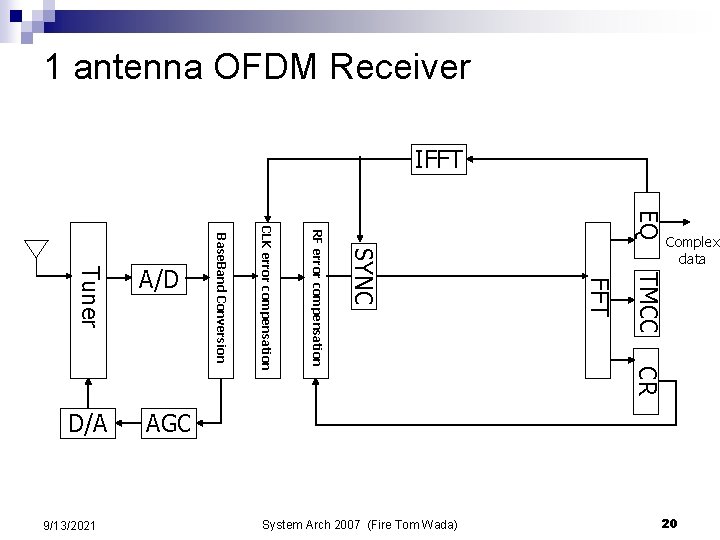

1 antenna OFDM Receiver IFFT EQ TMCC FFT SYNC CR RF error compensation CLK error compensation 9/13/2021 Base. Band Conversion Tuner D/A A/D Complex data AGC System Arch 2007 (Fire Tom Wada) 20

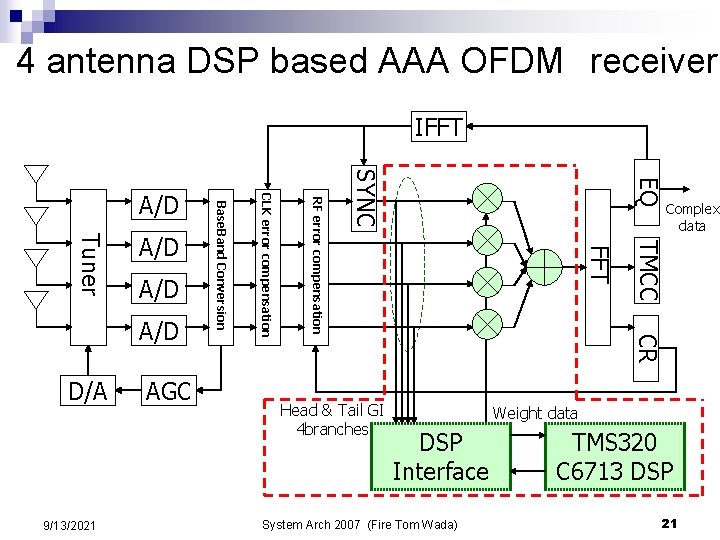

4 antenna DSP based AAA OFDM receiver IFFT Complex data TMCC CR Head & Tail GI 4 branches EQ 9/13/2021 AGC FFT D/A SYNC A/D RF error compensation A/D CLK error compensation Tuner A/D Base. Band Conversion A/D Weight data DSP Interface System Arch 2007 (Fire Tom Wada) TMS 320 C 6713 DSP 21

![DSP Interface From 4 Branch Signal To Weight Y 0 C[0: 511] Y 1 DSP Interface From 4 Branch Signal To Weight Y 0 C[0: 511] Y 1](http://slidetodoc.com/presentation_image_h2/a444ffddc4e65ec3a2956709dd020160/image-22.jpg)

DSP Interface From 4 Branch Signal To Weight Y 0 C[0: 511] Y 1 C[0: 511] Y 2 C[0: 511] Y 3 C[0: 511] BRAMC 8 kw x 32 b Buffer RAM Write Data Logic Parameter 4 w x 32 b FF 4 w x 32 b Signal Transfer Logic DSP Board CE 2 SDRAM (option) GP_IO CE 1 FLASH CLK 9/13/2021 DSP Controll Logic RESET EXTHWI 1 -3 Bk. Sel 2 VALID DSP_RUN DSP interface System Arch 2007 (Fire Tom Wada) TI DSP C 6713 LED DIP 22

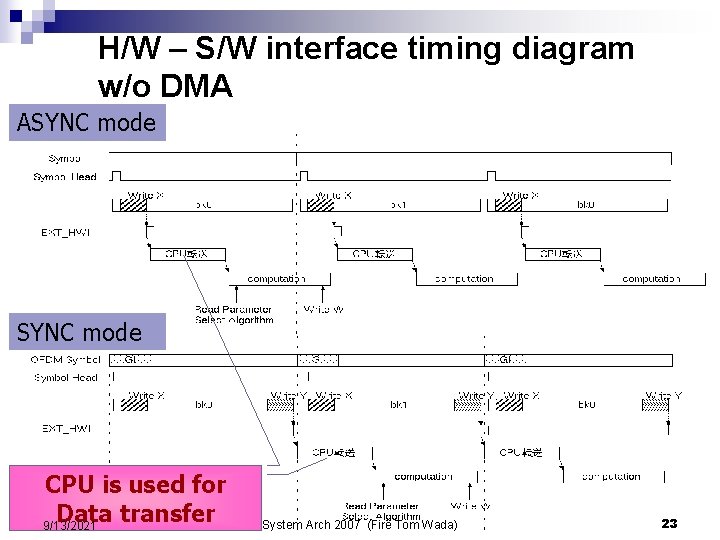

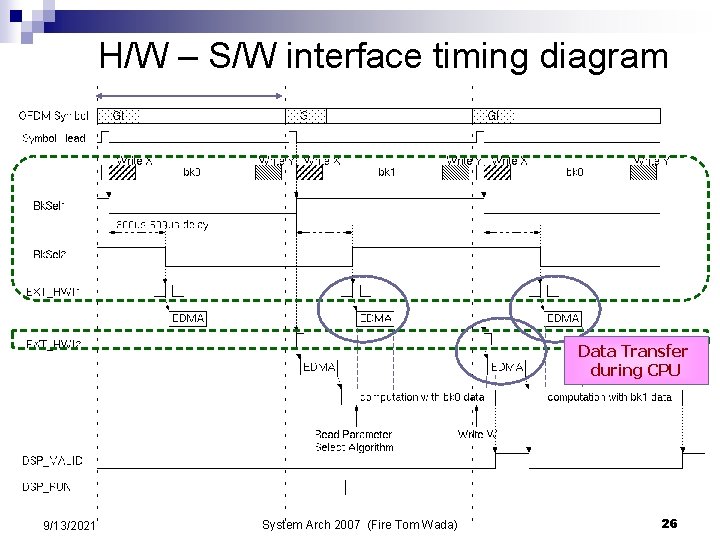

H/W – S/W interface timing diagram w/o DMA ASYNC mode CPU is used for Data transfer 9/13/2021 System Arch 2007 (Fire Tom Wada) 23

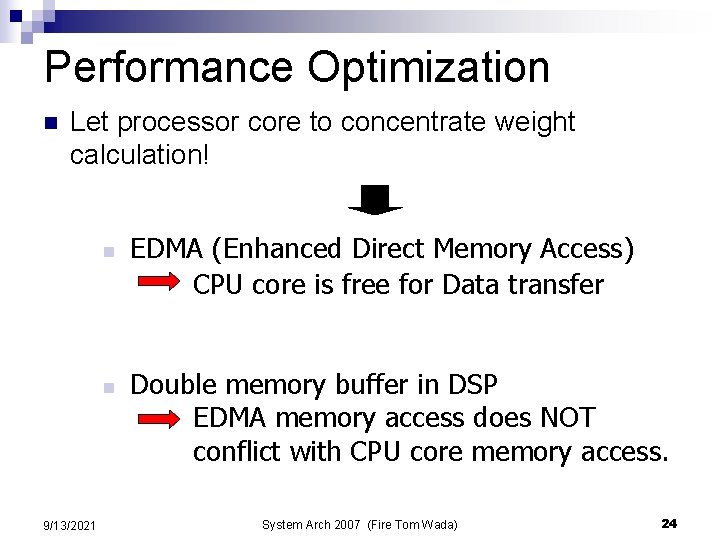

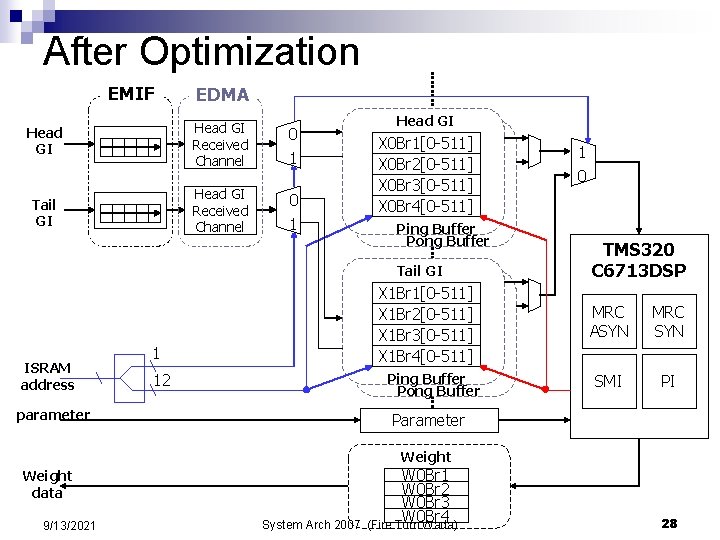

Performance Optimization n Let processor core to concentrate weight calculation! n n 9/13/2021 EDMA (Enhanced Direct Memory Access) CPU core is free for Data transfer Double memory buffer in DSP EDMA memory access does NOT conflict with CPU core memory access. System Arch 2007 (Fire Tom Wada) 24

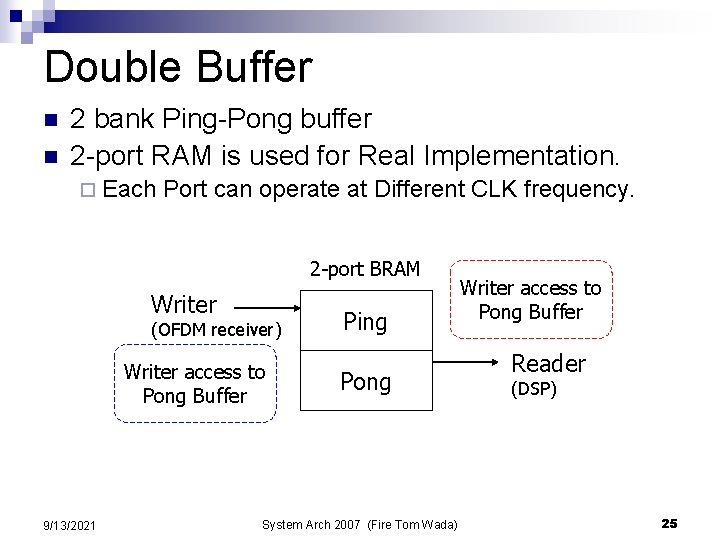

Double Buffer n n 2 bank Ping-Pong buffer 2 -port RAM is used for Real Implementation. ¨ Each Port can operate at Different CLK frequency. 2 -port BRAM Writer (OFDM receiver) Writer access to Pong Buffer 9/13/2021 Ping Pong System Arch 2007 (Fire Tom Wada) Writer access to Pong Buffer Reader (DSP) 25

H/W – S/W interface timing diagram Data Transfer during CPU 9/13/2021 System Arch 2007 (Fire Tom Wada) 26

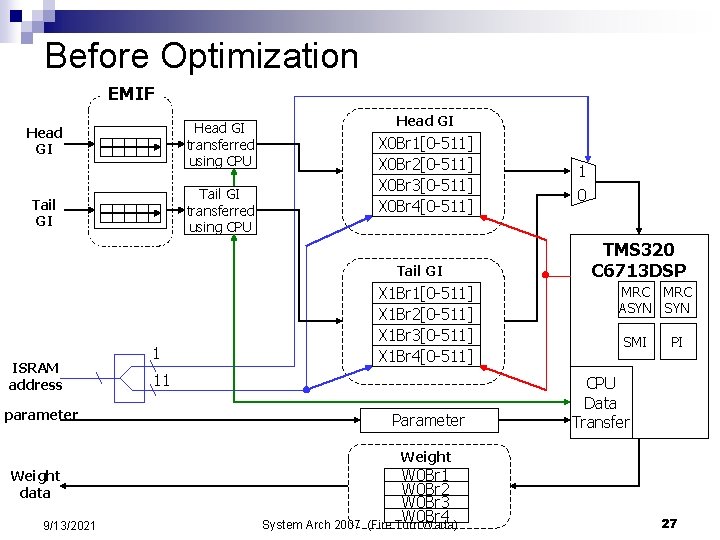

Before Optimization EMIF Head GI transferred using CPU Head GI X 0 Br 1[0 -511] X 0 Br 2[0 -511] X 0 Br 3[0 -511] X 0 Br 4[0 -511] Tail GI transferred using CPU Tail GI ISRAM address X 1 Br 1[0 -511] X 1 Br 2[0 -511] X 1 Br 3[0 -511] X 1 Br 4[0 -511] 1 11 parameter Parameter 1 0 TMS 320 C 6713 DSP MRC ASYN SMI PI CPU Data Transfer Weight data 9/13/2021 System Arch 2007 W 0 Br 1 W 0 Br 2 W 0 Br 3 W 0 Br 4 (Fire Tom Wada) 27

After Optimization EMIF EDMA Head GI Received Channel 0 Tail GI Head GI Received Channel 0 1 1 Head GI X 0 Br 1[0 -511] X 0 Br 2[0 -511] X 0 Br 3[0 -511] X 0 Br 4[0 -511] Ping Buffer Pong Buffer Tail GI ISRAM address X 1 Br 1[0 -511] X 1 Br 2[0 -511] X 1 Br 3[0 -511] X 1 Br 4[0 -511] 1 12 Ping Buffer Pong Buffer parameter 1 0 TMS 320 C 6713 DSP MRC ASYN MRC SYN SMI PI Parameter Weight data 9/13/2021 System Arch 2007 W 0 Br 1 W 0 Br 2 W 0 Br 3 W 0 Br 4 (Fire Tom Wada) 28

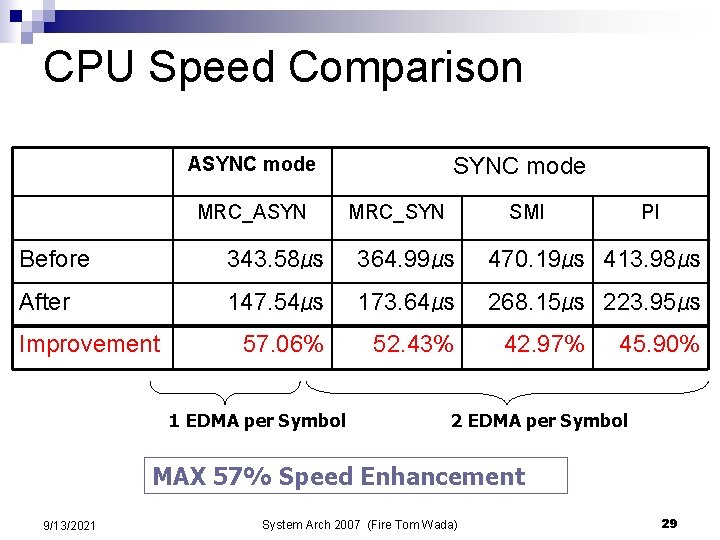

CPU Speed Comparison ASYNC mode MRC_ASYN SYNC mode MRC_SYN SMI PI Before 343. 58㎲ 364. 99㎲ 470. 19㎲ 413. 98㎲ After 147. 54㎲ 173. 64㎲ 268. 15㎲ 223. 95㎲ 57. 06% 52. 43% Improvement 1 EDMA per Symbol 42. 97% 45. 90% 2 EDMA per Symbol MAX 57% Speed Enhancement 9/13/2021 System Arch 2007 (Fire Tom Wada) 29

![Measured Results [MRC_ASYN, MRC_SYN)] MRC_ASYN方式 BER: 1. 30 E-02 9/13/2021 MRC_SYN方式 BER: 4. 3 Measured Results [MRC_ASYN, MRC_SYN)] MRC_ASYN方式 BER: 1. 30 E-02 9/13/2021 MRC_SYN方式 BER: 4. 3](http://slidetodoc.com/presentation_image_h2/a444ffddc4e65ec3a2956709dd020160/image-30.jpg)

Measured Results [MRC_ASYN, MRC_SYN)] MRC_ASYN方式 BER: 1. 30 E-02 9/13/2021 MRC_SYN方式 BER: 4. 3 E-03 System Arch 2007 (Fire Tom Wada) 30

![Measured Results [SMI, PI] SMI方式 BER: 6. 60 E-03 9/13/2021 PI方式 BER: 2. 40 Measured Results [SMI, PI] SMI方式 BER: 6. 60 E-03 9/13/2021 PI方式 BER: 2. 40](http://slidetodoc.com/presentation_image_h2/a444ffddc4e65ec3a2956709dd020160/image-31.jpg)

Measured Results [SMI, PI] SMI方式 BER: 6. 60 E-03 9/13/2021 PI方式 BER: 2. 40 E-03 System Arch 2007 (Fire Tom Wada) 31

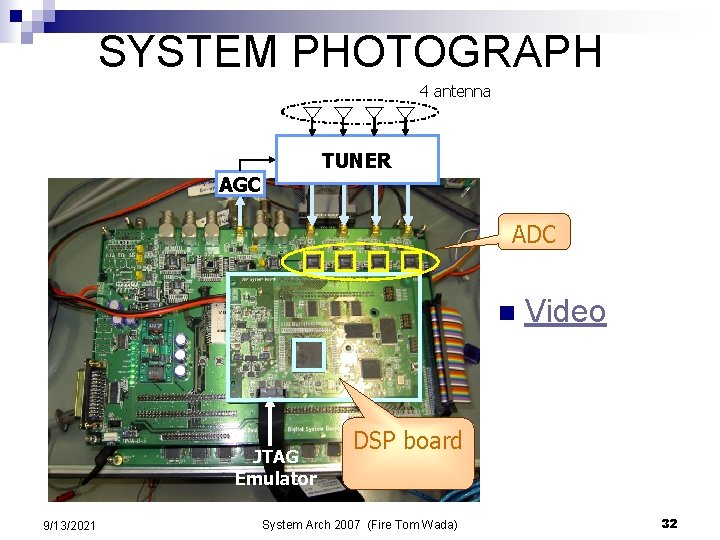

SYSTEM PHOTOGRAPH 4 antenna TUNER AGC ADC n JTAG Emulator 9/13/2021 Video DSP board System Arch 2007 (Fire Tom Wada) 32

n ALL SUBJECTS ARE FINISHED! n THANK YOU!!! 9/13/2021 System Arch 2007 (Fire Tom Wada) 33

- Slides: 33