Il sistema di trigger di MEG Per conto

- Slides: 15

Il sistema di trigger di MEG Per conto di D. Nicolò F. Morsani S. Galeotti S. Giurgola Marco Grassi INFN - Pisa Gruppo 1 - Sep. 21 st 2004 1

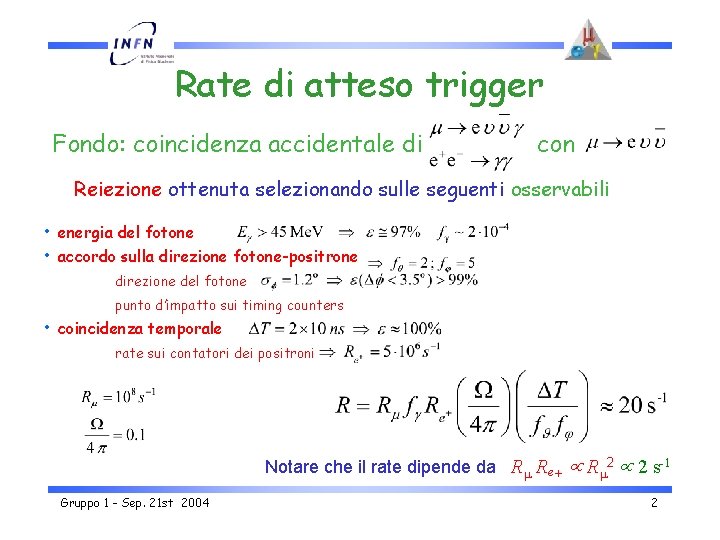

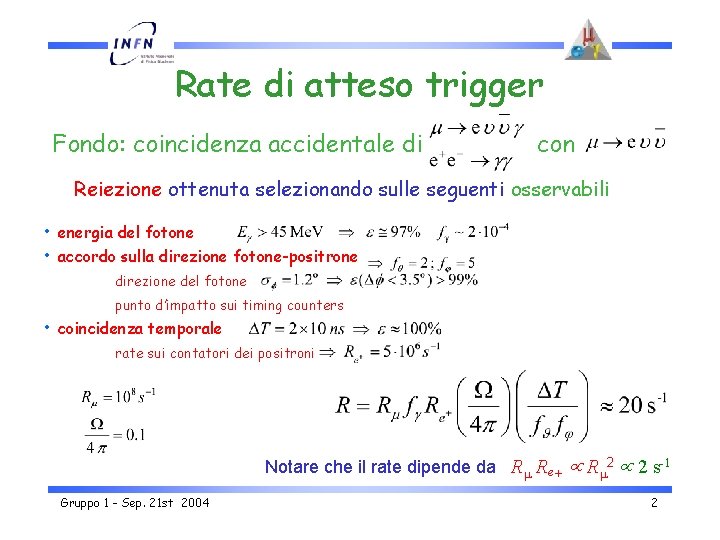

Rate di atteso trigger Fondo: coincidenza accidentale di con Reiezione ottenuta selezionando sulle seguenti osservabili • • energia del fotone accordo sulla direzione fotone-positrone direzione del fotone • punto d’impatto sui timing counters coincidenza temporale rate sui contatori dei positroni Notare che il rate dipende da R Re+ R 2 2 s-1 Gruppo 1 - Sep. 21 st 2004 2

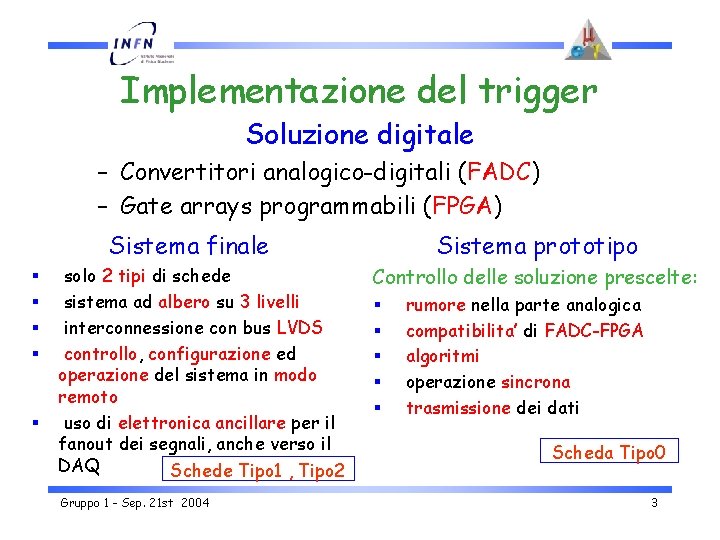

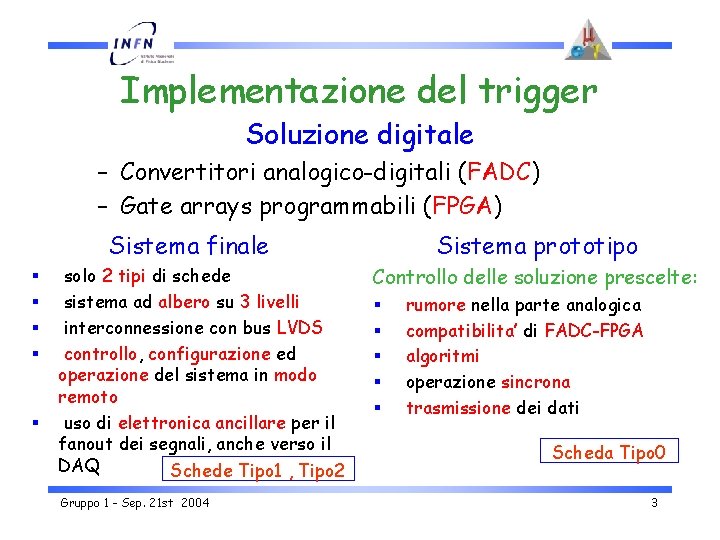

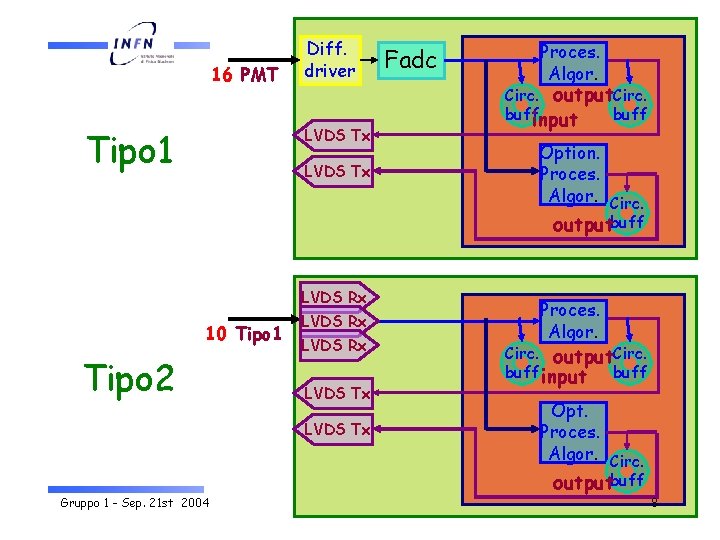

Implementazione del trigger Soluzione digitale – Convertitori analogico-digitali (FADC) – Gate arrays programmabili (FPGA) Sistema finale § § § solo 2 tipi di schede sistema ad albero su 3 livelli interconnessione con bus LVDS controllo, configurazione ed operazione del sistema in modo remoto uso di elettronica ancillare per il fanout dei segnali, anche verso il DAQ Schede Tipo 1 , Tipo 2 Gruppo 1 - Sep. 21 st 2004 Sistema prototipo Controllo delle soluzione prescelte: § § § rumore nella parte analogica compatibilita’ di FADC-FPGA algoritmi operazione sincrona trasmissione dei dati Scheda Tipo 0 3

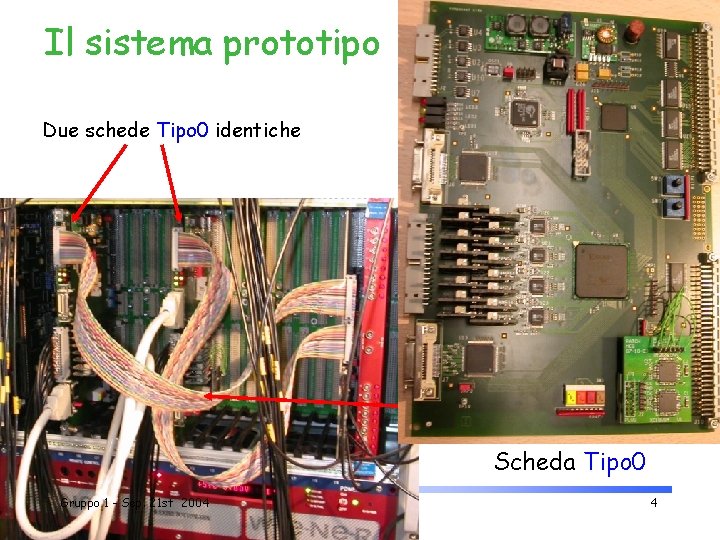

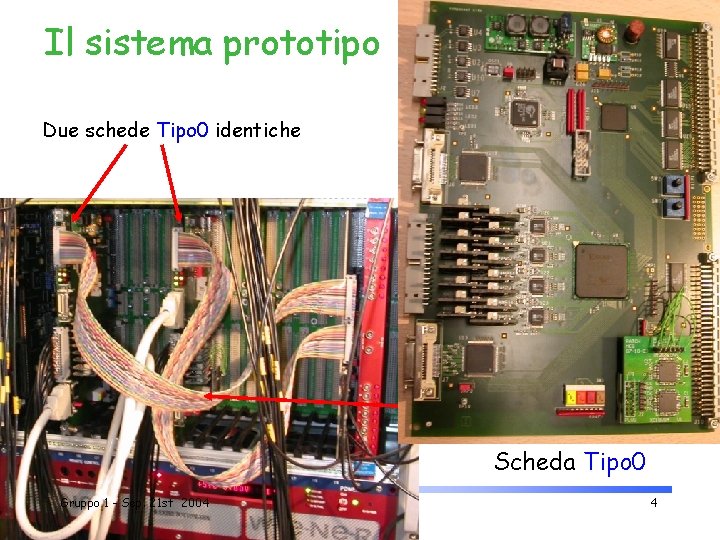

Il sistema prototipo Due schede Tipo 0 identiche Scheda Tipo 0 Gruppo 1 - Sep. 21 st 2004 4

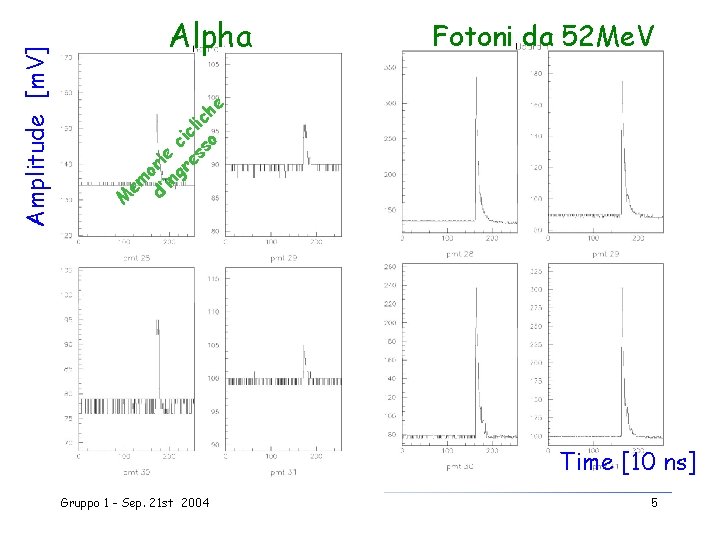

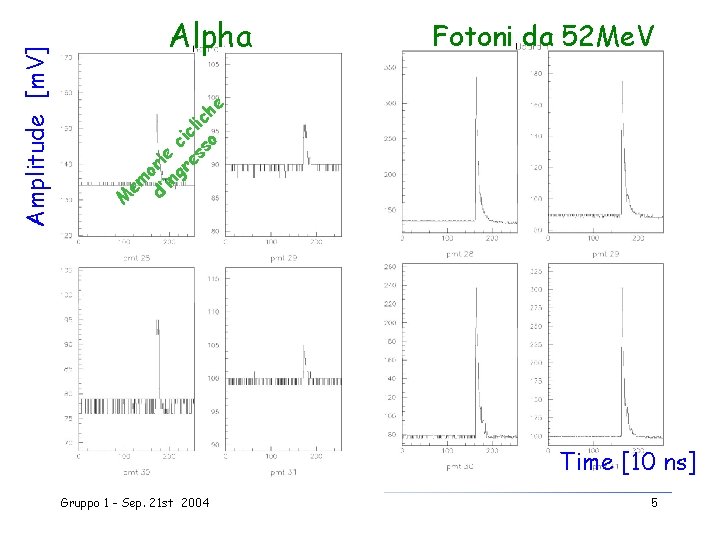

em d’ orie in gr ci es cli so ch e Fotoni da 52 Me. V M Amplitude [m. V] Alpha Time [10 ns] Gruppo 1 - Sep. 21 st 2004 5

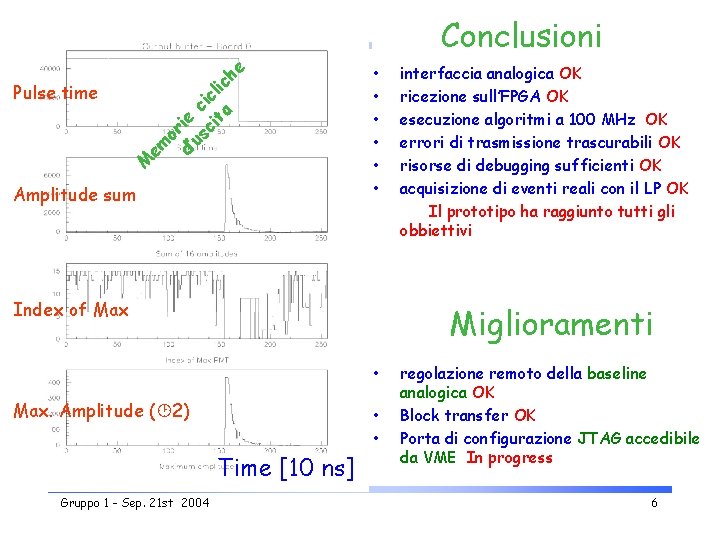

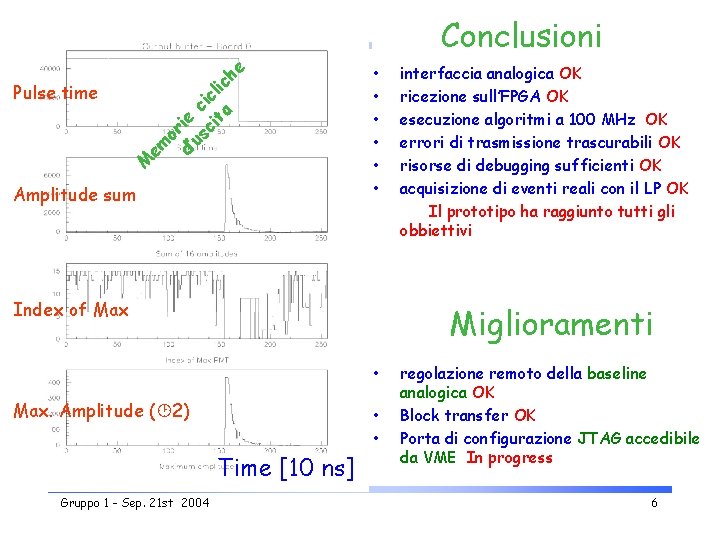

he Conclusioni M em o d’ rie us c ci icl ta ic Pulse time Amplitude sum • • • Index of Max Miglioramenti • Max. Amplitude ( 2) • • Time [10 ns] Gruppo 1 - Sep. 21 st 2004 interfaccia analogica OK ricezione sull’FPGA OK esecuzione algoritmi a 100 MHz OK errori di trasmissione trascurabili OK risorse di debugging sufficienti OK acquisizione di eventi reali con il LP OK Il prototipo ha raggiunto tutti gli obbiettivi regolazione remoto della baseline analogica OK Block transfer OK Porta di configurazione JTAG accedibile da VME In progress 6

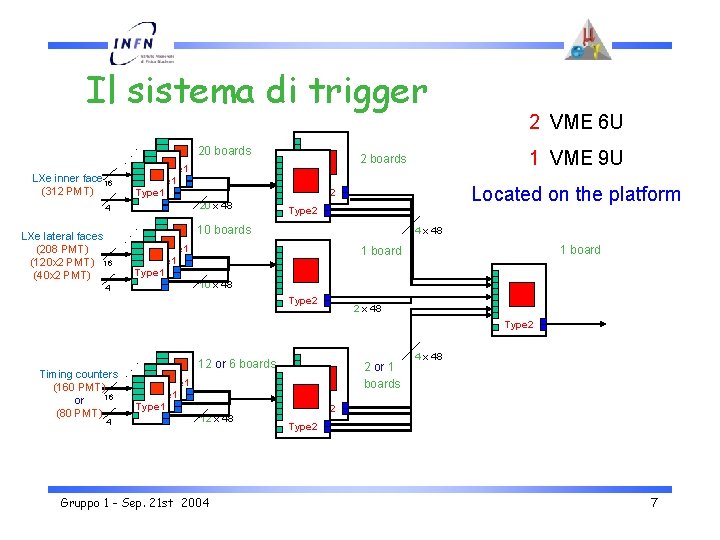

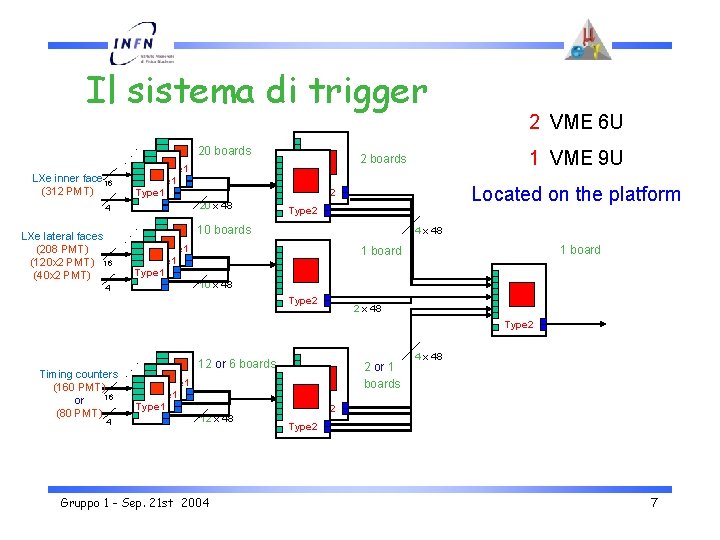

. . . Il sistema di trigger LXe inner face 16 (312 PMT) Type 1 . . . 1 VME 9 U 2 boards Located on the platform Type 2 20 x 48 4 LXe lateral faces (208 PMT) (120 x 2 PMT) 16 (40 x 2 PMT) 20 boards 2 VME 6 U Type 2 10 boards 4 x 48 Type 1 1 board 10 x 48 4 Type 2 2 x 48 . Type 2 . . Timing counters (160 PMT) 16 or (80 PMT) 4 12 or 6 boards Type 1 12 x 48 Gruppo 1 - Sep. 21 st 2004 2 or 1 boards 4 x 48 Type 2 7

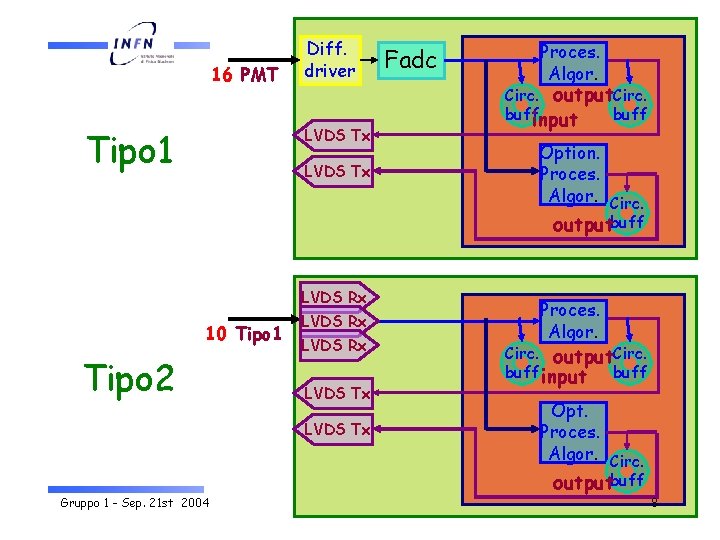

16 PMT Tipo 1 Diff. driver LVDS Tx Fadc Proces. Algor. Circ. output. Circ. buffinput buff Option. Proces. Algor. Circ. outputbuff 10 Tipo 1 Tipo 2 LVDS Rx LVDS Tx Gruppo 1 - Sep. 21 st 2004 Proces. Algor. Circ. output. Circ. buff input buff Opt. Proces. Algor. Circ. outputbuff 8

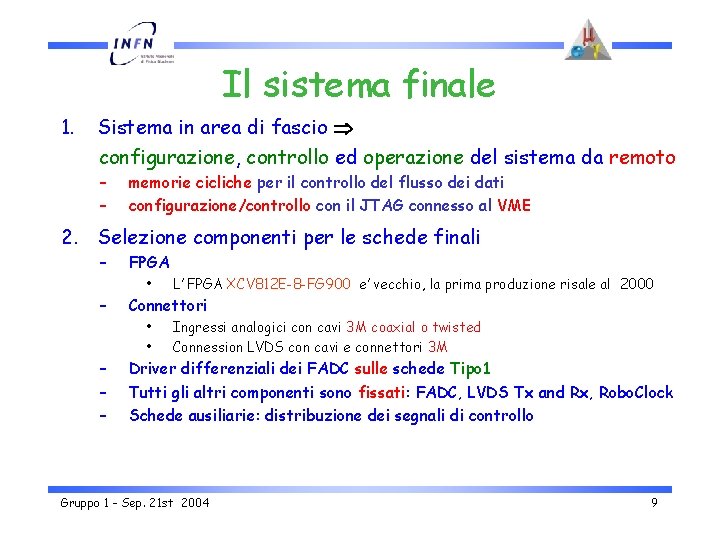

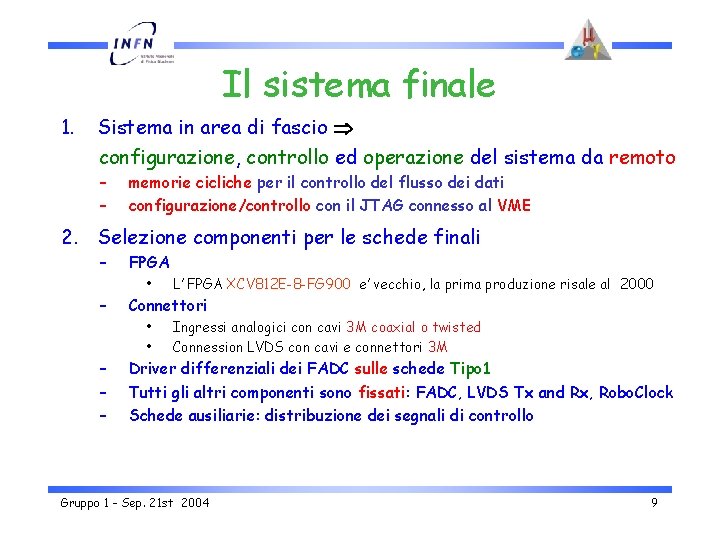

Il sistema finale 1. Sistema in area di fascio configurazione, controllo ed operazione del sistema da remoto – – memorie cicliche per il controllo del flusso dei dati configurazione/controllo con il JTAG connesso al VME 2. Selezione componenti per le schede finali – – – FPGA • L’ FPGA XCV 812 E-8 -FG 900 e’ vecchio, la prima produzione risale al 2000 Connettori • • Ingressi analogici con cavi 3 M coaxial o twisted Connession LVDS con cavi e connettori 3 M Driver differenziali dei FADC sulle schede Tipo 1 Tutti gli altri componenti sono fissati: FADC, LVDS Tx and Rx, Robo. Clock Schede ausiliarie: distribuzione dei segnali di controllo Gruppo 1 - Sep. 21 st 2004 9

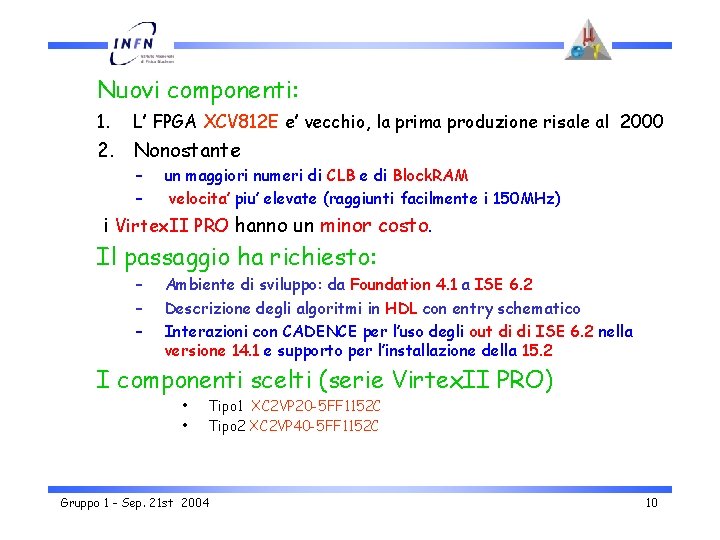

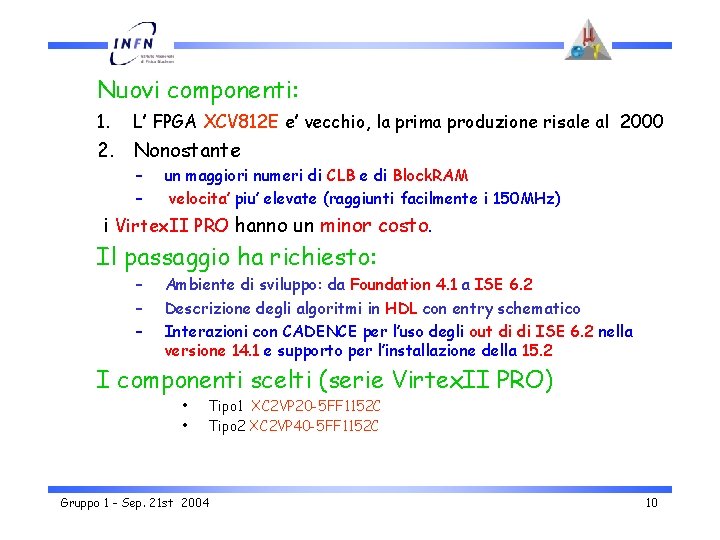

Nuovi componenti: 1. L’ FPGA XCV 812 E e’ vecchio, la prima produzione risale al 2000 2. Nonostante – – un maggiori numeri di CLB e di Block. RAM velocita’ piu’ elevate (raggiunti facilmente i 150 MHz) i Virtex. II PRO hanno un minor costo. Il passaggio ha richiesto: – – – Ambiente di sviluppo: da Foundation 4. 1 a ISE 6. 2 Descrizione degli algoritmi in HDL con entry schematico Interazioni con CADENCE per l’uso degli out di di ISE 6. 2 nella versione 14. 1 e supporto per l’installazione della 15. 2 I componenti scelti (serie Virtex. II PRO) • • Tipo 1 XC 2 VP 20 -5 FF 1152 C Tipo 2 XC 2 VP 40 -5 FF 1152 C Gruppo 1 - Sep. 21 st 2004 10

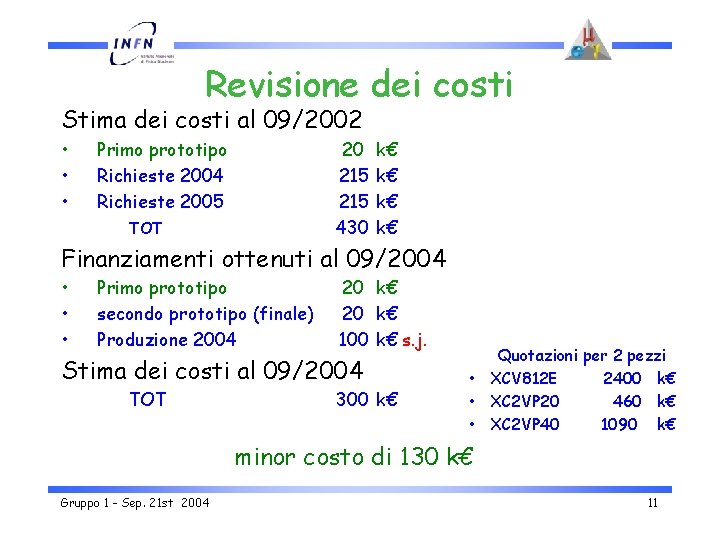

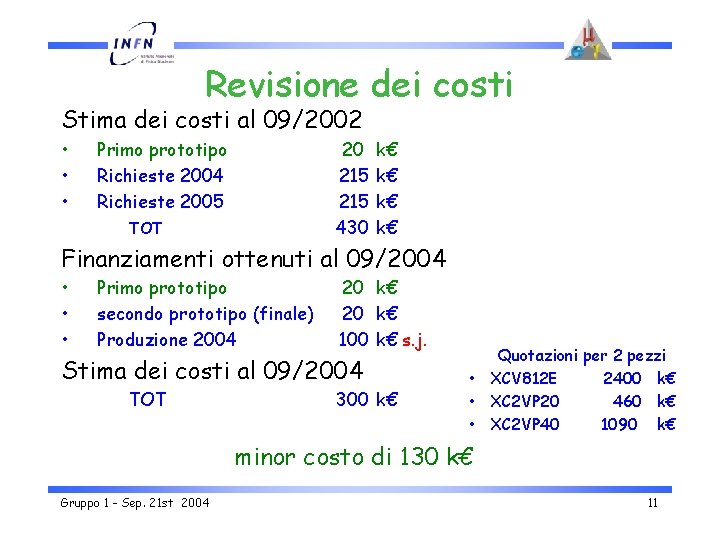

Revisione dei costi Stima dei costi al 09/2002 • • • Primo prototipo Richieste 2004 Richieste 2005 20 215 430 TOT k€ k€ Finanziamenti ottenuti al 09/2004 • • • Primo prototipo secondo prototipo (finale) Produzione 2004 20 k€ 100 k€ s. j. Stima dei costi al 09/2004 TOT 300 k€ Quotazioni per 2 pezzi • XCV 812 E 2400 k€ • XC 2 VP 20 460 k€ • XC 2 VP 40 1090 k€ minor costo di 130 k€ Gruppo 1 - Sep. 21 st 2004 11

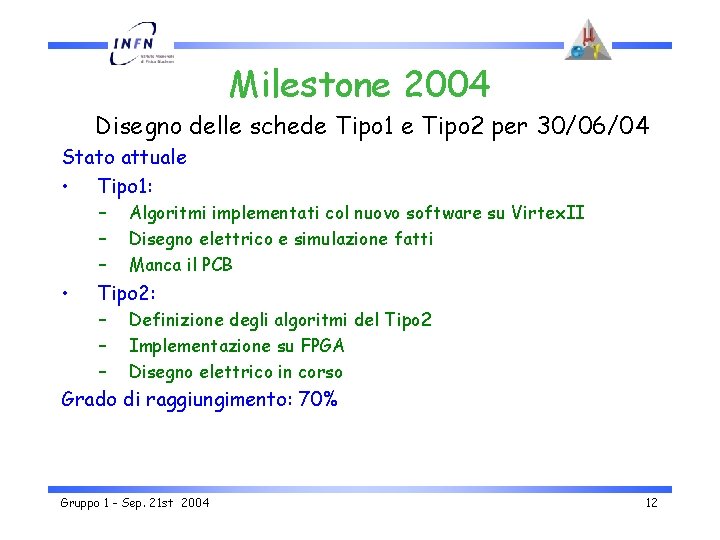

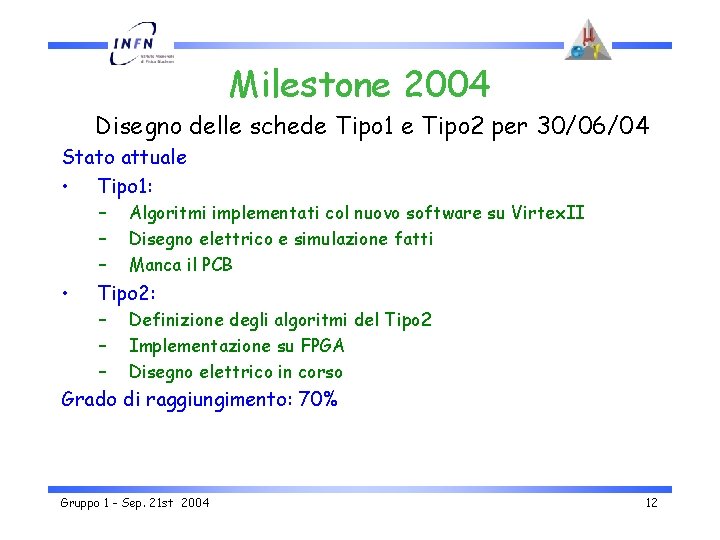

Milestone 2004 Disegno delle schede Tipo 1 e Tipo 2 per 30/06/04 Stato attuale • Tipo 1: – – – • Algoritmi implementati col nuovo software su Virtex. II Disegno elettrico e simulazione fatti Manca il PCB Tipo 2: – – – Definizione degli algoritmi del Tipo 2 Implementazione su FPGA Disegno elettrico in corso Grado di raggiungimento: 70% Gruppo 1 - Sep. 21 st 2004 12

Richieste Chiediamo lo sblocco del s. j. per procedere all’acquisto dei componenti in particolare Xilinx che ha tempi di fornitura superiori attorno a 12 settimane e nonostante la milestone solo parzialmente raggiunta Chiediamo i restanti 200 k€ nel 2005 Gruppo 1 - Sep. 21 st 2004 13

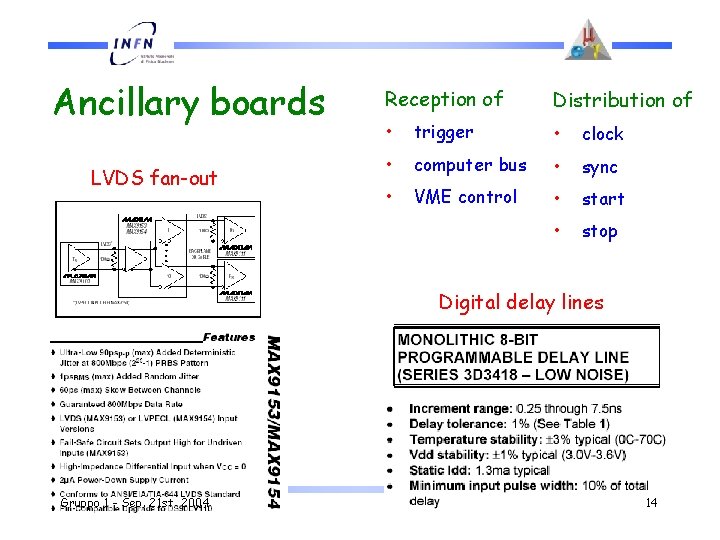

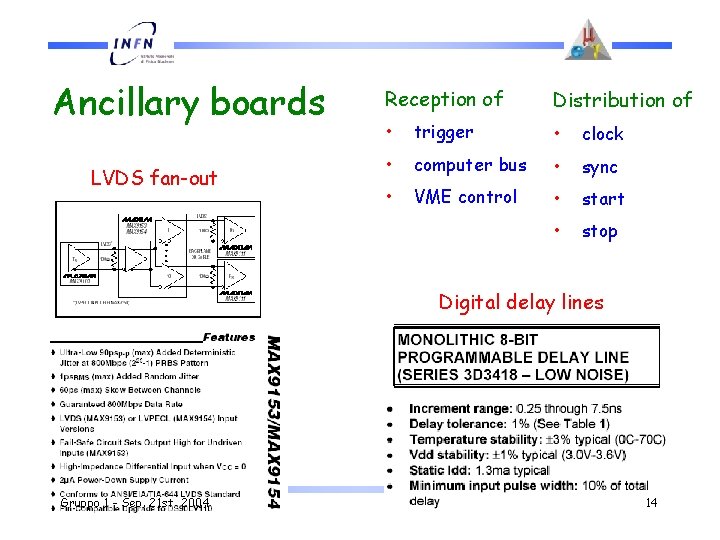

Ancillary boards LVDS fan-out Reception of Distribution of • trigger • clock • computer bus • sync • VME control • start • stop Digital delay lines Gruppo 1 - Sep. 21 st 2004 14

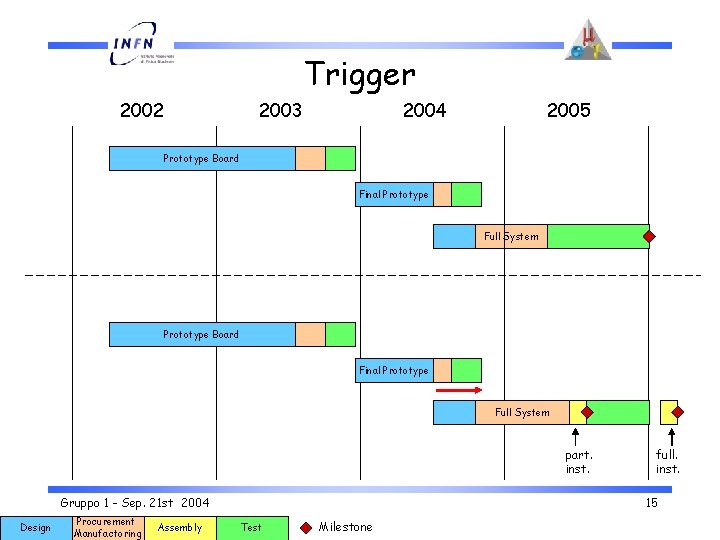

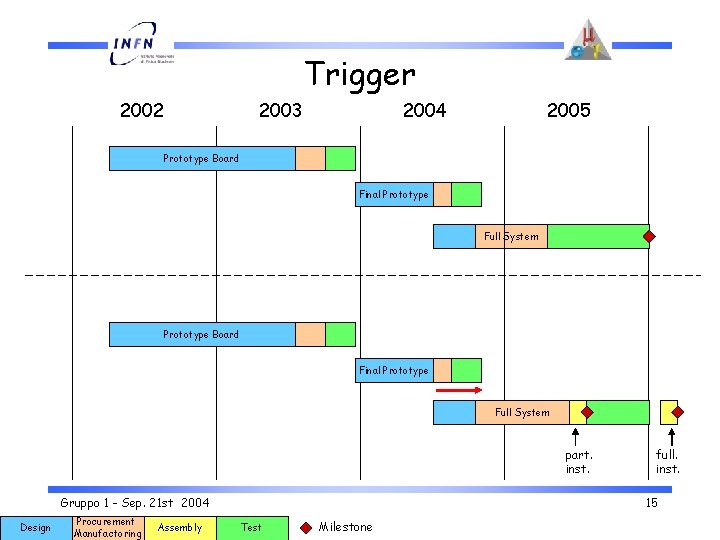

Trigger 2002 2003 2004 2005 Prototype Board Final Prototype Full System part. inst. Gruppo 1 - Sep. 21 st 2004 Design Procurement Manufactoring Assembly full. inst. 15 Test Milestone