IKI 10230 Pengantar Organisasi Komputer Bab 7 Datapath

IKI 10230 Pengantar Organisasi Komputer Bab 7: Datapath Sumber: 1. Hamacher. Computer Organization, ed-5. 21 Mei 2003 Bobby Nazief (nazief@cs. ui. ac. id) Qonita Shahab (niet@cs. ui. ac. id) bahan kuliah: http: //www. cs. ui. ac. id/kuliah/iki 10230/

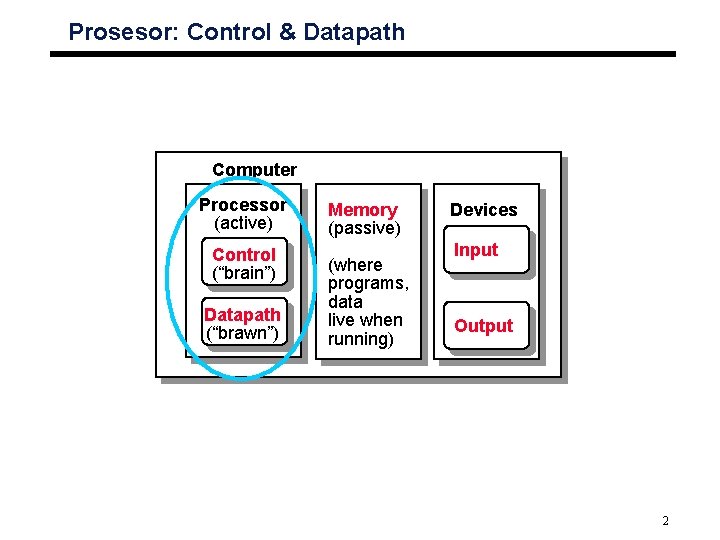

Prosesor: Control & Datapath Computer Processor (active) Control (“brain”) Datapath (“brawn”) Memory (passive) (where programs, data live when running) Devices Input Output 2

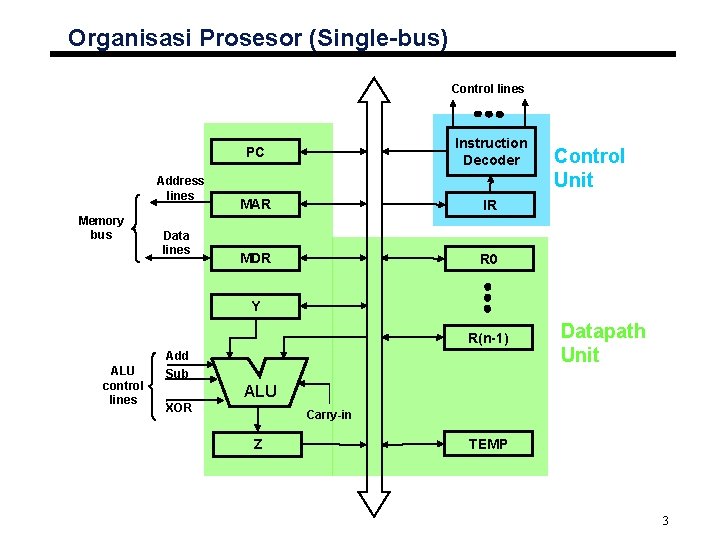

Organisasi Prosesor (Single-bus) Control lines Address lines Memory bus Data lines PC Instruction Decoder MAR IR MDR R 0 Control Unit Y R(n-1) ALU control lines Add Sub Datapath Unit ALU XOR Carry-in Z TEMP 3

![Siklus Eksekusi Instruksi Eksekusi instruksi yang ukurannya tetap do { 1. IR M[PC] // Siklus Eksekusi Instruksi Eksekusi instruksi yang ukurannya tetap do { 1. IR M[PC] //](http://slidetodoc.com/presentation_image_h/b6fd993281d50d55b814d99f3cae0989/image-4.jpg)

Siklus Eksekusi Instruksi Eksekusi instruksi yang ukurannya tetap do { 1. IR M[PC] // Fetch instruksi 2. PC + d // Tunjuk ke lokasi instruksi berikutnya 3. Eksekusi instruksi } while (!stop) Eksekusi instruksi yang ukurannya bervariasi do { // Fetch instruksi IR M[PC] PC + d } while (!end-of-instruction) Eksekusi instruksi } while (!stop) 4

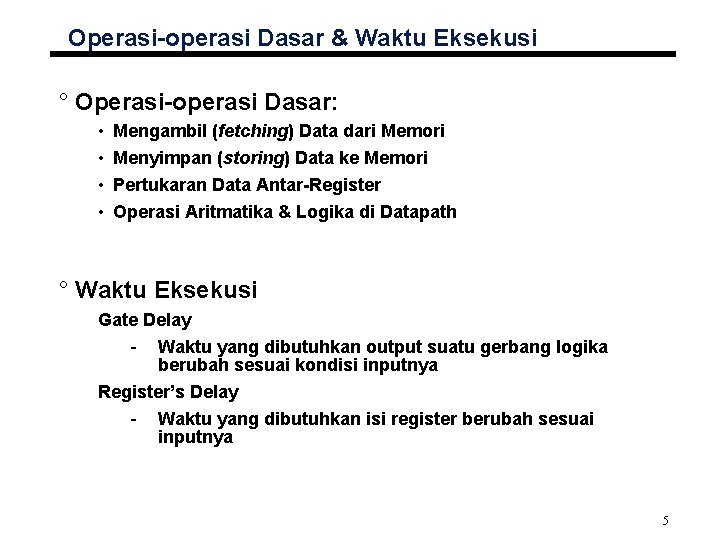

Operasi-operasi Dasar & Waktu Eksekusi ° Operasi-operasi Dasar: • • Mengambil (fetching) Data dari Memori Menyimpan (storing) Data ke Memori Pertukaran Data Antar-Register Operasi Aritmatika & Logika di Datapath ° Waktu Eksekusi Gate Delay - Waktu yang dibutuhkan output suatu gerbang logika berubah sesuai kondisi inputnya Register’s Delay - Waktu yang dibutuhkan isi register berubah sesuai inputnya 5

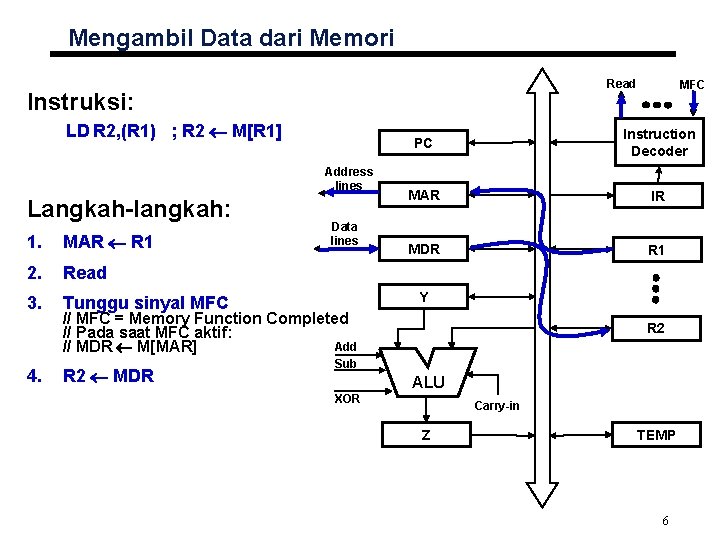

Mengambil Data dari Memori Read Instruksi: LD R 2, (R 1) ; R 2 M[R 1] Address lines Langkah-langkah: 1. MAR R 1 2. Read 3. Tunggu sinyal MFC 4. Data lines PC Instruction Decoder MAR IR MDR R 1 Y // MFC = Memory Function Completed // Pada saat MFC aktif: Add // MDR M[MAR] R 2 MDR MFC R 2 Sub ALU XOR Carry-in Z TEMP 6

![Menyimpan Data ke Memori Write Instruksi: ST (R 1), R 2 ; M[R 1] Menyimpan Data ke Memori Write Instruksi: ST (R 1), R 2 ; M[R 1]](http://slidetodoc.com/presentation_image_h/b6fd993281d50d55b814d99f3cae0989/image-7.jpg)

Menyimpan Data ke Memori Write Instruksi: ST (R 1), R 2 ; M[R 1] R 2 Address lines Langkah-langkah: 1. MAR R 1 2. MDR R 2, Write 3. Tunggu sinyal MFC Data lines MFC PC Instruction Decoder MAR IR MDR R 1 Y // MFC = Memory Function Completed // Pada saat MFC aktif: Add // M[MAR] MDR R 2 Sub ALU XOR Carry-in Z TEMP 7

Pengendalian Transfer Data Dari/Ke Register

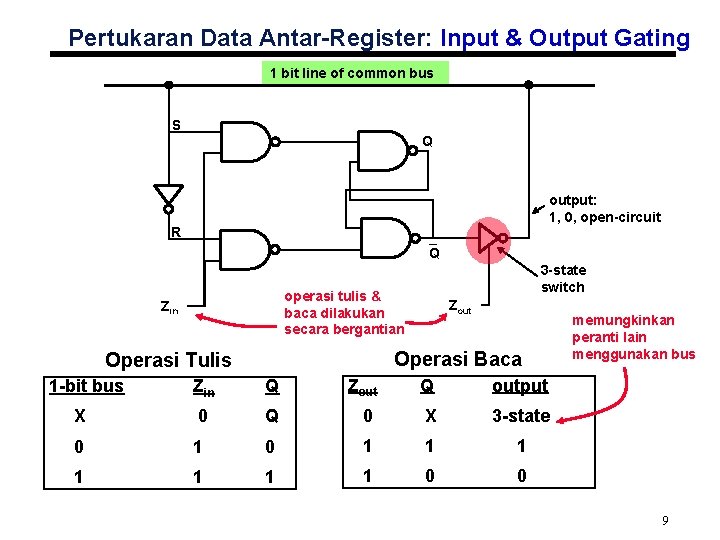

Pertukaran Data Antar-Register: Input & Output Gating 1 bit line of common bus S Q output: 1, 0, open-circuit R _ Q 3 -state switch operasi tulis & baca dilakukan secara bergantian Zin Zout Operasi Baca Operasi Tulis Zin Q Zout Q output X 0 Q 0 X 3 -state 0 1 1 1 1 0 0 1 -bit bus memungkinkan peranti lain menggunakan bus 9

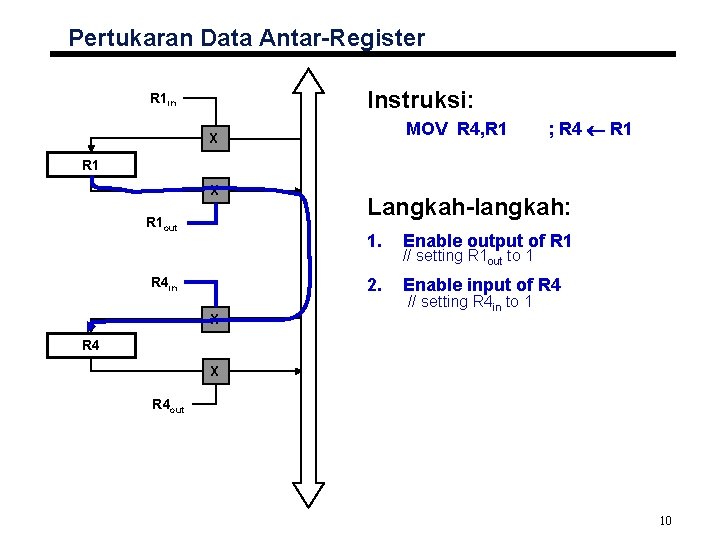

Pertukaran Data Antar-Register Instruksi: R 1 in MOV R 4, R 1 X ; R 4 R 1 X R 1 out R 4 in X Langkah-langkah: 1. Enable output of R 1 2. Enable input of R 4 // setting R 1 out to 1 // setting R 4 in to 1 R 4 X R 4 out 10

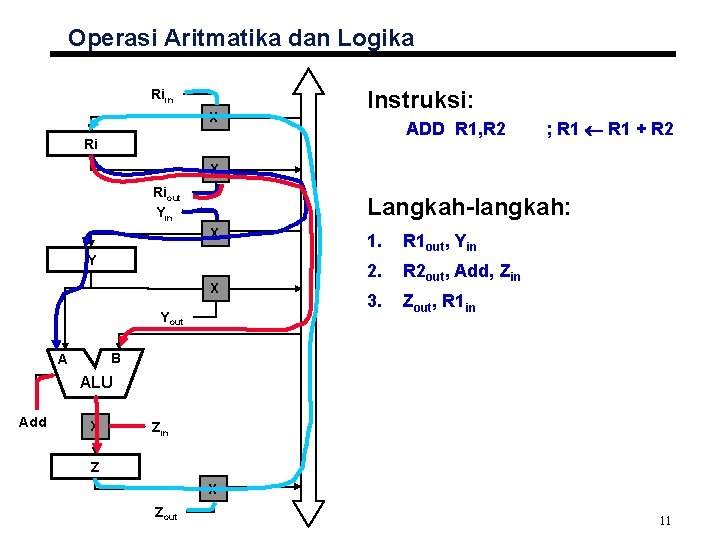

Operasi Aritmatika dan Logika Riin X Instruksi: ADD R 1, R 2 Ri ; R 1 + R 2 X Riout Yin Langkah-langkah: X Yout 1. R 1 out, Yin 2. R 2 out, Add, Zin 3. Zout, R 1 in B A ALU Add X Zin Z X Zout 11

Waktu Eksekusi

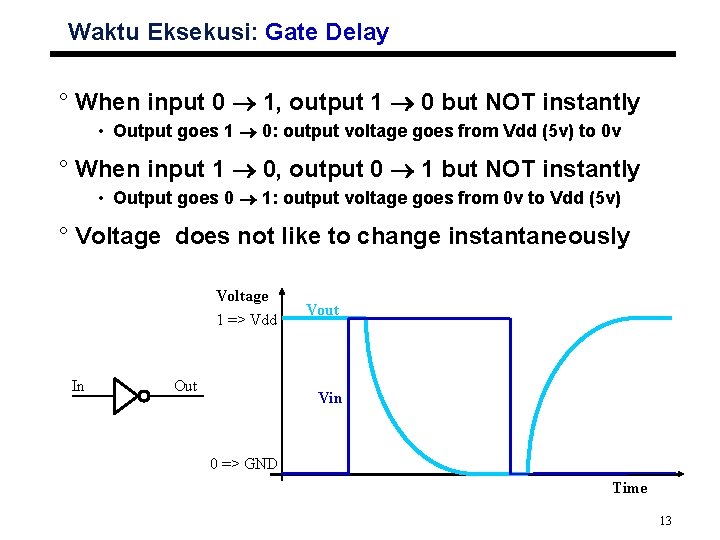

Waktu Eksekusi: Gate Delay ° When input 0 1, output 1 0 but NOT instantly • Output goes 1 0: output voltage goes from Vdd (5 v) to 0 v ° When input 1 0, output 0 1 but NOT instantly • Output goes 0 1: output voltage goes from 0 v to Vdd (5 v) ° Voltage does not like to change instantaneously Voltage 1 => Vdd In Out Vout Vin 0 => GND Time 13

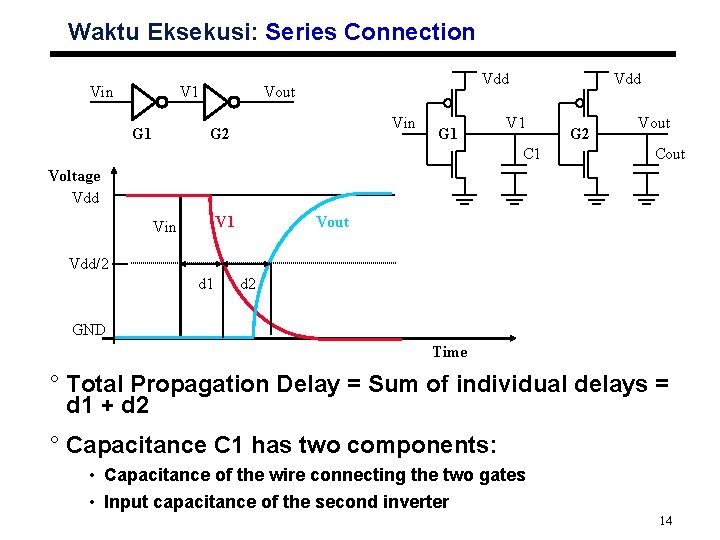

Waktu Eksekusi: Series Connection Vin V 1 G 1 Vdd Vout Vin G 2 G 1 Vdd V 1 C 1 G 2 Vout Cout Voltage Vdd V 1 Vin Vout Vdd/2 d 1 d 2 GND Time ° Total Propagation Delay = Sum of individual delays = d 1 + d 2 ° Capacitance C 1 has two components: • Capacitance of the wire connecting the two gates • Input capacitance of the second inverter 14

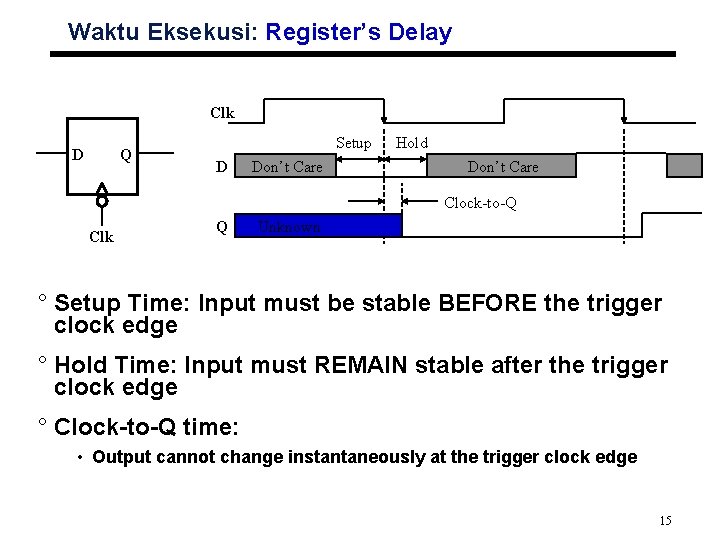

Waktu Eksekusi: Register’s Delay Clk D Q Setup D Don’t Care Hold Don’t Care Clock-to-Q Clk Q Unknown ° Setup Time: Input must be stable BEFORE the trigger clock edge ° Hold Time: Input must REMAIN stable after the trigger clock edge ° Clock-to-Q time: • Output cannot change instantaneously at the trigger clock edge 15

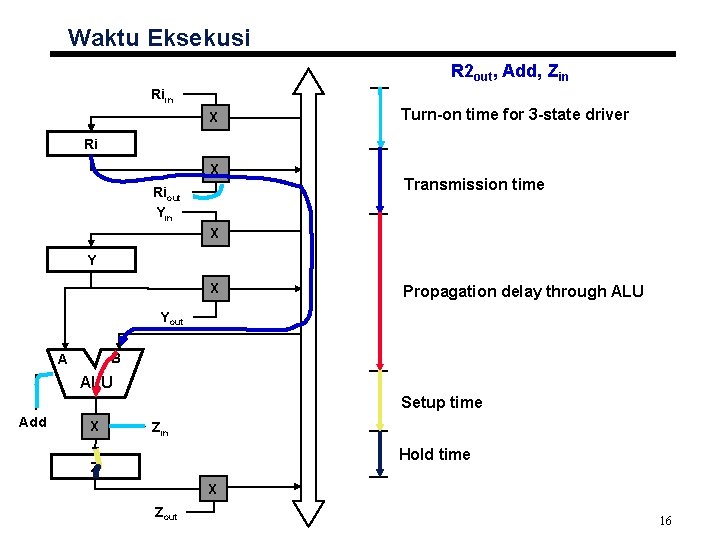

Waktu Eksekusi R 2 out, Add, Zin Riin X Turn-on time for 3 -state driver Ri X Riout Yin Transmission time X Y X Propagation delay through ALU Yout B A ALU Setup time Add X Zin Hold time Z X Zout 16

PR no. 5

PR no. 5: batas waktu 4 Juni 2003 1. 7. 3 2. 7. 5 3. 7. 10 4. 7. 11 5. 7. 24 18

Langkah-langkah Pengeksekusian Instruksi

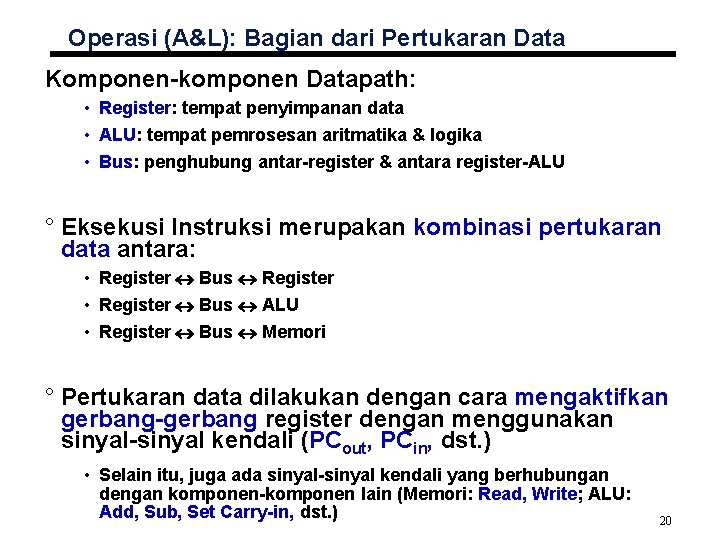

Operasi (A&L): Bagian dari Pertukaran Data Komponen-komponen Datapath: • Register: tempat penyimpanan data • ALU: tempat pemrosesan aritmatika & logika • Bus: penghubung antar-register & antara register-ALU ° Eksekusi Instruksi merupakan kombinasi pertukaran data antara: • Register Bus Register • Register Bus ALU • Register Bus Memori ° Pertukaran data dilakukan dengan cara mengaktifkan gerbang-gerbang register dengan menggunakan sinyal-sinyal kendali (PCout, PCin, dst. ) • Selain itu, juga ada sinyal-sinyal kendali yang berhubungan dengan komponen-komponen lain (Memori: Read, Write; ALU: Add, Sub, Set Carry-in, dst. ) 20

![Tahapan Eksekusi Instruksi: Add R 1, (R 3) ; R 1 + M[R 3] Tahapan Eksekusi Instruksi: Add R 1, (R 3) ; R 1 + M[R 3]](http://slidetodoc.com/presentation_image_h/b6fd993281d50d55b814d99f3cae0989/image-21.jpg)

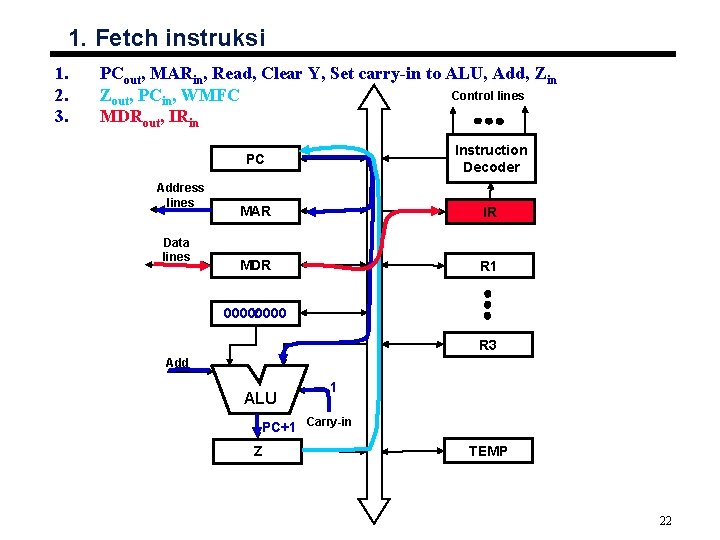

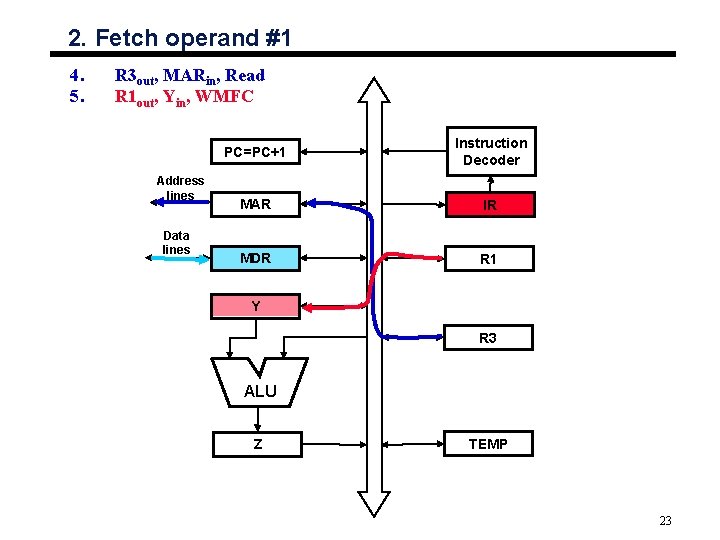

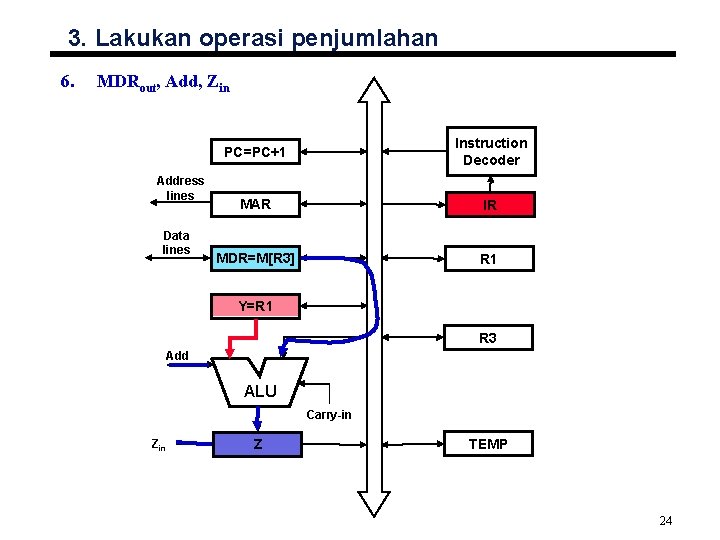

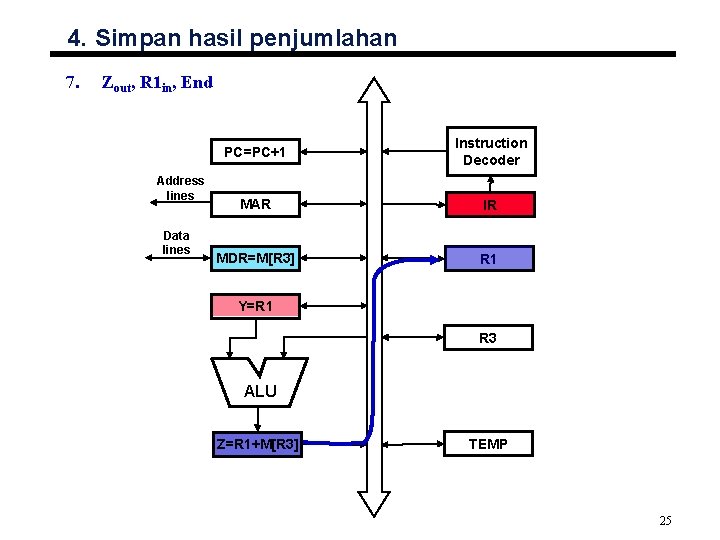

Tahapan Eksekusi Instruksi: Add R 1, (R 3) ; R 1 + M[R 3] Langkah-langkah: 1. Fetch instruksi 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 2. Fetch operand #1 (isi lokasi memori yg ditunjuk oleh R 3) 4. R 3 out, MARin, Read 5. R 1 out, Yin, WMFC 3. Lakukan operasi penjumlahan 6. MDRout, Add, Zin 4. Simpan hasil penjumlahan di R 1 7. Zout, R 1 in, End 21

1. Fetch instruksi 1. 2. 3. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Control lines Zout, PCin, WMFC MDRout, IRin Address lines Data lines PC Instruction Decoder MAR IR MDR R 1 0000 Y R 3 Add ALU 1 PC+1 Carry-in Z TEMP 22

2. Fetch operand #1 4. 5. R 3 out, MARin, Read R 1 out, Yin, WMFC Address lines Data lines PC=PC+1 Instruction Decoder MAR IR MDR R 1 Y R 3 ALU Z TEMP 23

3. Lakukan operasi penjumlahan 6. MDRout, Add, Zin Address lines Data lines PC=PC+1 Instruction Decoder MAR IR MDR=M[R 3] R 1 Y=R 1 R 3 Add ALU Carry-in Z TEMP 24

4. Simpan hasil penjumlahan 7. Zout, R 1 in, End Address lines Data lines PC=PC+1 Instruction Decoder MAR IR MDR=M[R 3] R 1 Y=R 1 R 3 ALU Z=R 1+M[R 3] TEMP 25

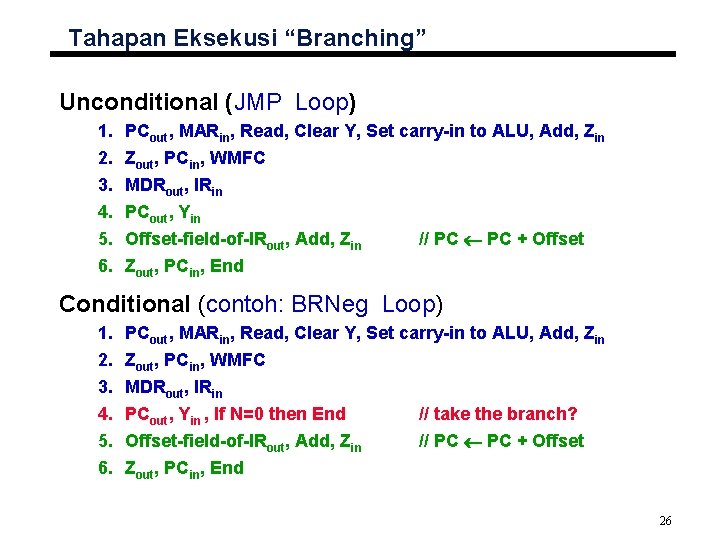

Tahapan Eksekusi “Branching” Unconditional (JMP Loop) 1. 2. 3. 4. 5. 6. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Zout, PCin, WMFC MDRout, IRin PCout, Yin Offset-field-of-IRout, Add, Zin Zout, PCin, End // PC + Offset Conditional (contoh: BRNeg Loop) 1. 2. 3. 4. 5. 6. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Zout, PCin, WMFC MDRout, IRin PCout, Yin , If N=0 then End // take the branch? Offset-field-of-IRout, Add, Zin // PC + Offset Zout, PCin, End 26

LD Rd, X

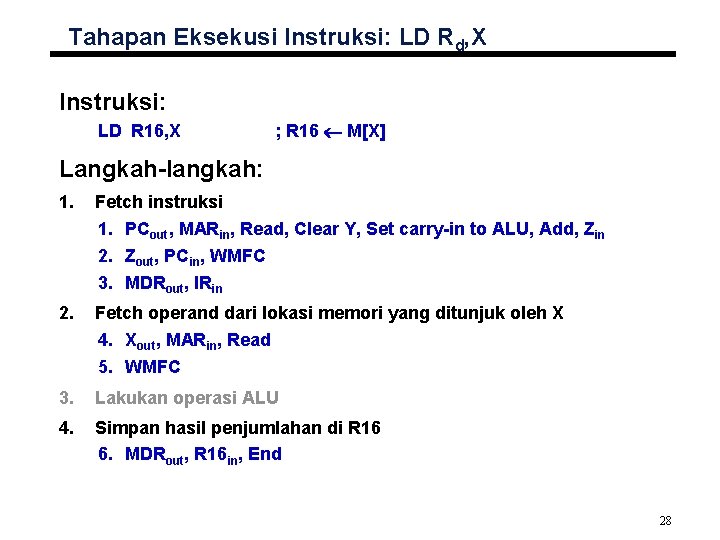

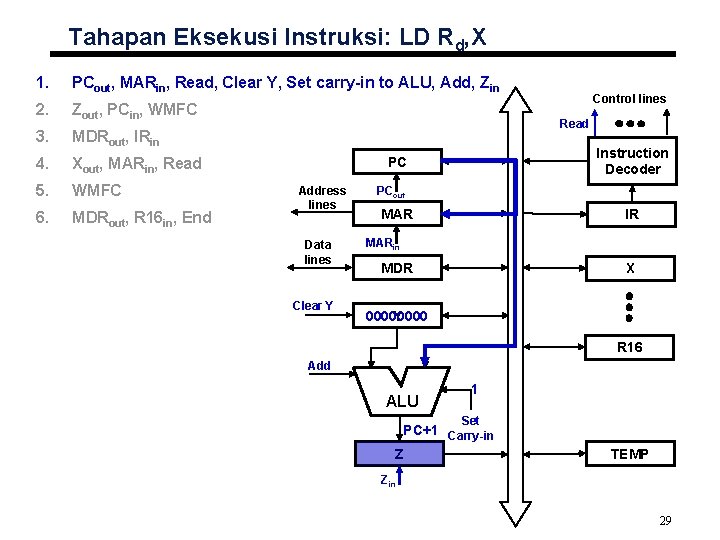

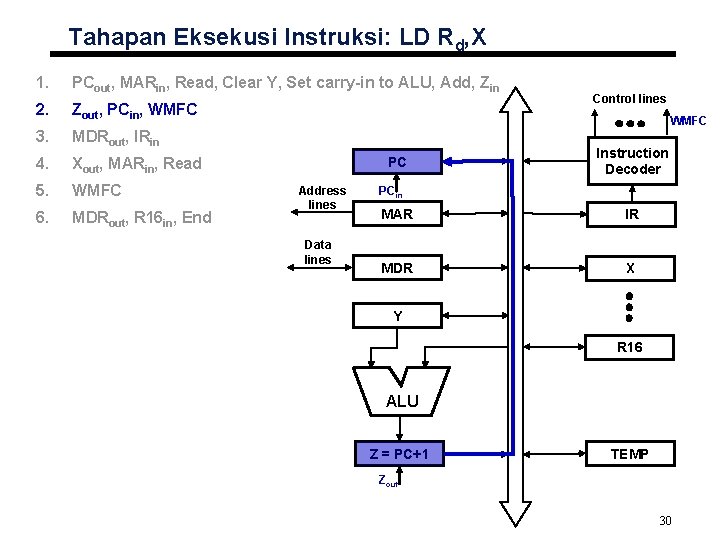

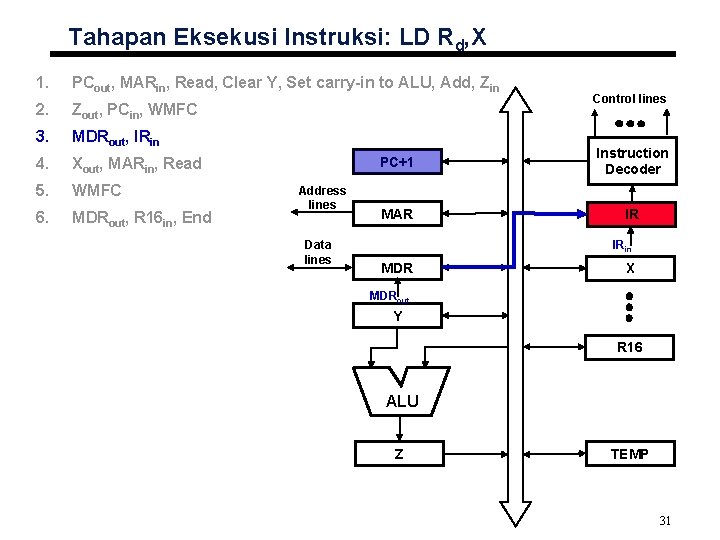

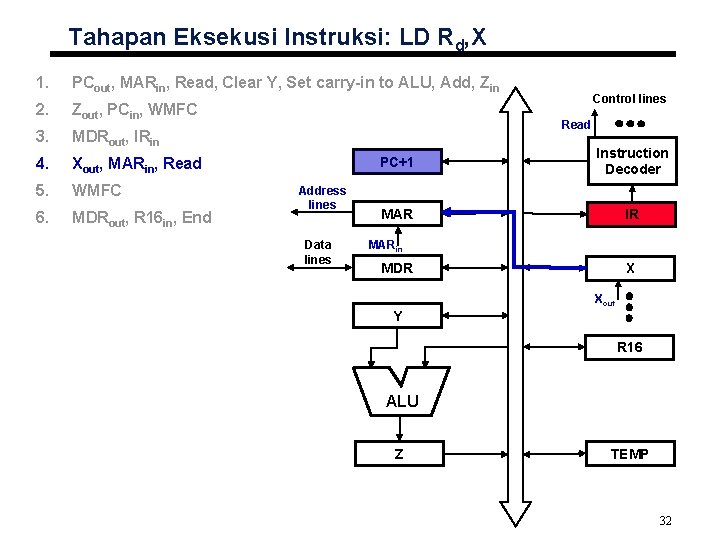

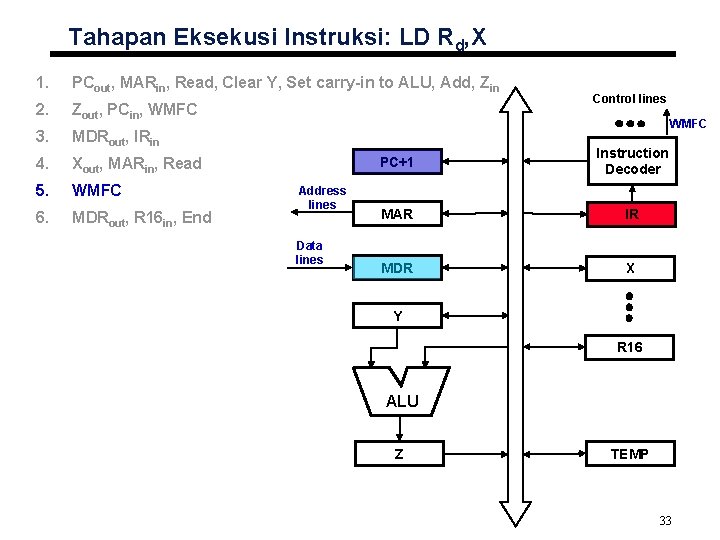

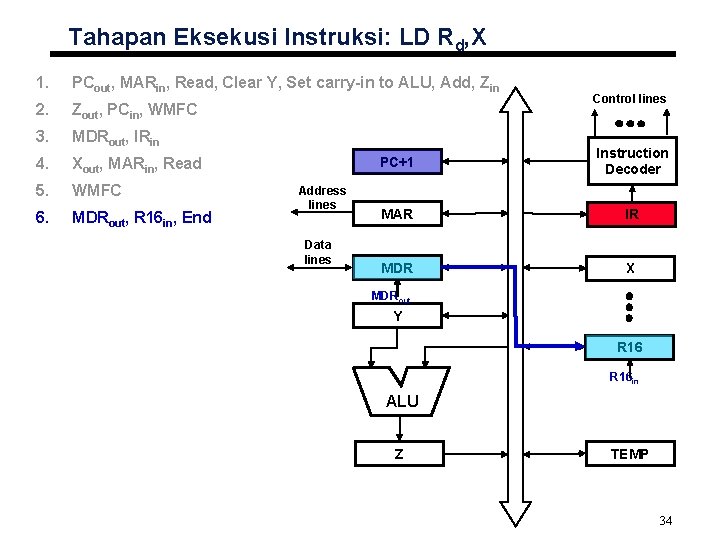

Tahapan Eksekusi Instruksi: LD Rd, X Instruksi: LD R 16, X ; R 16 M[X] Langkah-langkah: 1. Fetch instruksi 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 2. Fetch operand dari lokasi memori yang ditunjuk oleh X 4. Xout, MARin, Read 5. WMFC 3. Lakukan operasi ALU 4. Simpan hasil penjumlahan di R 16 6. MDRout, R 16 in, End 28

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines Read Instruction Decoder PC Address lines Data lines Clear Y PCout MAR IR MARin MDR X 0000 Y R 16 Add ALU 1 Set PC+1 Carry-in Z TEMP Zin 29

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines WMFC PC Address lines Data lines Instruction Decoder PCin MAR IR MDR X Y R 16 ALU Z = PC+1 TEMP Zout 30

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Address lines Data lines Control lines PC+1 Instruction Decoder MAR IR IRin MDR X MDRout Y R 16 ALU Z TEMP 31

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines Read Address lines Data lines PC+1 Instruction Decoder MAR IR MARin MDR X Xout Y R 16 ALU Z TEMP 32

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines WMFC Address lines Data lines PC+1 Instruction Decoder MAR IR MDR X Y R 16 ALU Z TEMP 33

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Address lines Data lines Control lines PC+1 Instruction Decoder MAR IR MDR X MDRout Y R 16 in ALU Z TEMP 34

ADD Rd, Rs

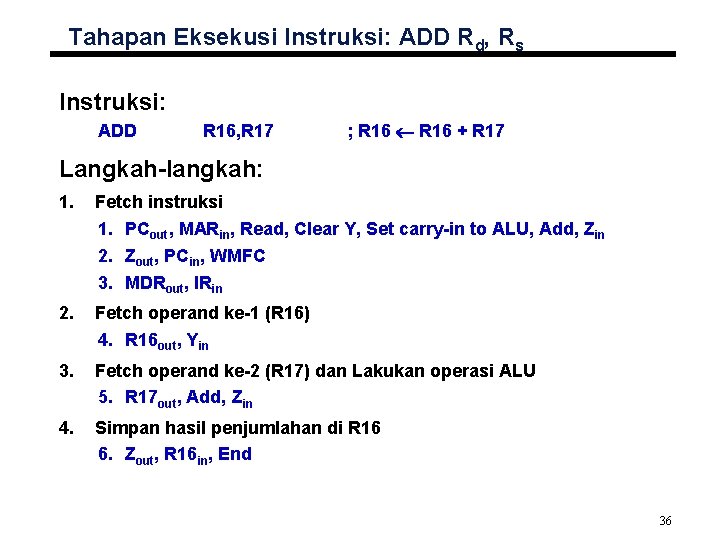

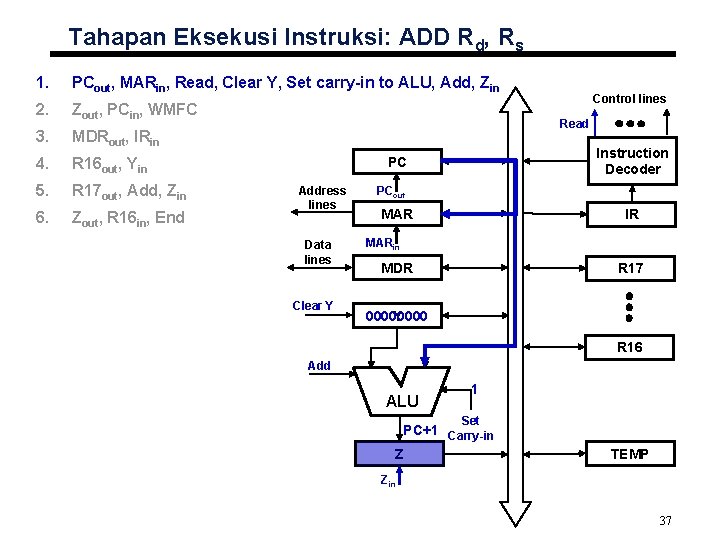

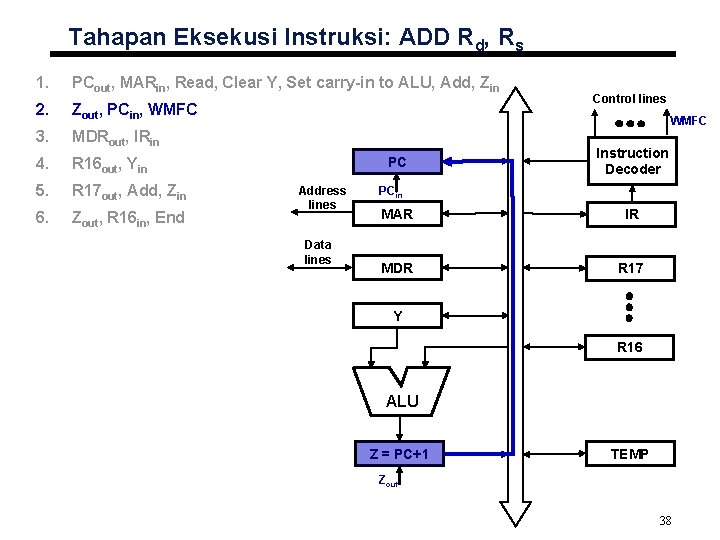

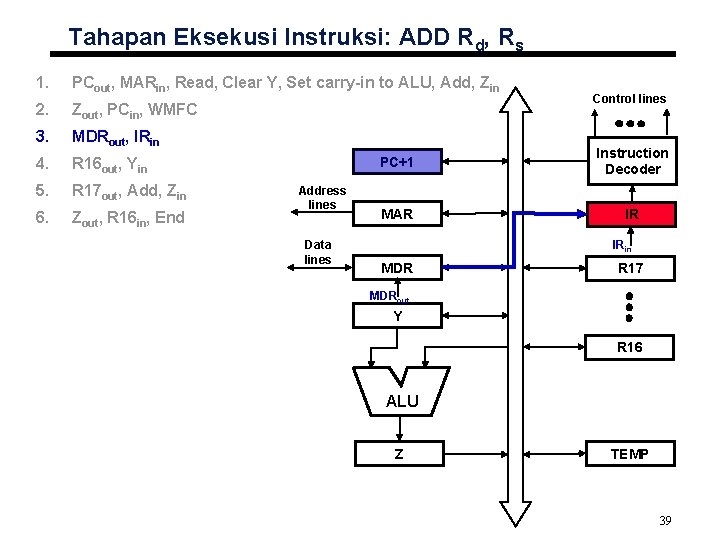

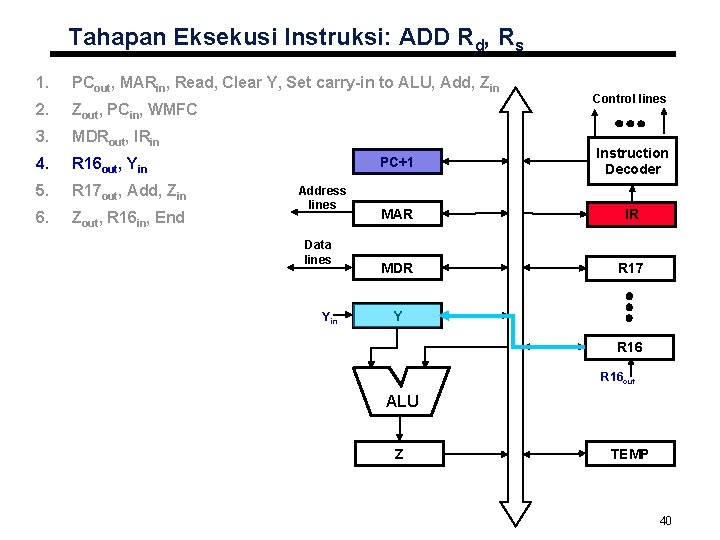

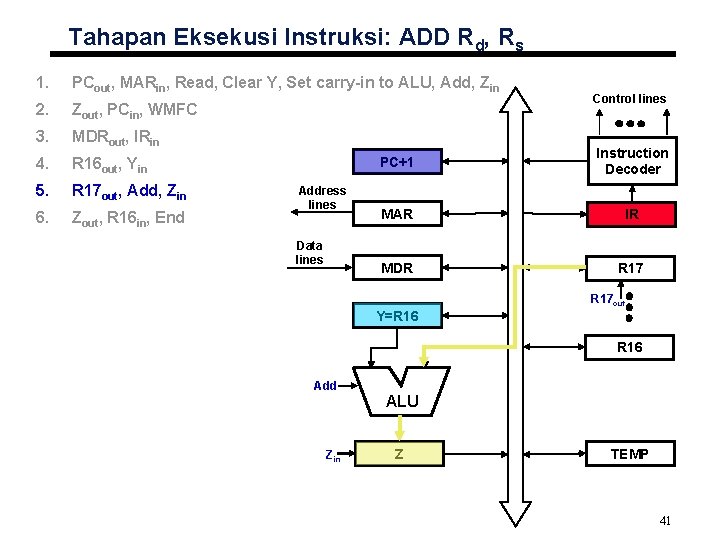

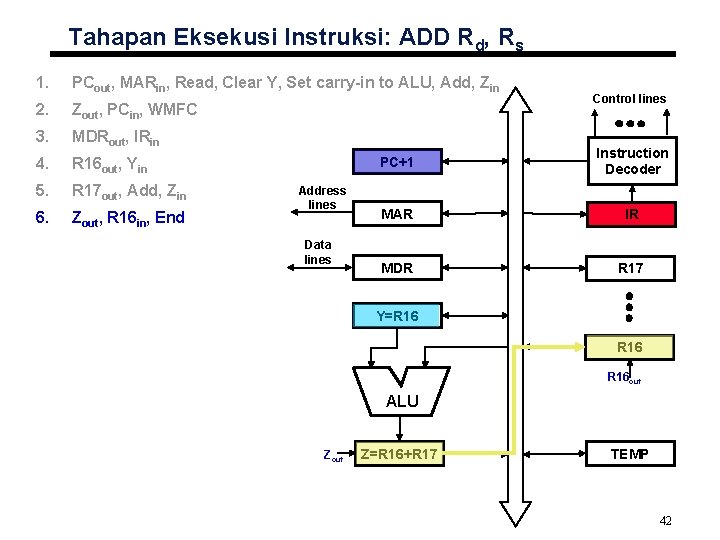

Tahapan Eksekusi Instruksi: ADD Rd, Rs Instruksi: ADD R 16, R 17 ; R 16 + R 17 Langkah-langkah: 1. Fetch instruksi 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 2. Fetch operand ke-1 (R 16) 4. R 16 out, Yin 3. Fetch operand ke-2 (R 17) dan Lakukan operasi ALU 5. R 17 out, Add, Zin 4. Simpan hasil penjumlahan di R 16 6. Zout, R 16 in, End 36

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Control lines Read Instruction Decoder PC Address lines Data lines Clear Y PCout MAR IR MARin MDR R 17 0000 Y R 16 Add ALU 1 Set PC+1 Carry-in Z TEMP Zin 37

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Control lines WMFC PC Address lines Data lines Instruction Decoder PCin MAR IR MDR R 17 Y R 16 ALU Z = PC+1 TEMP Zout 38

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Address lines Data lines Control lines PC+1 Instruction Decoder MAR IR IRin MDR R 17 MDRout Y R 16 ALU Z TEMP 39

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Address lines Data lines Yin Control lines PC+1 Instruction Decoder MAR IR MDR R 17 Y R 16 out ALU Z TEMP 40

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Address lines Data lines Control lines PC+1 Instruction Decoder MAR IR MDR R 17 out Y=R 16 Add Zin ALU Z TEMP 41

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Address lines Data lines Control lines PC+1 Instruction Decoder MAR IR MDR R 17 Y=R 16 out ALU Zout Z=R 16+R 17 TEMP 42

Peningkatan Kinerja Prosesor

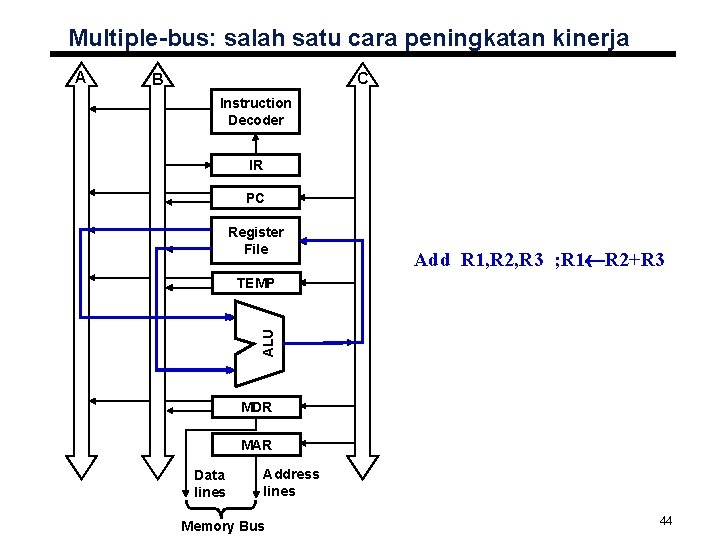

Multiple-bus: salah satu cara peningkatan kinerja C B Instruction Decoder IR PC Register File Add R 1, R 2, R 3 ; R 1 R 2+R 3 TEMP ALU A MDR MAR Data lines Address lines Memory Bus 44

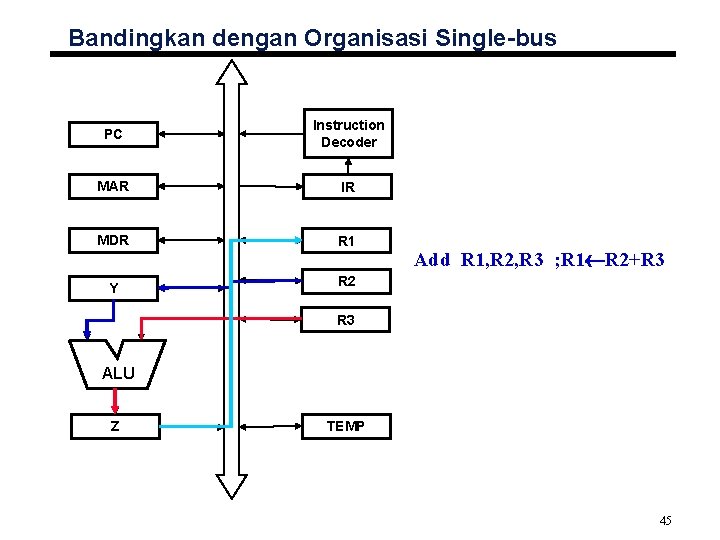

Bandingkan dengan Organisasi Single-bus PC Instruction Decoder MAR IR MDR R 1 Y Add R 1, R 2, R 3 ; R 1 R 2+R 3 R 2 R 3 ALU Z TEMP 45

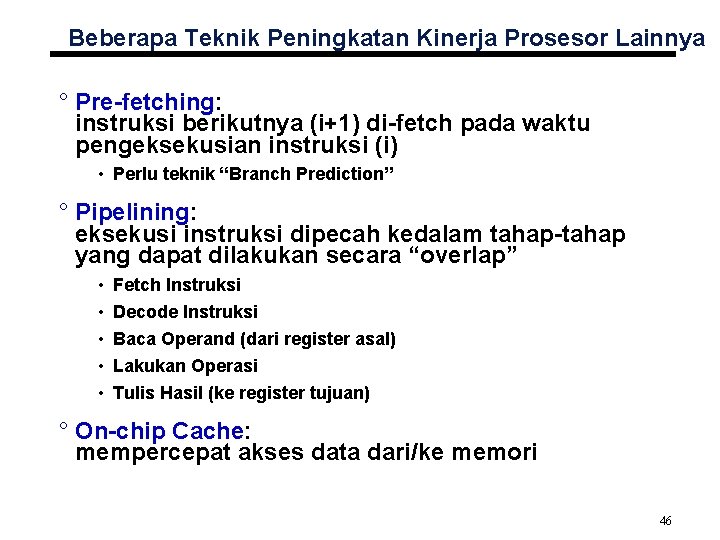

Beberapa Teknik Peningkatan Kinerja Prosesor Lainnya ° Pre-fetching: instruksi berikutnya (i+1) di-fetch pada waktu pengeksekusian instruksi (i) • Perlu teknik “Branch Prediction” ° Pipelining: eksekusi instruksi dipecah kedalam tahap-tahap yang dapat dilakukan secara “overlap” • • • Fetch Instruksi Decode Instruksi Baca Operand (dari register asal) Lakukan Operasi Tulis Hasil (ke register tujuan) ° On-chip Cache: mempercepat akses data dari/ke memori 46

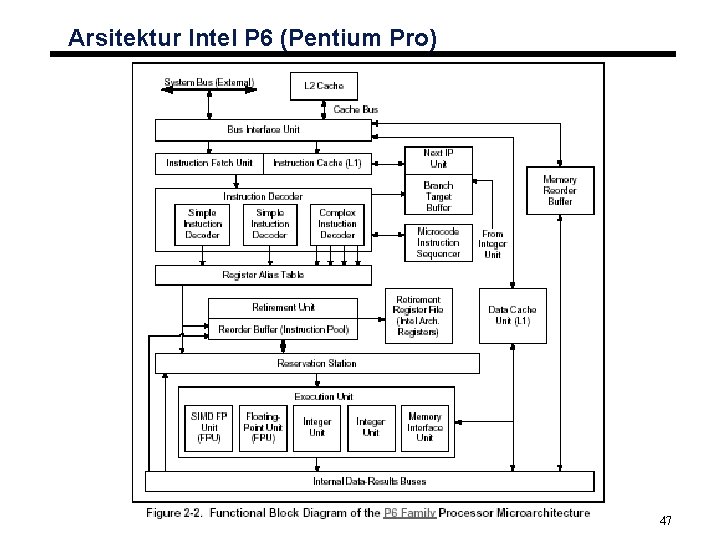

Arsitektur Intel P 6 (Pentium Pro) 47

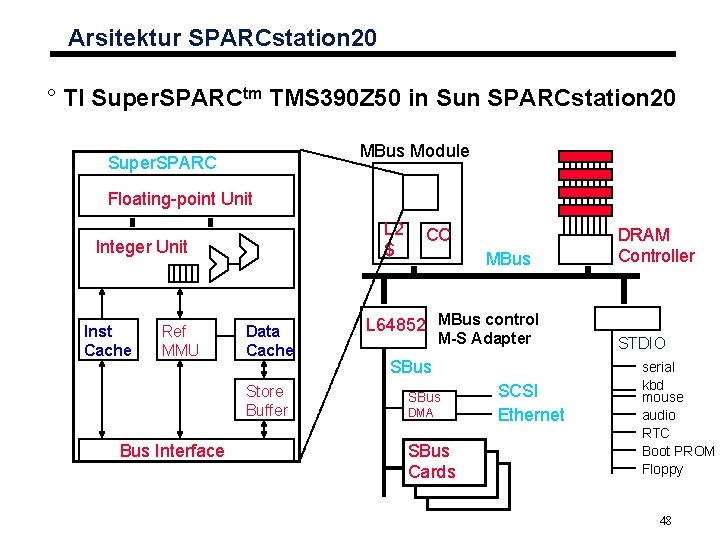

Arsitektur SPARCstation 20 ° TI Super. SPARCtm TMS 390 Z 50 in Sun SPARCstation 20 MBus Module Super. SPARC Floating-point Unit L 2 $ Integer Unit Inst Cache Ref MMU Data Cache Store Buffer Bus Interface CC MBus L 64852 MBus control M-S Adapter SBus DMA SBus Cards SCSI Ethernet DRAM Controller STDIO serial kbd mouse audio RTC Boot PROM Floppy 48

- Slides: 48