IKI 10230 Pengantar Organisasi Komputer Bab 6 Aritmatika

IKI 10230 Pengantar Organisasi Komputer Bab 6: Aritmatika Sumber: 1. Hamacher. Computer Organization, ed-5. 2. Materi kuliah CS 61 C/2000 & CS 152/1997, UCB. 7 & 14 Mei 2003 Bobby Nazief (nazief@cs. ui. ac. id) Qonita Shahab (niet@cs. ui. ac. id) bahan kuliah: http: //www. cs. ui. ac. id/kuliah/iki 10230/

Number Representation

How to Represent Negative Numbers? ° So far, unsigned numbers ° Obvious solution: define leftmost bit to be sign! • 0 => +, 1 => • Rest of bits can be numerical value of number ° Representation called sign and magnitude 3

Shortcomings of sign and magnitude? ° Arithmetic circuit more complicated • Special steps depending whether signs are the same or not ° Also, Two zeros • 0 x 0000 = +0 ten • 0 x 80000000 = -0 ten • What would it mean for programming? ° Sign and magnitude abandoned 4

Another try: complement the bits ° Example: 710 = 001112 -710 = 110002 ° Called one’s Complement ° Note: postive numbers have leading 0 s, negative numbers have leadings 1 s. 000001. . . 01111 10000. . . 11110 11111 ° What is -00000 ? ° How many positive numbers in N bits? ° How many negative ones? 5

Shortcomings of ones complement? ° Arithmetic not too hard ° Still two zeros • 0 x 0000 = +0 ten • 0 x. FFFF = -0 ten • What would it mean for programming? ° One’s complement eventually abandoned because another solution was better 6

Search for Negative Number Representation ° Obvious solution didn’t work, find another ° What is result for unsigned numbers if tried to subtract large number from a small one? • Would try to borrow from string of leading 0 s, so result would have a string of leading 1 s • With no obvious better alternative, pick representation that made the hardware simple: leading 0 s positive, leading 1 s negative • 000000. . . xxx is >=0, 111111. . . xxx is < 0 ° This representation called two’s complement 7

Two’s Complement Number line 11111 000001 ° 2 N-1 non-negatives N-1 negatives 11110 00010 ° 2 -1 0 1 2 -2 ° one zero ° how many positives? . . . ° comparison? ° overflow? -15 -16 15 10001 10000 01111 8

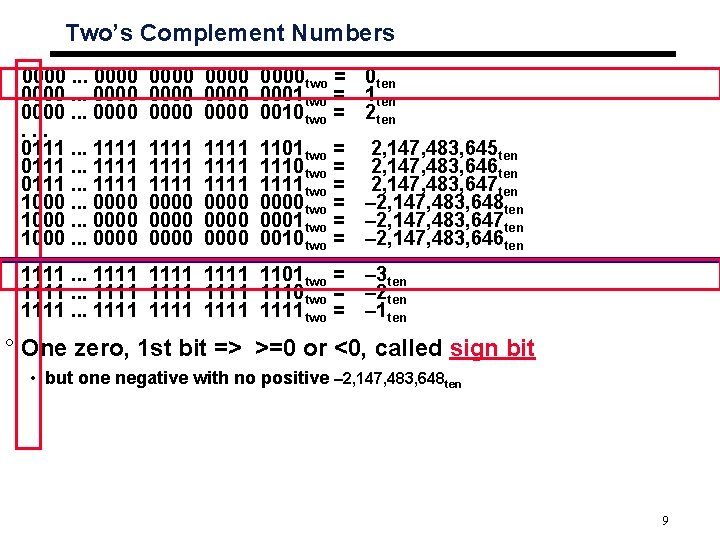

Two’s Complement Numbers 0000. . . 0111. . . 1111 1000. . . 0000. . . 1111 0000 two = 0 ten 0000 0001 two = 1 ten 0000 0010 two = 2 ten 1111 1111 0000 0000 1101 two = 1110 two = 1111 two = 0000 two = 0001 two = 0010 two = 1111 1101 two = 1111 1110 two = 1111 two = 2, 147, 483, 645 ten 2, 147, 483, 646 ten 2, 147, 483, 647 ten – 2, 147, 483, 648 ten – 2, 147, 483, 647 ten – 2, 147, 483, 646 ten – 3 ten – 2 ten – 1 ten ° One zero, 1 st bit => >=0 or <0, called sign bit • but one negative with no positive – 2, 147, 483, 648 ten 9

Two’s Complement Formula ° Can represent positive and negative numbers in terms of the bit value times a power of 2: • d 31 x -231 + d 30 x 230 +. . . + d 2 x 22 + d 1 x 21 + d 0 x 20 ° Example 1111 1111 1100 two = 1 x-231 +1 x 230 +1 x 229+. . . +1 x 22+0 x 21+0 x 20 = -231 + 230 + 229 +. . . + 22 + 0 = -2, 147, 483, 648 ten + 2, 147, 483, 644 ten = -4 ten ° Note: need to specify width: we use 32 bits 10

Two’s complement shortcut: Negation ° Invert every 0 to 1 and every 1 to 0, then add 1 to the result • • Sum of number and its one’s complement must be 111. . . 111 two= -1 ten Let x’ mean the inverted representation of x Then x + x’ = -1 x + x’ + 1 = 0 x’ + 1 = -x ° Example: -4 to +4 to -4 x : 1111 1111 1100 two x’: 0000 0000 0011 two +1: 0000 0000 0100 two ()’: 1111 1111 1011 two +1: 1111 1111 1100 two 11

Two’s comp. shortcut: Sign extension ° Convert 2’s complement number using n bits to more than n bits ° Simply replicate the most significant bit (sign bit) of smaller to fill new bits • 2’s comp. positive number has infinite 0 s • 2’s comp. negative number has infinite 1 s • Bit representation hides leading bits; sign extension restores some of them • 16 -bit -4 ten to 32 -bit: 1111 1100 two 1111 1111 1100 two 12

Distribusi Nilai UTS 13

Addition of Positive Numbers

One-Bit Full Adder (1/3) ° Example Binary Addition: a: 0 0 1 1 b: 0 1 Sum: 1 0 0 0 Carries ° Thus for any bit of addition: • The inputs are ai, bi, Carry. Ini • The outputs are Sumi, Carry. Outi ° Note: Carry. Ini+1 = Carry. Outi 15

One-Bit Full Adder (2/3) Definition Sum = ABC ¯ ¯ in + ABC ¯ ¯in + ABCin Carry. Out = AB + ACin + BCin 16

One-Bit Full Adder (3/3) ° To create one-bit full adder: • implement gates for Sum • implement gates for Carry. Out • connect all inputs with same name Carry. In A B + Sum Carry. Out 17

Ripple-Carry Adders: adding n-bits numbers Carry. In 0 A 0 B 0 A 1 B 1 A 2 B 2 A 3 B 3 1 -bit Sum 0 FA Carry. In 1 Carry. Out 0 1 -bit Sum 1 FA Carry. In 2 Carry. Out 1 1 -bit Sum 2 FA Carry. In 3 Carry. Out 2 1 -bit FA Sum 3 Carry. Out 3 ° Critical Path of n-bit Rippled-carry adder is n*CP • CP = 2 gate-delays (Cout = AB + ACin + BCin) 18

Fast Adders

Carry Look Ahead: reducing Carry Propagation delay Cin A 0 B 0 S 0 G P C 1 = G 0 + C 0 P 0 A B S G P A B A 0 0 1 1 = A 0 B 0 + C 0 (A 0+B 0) B 0 1 C-out 0 “kill” C-in “propagate” 1 “generate” P=A+B G=A B C 2 = G 1 + G 0 P 1 + C 0 P 1 S G P C 3 = G 2 + G 1 P 2 + G 0 P 1 P 2 + C 0 P 1 P 2 A B S G = G 3 + P 3·G 2 + P 3·P 2·G 1 + P 3·P 2·P 1·G 0 P = P 3·P 2·P 1·P 0 G P C 4 =. . . 20

Carry Look Ahead: Delays ° Expression for any carry: • Ci+1 = Gi + Pi. Gi-1 + … + Pi. Pi-1 … P 0 C 0 ° All carries can be obtained in 3 gate-delays: • 1 needed to developed all Pi and Gi • 2 needed in the AND-OR circuit ° All sums can be obtained in 6 gate-delays: • 3 needed to obtain carries ¯ in + ¯ABC ¯ in + ABC ¯ ¯ in + ABCin Sum = ¯ABC • 1 needed to invert carry • 2 needed in the AND-OR circuit of Sum’s circuit ° Independent of the number of bits (n) ° 4 -bit Adder: • CLA: 6 gate-delays • RC: (3*2 + 3) gate-delays ° 16 -bit Adder: • CLA: 6 gate-delays • RC: (15*2 + 3) gate-delays 21

Cascaded CLA: overcoming Fan-in constraint C L A C 0 G 0 P 0 C 1 = G 0 + C 0 P 0 Delay = 3 + 2 + 3 = 8 4 -bit Adder Delay. RC = 15*2 + 3 = 33 C 2 = G 1 + G 0 P 1 + C 0 P 1 4 -bit Adder C 3 = G 2 + G 1 P 2 + G 0 P 1 P 2 + C 0 P 1 P 2 G P 4 -bit Adder C 4 =. . . 22

Signed Addition & Subtraction

Addition & Subtraction Operations ° Subtraction: ° Addition: • Just add the two numbers • Ignore the Carry-out from MSB • Result will be correct, provided there’s no overflow • Form 2’s complement of the subtrahend • Add the two numbers as in Addition 0 1 (+5) +0 0 1 0 (+2) 0 1 1 1 (+7) 0 1 (+5) +1 0 (-6) 1 1 (-1) 0 0 1 0 (+2) 0 1 0 0 (+4) 1 0 1 1 (-5) +1 1 1 0 (-2) 11 0 0 1 (-7) 0 1 1 1 (+7) +1 1 0 1 (-3) 10 1 0 0 (+4) 1 1 1 0 (-2) 1 0 1 1 (-5) 0010 +1 1 0 0 (-4) 1 1 1 0 (-2) 1110 +0 1 (+5) 10 0 1 1 (+3) 24

Overflow Decimal 0 1 2 3 4 5 6 7 Binary 0000 0001 Decimal 0 -1 2’s Complement 0000 1111 0010 0011 0100 0101 0110 0111 -2 -3 -4 -5 -6 -7 -8 1110 1101 1100 1011 1010 1001 1000 ° Examples: 7 + 3 = 10 but. . . -4 5 = -9 ° 0 + but. . . 1 1 0 1 1 1 0 0 1 1 7 3 1 0 – 6 + 1 1 0 0 1 1 – 4 – 5 0 1 1 1 7 25

Overflow Detection ° Overflow: the result is too large (or too small) to represent properly • Example: - 8 < = 4 -bit binary number <= 7 ° When adding operands with different signs, overflow cannot occur! ° Overflow occurs when adding: • 2 positive numbers and the sum is negative • 2 negative numbers and the sum is positive ° On your own: Prove you can detect overflow by: • Carry into MSB ° Carry out of MSB 0 + 1 1 0 1 1 1 0 0 1 1 7 3 1 0 – 6 + 0 1 1 0 0 1 1 – 4 – 5 0 1 1 1 7 26

Overflow Detection Logic ° Carry into MSB ° Carry out of MSB • For a N-bit Adder: Overflow = Carry. In[N - 1] XOR Carry. Out[N - 1] Carry. In 0 A 0 B 0 A 1 B 1 A 2 B 2 A 3 B 3 1 -bit Result 0 FA Carry. In 1 Carry. Out 0 1 -bit Result 1 FA Carry. In 2 Carry. Out 1 1 -bit FA Carry. In 3 1 -bit FA X Y X XOR Y 0 0 1 1 0 1 0 1 1 0 Result 2 Overflow Result 3 Carry. Out 3 27

Arithmetic & Branching Conditions

Condition Codes ° CC Flags will be set/cleared by arithmetic operations: • • N (negative): 1 if result is negative (MSB = 1), otherwise 0 C (carry): 1 if carry-out(borrow) is generated, otherwise 0 V (overflow): 1 if overflow occurs, otherwise 0 Z (zero): 1 if result is zero, otherwise 0 0 1 (+5) +1 0 (-6) 1 1 (-1) 0 1 (+5) +0 1 0 0 (+4) 1 0 0 1 (-7? ) 0 1 1 1 (+7) +1 1 0 1 (-3) 10 1 0 0 (+4) 0 0 1 1 (+3) +1 1 0 1 (-3) 10 0 (0) 29

Multiplication of Positive Numbers

Unsigned Multiplication ° Paper and pencil example (unsigned): Multiplicand Multiplier Product 1101 0000 1101 10001111 1101 (13) 1011 (11) (143) ° m bits x n bits = m+n bit product ° Binary makes it easy: • 0 => place 0 ( 0 x multiplicand) • 1 => place a copy ( 1 x multiplicand) 31

Unsigned Combinational Multiplier 0 A 3 A 3 P 7 P 6 A 2 A 1 P 5 A 2 A 1 0 A 0 B 1 A 0 B 2 A 0 P 4 B 3 P 2 P 1 P 0 ° Stage i accumulates A * 2 i if Bi == 1 32

How does it work? 0 0 0 A 3 A 3 P 7 P 6 A 2 P 5 A 2 A 1 P 4 0 A 3 A 2 A 1 0 A 0 B 1 A 0 B 2 A 0 P 3 B 0 B 3 P 2 P 1 P 0 ° at each stage shift A left ( x 2) ° use next bit of B to determine whether to add in shifted multiplicand ° accumulate 2 n bit partial product at each stage 33

Multiplier Circuit Multiplicand 4 bits 0 MUX Shift Right 4 -bit FA Control Add/No. Add C 4 bits Product (Multiplier) 8 bits Multiplicand 1101 C Product 0 0000 Multiplier 1011 0 1101 0 0110 1011 1101 Add Shift 1 0011 0 1001 1110 Add Shift 0 1001 0 0100 1111 No. Add Shift 1 0001 0 1000 1111 Add Shift 34

Signed-Operand & Multiplication

Signed Multiplication ° Negative Multiplicand: Multiplicand Multiplier Product 10011 (-13) 01011 (+11) 1111110011 000000 1101110001 (-143) ° Negative Multiplier: • Form 2’s complement of both multiplier and multiplicand • Proceed as above 36

Motivation for Booth’s Algorithm ° Works well for both Negative & Positive Multipliers ° Example 2 x 6 = 0010 x 0110: 0010 x 0110 + 0000 + 0010 + 0100 + 00001100 shift (0 in multiplier) add (1 in multiplier) shift (0 in multiplier) ° FA with add or subtract gets same result in more than one way: 6 = – 2 + 8 0110 = – 00010 + 01000 = 11110 + 01000 ° For example ° x + 0010 0110 0000 shift (0 in multiplier) 1111110 sub (first 1 in multpl. ) 000000 shift (mid string of 1 s) 00010 add (prior step had last 1) 00001100 37

Booth’s Algorithm Current Bit to the Right. Explanation Example 1 0 Begins run of 1 s 0001111000 sub 1 1 Middle of run of 1 s 0001111000 none 0 1 End of run of 1 s 0001111000 add 0 0 Middle of run of 0 s 0001111000 none Op Originally for Speed (when shift was faster than add) • Small number of additions needed when multiplier has a few large blocks of 1 s 38

Booths Example (2 x 7) Operation Multiplicand Product next? 0. initial value 0010 0000 0111 0 10 -> sub 1 a. P = P - m 1110 0111 0 + 1110 shift P (sign ext) 1 b. 0010 1111 0011 1 11 -> nop, shift 2. 0010 1111 1001 1 11 -> nop, shift 3. 0010 1111 1100 1 01 -> add 4 a. 0010 4 b. 0010 + 0010 0001 1100 1 shift 0000 1110 0 done 39

Booths Example (2 x -3) Operation Multiplicand 0. initial value 0010 1 a. P = P - m 1110 1101 0 Product next? 0000 1101 0 + 1110 shift P (sign ext) 1 b. 0010 + 0010 1111 0110 1 01 -> add 2 a. 0001 0110 1 shift P 2 b. + 0010 1110 0000 1011 0 10 -> sub 3 a. 0010 1110 1011 0 shift 3 b. 4 a 0010 1111 0101 1 shift 4 b. 0010 1111 1010 1 10 -> sub 11 -> nop done 40

Fast Multiplication (read yourself!)

Integer Division

Divide: Paper & Pencil Divisor 1000 1001 Quotient 1001010 – 1000 10 Dividend Remainder (or Modulo result) ° See how big a number can be subtracted, creating quotient bit on each step Binary => 1 * divisor or 0 * divisor ° Dividend = Quotient x Divisor + Remainder => | Dividend | = | Quotient | + | Divisor | 43

Division Circuit Divisor 33 bits Shift Left 33 -bit FA 33 bits Remainder (Quotient) 65 bits Control Q Setting Sign-bit Checking 44

Restoring Division Algorithm Remainder Quotient Divisor 0010 11 1000 11 10 Quotient Dividend Remainder Initially 00000 1000 Shift 00001 Sub(-11) Set q 0 Restore 000_ 11101 11110 00001 0000 Shift 00010 Sub(-11) Set q 0 Restore 000_ 11101 11111 00010 0000 Shift 00100 Sub(-11) Set q 0 00001 000_ 11101 0001 Shift 00010 Sub(-11) Set q 0 Restore 001_ 11101 001_ 11111 00010 45

Floating-point Numbers & Operations

Review of Numbers ° Computers are made to deal with numbers ° What can we represent in N bits? • Unsigned integers: 0 to 2 N - 1 • Signed Integers (Two’s Complement) -2(N-1) to 2(N-1) - 1 47

Other Numbers ° What about other numbers? • Very large numbers? (seconds/century) 3, 155, 760, 00010 (3. 1557610 x 109) • Very small numbers? (atomic diameter) 0. 0000000110 (1. 010 x 10 -8) • Rationals (repeating pattern) 2/3 (0. 66666. . . ) • Irrationals 21/2 (1. 414213562373. . . ) • Transcendentals e (2. 718. . . ), (3. 141. . . ) ° All represented in scientific notation 48

Scientific Notation Review mantissa exponent 6. 02 x 1023 decimal point radix (base) ° Normalized form: no leadings 0 s (exactly one digit to left of decimal point) ° Alternatives to representing 1/1, 000, 000 • Normalized: 1. 0 x 10 -9 • Not normalized: 0. 1 x 10 -8, 10. 0 x 10 -10 49

Scientific Notation for Binary Numbers Mantissa exponent 1. 0 two x 2 -1 “binary point” radix (base) ° Computer arithmetic that supports it called floating point, because it represents numbers where binary point is not fixed, as it is for integers • Declare such variable in C as float 50

Floating Point Representation (1/2) ° Normal format: +1. xxxxxtwo*2 yyyytwo ° Multiple of Word Size (32 bits) 31 30 23 22 S Exponent 1 bit 8 bits Significand 23 bits 0 ° S represents Sign Exponent represents y’s Significand represents x’s ° Represent numbers as small as 2. 0 x 10 -38 to as large as 2. 0 x 1038 51

Floating Point Representation (2/2) ° What if result too large? (> 2. 0 x 1038 ) • Overflow! • Overflow => Exponent larger than represented in 8 -bit Exponent field ° What if result too small? (>0, < 2. 0 x 10 -38 ) • Underflow! • Underflow => Negative exponent larger than represented in 8 -bit Exponent field ° How to reduce chances of overflow or underflow? 52

Double Precision Fl. Pt. Representation ° Next Multiple of Word Size (64 bits) 31 30 20 19 S Exponent 1 bit 11 bits Significand 0 20 bits Significand (cont’d) 32 bits ° Double Precision (vs. Single Precision) • C variable declared as double • Represent numbers almost as small as 2. 0 x 10 -308 to almost as large as 2. 0 x 10308 • But primary advantage is greater accuracy due to larger significand 53

IEEE 754 Floating Point Standard (1/4) ° Single Precision, DP similar ° Sign bit: 1 means negative 0 means positive ° Significand: • To pack more bits, leading 1 implicit for normalized numbers • 1 + 23 bits single, 1 + 52 bits double • always true: 0 < Significand < 1 (for normalized numbers) ° Note: 0 has no leading 1, so reserve exponent value 0 just for number 0 54

IEEE 754 Floating Point Standard (2/4) ° Kahan wanted FP numbers to be used even if no FP hardware; e. g. , sort records with FP numbers using integer compares ° Could break FP number into 3 parts: compare signs, then compare exponents, then compare significands ° Wanted it to be faster, single compare if possible, especially if positive numbers ° Then want order: • Highest order bit is sign ( negative < positive) • Exponent next, so big exponent => bigger # • Significand last: exponents same => bigger # 55

IEEE 754 Floating Point Standard (3/4) ° Negative Exponent? • 2’s comp? 1. 0 x 2 -1 v. 1. 0 x 2+1 (1/2 v. 2) 1/2 0 1111 0000 0000 2 0 0001 0000 0000 • This notation using integer compare of 1/2 v. 2 makes 1/2 > 2! ° Instead, pick notation 0000 0001 is most negative, and 1111 is most positive • 1. 0 x 2 -1 v. 1. 0 x 2+1 (1/2 v. 2) 1/2 0 0111 1110 0000 0000 2 0 1000 0000 0000 56

IEEE 754 Floating Point Standard (4/4) ° Called Biased Notation, where bias is number subtract to get real number • IEEE 754 uses bias of 127 for single prec. • Subtract 127 from Exponent field to get actual value for exponent • 1023 is bias for double precision ° Summary (single precision): 31 30 23 22 S Exponent 1 bit 8 bits Significand 23 bits 0 ° (-1)S x (1 + Significand) x 2(Exponent-127) • Double precision identical, except with exponent bias of 1023 57

Special Numbers ° What have we defined so far? Precision) Exponent Significand Object 0 0 1 -254 255 0 nonzero anything 0 nonzero 0 ? ? ? +/- fl. pt. # +/- infinity Na. N (Single 58

Infinity and Na. Ns result of operation overflows, i. e. , is larger than the largest number that can be represented overflow is not the same as divide by zero (raises a different exception) +/- infinity S 1. . . 1 0. . . 0 It may make sense to do further computations with infinity e. g. , X/0 > Y may be a valid comparison Not a number, but not infinity (e. q. sqrt(-4)) invalid operation exception (unless operation is = or =) Na. N S 1. . . 1 non-zero HW decides what goes here Na. Ns propagate: f(Na. N) = Na. N 59

FP Addition ° Much more difficult than with integers ° Can’t just add significands ° How do we do it? • • De-normalize to match exponents Add significands to get resulting one Keep the same exponent Normalize (possibly changing exponent) ° Note: If signs differ, just perform a subtract instead. 60

FP Subtraction ° Similar to addition ° How do we do it? • • De-normalize to match exponents Subtract significands Keep the same exponent Normalize (possibly changing exponent) 61

Extra Bits for rounding "Floating Point numbers are like piles of sand; every time you move one you lose a little sand, but you pick up a little dirt. " How many extra bits? IEEE: As if computed the result exactly and rounded. Addition: 1. xxxxx + 1. xxxxx 1 x. xxxxy post-normalization 1. xxxxx 0. 001 xxxxx 0. 01 xxxxx 1. xxxxxyyy pre-normalization 1 x. xxxxyyy pre and post ° Guard Digits: digits to the right of the first p digits of significand to guard against loss of digits – can later be shifted left into first P places during normalization. ° Addition: carry-out shifted in ° Subtraction: borrow digit and guard ° Multiplication: carry and guard, Division requires guard 62

Rounding Digits normalized result, but some non-zero digits to the right of the significand --> the number should be rounded E. g. , B = 10, p = 3: = 1. 6900 * 102 -bias 0 0 7. 85 = -. 0785 * 10 2 -bias 0 2 1. 61 = 1. 6115 * 10 2 -bias 0 2 1. 69 - one round digit must be carried to the right of the guard digit so that after a normalizing left shift, the result can be rounded, according to the value of the round digit IEEE Standard: four rounding modes: round to nearest (default) round towards plus infinity round towards minus infinity round towards 0 round to nearest: round digit < B/2 then truncate > B/2 then round up (add 1 to ULP: unit in last place) = B/2 then round to nearest even digit it can be shown that this strategy minimizes the mean error introduced by rounding 63

Sticky Bit Additional bit to the right of the round digit to better fine tune rounding d 0. d 1 d 2 d 3. . . dp-1 0 0 0 + 0. 0 0 X. . . X XX S d 0. d 1 d 2 d 3. . . dp-1 0 0 0 - 0. 0 0 X. . . X XX 0 Sticky bit: set to 1 if any 1 bits fall off the end of the round digit d 0. d 1 d 2 d 3. . . dp-1 0 0 0 - 0. 0 0 X. . . X XX 1 generates a borrow Rounding Summary: Radix 2 minimizes wobble in precision Normal operations in +, -, *, / require one carry/borrow bit + one guard digit One round digit needed for correct rounding Sticky bit needed when round digit is B/2 for max accuracy Rounding to nearest has mean error = 0 if uniform distribution of digits are assumed 64

Denormalized Numbers 2 -bias denorm -bias 1 -bias 2 2 0 gap 2 normal numbers with hidden bit --> B = 2, p = 4 The gap between 0 and the next representable number is much larger than the gaps between nearby representable numbers. IEEE standard uses denormalized numbers to fill in the gap, making the distances between numbers near 0 more alike. 0 2 -bias p-1 bits of precision 2 1 -bias 2 2 -bias p bits of precision same spacing, half as many values! NOTE: PDP-11, VAX cannot represent subnormal numbers. These machines underflow to zero instead. 65

- Slides: 65