III Multicore Processors 2 Dezs Sima Spring 2007

- Slides: 35

III. Multicore Processors (2) Dezső Sima Spring 2007 (Ver. 2. 0) Dezső Sima, 2007

10. MC repository • 10. 1 Intel’s MC processors • 10. 2 AMD’s MC processors • 10. 3 IBM’s MC processors • 10. 4 Sun’s MC processors • 10. 5 Fujitsu’s MC processors • 10. 6 HP’s MC processors • 10. 7 RMI’s MC processors

10. 1 Intel’s MC processors • 10. 1. 1 Dual-core mobile processor lines • 10. 1. 2 Dual/quad-core desktop processor lines • 10. 1. 3 Dual/quad-core server processor lines • 10. 1. 4 Dual-core Itanium processor lines

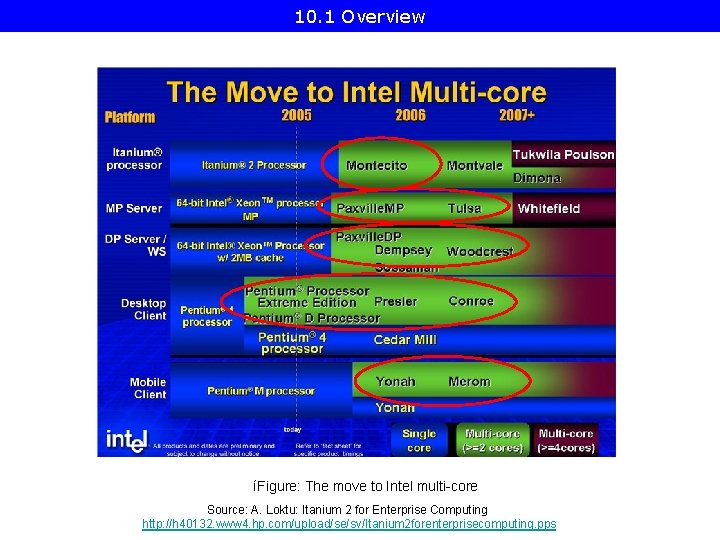

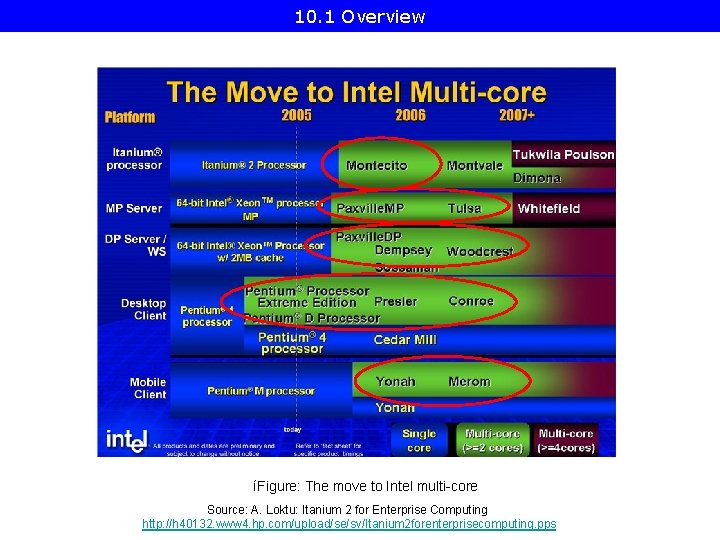

10. 1 Overview íFigure: The move to Intel multi-core Source: A. Loktu: Itanium 2 for Enterprise Computing http: //h 40132. www 4. hp. com/upload/se/sv/Itanium 2 forenterprisecomputing. pps

10. 1 Intel’s MC processors 10. 1. 1 Dual-core mobile processor lines • Core Duo (32 -bit) Yonah Duo 1/2006 65 nm • Core 2 Duo (64 -bit) Merom 7/2006 65 nm (Pentium M based, monolithic) (Core based, monolithic)

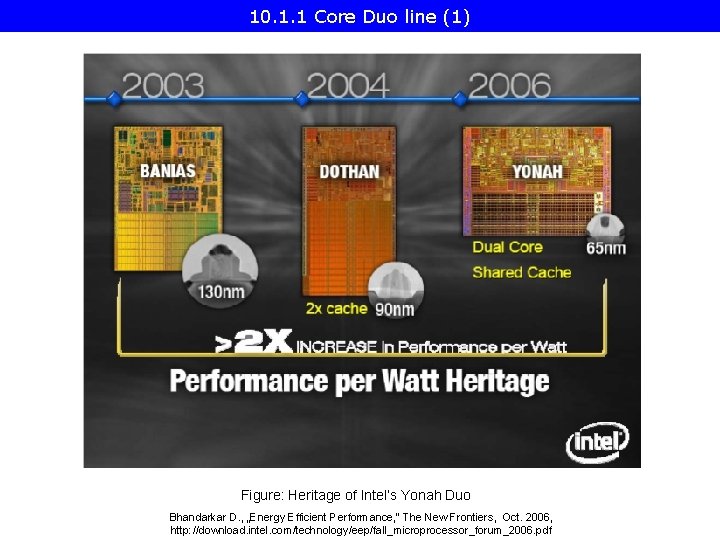

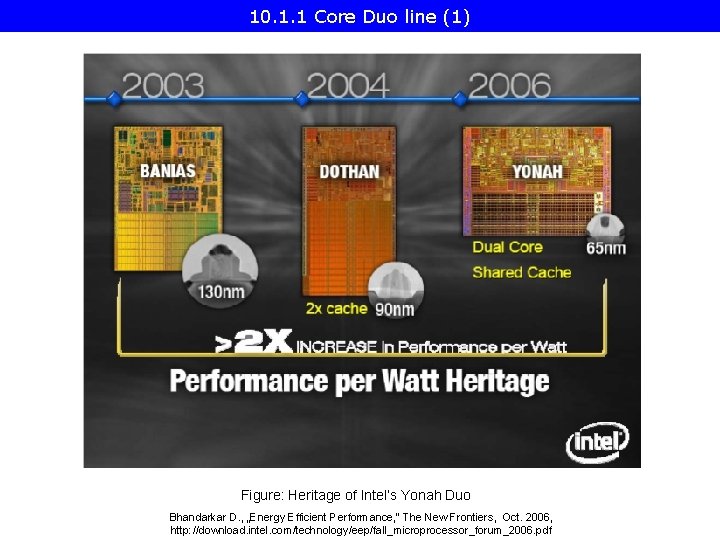

10. 1. 1 Core Duo line (1) Figure: Heritage of Intel’s Yonah Duo Bhandarkar D. , „Energy Efficient Performance, ” The New Frontiers, Oct. 2006, http: //download. intel. com/technology/eep/fall_microprocessor_forum_2006. pdf

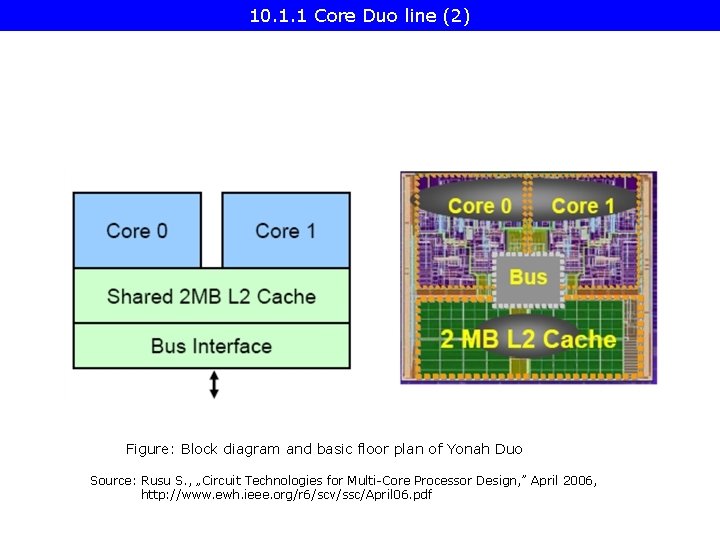

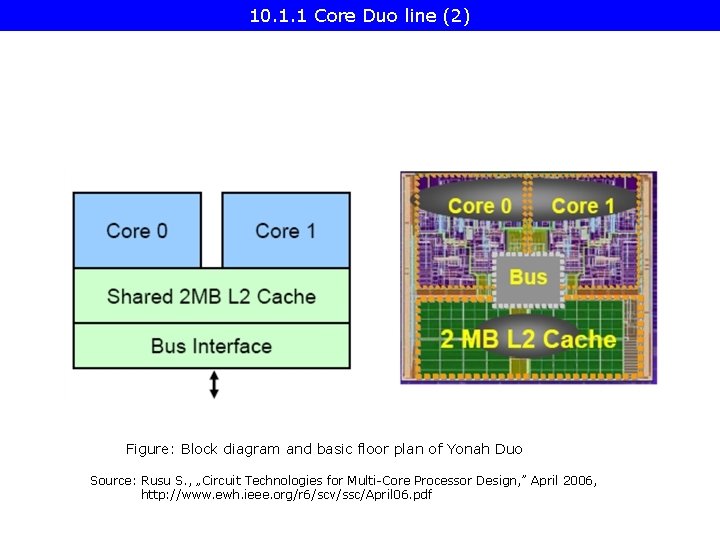

10. 1. 1 Core Duo line (2) Figure: Block diagram and basic floor plan of Yonah Duo Source: Rusu S. , „Circuit Technologies for Multi-Core Processor Design, ” April 2006, http: //www. ewh. ieee. org/r 6/scv/ssc/April 06. pdf

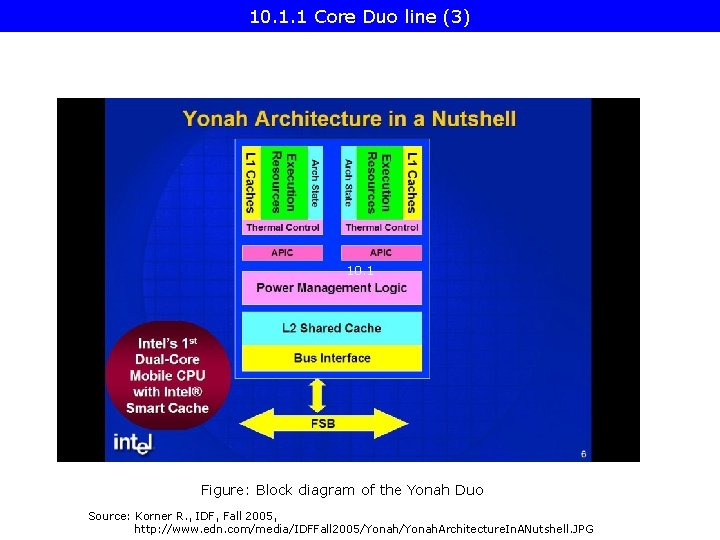

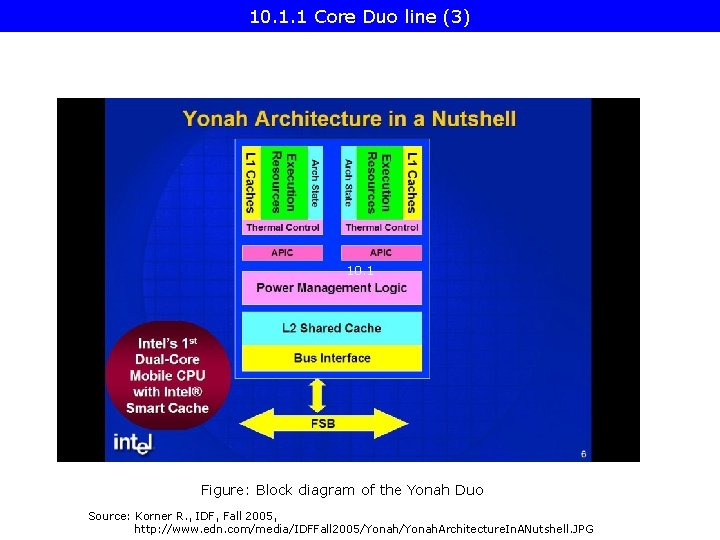

10. 1. 1 Core Duo line (3) 10. 1 Figure: Block diagram of the Yonah Duo Source: Korner R. , IDF, Fall 2005, http: //www. edn. com/media/IDFFall 2005/Yonah. Architecture. In. ANutshell. JPG

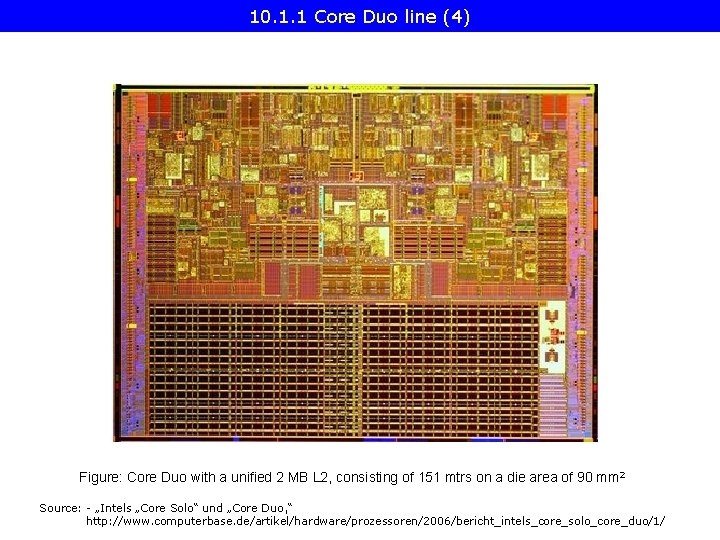

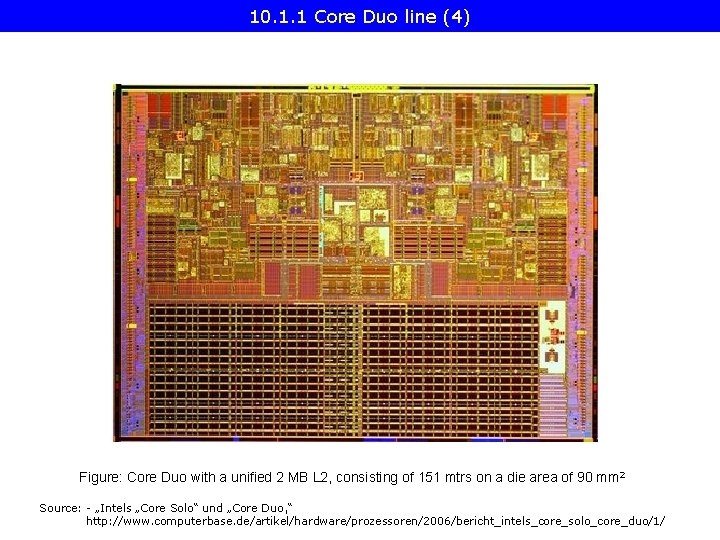

10. 1. 1 Core Duo line (4) Figure: Core Duo with a unified 2 MB L 2, consisting of 151 mtrs on a die area of 90 mm 2 Source: - „Intels „Core Solo“ und „Core Duo, “ http: //www. computerbase. de/artikel/hardware/prozessoren/2006/bericht_intels_core_solo_core_duo/1/

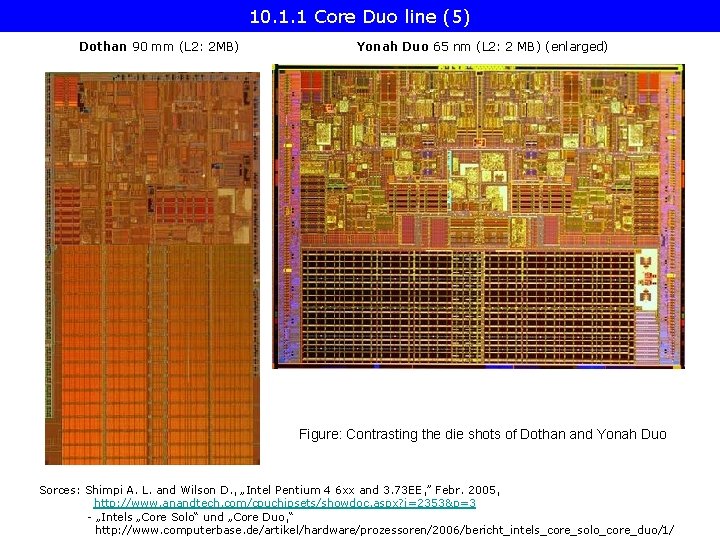

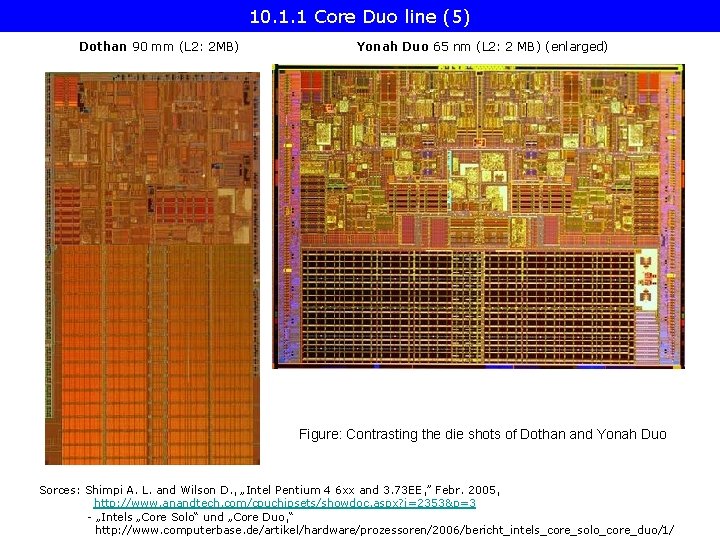

10. 1. 1 Core Duo line (5) Dothan 90 mm (L 2: 2 MB) Yonah Duo 65 nm (L 2: 2 MB) (enlarged) Figure: Contrasting the die shots of Dothan and Yonah Duo Sorces: Shimpi A. L. and Wilson D. , „Intel Pentium 4 6 xx and 3. 73 EE, ” Febr. 2005, http: //www. anandtech. com/cpuchipsets/showdoc. aspx? i=2353&p=3 - „Intels „Core Solo“ und „Core Duo, “ http: //www. computerbase. de/artikel/hardware/prozessoren/2006/bericht_intels_core_solo_core_duo/1/

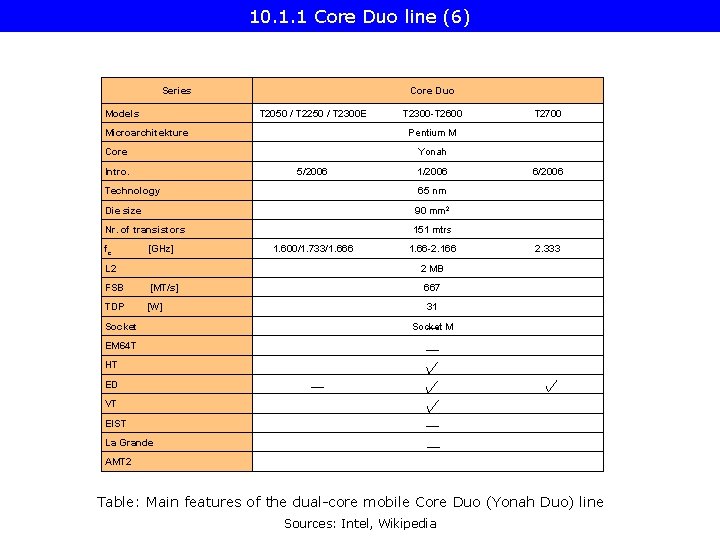

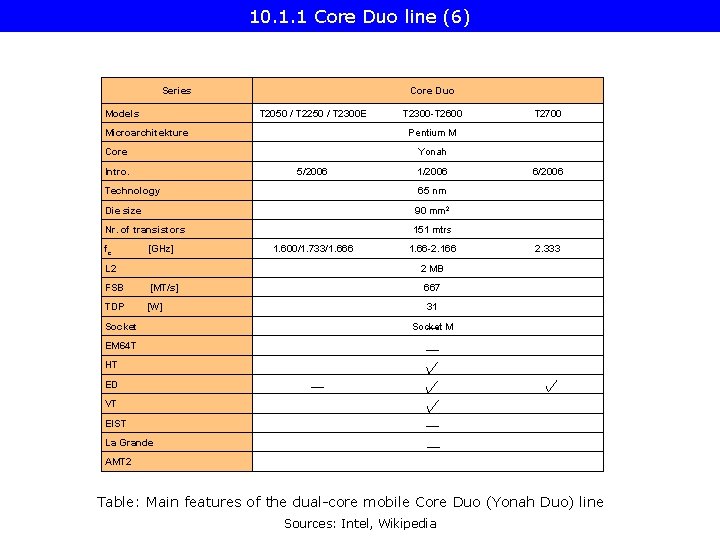

10. 1. 1 Core Duo line (6) Series Models Core Duo T 2050 / T 2250 / T 2300 E Microarchitekture T 2300 -T 2600 Pentium M Core Yonah Intro. 5/2006 Technology 1/2006 90 mm 2 Nr. of transistors 151 mtrs [GHz] L 2 6/2006 65 nm Die size fc T 2700 1. 600/1. 733/1. 666 1. 66 -2. 166 2. 333 2 MB FSB [MT/s] 667 TDP [W] 31 Socket M EM 64 T HT ED VT EIST La Grande AMT 2 Table: Main features of the dual-core mobile Core Duo (Yonah Duo) line Sources: Intel, Wikipedia

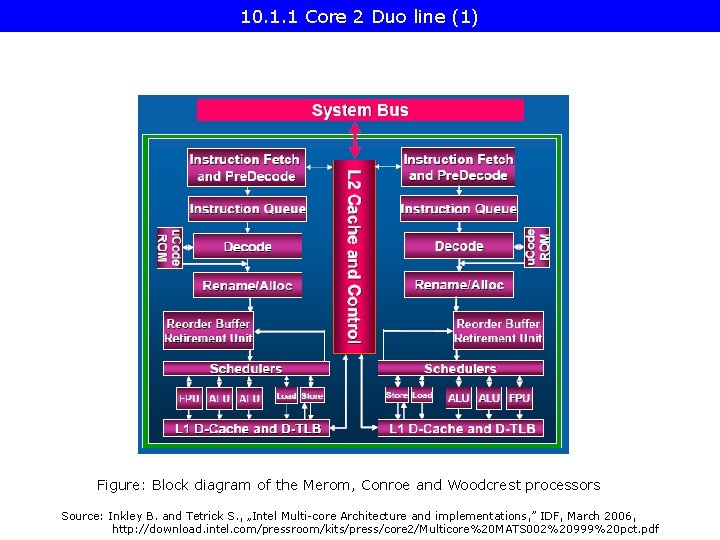

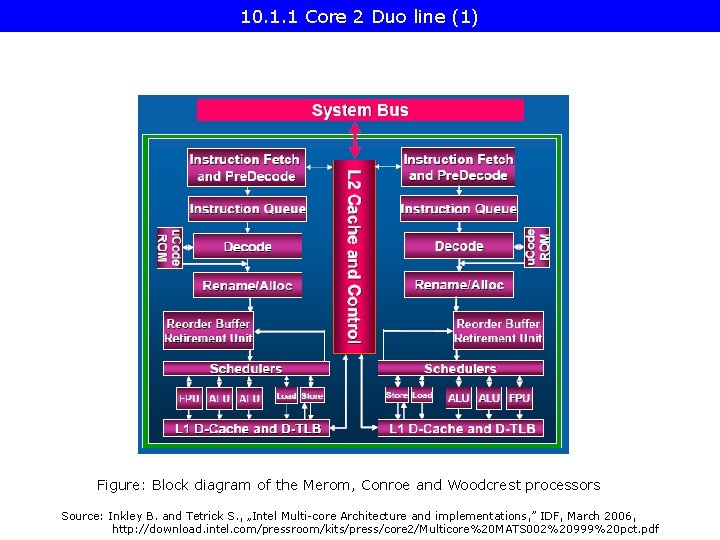

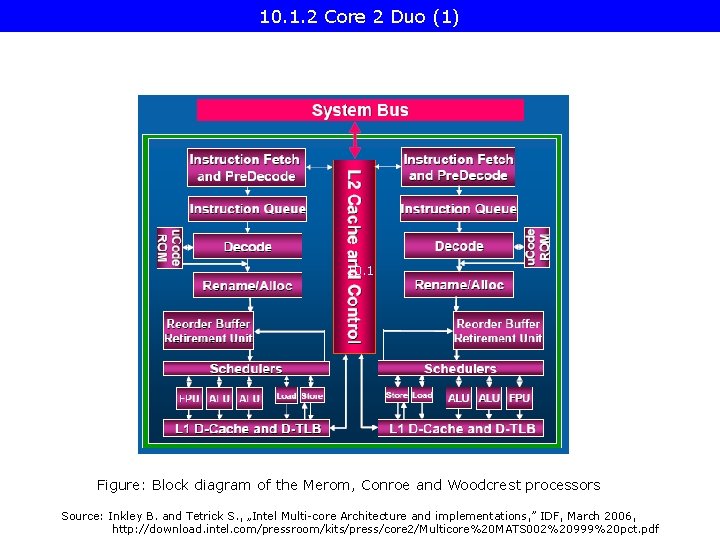

10. 1. 1 Core 2 Duo line (1) Figure: Block diagram of the Merom, Conroe and Woodcrest processors Source: Inkley B. and Tetrick S. , „Intel Multi-core Architecture and implementations, ” IDF, March 2006, http: //download. intel. com/pressroom/kits/press/core 2/Multicore%20 MATS 002%20999%20 pct. pdf

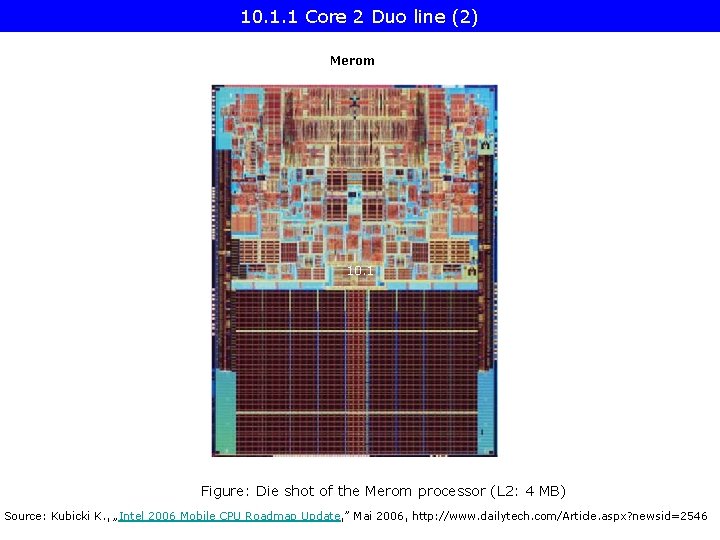

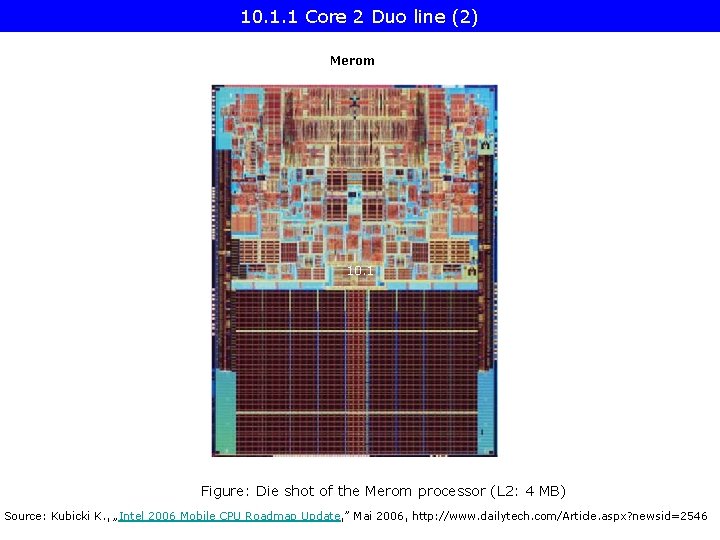

10. 1. 1 Core 2 Duo line (2) Merom 10. 1 Figure: Die shot of the Merom processor (L 2: 4 MB) Source: Kubicki K. , „Intel 2006 Mobile CPU Roadmap Update, ” Mai 2006, http: //www. dailytech. com/Article. aspx? newsid=2546

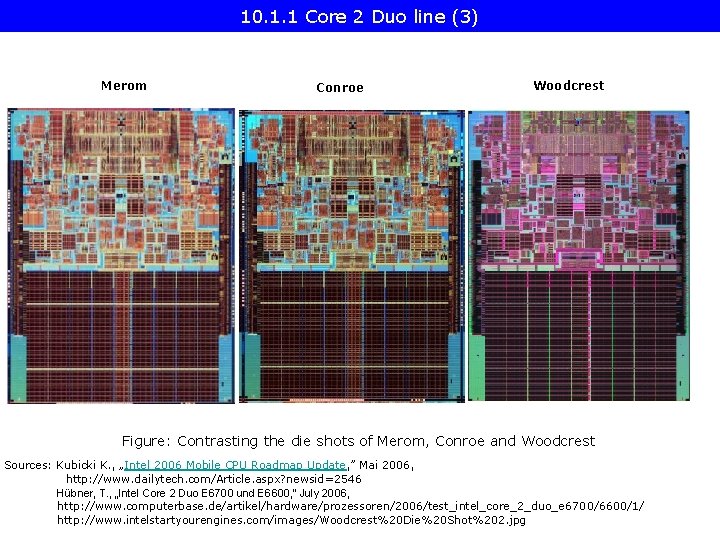

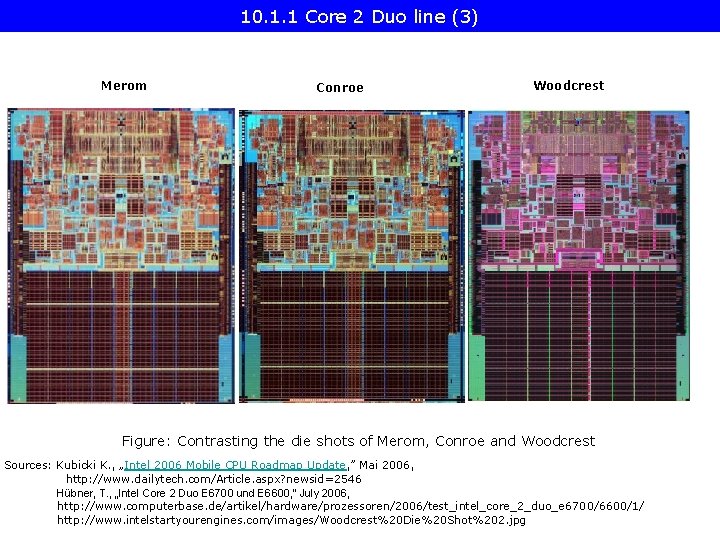

10. 1. 1 Core 2 Duo line (3) Merom Conroe Woodcrest Figure: Contrasting the die shots of Merom, Conroe and Woodcrest Sources: Kubicki K. , „Intel 2006 Mobile CPU Roadmap Update, ” Mai 2006, http: //www. dailytech. com/Article. aspx? newsid=2546 Hübner, T. , „Intel Core 2 Duo E 6700 und E 6600, ” July 2006, http: //www. computerbase. de/artikel/hardware/prozessoren/2006/test_intel_core_2_duo_e 6700/6600/1/ http: //www. intelstartyourengines. com/images/Woodcrest%20 Die%20 Shot%202. jpg

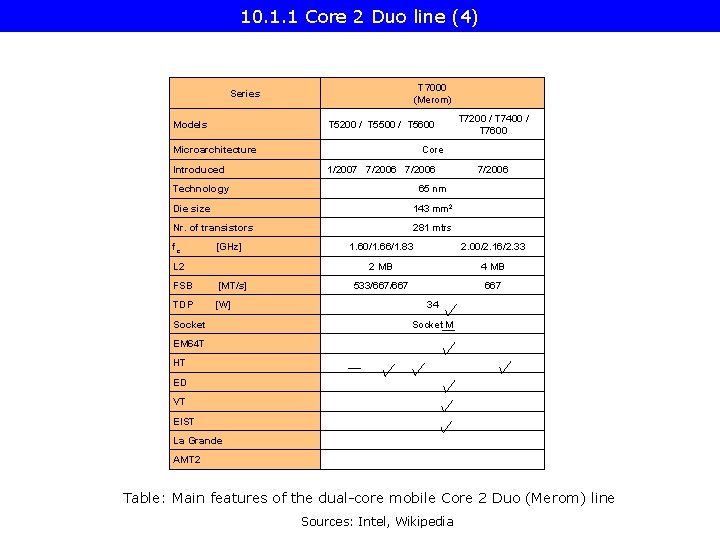

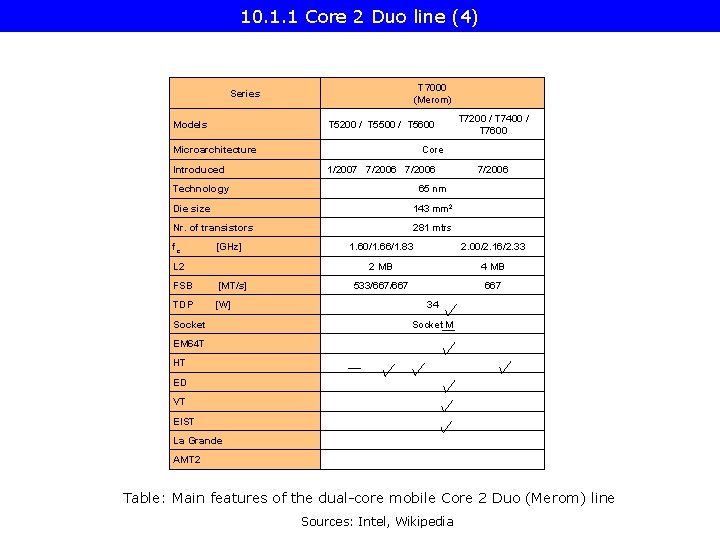

10. 1. 1 Core 2 Duo line (4) T 7000 (Merom) Series Models T 5200 / T 5500 / T 5600 Microarchitecture Introduced Core 1/2007 7/2006 Technology 143 mm 2 Nr. of transistors 281 mtrs [GHz] L 2 FSB [MT/s] TDP [W] Socket 7/2006 65 nm Die size fc T 7200 / T 7400 / T 7600 1. 60/1. 66/1. 83 2. 00/2. 16/2. 33 2 MB 4 MB 533/667 667 34 Socket M EM 64 T HT ED VT EIST La Grande AMT 2 Table: Main features of the dual-core mobile Core 2 Duo (Merom) line Sources: Intel, Wikipedia

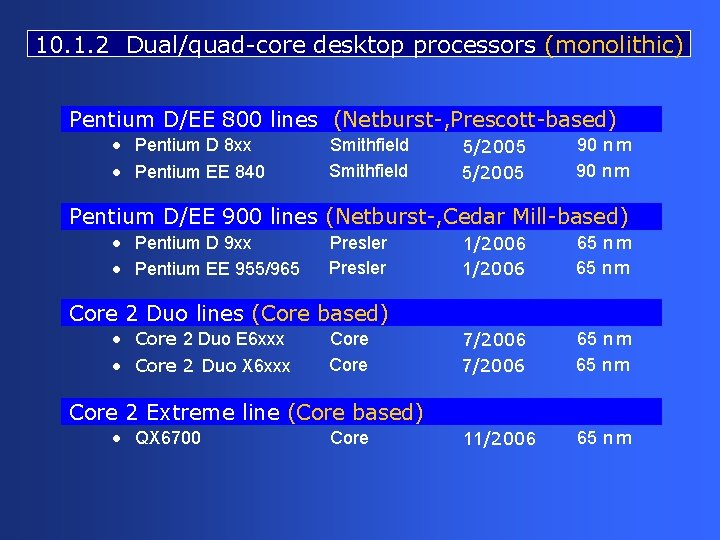

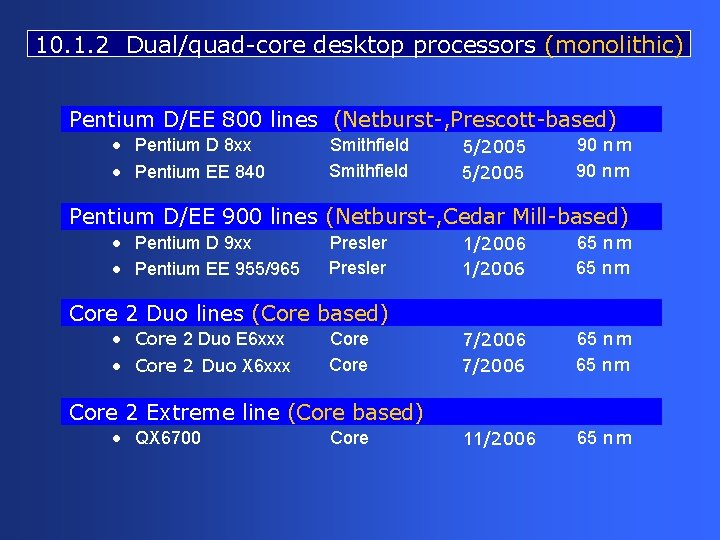

10. 1. 2 Dual/quad-core desktop processors (monolithic) Pentium D/EE 800 lines (Netburst-, Prescott-based) • Pentium D 8 xx • Pentium EE 840 Smithfield 5/2005 90 nm Pentium D/EE 900 lines (Netburst-, Cedar Mill-based) • Pentium D 9 xx • Pentium EE 955/965 Presler 1/2006 65 nm 7/2006 65 nm 11/2006 65 nm Core 2 Duo lines (Core based) • Core 2 Duo E 6 xxx • Core 2 Duo X 6 xxx Core 2 Extreme line (Core based) • QX 6700 Core

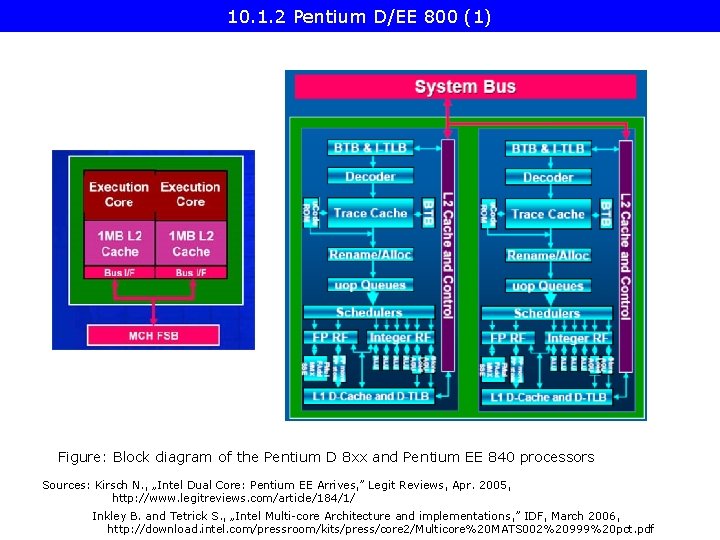

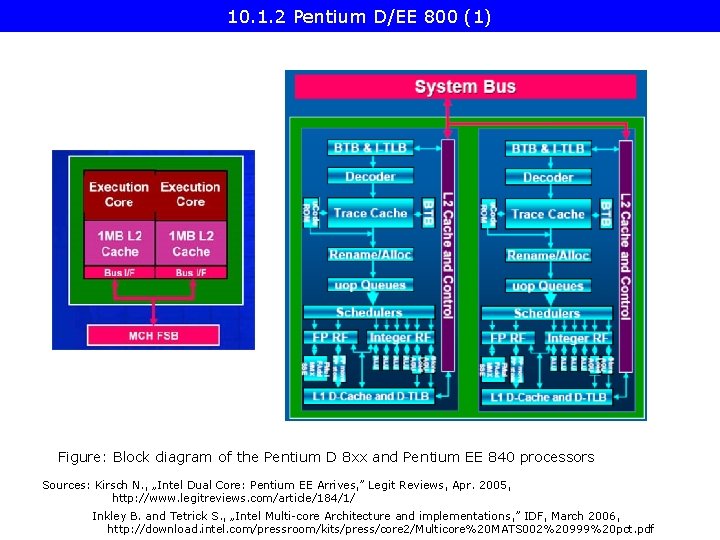

10. 1. 2 Pentium D/EE 800 (1) Figure: Block diagram of the Pentium D 8 xx and Pentium EE 840 processors Sources: Kirsch N. , „Intel Dual Core: Pentium EE Arrives, ” Legit Reviews, Apr. 2005, http: //www. legitreviews. com/article/184/1/ Inkley B. and Tetrick S. , „Intel Multi-core Architecture and implementations, ” IDF, March 2006, http: //download. intel. com/pressroom/kits/press/core 2/Multicore%20 MATS 002%20999%20 pct. pdf

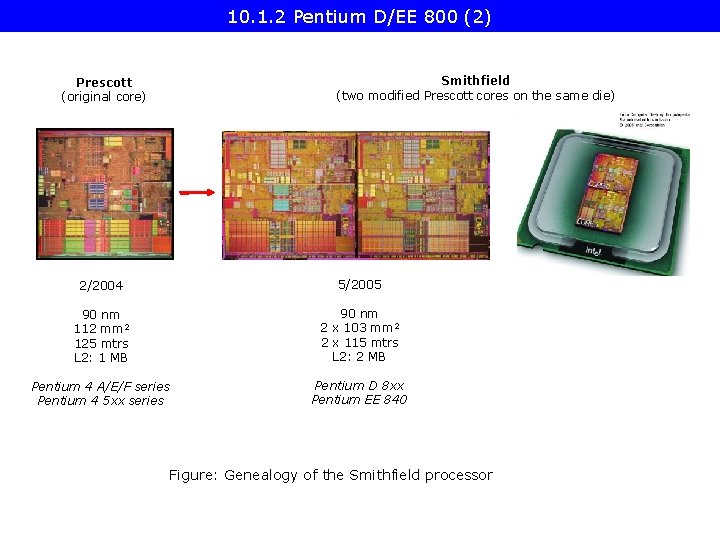

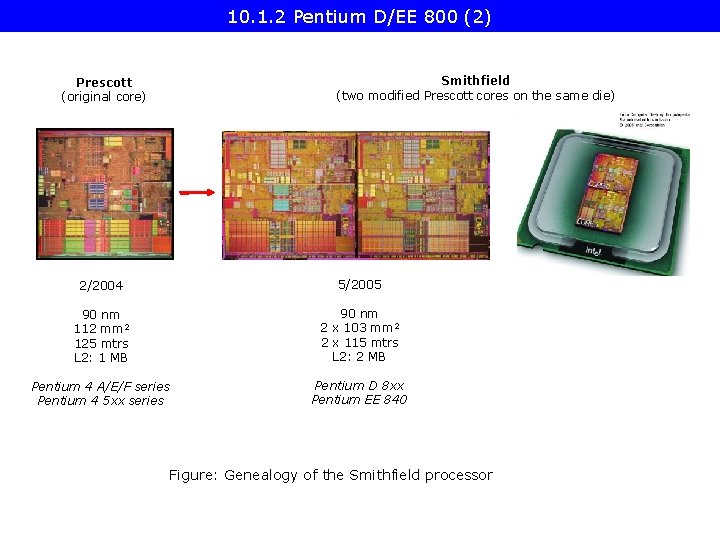

10. 1. 2 Pentium D/EE 800 (2) Smithfield (two modified Prescott cores on the same die) Prescott (original core) 2/2004 5/2005 90 nm 112 mm 2 125 mtrs L 2: 1 MB 90 nm 2 x 103 mm 2 2 x 115 mtrs L 2: 2 MB Pentium 4 A/E/F series Pentium 4 5 xx series Pentium D 8 xx Pentium EE 840 Figure: Genealogy of the Smithfield processor

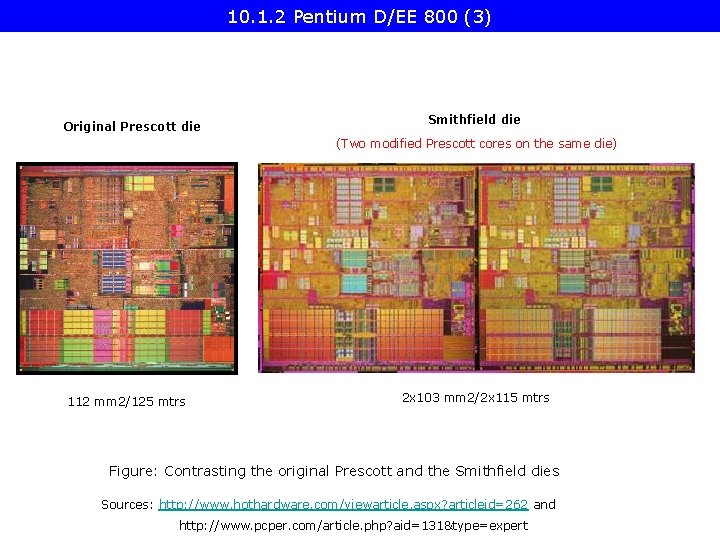

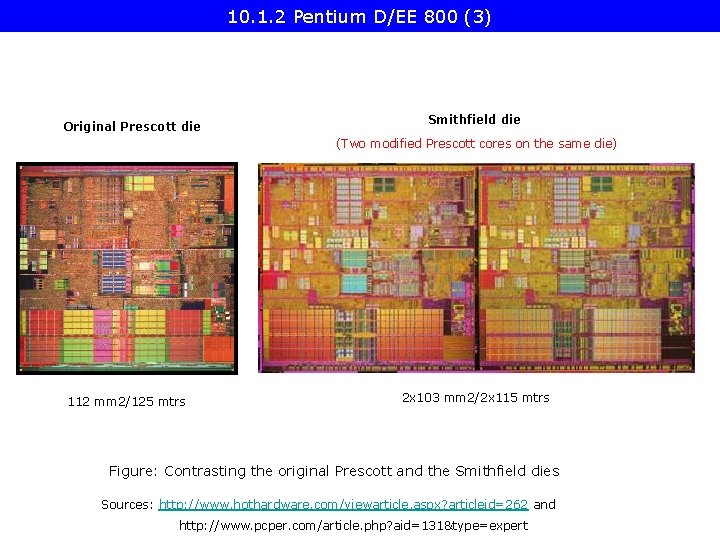

10. 1. 2 Pentium D/EE 800 (3) Original Prescott die Smithfield die (Two modified Prescott cores on the same die) 112 mm 2/125 mtrs 2 x 103 mm 2/2 x 115 mtrs Figure: Contrasting the original Prescott and the Smithfield dies Sources: http: //www. hothardware. com/viewarticle. aspx? articleid=262 and http: //www. pcper. com/article. php? aid=131&type=expert

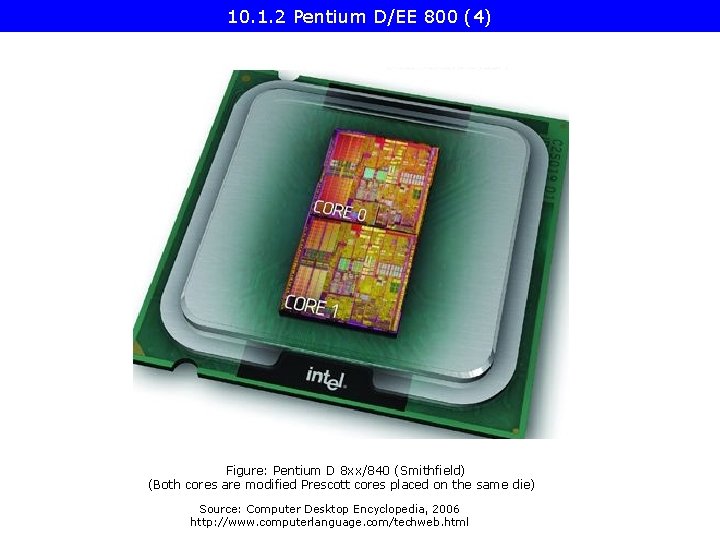

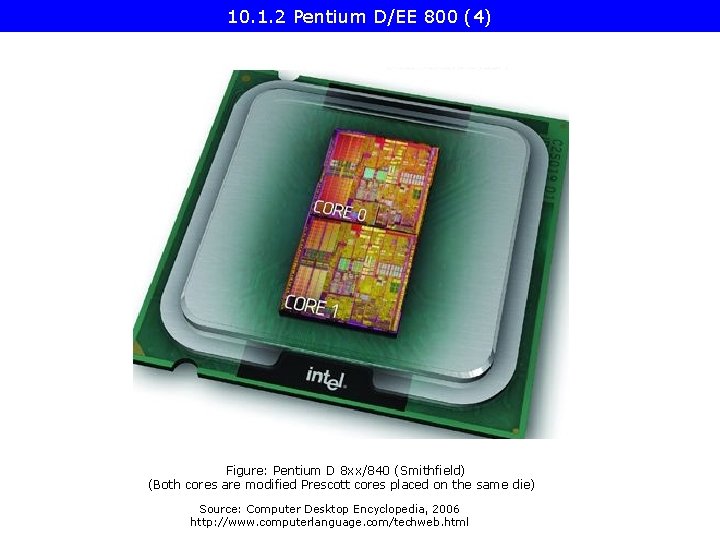

10. 1. 2 Pentium D/EE 800 (4) Figure: Pentium D 8 xx/840 (Smithfield) (Both cores are modified Prescott cores placed on the same die) Source: Computer Desktop Encyclopedia, 2006 http: //www. computerlanguage. com/techweb. html

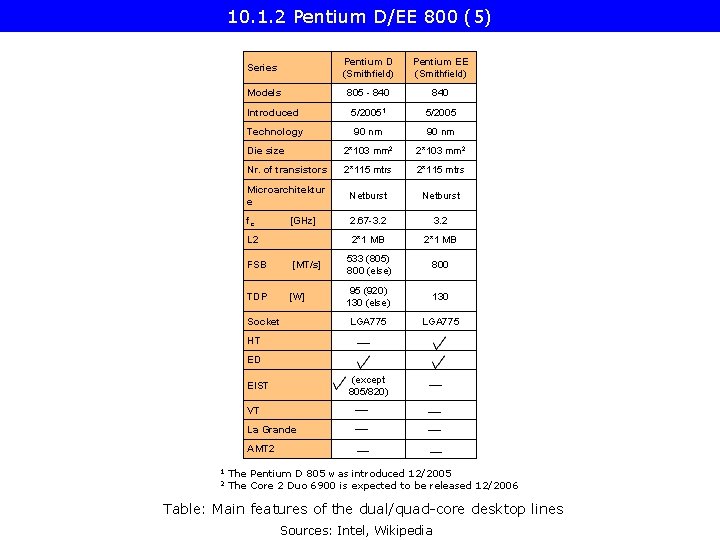

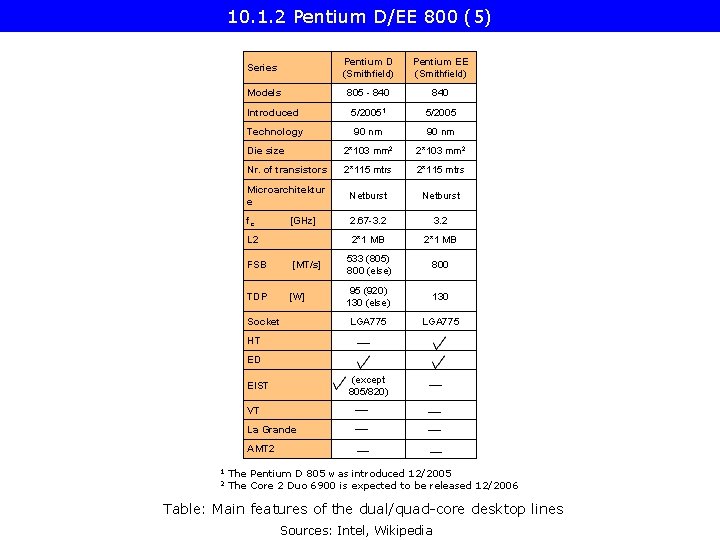

10. 1. 2 Pentium D/EE 800 (5) Series Pentium D (Smithfield) Pentium EE (Smithfield) Models 805 - 840 Introduced 5/20051 5/2005 Technology 90 nm Die size 2*103 mm 2 Nr. of transistors 2*115 mtrs Microarchitektur e Netburst fc 2. 67 -3. 2 2*1 MB [GHz] L 2 FSB [MT/s] 533 (805) 800 (else) 800 TDP [W] 95 (920) 130 (else) 130 LGA 775 Socket HT ED (except 805/820) EIST VT La Grande AMT 2 1 2 The Pentium D 805 was introduced 12/2005 The Core 2 Duo 6900 is expected to be released 12/2006 Table: Main features of the dual/quad-core desktop lines Sources: Intel, Wikipedia

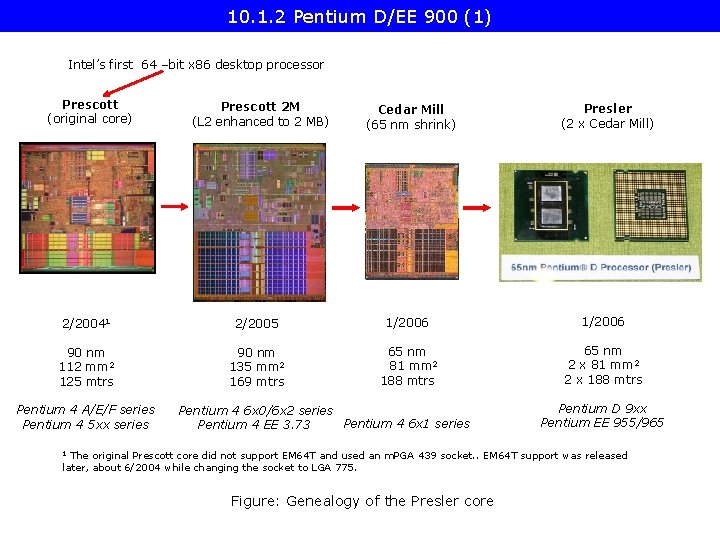

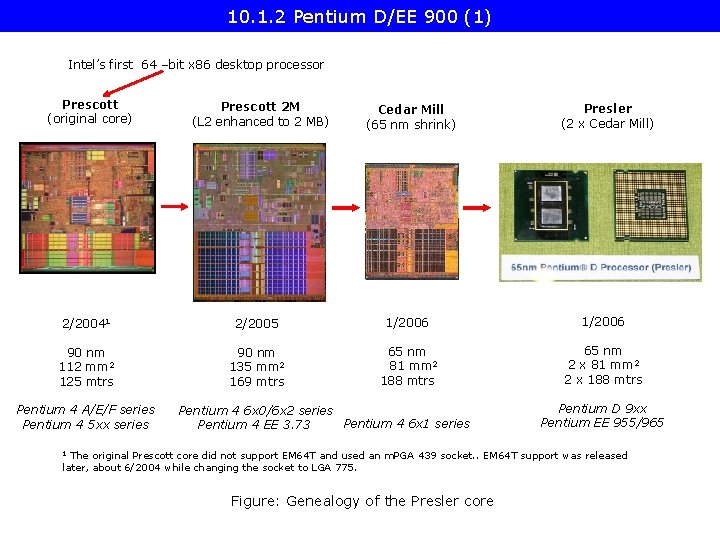

10. 1. 2 Pentium D/EE 900 (1) Intel’s first 64 –bit x 86 desktop processor Prescott (original core) Prescott 2 M (L 2 enhanced to 2 MB) Cedar Mill (65 nm shrink) Presler (2 x Cedar Mill) 2/20041 2/2005 1/2006 90 nm 112 mm 2 125 mtrs 90 nm 135 mm 2 169 mtrs 65 nm 81 mm 2 188 mtrs 65 nm 2 x 81 mm 2 2 x 188 mtrs Pentium 4 A/E/F series Pentium 4 5 xx series Pentium 4 6 x 0/6 x 2 series Pentium 4 6 x 1 series Pentium 4 EE 3. 73 Pentium D 9 xx Pentium EE 955/965 The original Prescott core did not support EM 64 T and used an m. PGA 439 socket. . EM 64 T support was released later, about 6/2004 while changing the socket to LGA 775. 1 Figure: Genealogy of the Presler core

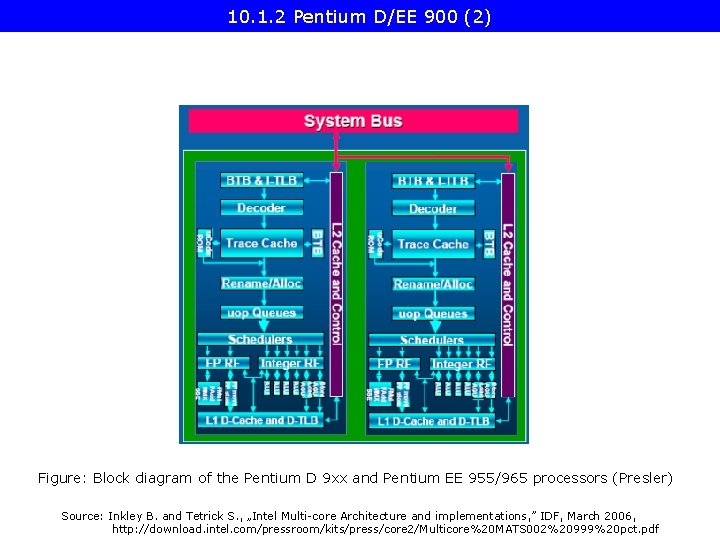

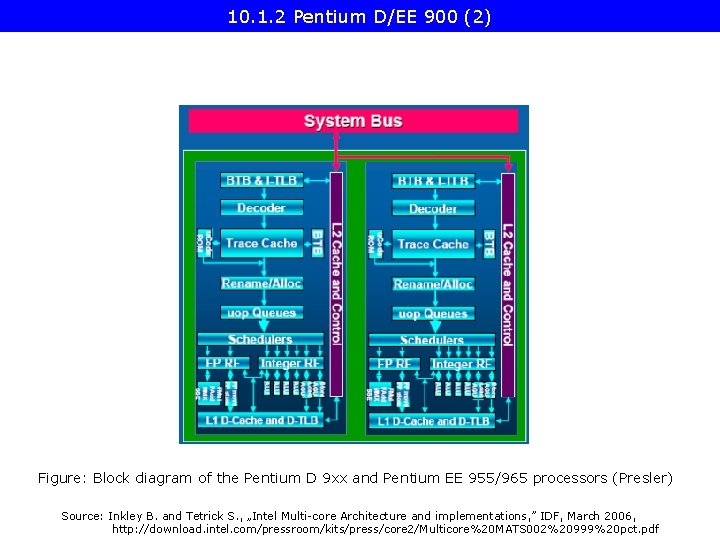

10. 1. 2 Pentium D/EE 900 (2) Figure: Block diagram of the Pentium D 9 xx and Pentium EE 955/965 processors (Presler) Source: Inkley B. and Tetrick S. , „Intel Multi-core Architecture and implementations, ” IDF, March 2006, http: //download. intel. com/pressroom/kits/press/core 2/Multicore%20 MATS 002%20999%20 pct. pdf

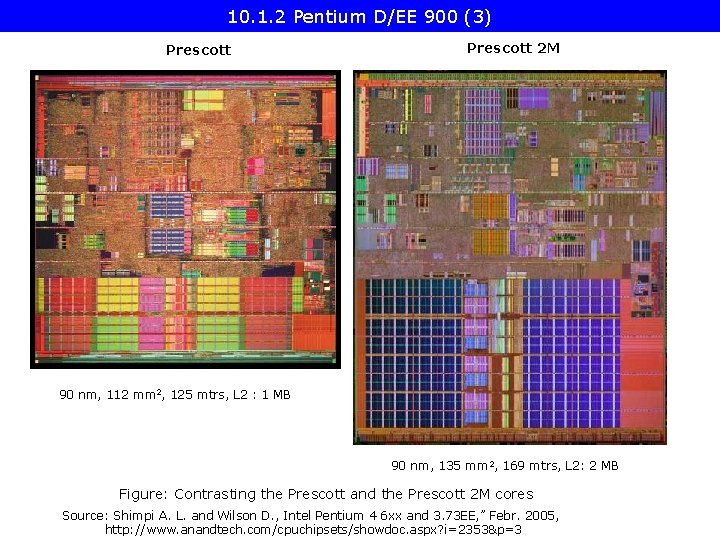

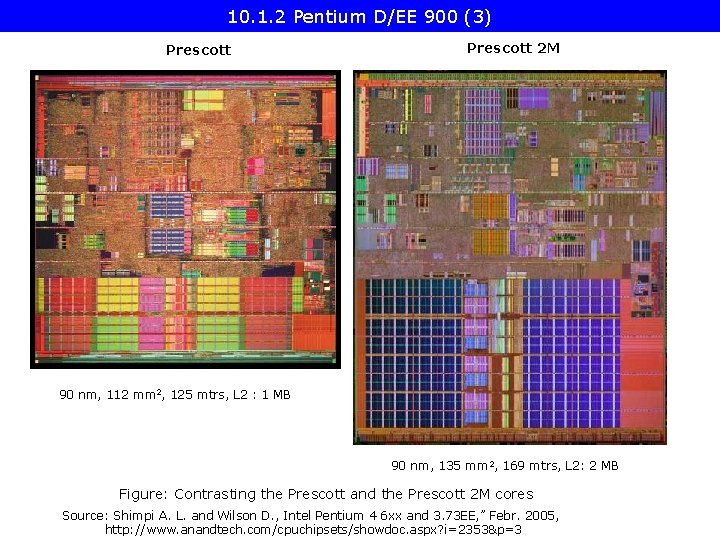

10. 1. 2 Pentium D/EE 900 (3) Prescott 2 M 90 nm, 112 mm 2, 125 mtrs, L 2 : 1 MB 90 nm, 135 mm 2, 169 mtrs, L 2: 2 MB Figure: Contrasting the Prescott and the Prescott 2 M cores Source: Shimpi A. L. and Wilson D. , Intel Pentium 4 6 xx and 3. 73 EE, ” Febr. 2005, http: //www. anandtech. com/cpuchipsets/showdoc. aspx? i=2353&p=3

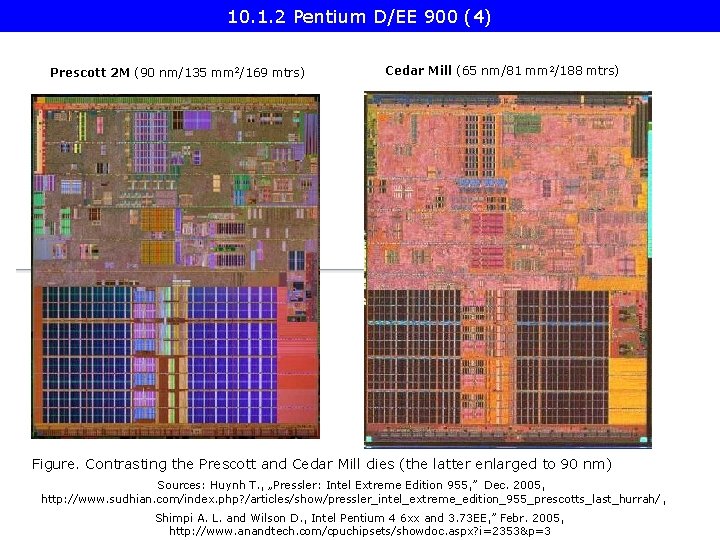

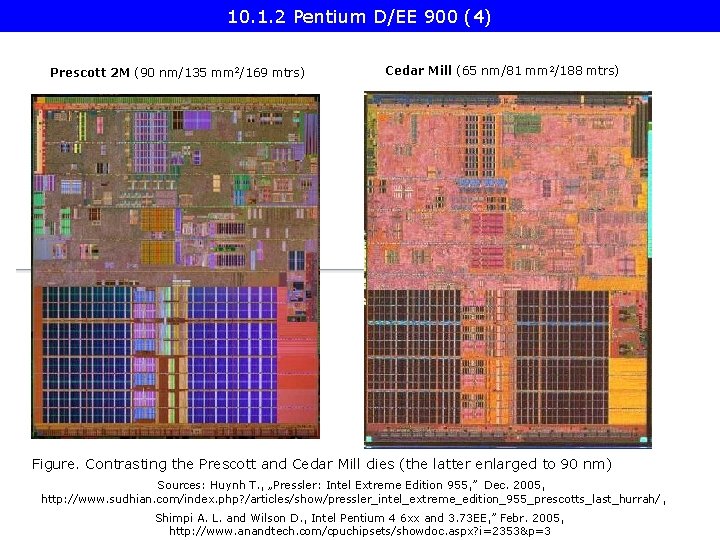

10. 1. 2 Pentium D/EE 900 (4) Prescott 2 M (90 nm/135 mm 2/169 mtrs) Cedar Mill (65 nm/81 mm 2/188 mtrs) Figure. Contrasting the Prescott and Cedar Mill dies (the latter enlarged to 90 nm) Sources: Huynh T. , „Pressler: Intel Extreme Edition 955, ” Dec. 2005, http: //www. sudhian. com/index. php? /articles/show/pressler_intel_extreme_edition_955_prescotts_last_hurrah/ , Shimpi A. L. and Wilson D. , Intel Pentium 4 6 xx and 3. 73 EE, ” Febr. 2005, http: //www. anandtech. com/cpuchipsets/showdoc. aspx? i=2353&p=3

10. 1. 2 Pentium D/EE 900 (5) Figure: The Pentium D 9 xx (Presler) processor package Source: Chainbolt, „Intel Pentium D 920 and 955 Extreme Edition, ” Febr. 2006, http: //www. overclockers. com. au/article. php? id=452447

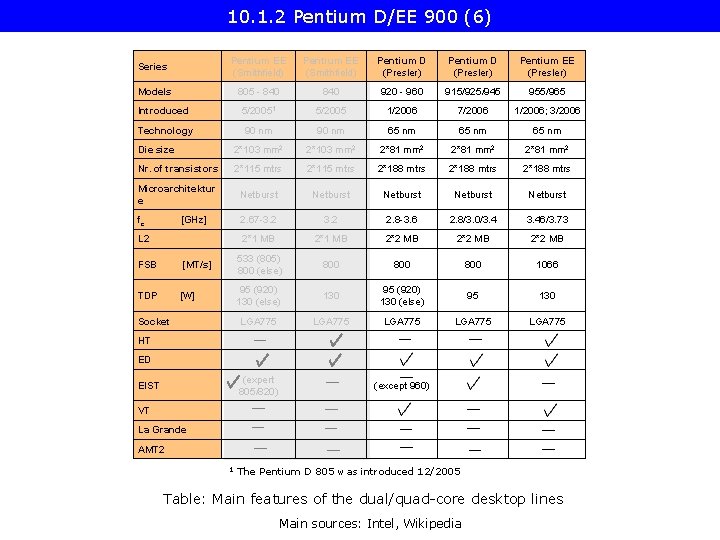

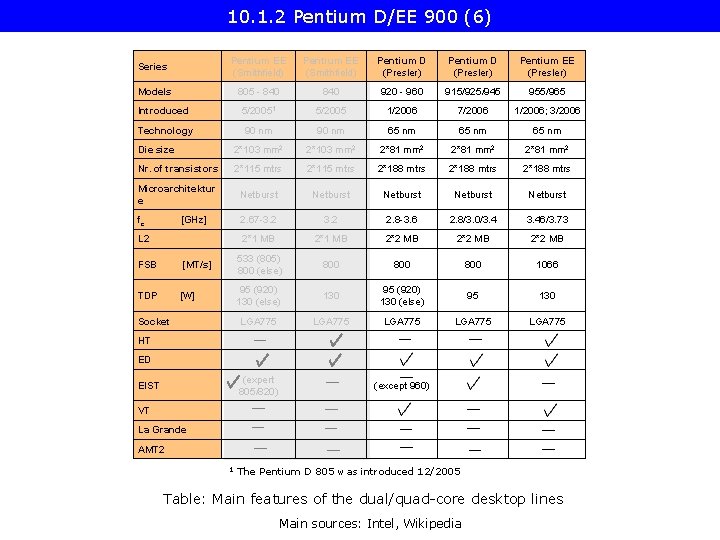

10. 1. 2 Pentium D/EE 900 (6) Series Pentium EE (Smithfield) Pentium D (Presler) Pentium EE (Presler) Models 805 - 840 920 - 960 915/925/945 955/965 Introduced 5/20051 5/2005 1/2006 7/2006 1/2006; 3/2006 Technology 90 nm 65 nm Die size 2*103 mm 2 2*81 mm 2 Nr. of transistors 2*115 mtrs 2*188 mtrs Microarchitektur e Netburst Netburst fc 2. 67 -3. 2 2. 8 -3. 6 2. 8/3. 0/3. 46/3. 73 2*1 MB 2*2 MB [GHz] L 2 FSB [MT/s] 533 (805) 800 (else) 800 800 1066 TDP [W] 95 (920) 130 (else) 130 95 (920) 130 (else) 95 130 LGA 775 LGA 775 Socket HT ED (expert 805/820) EIST (except 960) VT La Grande AMT 2 1 The Pentium D 805 was introduced 12/2005 Table: Main features of the dual/quad-core desktop lines Main sources: Intel, Wikipedia

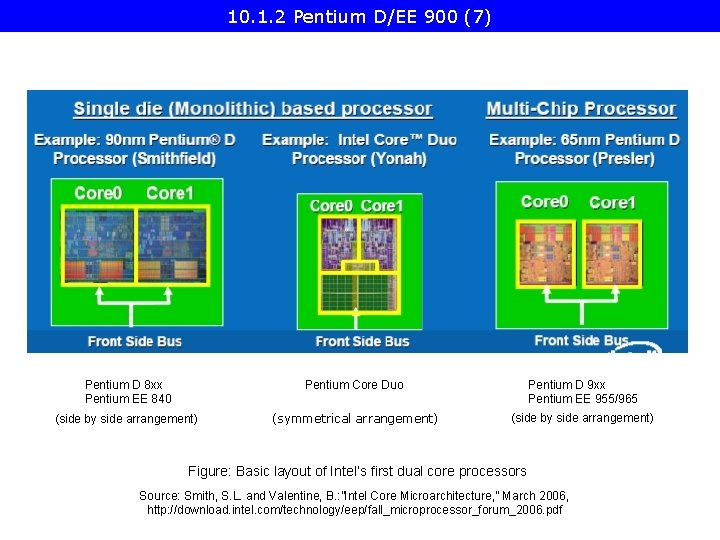

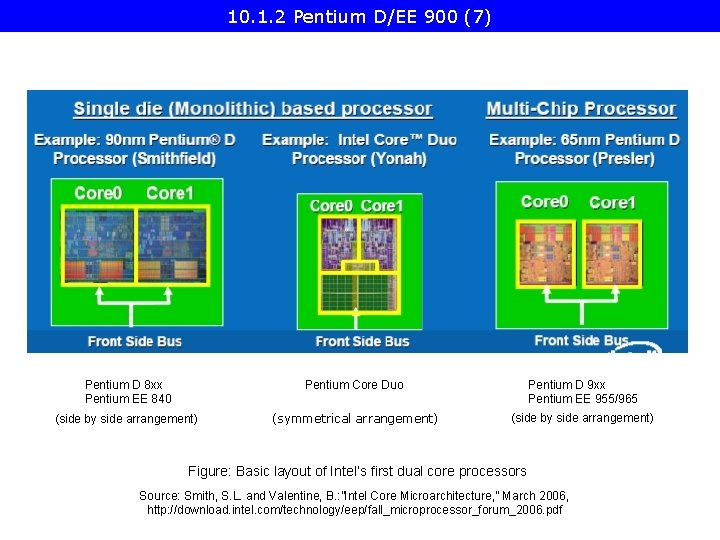

10. 1. 2 Pentium D/EE 900 (7) Pentium D 8 xx Pentium EE 840 Pentium Core Duo Pentium D 9 xx Pentium EE 955/965 (side by side arrangement) (symmetrical arrangement) (side by side arrangement) Figure: Basic layout of Intel’s first dual core processors Source: Smith, S. L. and Valentine, B. : ”Intel Core Microarchitecture, ” March 2006, http: //download. intel. com/technology/eep/fall_microprocessor_forum_2006. pdf

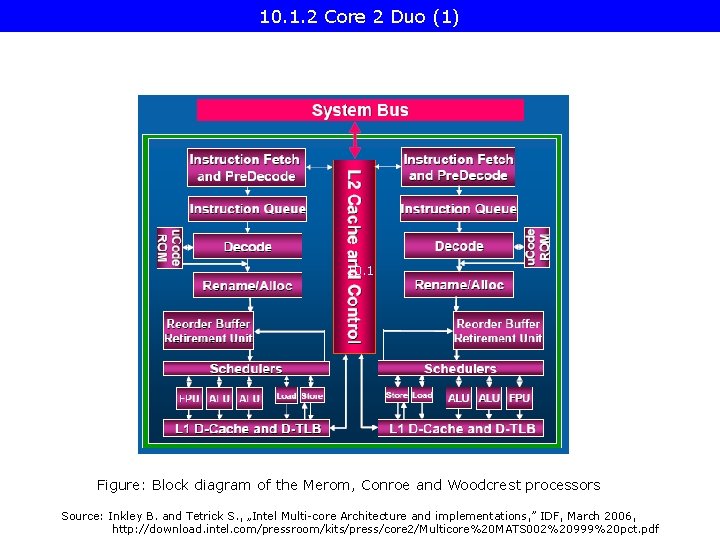

10. 1. 2 Core 2 Duo (1) 10. 1 Figure: Block diagram of the Merom, Conroe and Woodcrest processors Source: Inkley B. and Tetrick S. , „Intel Multi-core Architecture and implementations, ” IDF, March 2006, http: //download. intel. com/pressroom/kits/press/core 2/Multicore%20 MATS 002%20999%20 pct. pdf

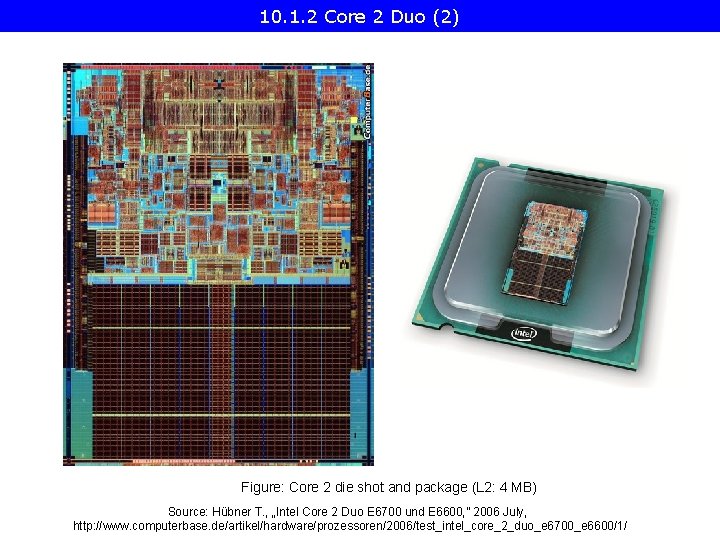

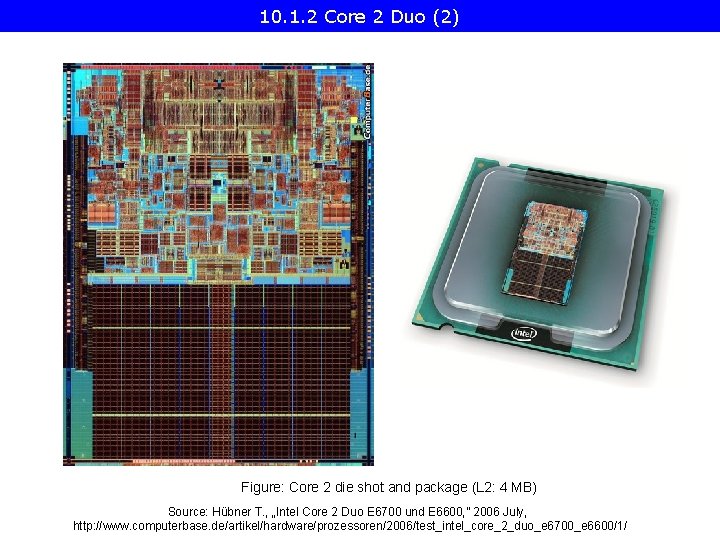

10. 1. 2 Core 2 Duo (2) Figure: Core 2 die shot and package (L 2: 4 MB) Source: Hübner T. , „Intel Core 2 Duo E 6700 und E 6600, ” 2006 July, http: //www. computerbase. de/artikel/hardware/prozessoren/2006/test_intel_core_2_duo_e 6700_e 6600/1/

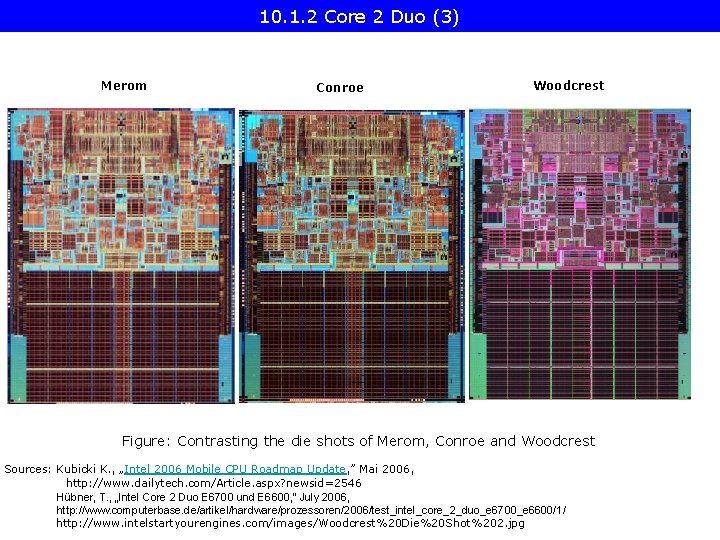

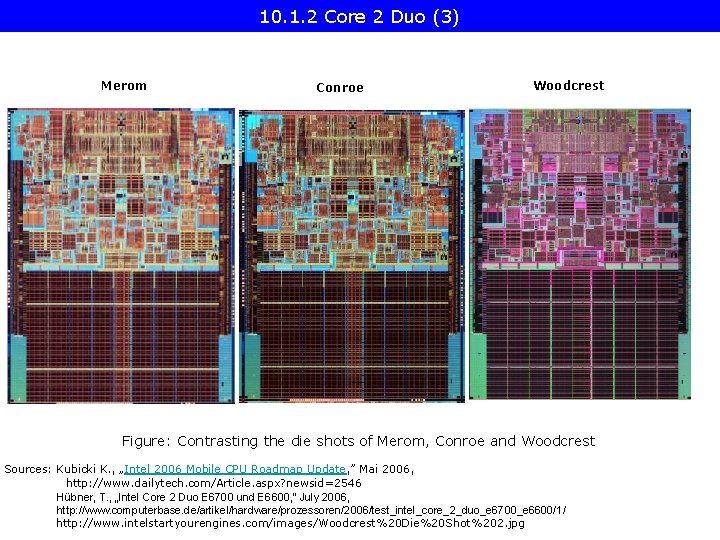

10. 1. 2 Core 2 Duo (3) Merom Conroe Woodcrest Figure: Contrasting the die shots of Merom, Conroe and Woodcrest Sources: Kubicki K. , „Intel 2006 Mobile CPU Roadmap Update, ” Mai 2006, http: //www. dailytech. com/Article. aspx? newsid=2546 Hübner, T. , „Intel Core 2 Duo E 6700 und E 6600, ” July 2006, http: //www. computerbase. de/artikel/hardware/prozessoren/2006/test_intel_core_2_duo_e 6700_e 6600/1/ http: //www. intelstartyourengines. com/images/Woodcrest%20 Die%20 Shot%202. jpg

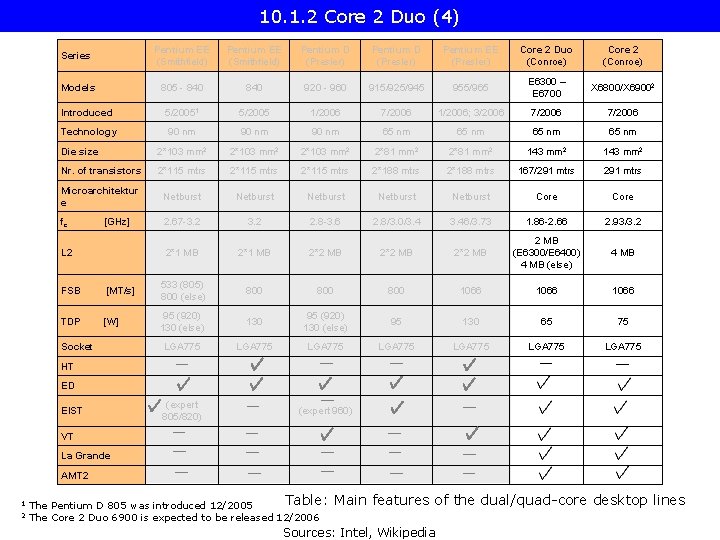

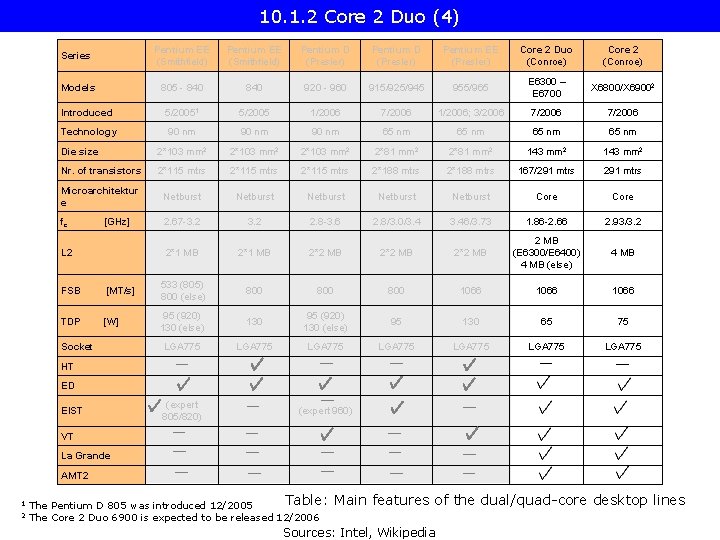

10. 1. 2 Core 2 Duo (4) Series Pentium EE (Smithfield) Pentium D (Presler) Pentium EE (Presler) Core 2 Duo (Conroe) Core 2 (Conroe) Models 805 - 840 920 - 960 915/925/945 955/965 E 6300 – E 6700 X 6800/X 69002 Introduced 5/20051 5/2005 1/2006 7/2006 1/2006; 3/2006 7/2006 Technology 90 nm 65 nm Die size 2*103 mm 2 2*81 mm 2 143 mm 2 Nr. of transistors 2*115 mtrs 2*188 mtrs 167/291 mtrs Microarchitektur e Netburst Netburst Core fc 2. 67 -3. 2 2. 8 -3. 6 2. 8/3. 0/3. 46/3. 73 1. 86 -2. 66 2. 93/3. 2 2*1 MB 2*2 MB (E 6300/E 6400) 4 MB (else) 4 MB [GHz] L 2 FSB [MT/s] 533 (805) 800 (else) 800 800 1066 TDP [W] 95 (920) 130 (else) 130 95 (920) 130 (else) 95 130 65 75 LGA 775 LGA 775 Socket HT ED EIST (expert 805/820) (expert 960) VT La Grande AMT 2 1 2 Table: The Pentium D 805 was introduced 12/2005 The Core 2 Duo 6900 is expected to be released 12/2006 Main features of the dual/quad-core desktop lines Sources: Intel, Wikipedia

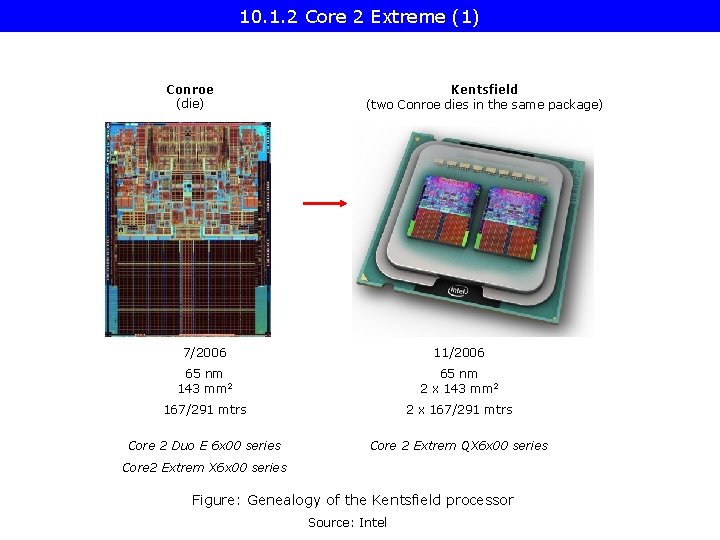

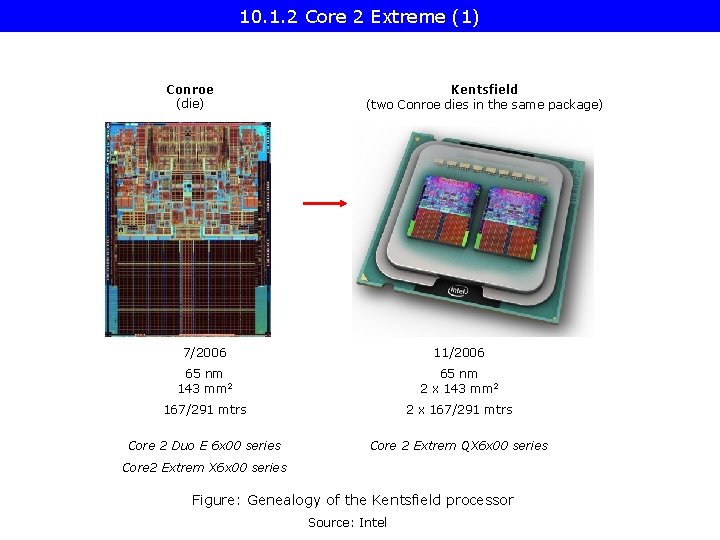

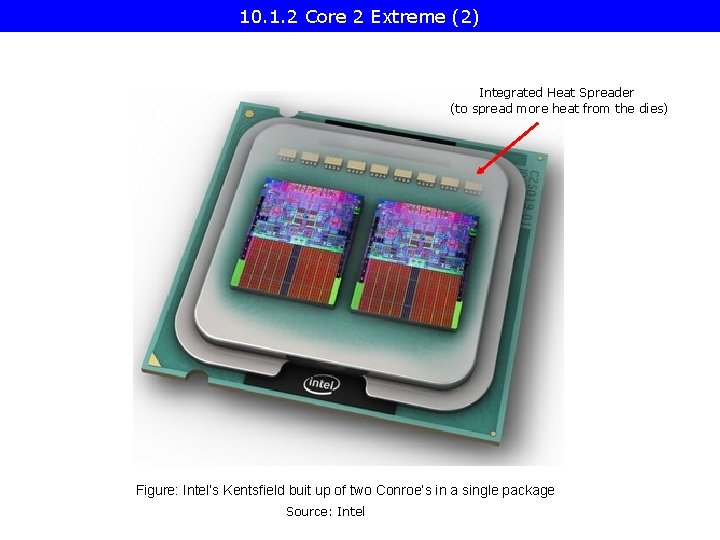

10. 1. 2 Core 2 Extreme (1) Conroe (die) Kentsfield (two Conroe dies in the same package) 7/2006 11/2006 65 nm 143 mm 2 65 nm 2 x 143 mm 2 167/291 mtrs 2 x 167/291 mtrs Core 2 Duo E 6 x 00 series Core 2 Extrem QX 6 x 00 series Core 2 Extrem X 6 x 00 series Figure: Genealogy of the Kentsfield processor Source: Intel

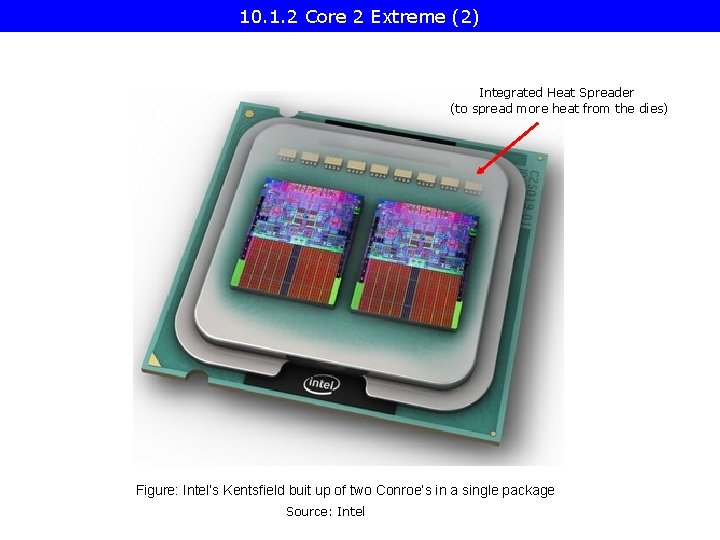

10. 1. 2 Core 2 Extreme (2) Integrated Heat Spreader (to spread more heat from the dies) Figure: Intel’s Kentsfield buit up of two Conroe’s in a single package Source: Intel

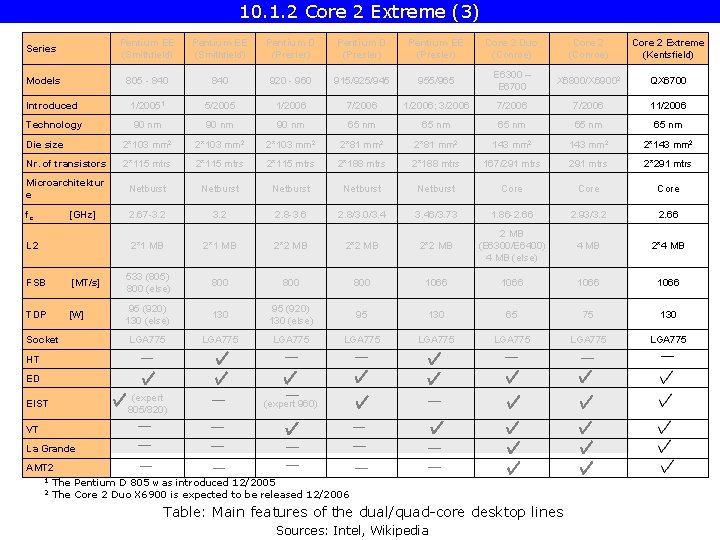

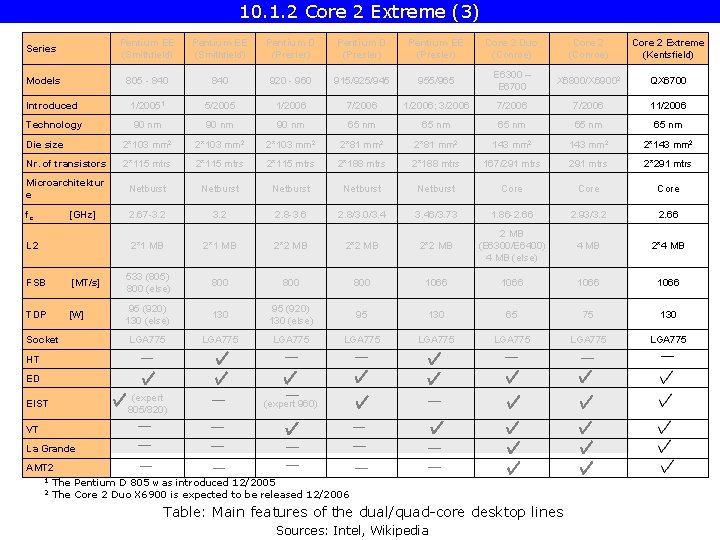

10. 1. 2 Core 2 Extreme (3) Series Pentium EE (Smithfield) Pentium D (Presler) Pentium EE (Presler) Core 2 Duo (Conroe) Core 2 Extreme (Kentsfield) Models 805 - 840 920 - 960 915/925/945 955/965 E 6300 – E 6700 X 6800/X 69002 QX 6700 Introduced 1/20051 5/2005 1/2006 7/2006 1/2006; 3/2006 7/2006 11/2006 Technology 90 nm 65 nm 65 nm Die size 2*103 mm 2 2*81 mm 2 143 mm 2 2*143 mm 2 Nr. of transistors 2*115 mtrs 2*188 mtrs 167/291 mtrs 2*291 mtrs Microarchitektur e Netburst Netburst Core fc 2. 67 -3. 2 2. 8 -3. 6 2. 8/3. 0/3. 46/3. 73 1. 86 -2. 66 2. 93/3. 2 2. 66 2*1 MB 2*2 MB (E 6300/E 6400) 4 MB (else) 4 MB 2*4 MB [GHz] L 2 FSB [MT/s] 533 (805) 800 (else) 800 800 1066 TDP [W] 95 (920) 130 (else) 130 95 (920) 130 (else) 95 130 65 75 130 LGA 775 LGA 775 Socket HT ED EIST (expert 805/820) (expert 960) VT La Grande AMT 2 1 The Pentium D 805 was introduced 12/2005 2 The Core 2 Duo X 6900 is expected to be released 12/2006 Table: Main features of the dual/quad-core desktop lines Sources: Intel, Wikipedia