IDPU Subsystem Fabrication and Test Plan Critical Design

IDPU Subsystem Fabrication and Test Plan Critical Design Review Michael Ludlam University of California - Berkeley THEMIS Instrument CDR 1 UCB, April 19 -20, 2004

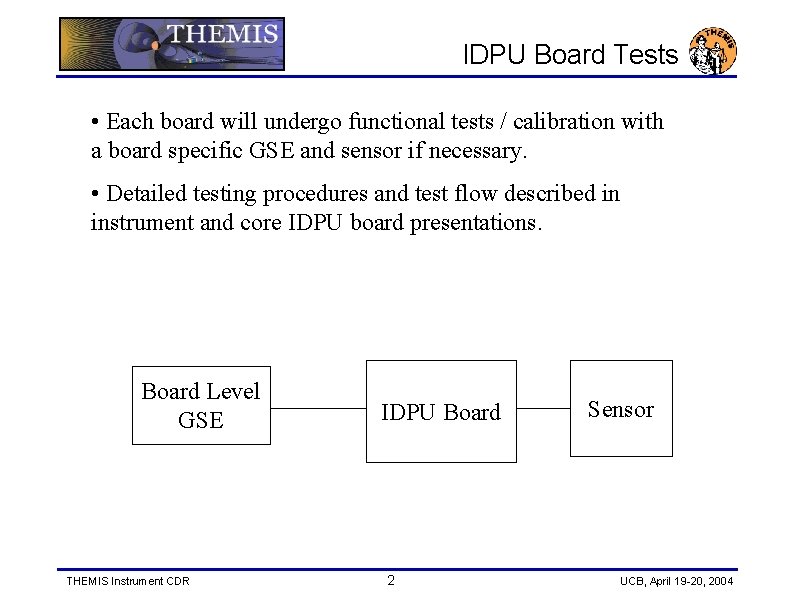

IDPU Board Tests • Each board will undergo functional tests / calibration with a board specific GSE and sensor if necessary. • Detailed testing procedures and test flow described in instrument and core IDPU board presentations. Board Level GSE THEMIS Instrument CDR IDPU Board 2 Sensor UCB, April 19 -20, 2004

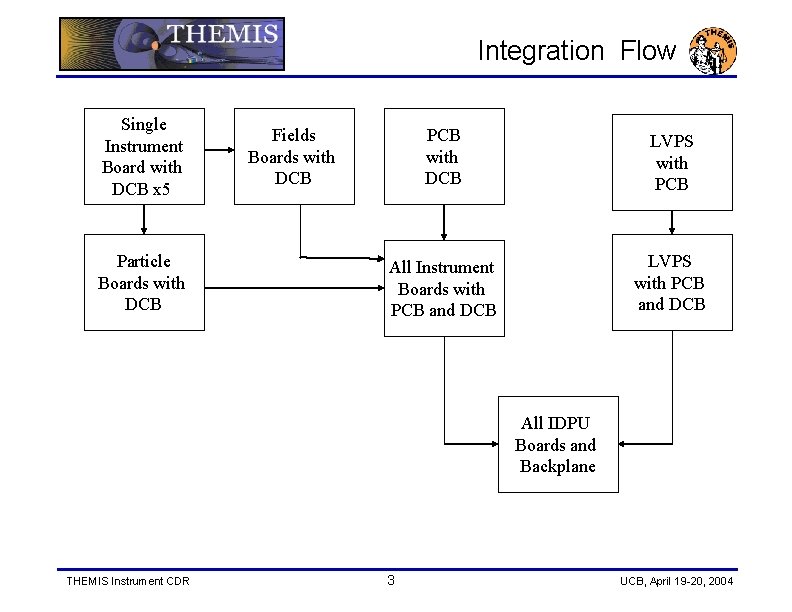

Integration Flow Single Instrument Board with DCB x 5 Particle Boards with DCB Fields Boards with DCB PCB with DCB LVPS with PCB All Instrument Boards with PCB and DCB LVPS with PCB and DCB All IDPU Boards and Backplane THEMIS Instrument CDR 3 UCB, April 19 -20, 2004

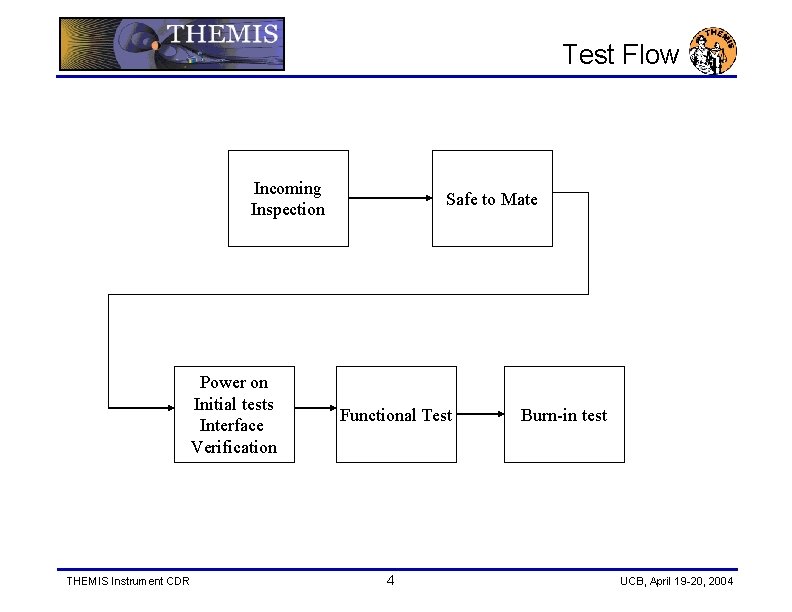

Test Flow Incoming Inspection Power on Initial tests Interface Verification THEMIS Instrument CDR Safe to Mate Functional Test 4 Burn-in test UCB, April 19 -20, 2004

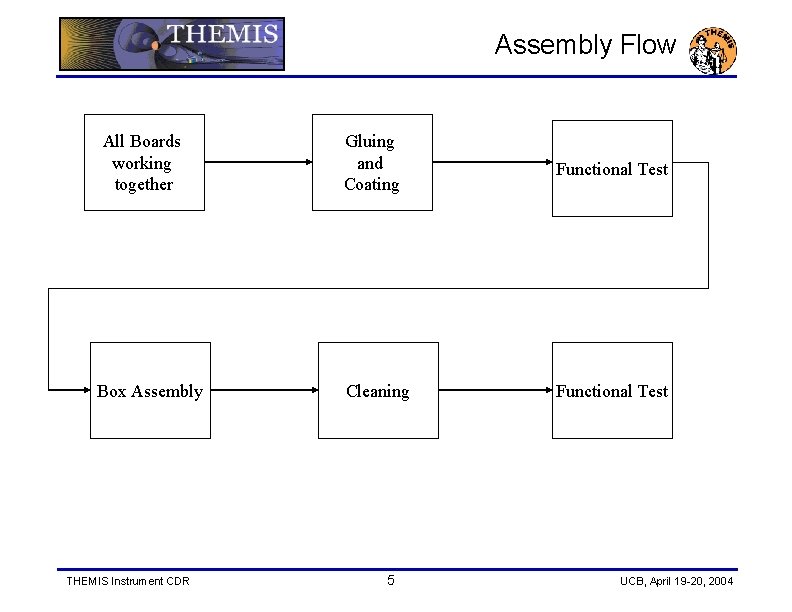

Assembly Flow All Boards working together Box Assembly THEMIS Instrument CDR Gluing and Coating Functional Test Cleaning Functional Test 5 UCB, April 19 -20, 2004

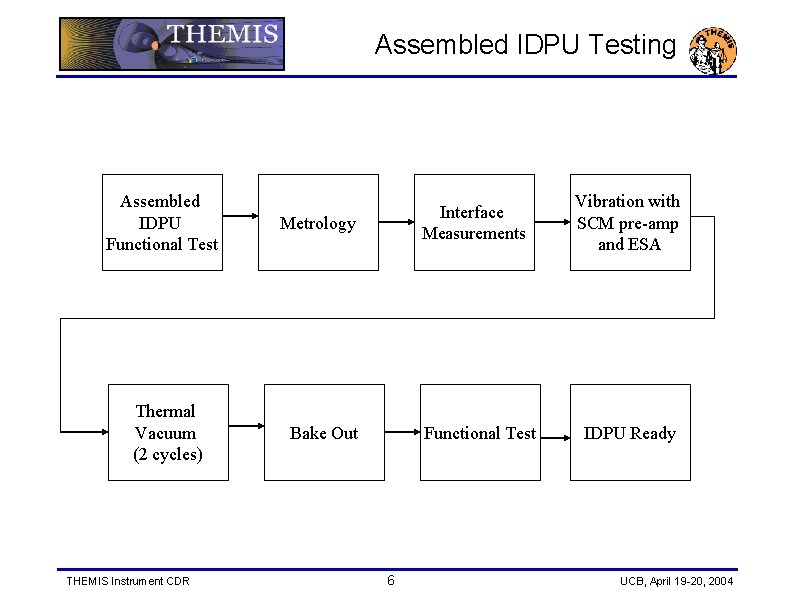

Assembled IDPU Testing Assembled IDPU Functional Test Thermal Vacuum (2 cycles) THEMIS Instrument CDR Interface Measurements Metrology Bake Out Functional Test 6 Vibration with SCM pre-amp and ESA IDPU Ready UCB, April 19 -20, 2004

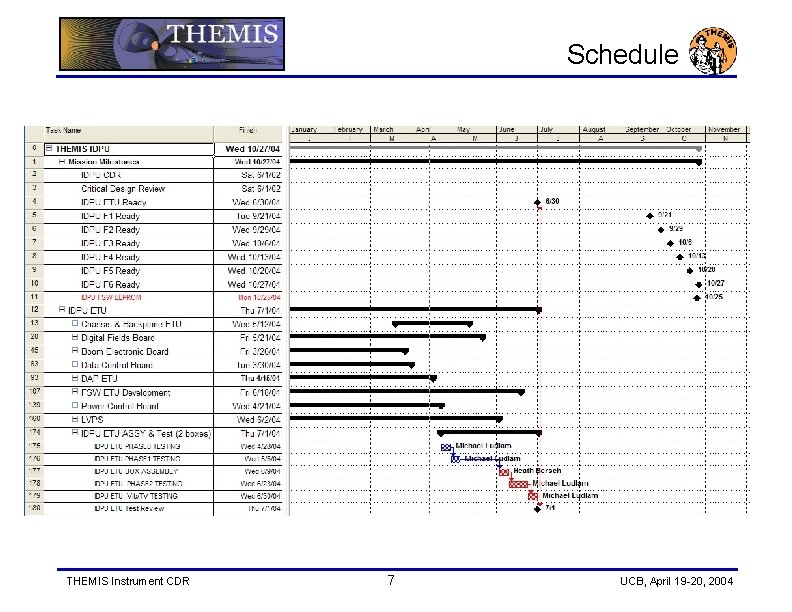

Schedule THEMIS Instrument CDR 7 UCB, April 19 -20, 2004

- Slides: 7