IBMMotorolaApple Power PC CS 480 Computer Architecture Summer

IBM/Motorola/Apple Power. PC CS 480: Computer Architecture Summer 2002 Patrick Kang Temitope Akanni Jane Mc. Hugh Kenneth Kincel

How Did Power. PC Start? • In 1991 Intel’s domination of the PC market. • Other competitors’ uphill struggle. • Realization of cooperating among the competitors. • What to do about Intel’s domination. 2

Birth of Power. PC • Power. PC Alliance, IBM, Apple, and Motorola. • Development of Power. PC Architecture. • Some changes. • A three year of their hard work. • The new architecture in 1994. • Performance Optimization With Enhanced RISC Personal Computer. 3

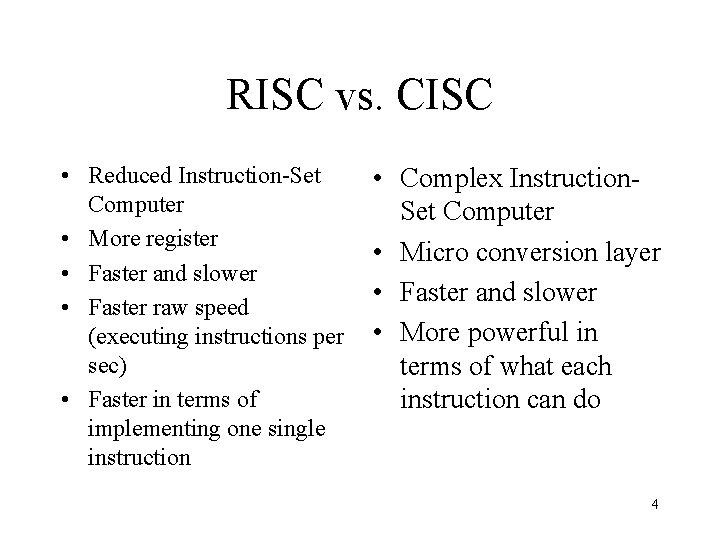

RISC vs. CISC • Reduced Instruction-Set Computer • More register • Faster and slower • Faster raw speed (executing instructions per sec) • Faster in terms of implementing one single instruction • Complex Instruction. Set Computer • Micro conversion layer • Faster and slower • More powerful in terms of what each instruction can do 4

![RISC vs. CISC • A=B+C • ld[A], %r 1 ld[B], %r 2 addcc %r RISC vs. CISC • A=B+C • ld[A], %r 1 ld[B], %r 2 addcc %r](http://slidetodoc.com/presentation_image_h/caf4a3df779158ba1e00eefcd12b53c5/image-5.jpg)

RISC vs. CISC • A=B+C • ld[A], %r 1 ld[B], %r 2 addcc %r 1, %r 2, %r 3 st %r 3, [C] • A=B+C • addcc [A], [B], [C] 5

So, which one is faster? • No simple answer • Neither • It all depends on what application you are using. • You have the power to make one of these faster by carefully choosing the best instruction for your application. 6

Power Architecture • Complex CISC instructions can be replaced with simple RISC instruction. • Aspects of RISC computing incorporated into the Power architecture: – Instructions were fixed to four bytes in length – Load and store instructions were used to provide all the access to and from memory 7

Power Architecture • Difference between earlier RISC machines and Power architecture: – Each function (floating-point, fixed-point, integer computation were placed in their own units. • Emphasized the superscalar aspect of the Power architecture. Instructions to and from different units can be accessed in parallel. • Power. PC 601 - the first microprocessor, architecture implemented in IBM RS/6000 workstations. 8

Power. PC Architecture: A New Beginning • The Power. PC is 64 -bits in length and is compatible with the Power 32 -bit data paths. • Dynamic switching between the 64 -bit and 32 -bit is supported. • Infrequently executed instructions in the Power architecture were discarded in the Power. PC. • IBM 601 microprocessor used all but two of the instructions in the of the Power instructions set. 9

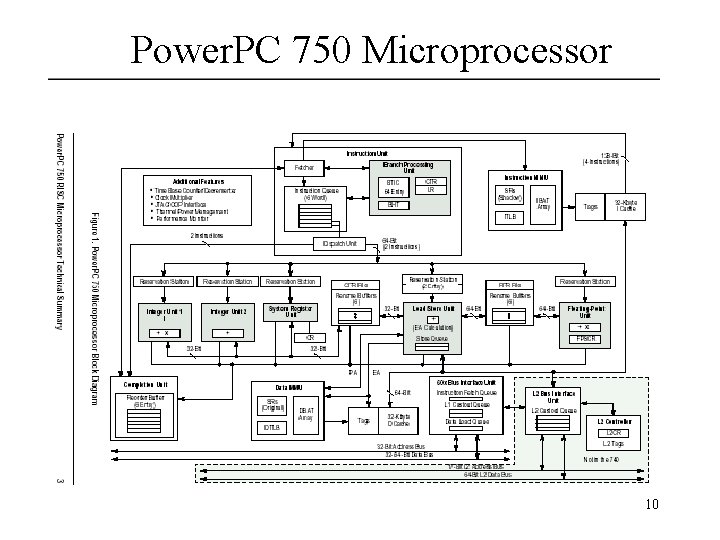

Power. PC 750 Microprocessor 10

IBM Power. PC 604 e

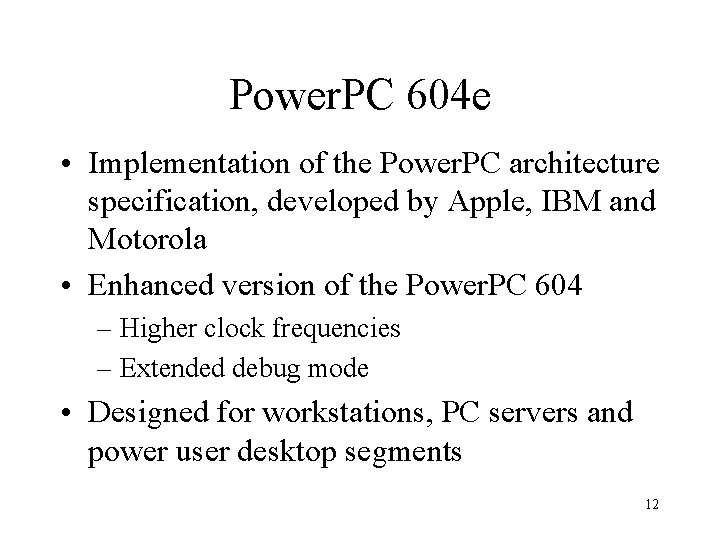

Power. PC 604 e • Implementation of the Power. PC architecture specification, developed by Apple, IBM and Motorola • Enhanced version of the Power. PC 604 – Higher clock frequencies – Extended debug mode • Designed for workstations, PC servers and power user desktop segments 12

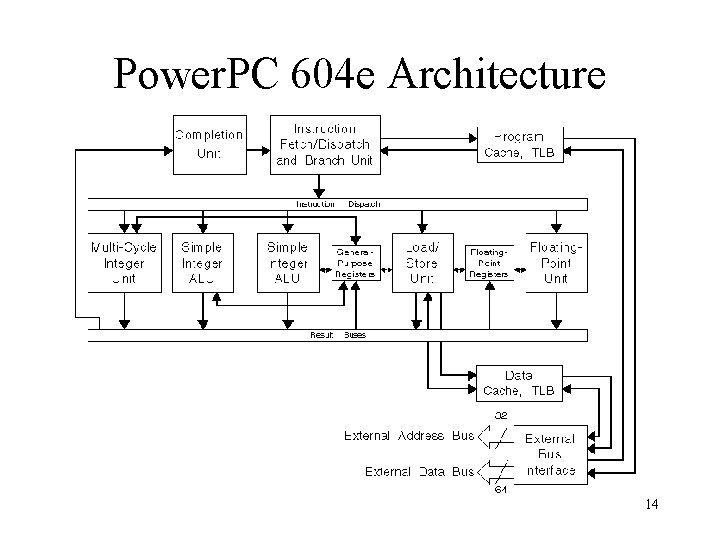

Power. PC 604 e • Architecture consists of: – PCU – 2 simple integer ALUs – 1 complex integer unit – Floating-point unit – LOAD/STORE unit – Branch unit – Instruction and data caches – CRU 13

Power. PC 604 e Architecture 14

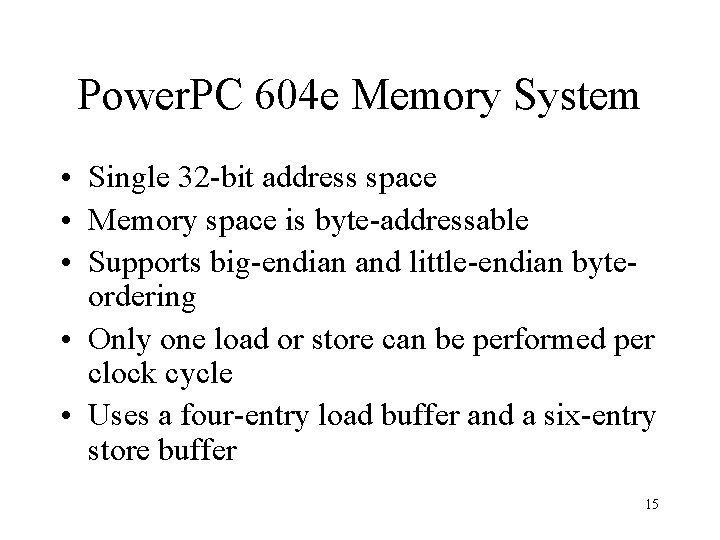

Power. PC 604 e Memory System • Single 32 -bit address space • Memory space is byte-addressable • Supports big-endian and little-endian byteordering • Only one load or store can be performed per clock cycle • Uses a four-entry load buffer and a six-entry store buffer 15

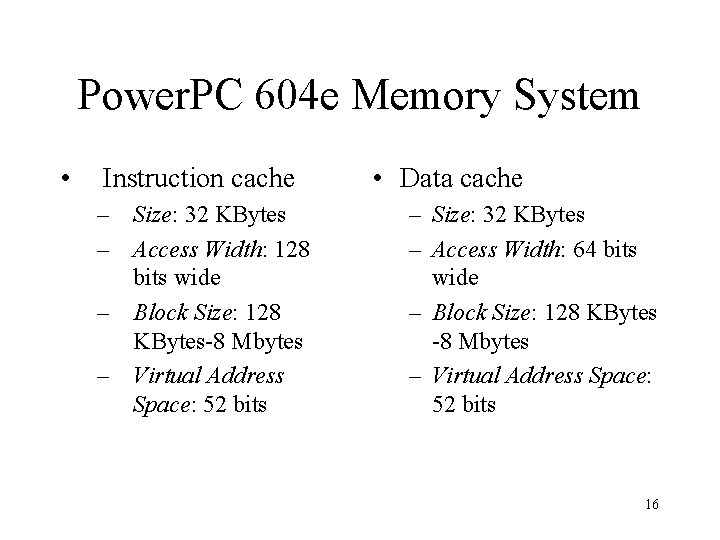

Power. PC 604 e Memory System • Instruction cache – Size: 32 KBytes – Access Width: 128 bits wide – Block Size: 128 KBytes-8 Mbytes – Virtual Address Space: 52 bits • Data cache – Size: 32 KBytes – Access Width: 64 bits wide – Block Size: 128 KBytes -8 Mbytes – Virtual Address Space: 52 bits 16

IBM Power. PC 750 CX

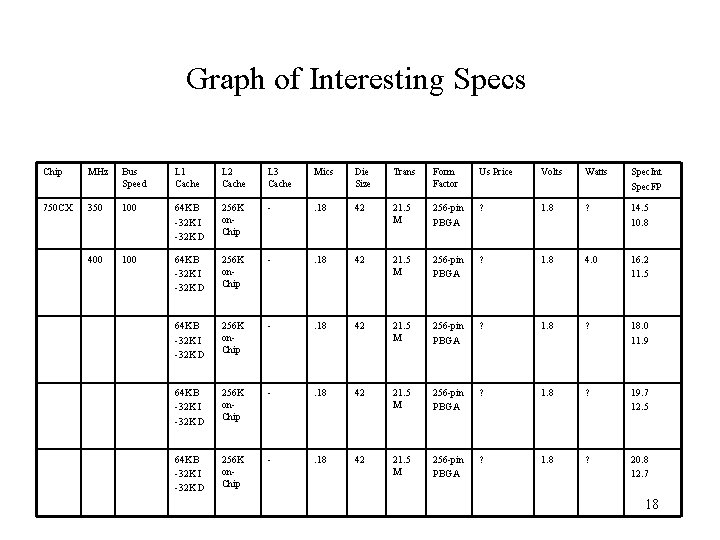

Graph of Interesting Specs Chip MHz Bus Speed L 1 Cache L 2 Cache L 3 Cache Mics Die Size Trans Form Factor Us Price Volts Watts Spec. Int Spec. FP 750 CX 350 100 64 KB -32 K I -32 K D 256 K on. Chip - . 18 42 21. 5 M 256 -pin PBGA ? 1. 8 ? 14. 5 10. 8 400 100 64 KB -32 K I -32 K D 256 K on. Chip - . 18 42 21. 5 M 256 -pin PBGA ? 1. 8 4. 0 16. 2 11. 5 64 KB -32 K I -32 K D 256 K on. Chip - . 18 42 21. 5 M 256 -pin PBGA ? 1. 8 ? 18. 0 11. 9 64 KB -32 K I -32 K D 256 K on. Chip - . 18 42 21. 5 M 256 -pin PBGA ? 1. 8 ? 19. 7 12. 5 64 KB -32 K I -32 K D 256 K on. Chip - . 18 42 21. 5 M 256 -pin PBGA ? 1. 8 ? 20. 8 12. 7 18

Interesting Features • Two fixed-point (integer) execution units. • 38 32 -bit registers. 32 are architected generalpurpose registers and six rename registers. • L 1 instruction cache has a 128 -bit-wide read bus that allows four instructions to be fetched into the instruction queue every cycle. 19

Integrated Cache • What separates the 750 CX from its predecessor the 750, commonly known as the G 3, is that the 750 CX has an integrated 256 KB level 2 (L 2) cache. • Integrated cache runs at full CPU clock speed. 20

Advantage of Integrated Cache • Power Usage • Inexpensive to manufacture which equates to lower cost for the consumers 21

Future of the Power. PC • Strong future with expanded possibilities – PC that automatically downloads software updates and security controls – Intel Lecta to wirelessly host multimedia applications for other home devices – Third Generation I/O to replace the common PCI bus 22

- Slides: 22