IAY 0600 Digital Systems Design VHDL discussion Dataflow

- Slides: 17

IAY 0600 Digital Systems Design VHDL discussion Dataflow Style Combinational Design Alexander Sudnitson Tallinn University of Technology

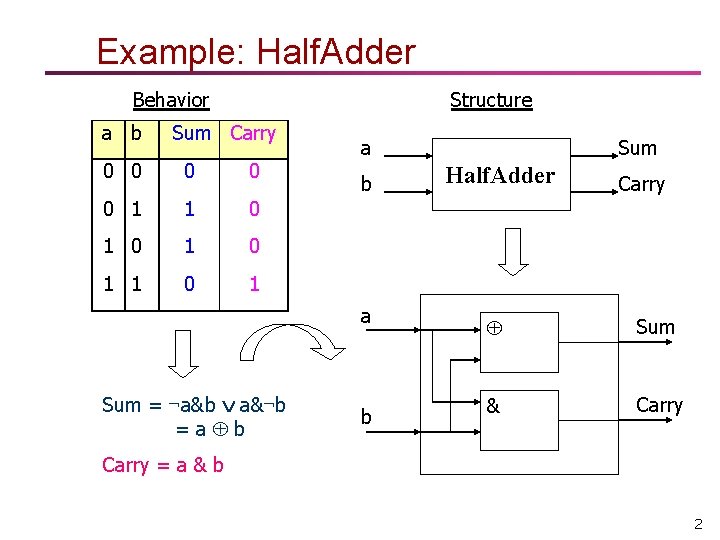

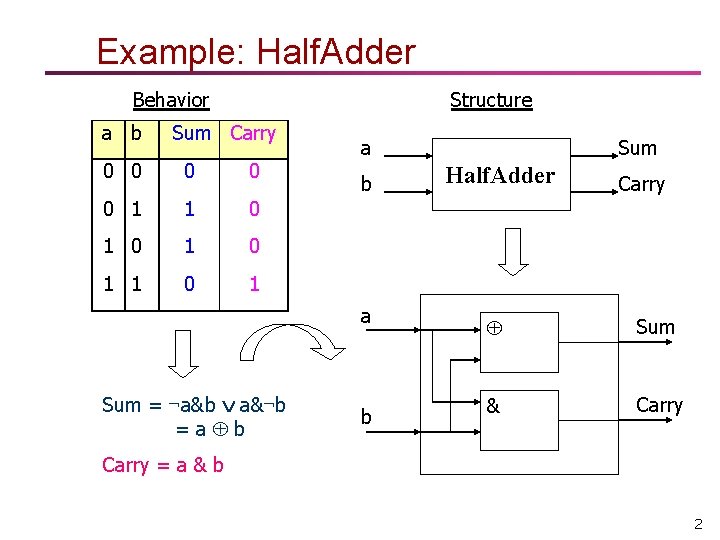

Example: Half. Adder Behavior a b Structure Sum Carry 0 0 0 1 1 0 1 0 1 a b a Sum = ¬a&b a&¬b =a b b Sum Half. Adder Carry Sum & Carry = a & b 2

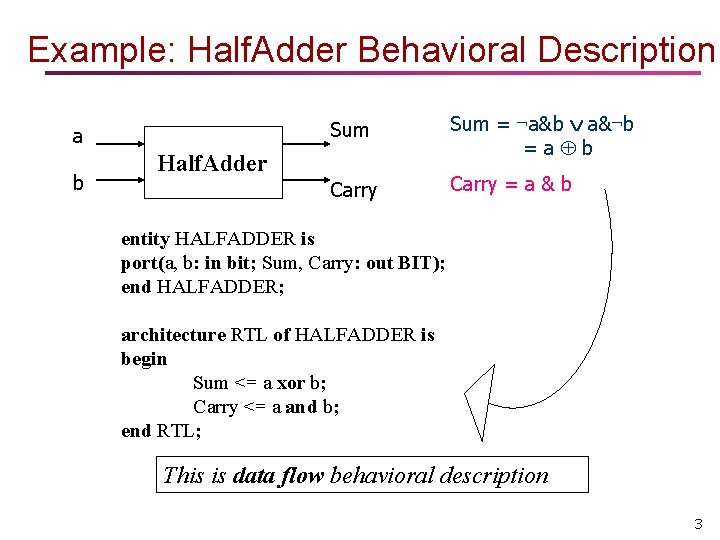

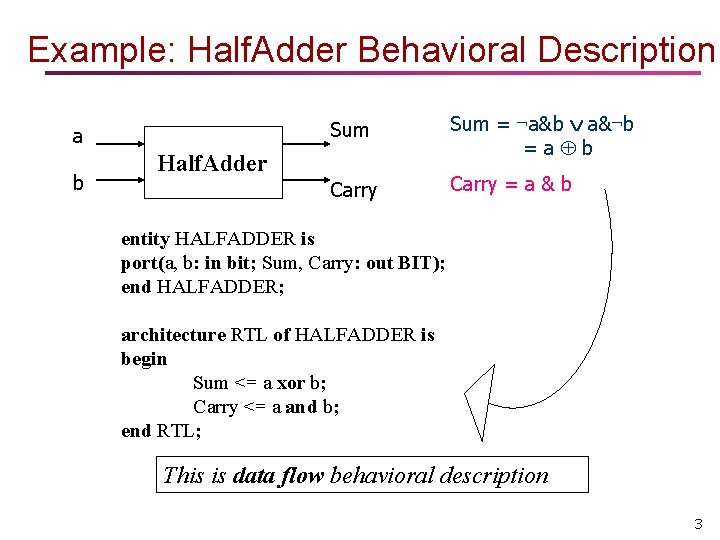

Example: Half. Adder Behavioral Description a b Sum = ¬a&b a&¬b =a b Carry = a & b Half. Adder entity HALFADDER is port(a, b: in bit; Sum, Carry: out BIT); end HALFADDER; architecture RTL of HALFADDER is begin Sum <= a xor b; Carry <= a and b; end RTL; This is data flow behavioral description 3

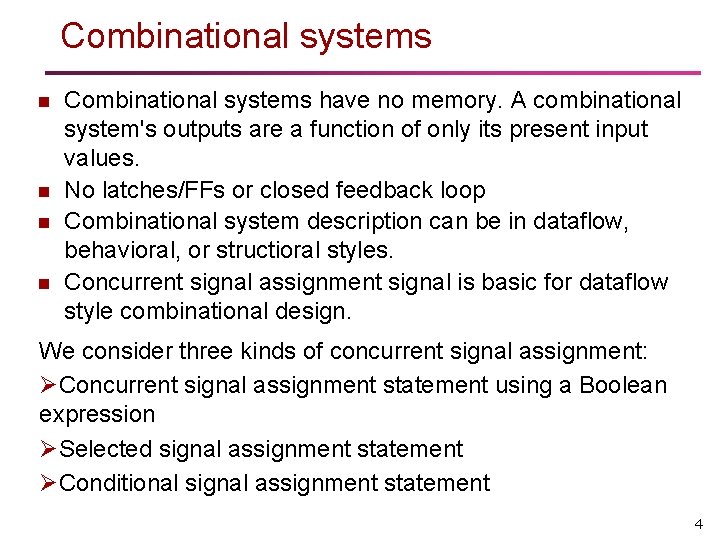

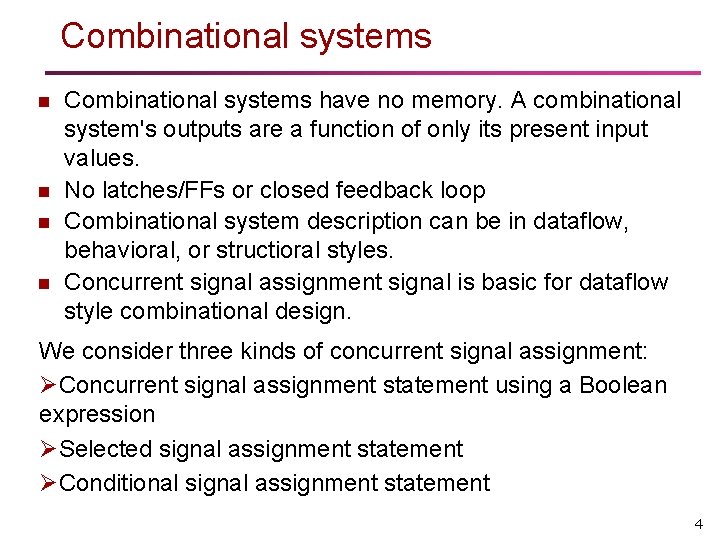

Combinational systems n n Combinational systems have no memory. A combinational system's outputs are a function of only its present input values. No latches/FFs or closed feedback loop Combinational system description can be in dataflow, behavioral, or structioral styles. Concurrent signal assignment signal is basic for dataflow style combinational design. We consider three kinds of concurrent signal assignment: ØConcurrent signal assignment statement using a Boolean expression ØSelected signal assignment statement ØConditional signal assignment statement 4

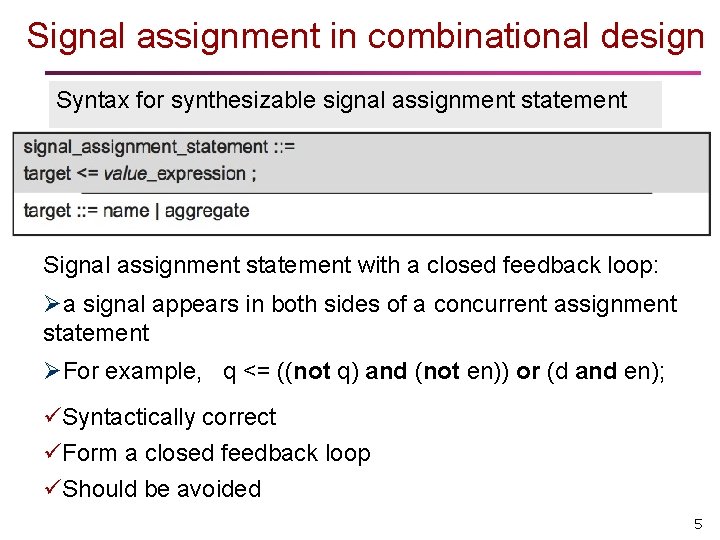

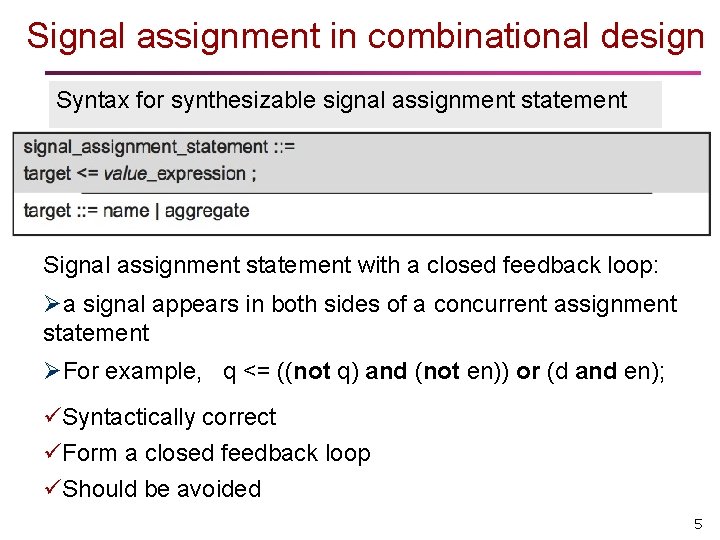

Signal assignment in combinational design Syntax for synthesizable signal assignment statement Signal assignment statement with a closed feedback loop: Øa signal appears in both sides of a concurrent assignment statement ØFor example, q <= ((not q) and (not en)) or (d and en); üSyntactically correct üForm a closed feedback loop üShould be avoided 5

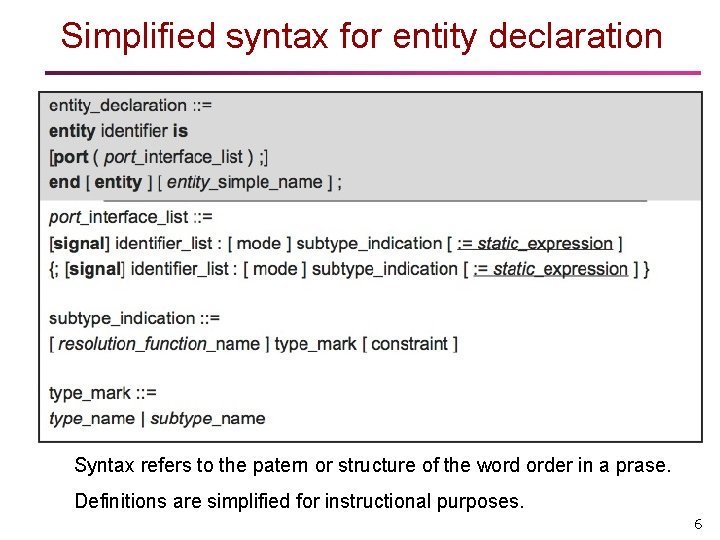

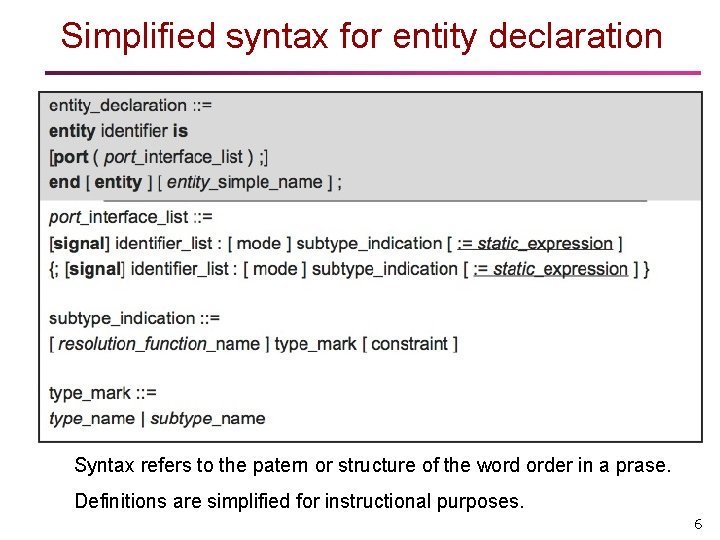

Simplified syntax for entity declaration Syntax refers to the patern or structure of the word order in a prase. Definitions are simplified for instructional purposes. 6

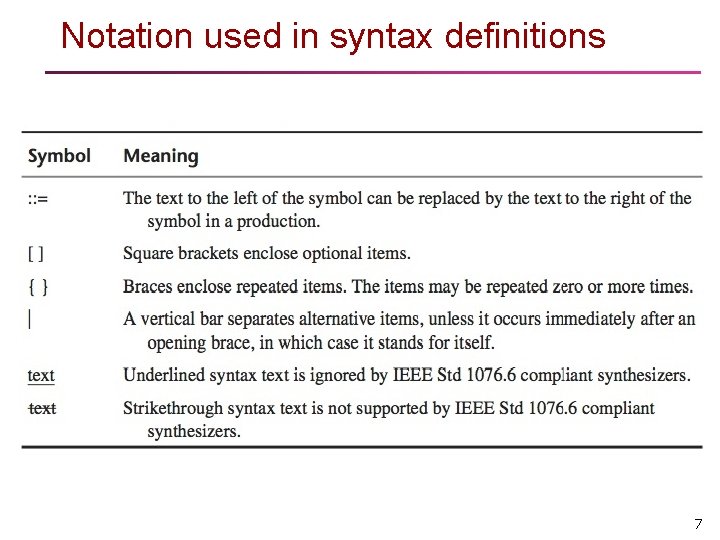

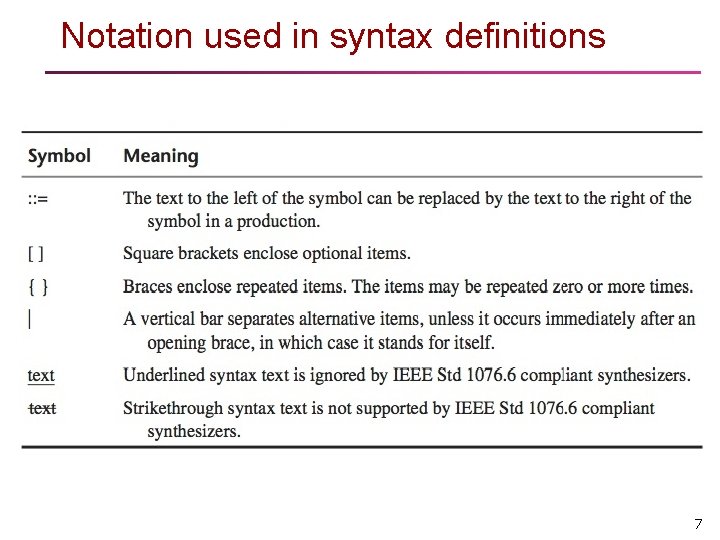

Notation used in syntax definitions 7

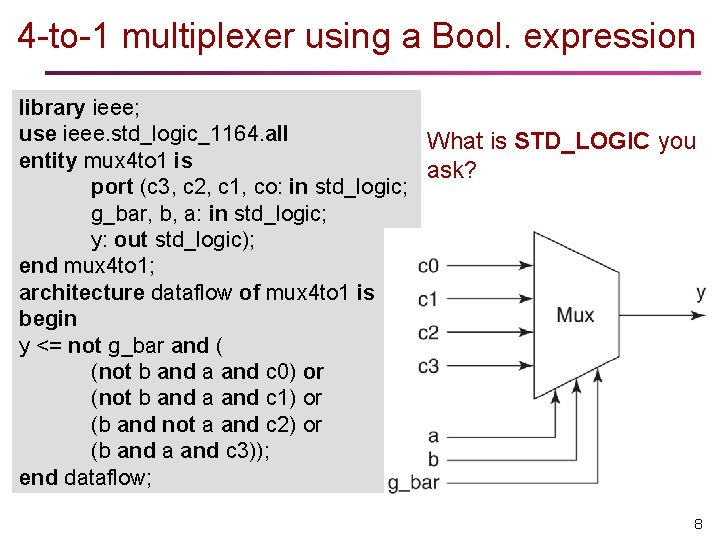

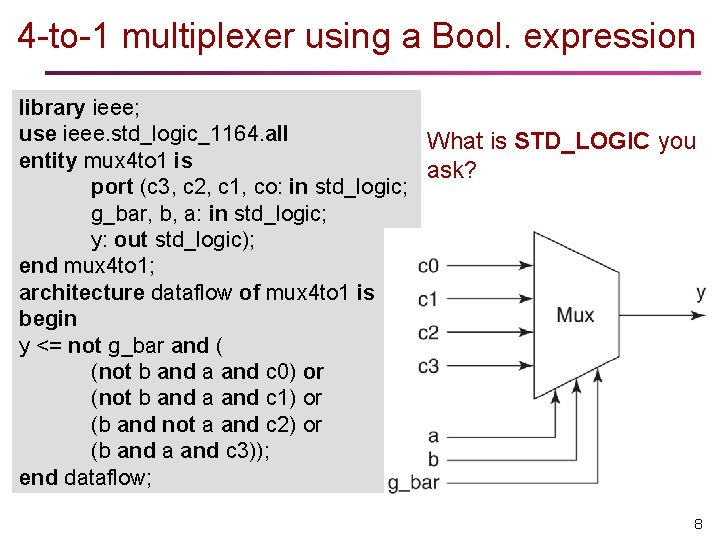

4 -to-1 multiplexer using a Bool. expression library ieee; use ieee. std_logic_1164. all What is STD_LOGIC you entity mux 4 to 1 is ask? port (c 3, c 2, c 1, co: in std_logic; g_bar, b, a: in std_logic; y: out std_logic); end mux 4 to 1; architecture dataflow of mux 4 to 1 is begin y <= not g_bar and ( (not b and a and c 0) or (not b and a and c 1) or (b and not a and c 2) or (b and a and c 3)); end dataflow; 8

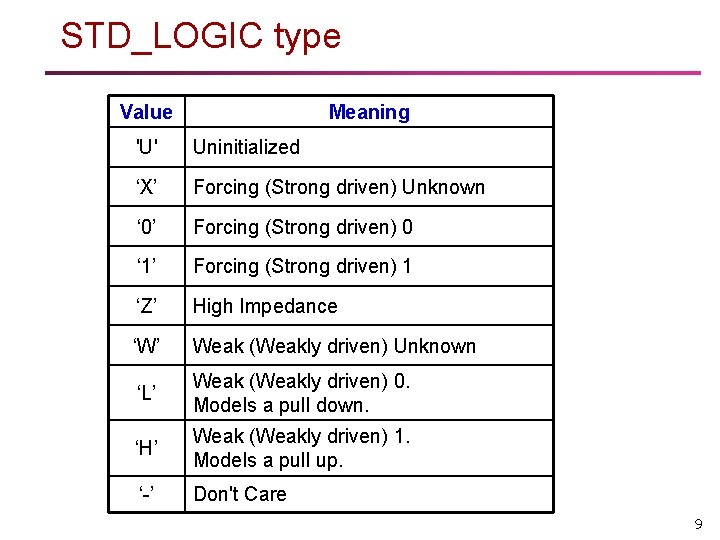

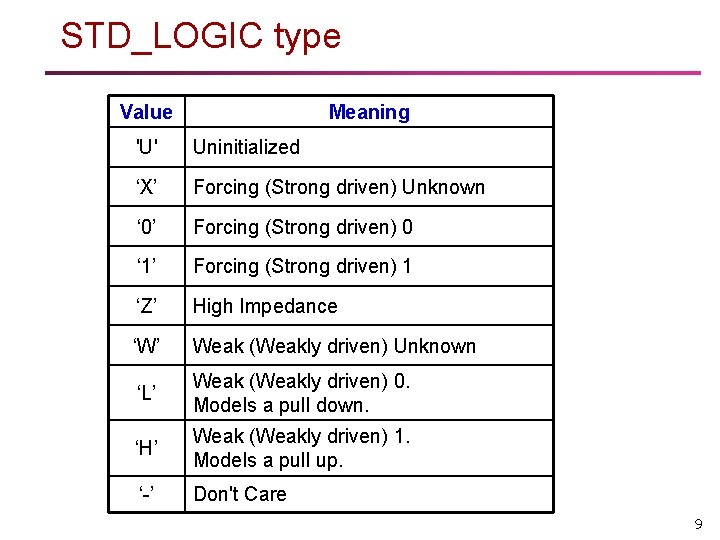

STD_LOGIC type Value Meaning 'U' Uninitialized ‘X’ Forcing (Strong driven) Unknown ‘ 0’ Forcing (Strong driven) 0 ‘ 1’ Forcing (Strong driven) 1 ‘Z’ High Impedance ‘W’ Weak (Weakly driven) Unknown ‘L’ Weak (Weakly driven) 0. Models a pull down. ‘H’ Weak (Weakly driven) 1. Models a pull up. ‘-’ Don't Care 9

BIT versus STD_LOGIC n n BIT type can only have a value of ‘ 0’ or ‘ 1’ STD_LOGIC can have nine values n 'U', ‘ 0’, ’ 1’, ’X’, ’Z’, ’W’, ’L’, ’H’, ’-’ n Useful mainly for simulation n ‘ 0’, ’ 1’, and ‘Z’ are synthesizable 10

Selected signal assignment statement Simplified syntax: with select_expression select signal_name <= value_expr_1 when choice_1, value_expr_2 when choice_2, value_expr_3 when choice_3, . . . value_expr_n when choice_n; The value of one and only one choice must equal the value of the select expression. 11

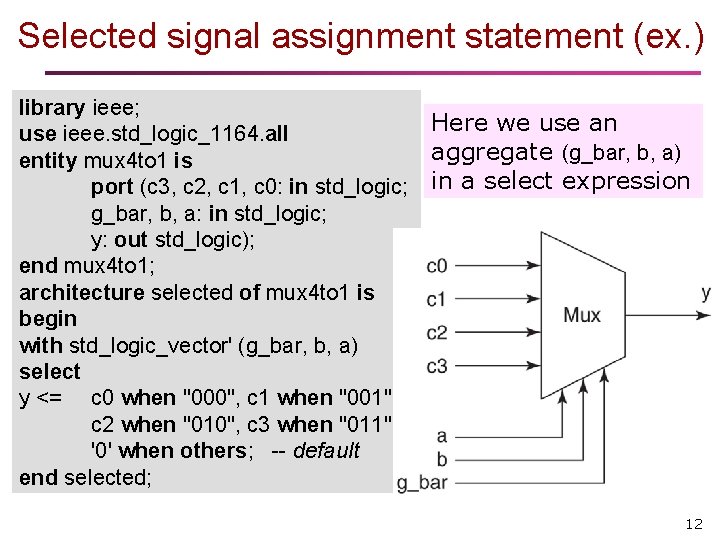

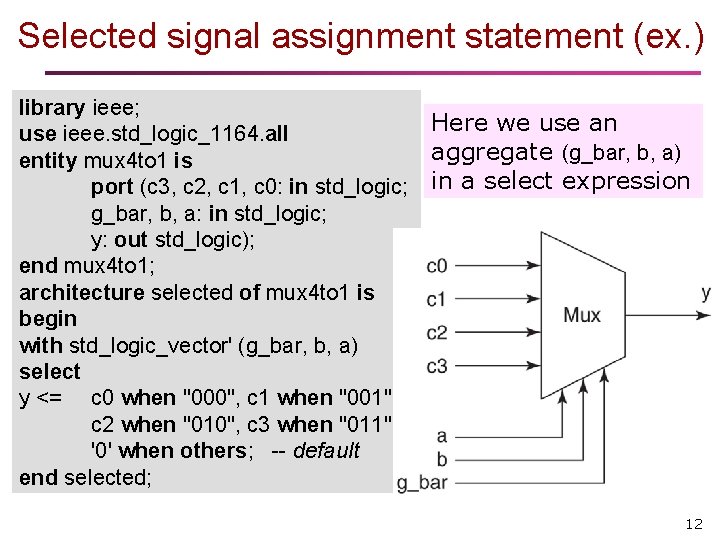

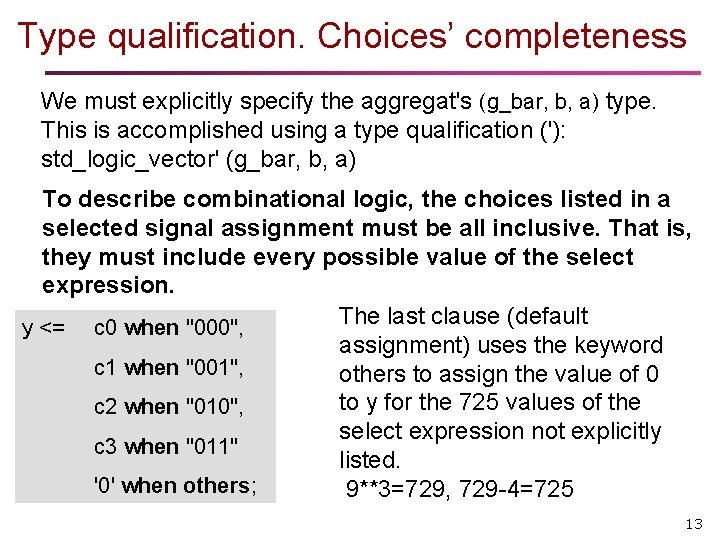

Selected signal assignment statement (ex. ) library ieee; use ieee. std_logic_1164. all entity mux 4 to 1 is port (c 3, c 2, c 1, c 0: in std_logic; g_bar, b, a: in std_logic; y: out std_logic); end mux 4 to 1; architecture selected of mux 4 to 1 is begin with std_logic_vector' (g_bar, b, a) select y <= c 0 when "000", c 1 when "001", c 2 when "010", c 3 when "011" '0' when others; -- default end selected; Here we use an aggregate (g_bar, b, a) in a select expression 12

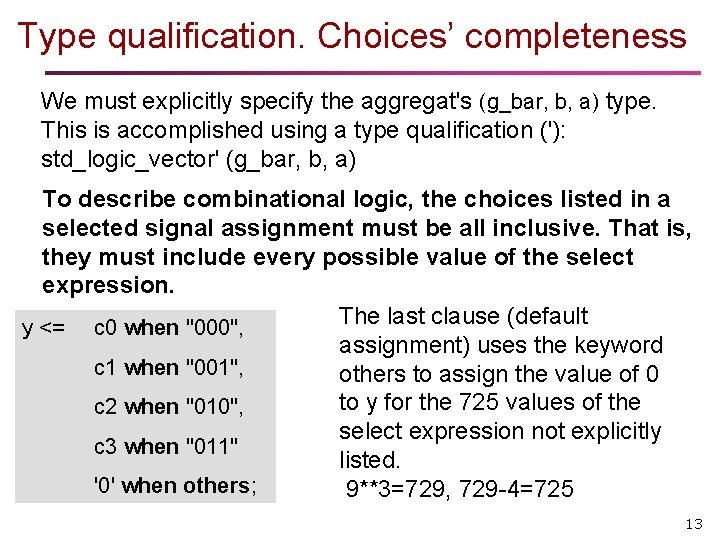

Type qualification. Choices’ completeness We must explicitly specify the aggregat's (g_bar, b, a) type. This is accomplished using a type qualification ('): std_logic_vector' (g_bar, b, a) To describe combinational logic, the choices listed in a selected signal assignment must be all inclusive. That is, they must include every possible value of the select expression. The last clause (default y <= c 0 when "000", assignment) uses the keyword c 1 when "001", others to assign the value of 0 to y for the 725 values of the c 2 when "010", select expression not explicitly c 3 when "011" listed. '0' when others; 9**3=729, 729 -4=725 13

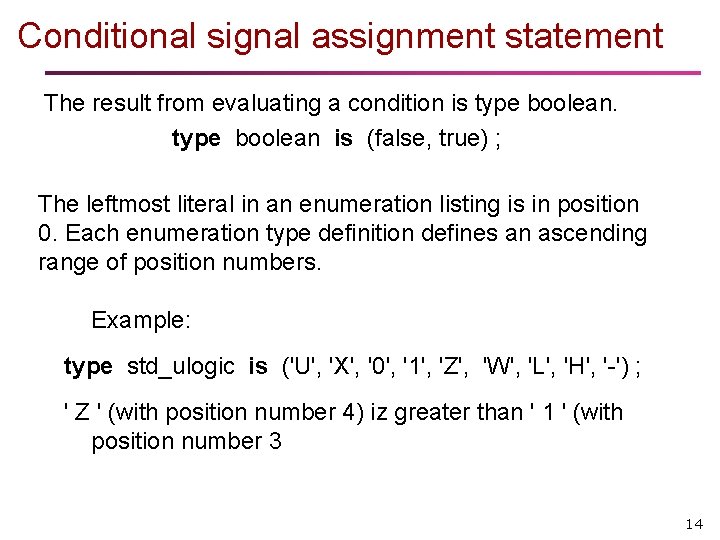

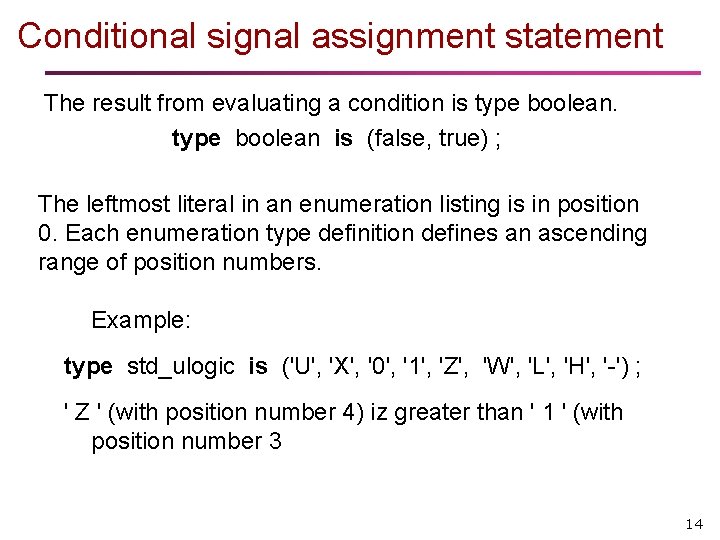

Conditional signal assignment statement The result from evaluating a condition is type boolean is (false, true) ; The leftmost literal in an enumeration listing is in position 0. Each enumeration type definition defines an ascending range of position numbers. Example: type std_ulogic is ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-') ; ' Z ' (with position number 4) iz greater than ' 1 ' (with position number 3 14

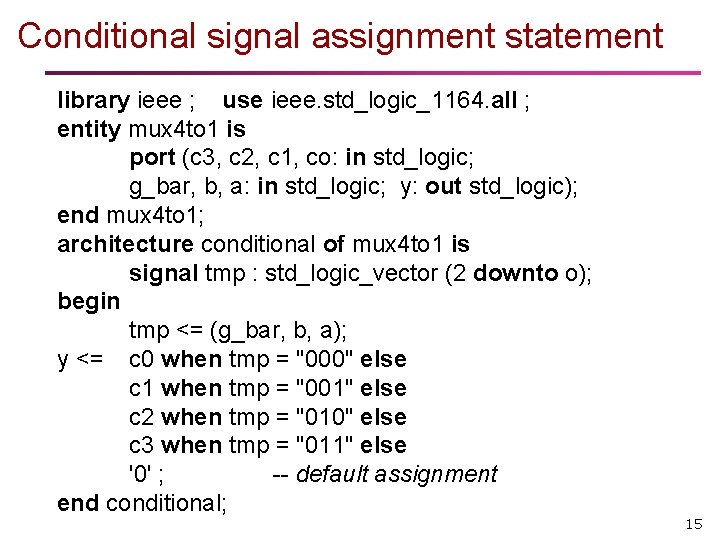

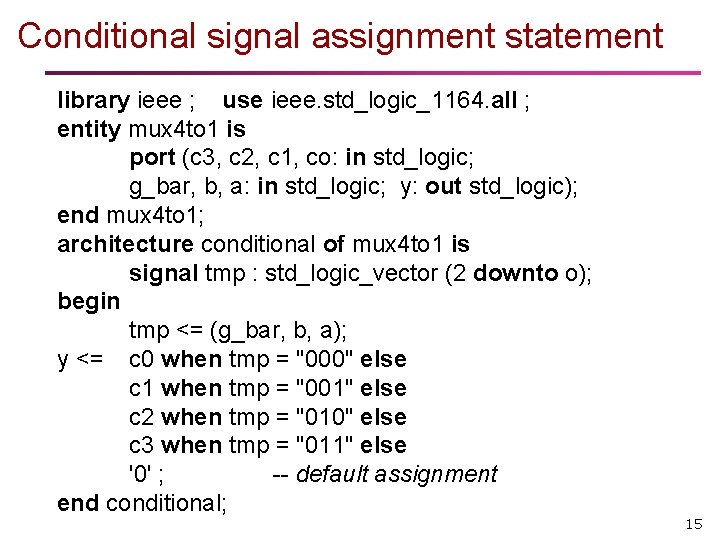

Conditional signal assignment statement library ieee ; use ieee. std_logic_1164. all ; entity mux 4 to 1 is port (c 3, c 2, c 1, co: in std_logic; g_bar, b, a: in std_logic; y: out std_logic); end mux 4 to 1; architecture conditional of mux 4 to 1 is signal tmp : std_logic_vector (2 downto o); begin tmp <= (g_bar, b, a); y <= c 0 when tmp = "000" else c 1 when tmp = "001" else c 2 when tmp = "010" else c 3 when tmp = "011" else '0' ; -- default assignment end conditional; 15

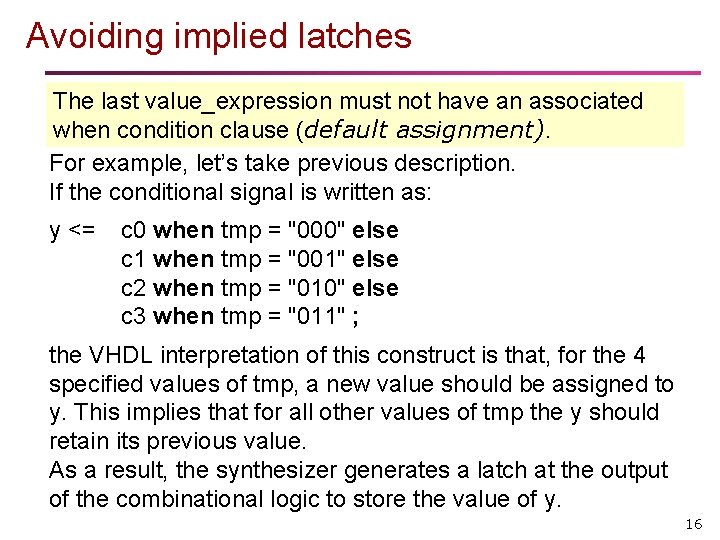

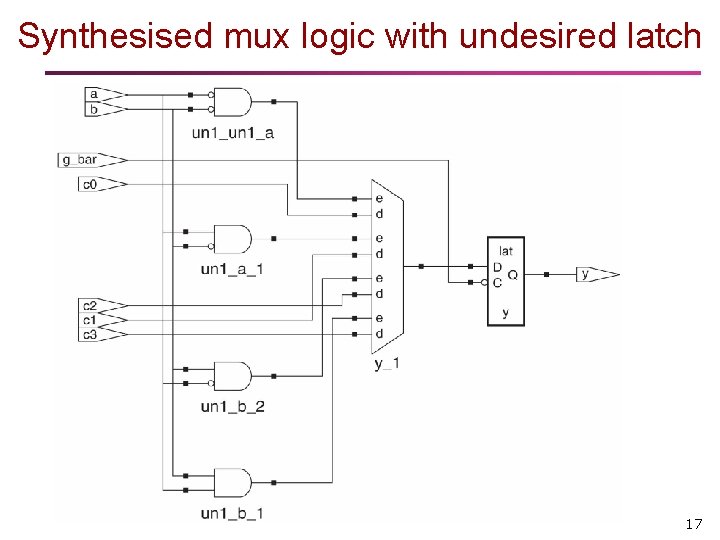

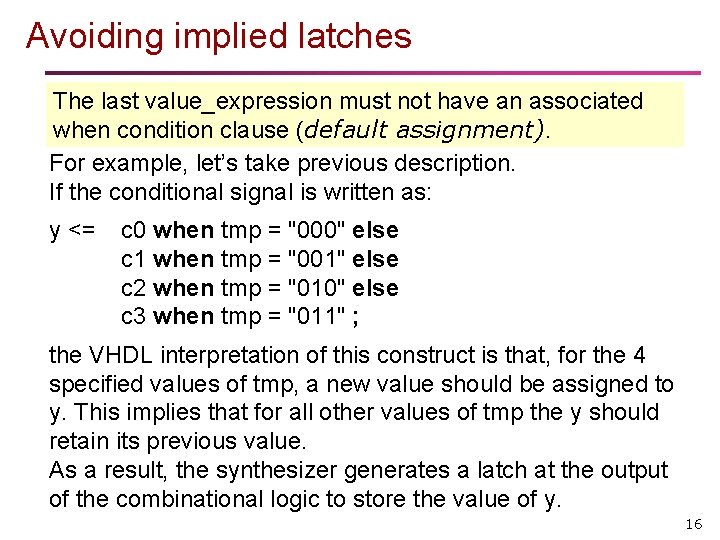

Avoiding implied latches The last value_expression must not have an associated when condition clause (default assignment). For example, let’s take previous description. If the conditional signal is written as: y <= c 0 when tmp = "000" else c 1 when tmp = "001" else c 2 when tmp = "010" else c 3 when tmp = "011" ; the VHDL interpretation of this construct is that, for the 4 specified values of tmp, a new value should be assigned to y. This implies that for all other values of tmp the y should retain its previous value. As a result, the synthesizer generates a latch at the output of the combinational logic to store the value of y. 16

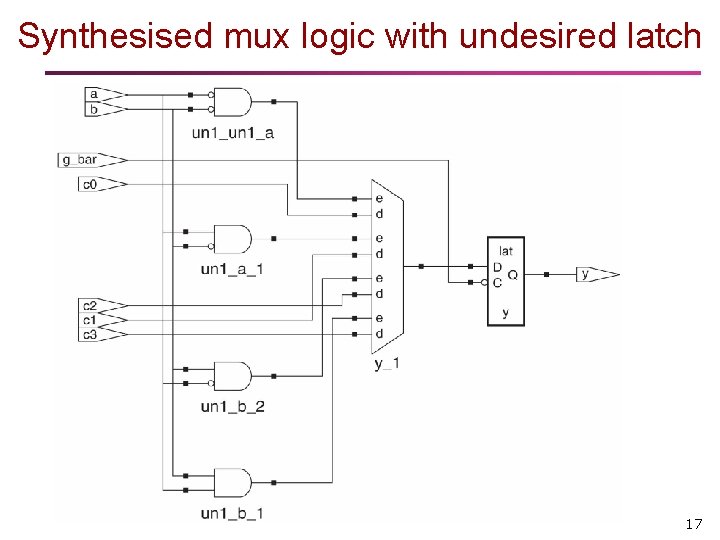

Synthesised mux logic with undesired latch 17