IA64 Architecture RISC designed to cooperate with the

- Slides: 8

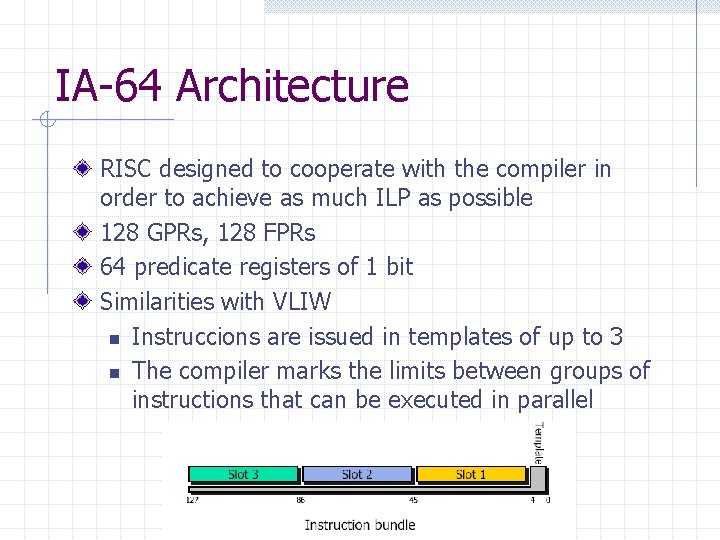

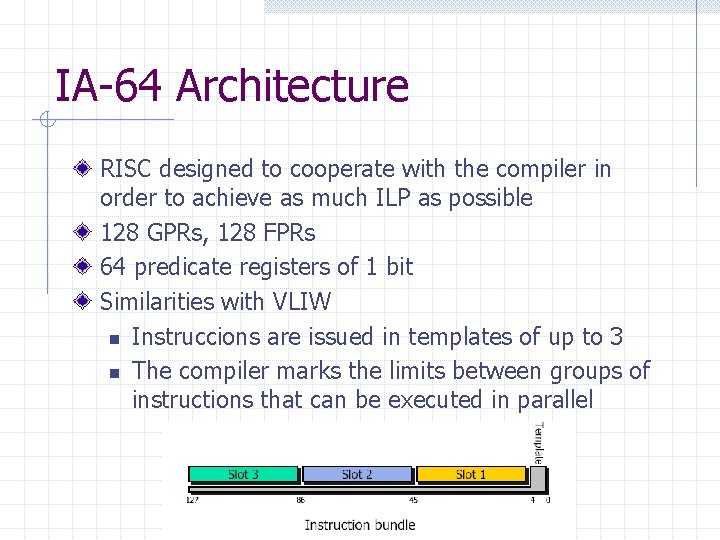

IA-64 Architecture RISC designed to cooperate with the compiler in order to achieve as much ILP as possible 128 GPRs, 128 FPRs 64 predicate registers of 1 bit Similarities with VLIW n Instruccions are issued in templates of up to 3 n The compiler marks the limits between groups of instructions that can be executed in parallel

Predication in IA-64 Particularly useful for branches difficult to predict Increases ILP, but can also increase critical path length Predication on registers that mark the result of the conditions for conditional branches Allows the parallel execution of several branches IA-64 allows to predicate almost all its instructions

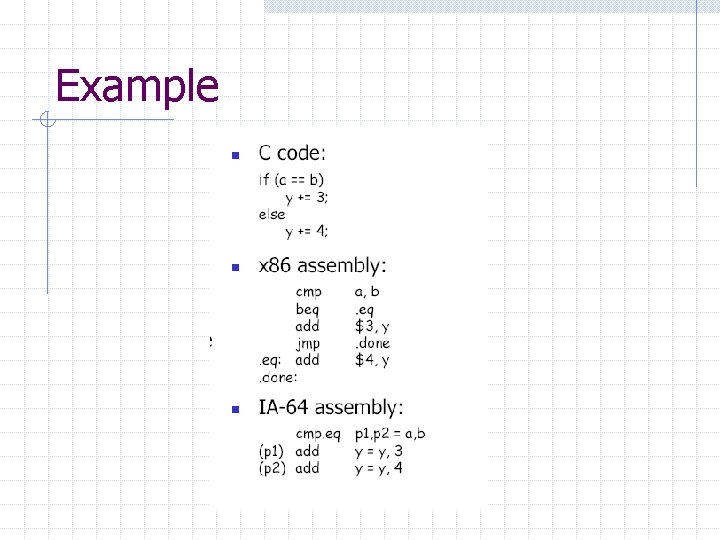

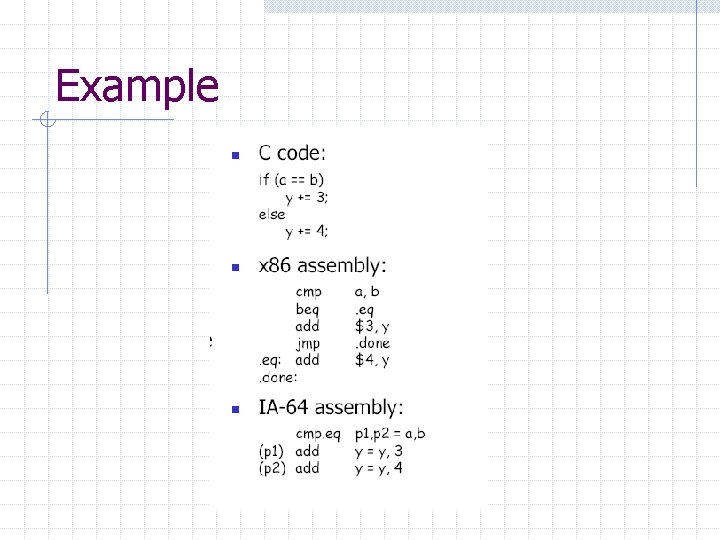

Example

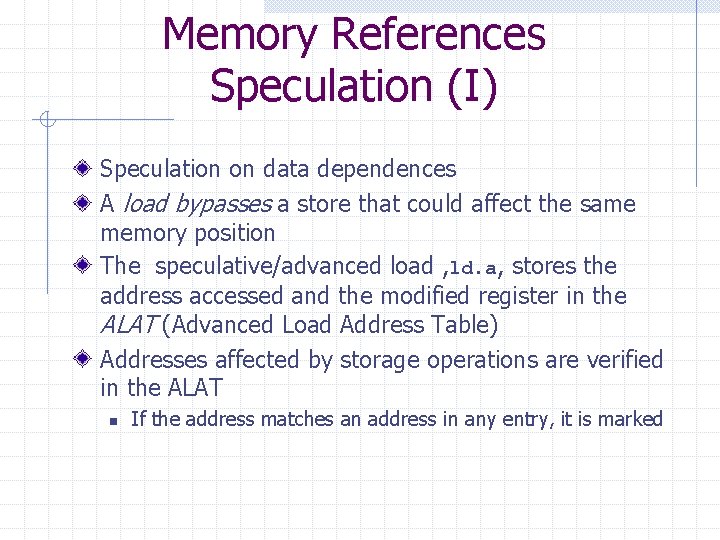

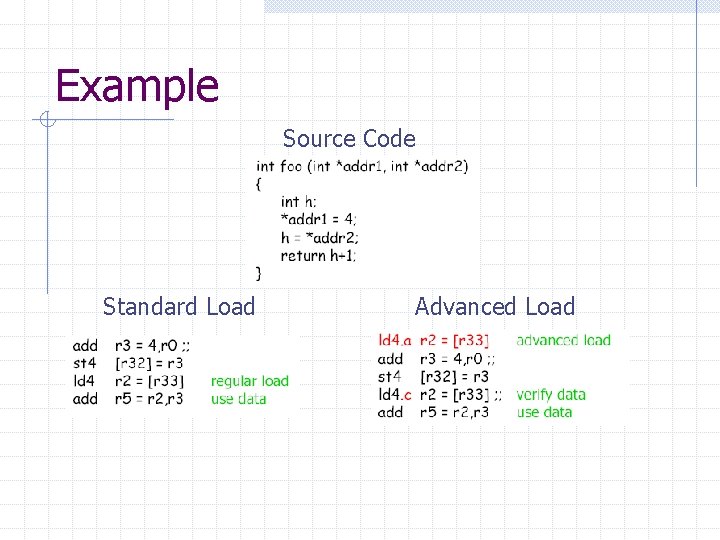

Memory References Speculation (I) Speculation on data dependences A load bypasses a store that could affect the same memory position The speculative/advanced load , ld. a, stores the address accessed and the modified register in the ALAT (Advanced Load Address Table) Addresses affected by storage operations are verified in the ALAT n If the address matches an address in any entry, it is marked

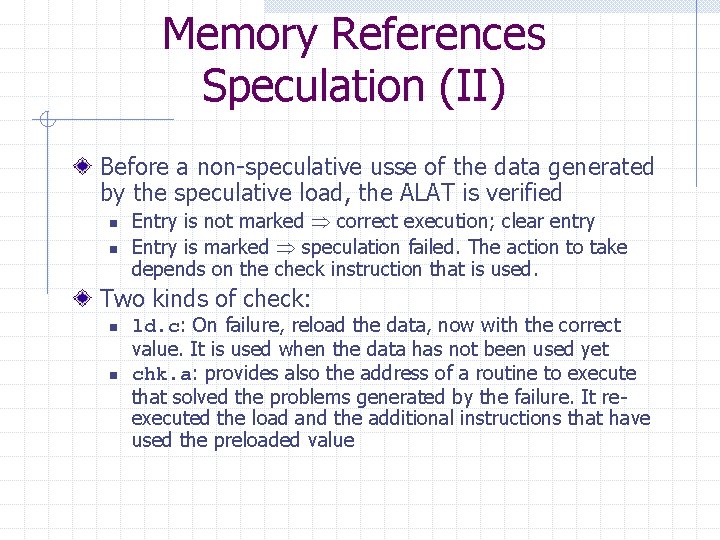

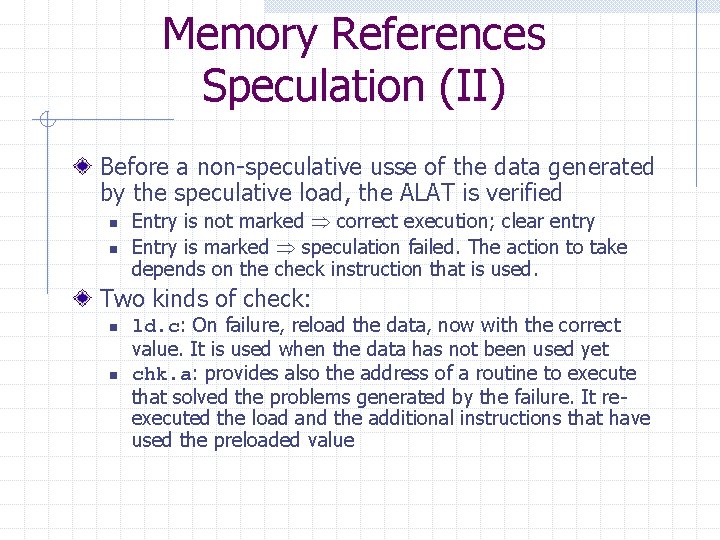

Memory References Speculation (II) Before a non-speculative usse of the data generated by the speculative load, the ALAT is verified n n Entry is not marked correct execution; clear entry Entry is marked speculation failed. The action to take depends on the check instruction that is used. Two kinds of check: n n ld. c: On failure, reload the data, now with the correct value. It is used when the data has not been used yet chk. a: provides also the address of a routine to execute that solved the problems generated by the failure. It reexecuted the load and the additional instructions that have used the preloaded value

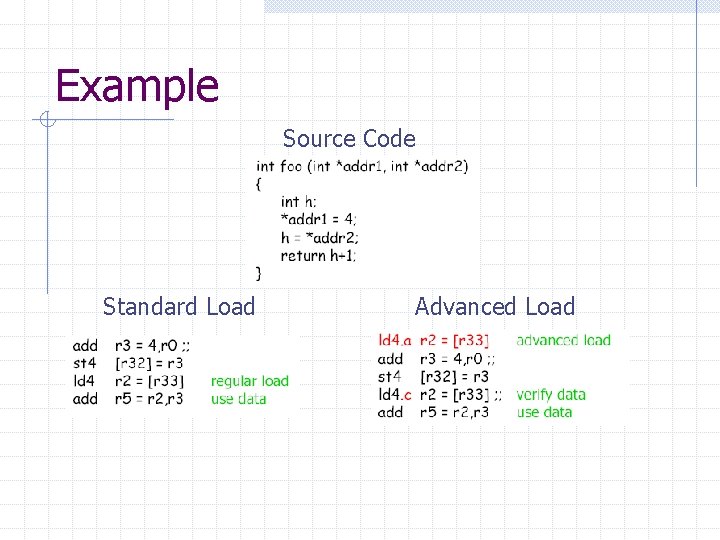

Example Source Code Standard Load Advanced Load

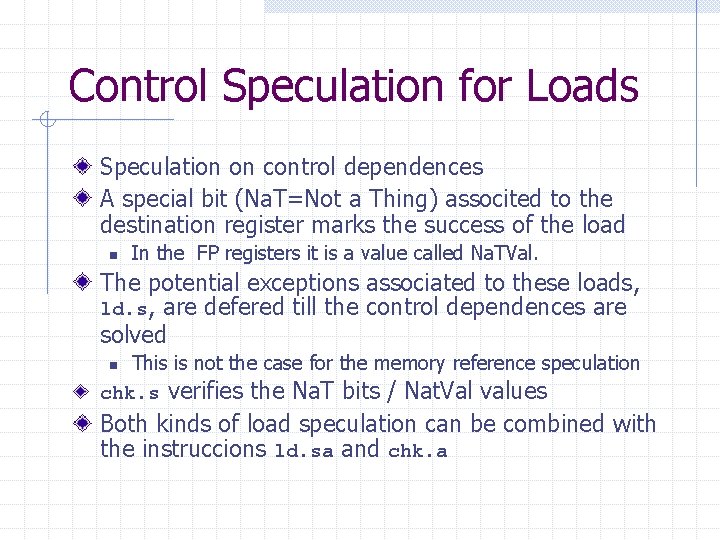

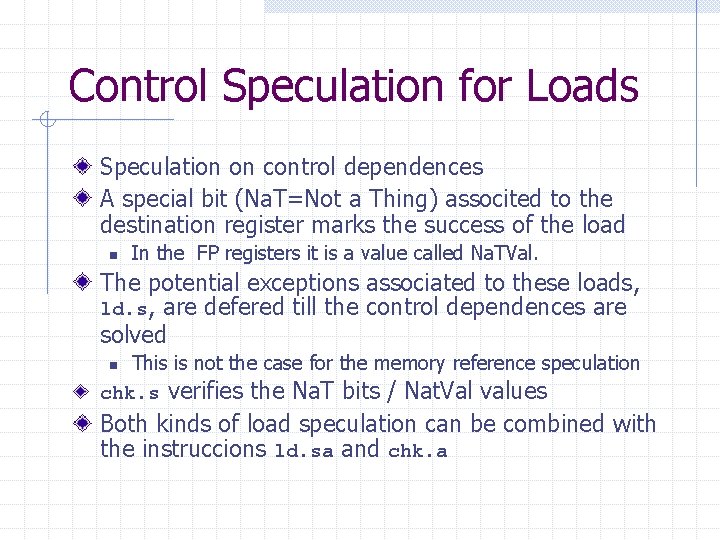

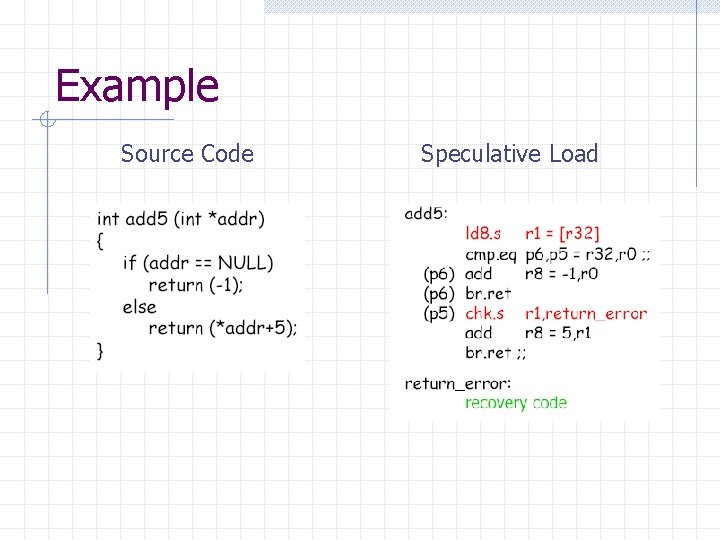

Control Speculation for Loads Speculation on control dependences A special bit (Na. T=Not a Thing) associted to the destination register marks the success of the load n In the FP registers it is a value called Na. TVal. The potential exceptions associated to these loads, ld. s, are defered till the control dependences are solved This is not the case for the memory reference speculation chk. s verifies the Na. T bits / Nat. Val values n Both kinds of load speculation can be combined with the instruccions ld. sa and chk. a

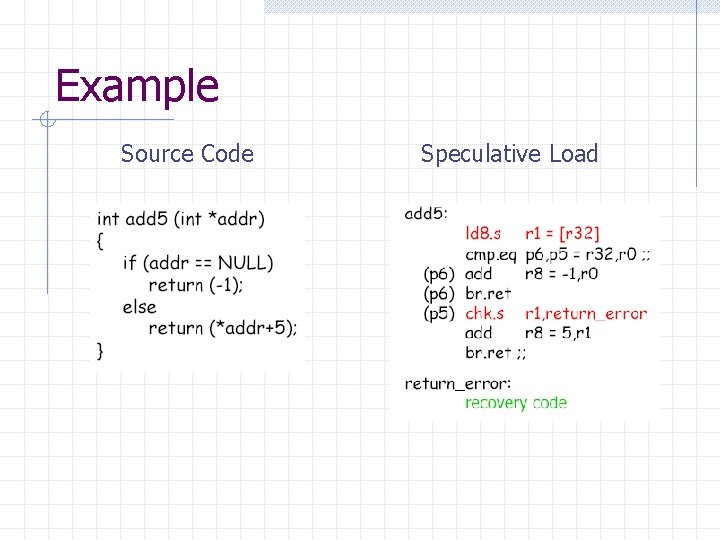

Example Source Code Speculative Load