Hybrid cache architecture for highspeed packet processing Authors

Hybrid cache architecture for high-speed packet processing Authors: Z. Liu, K. Zheng and B. Liu Publisher: Computers & Digital Techniques, IET; Volume 1, Issue 2, March 2007 Page(s): 105 – 112 Present: Fang-Chen, Kuo (郭芳辰) Date: December, 18, 2007 Department of Computer Science and Information Engineering National Cheng Kung University, Taiwan R. O. C. 1

Outline l Split-Control Cache l Memory Scheduler Performance Evaluation l • App-Cache • Flow-Cache 2

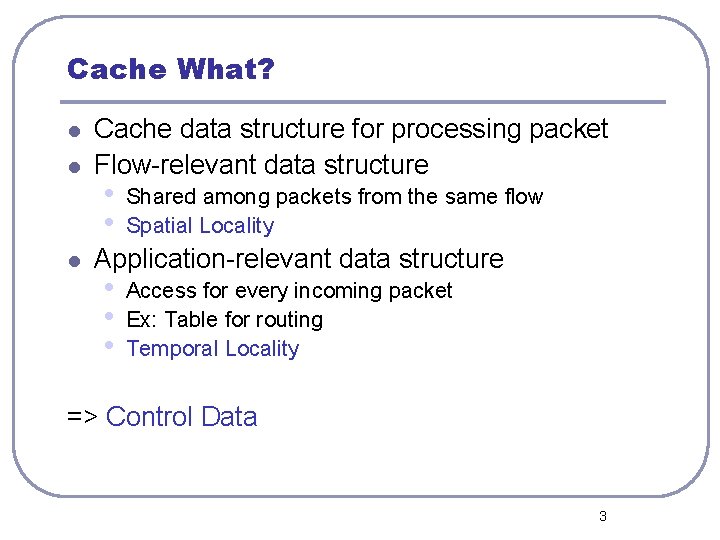

Cache What? l l l Cache data structure for processing packet Flow-relevant data structure • • Shared among packets from the same flow Spatial Locality Application-relevant data structure • • • Access for every incoming packet Ex: Table for routing Temporal Locality => Control Data 3

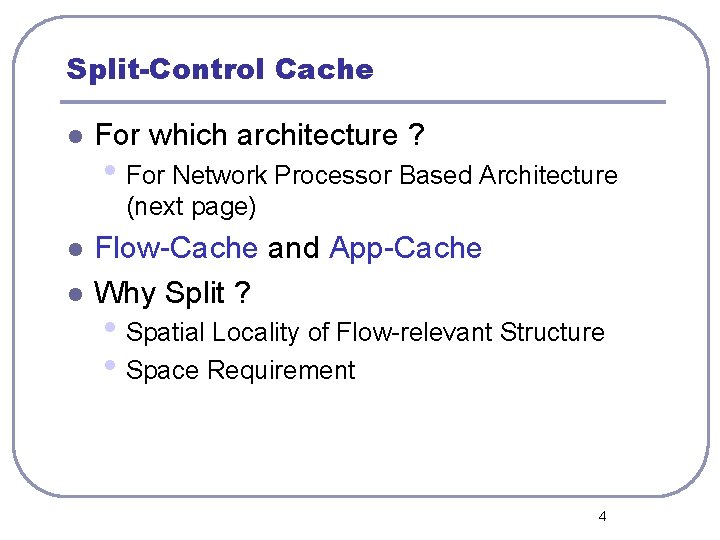

Split-Control Cache l For which architecture ? • For Network Processor Based Architecture (next page) l l Flow-Cache and App-Cache Why Split ? • Spatial Locality of Flow-relevant Structure • Space Requirement 4

Base NP Architecture (AMCC n. P 3700) Notice that the packet classification is done by Coprocessor. 5

App-Cache l The app-cache has the same organization with conventional caches. 6

Split-Control Cache Architecture 7

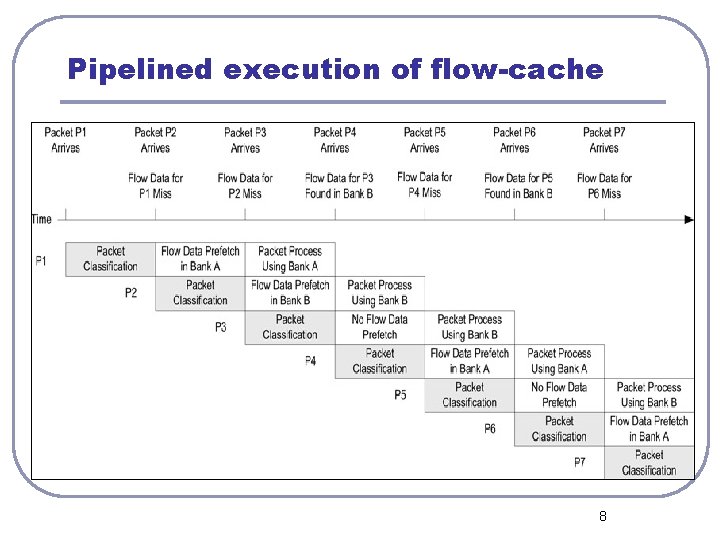

Pipelined execution of flow-cache 8

Flow-Cache Architecture 9

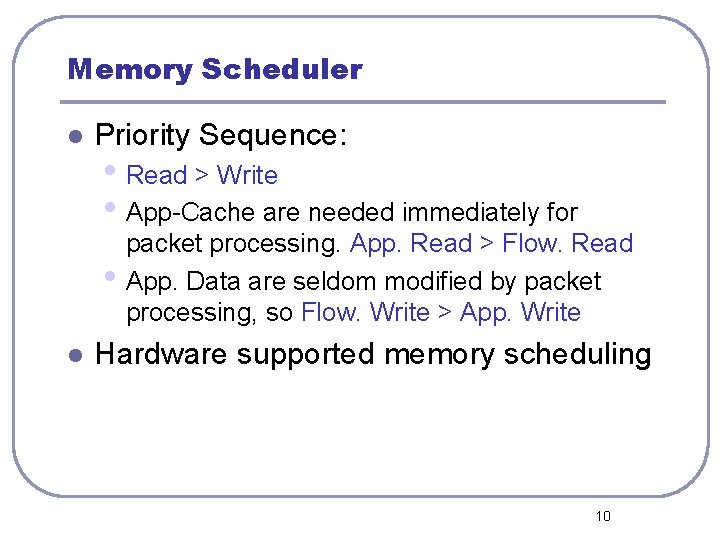

Memory Scheduler l Priority Sequence: • Read > Write • App-Cache are needed immediately for • l packet processing. App. Read > Flow. Read App. Data are seldom modified by packet processing, so Flow. Write > App. Write Hardware supported memory scheduling 10

- Slides: 10