Hybrid and ASIC Issues from MIWG Phil Allport

Hybrid and ASIC Issues from MIWG Phil Allport Module Integration Working Group 17 th April 2007 • Useful Links • Module ASIC Discussion • ASIC Review • Hybrid Discussions • Conclusions

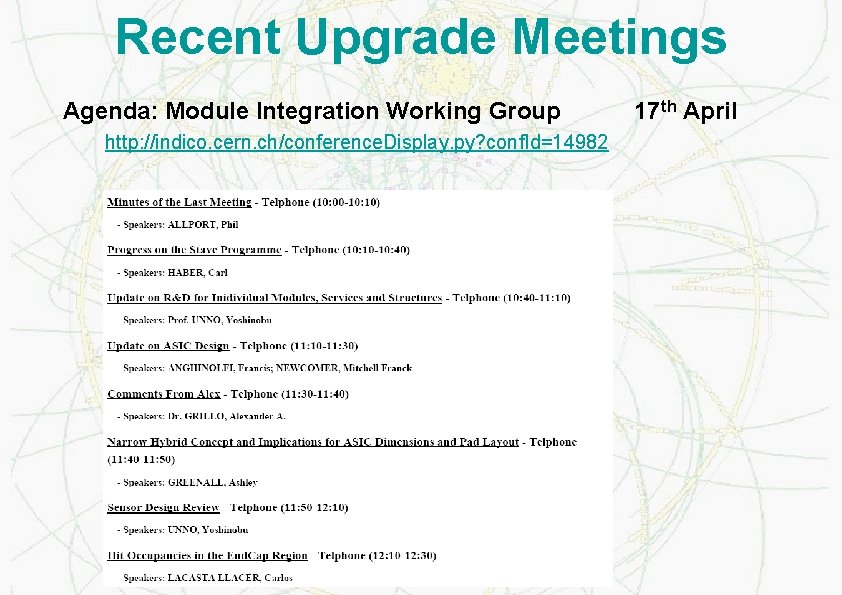

Recent Upgrade Meetings Agenda: Module Integration Working Group http: //indico. cern. ch/conference. Display. py? conf. Id=14982 17 th April

Recent Upgrade Meetings The focus was on recent developments in both the stave and wide sensor module concepts. In addition, the meeting discussed some of the recent ideas coming out of the ASIC review and made several recommendations based on the following inputs: • ABC-next Preview (07/3/07) http: //indico. cern. ch/conference. Display. py? conf. Id=12921 • ABC-next (12/4/07) http: //indico. cern. ch/conference. Display. py? conf. Id=14966 Also of relevance to the module integration group activities is the material in thermal management group: • Thermal Management Working Group (27/2/07) http: //indico. cern. ch/conference. Display. py? conf. Id=12941

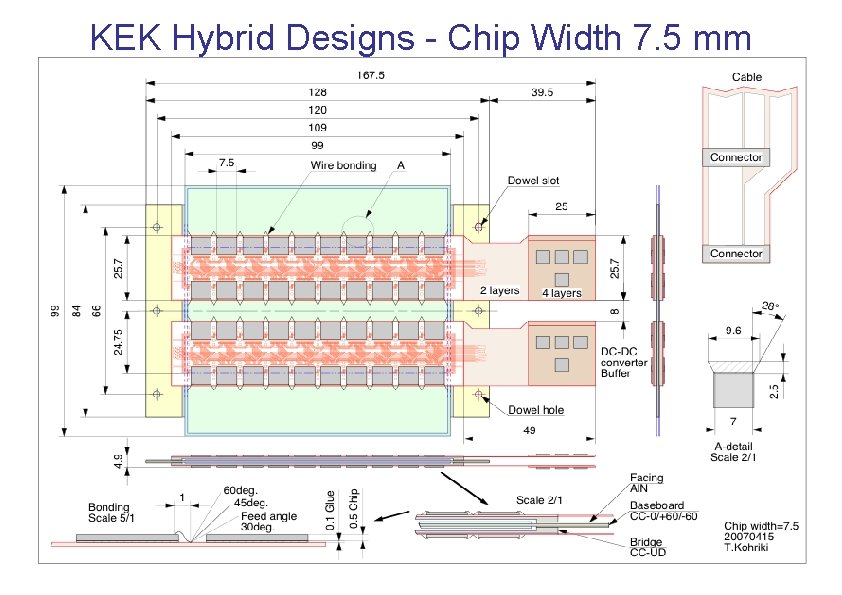

Module ASIC Concerns § Two new wide module concepts were presented § With 40 chips per sensor face, ideas with read-out separated for the two faces are advantageous and the occupancy (even at 160 MHz clocking, may limit us to ≤ 10 chips read out serially). § The idea of a Module Controller Chip to provide read-out control for groups of 10 or less ABCNs, DCS functionality, data buffering, power, … looks very attractive § While a perfect match to the sensor pitch is not possible and some space is needed for FE capacitive decoupling between ASICs, 7. 5 mm chip width both allows bonding without a fan-in, hybrid rework and adequate space between ASICs (see next slide) This will reduce the length (and hence the material of the hybrid) and possibly with a wider chip its length can further be reduced

KEK Hybrid Designs - Chip Width 7. 5 mm

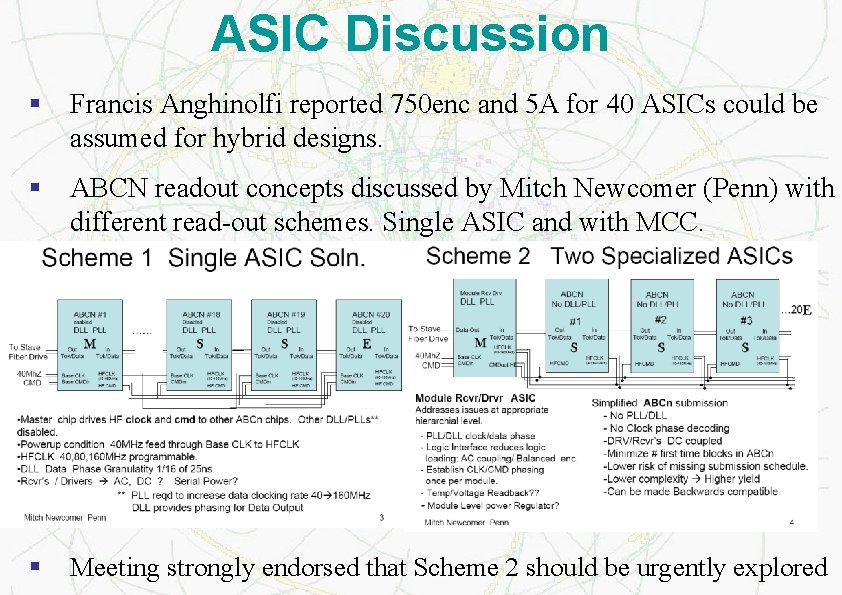

ASIC Discussion § Francis Anghinolfi reported 750 enc and 5 A for 40 ASICs could be assumed for hybrid designs. § ABCN readout concepts discussed by Mitch Newcomer (Penn) with different read-out schemes. Single ASIC and with MCC. § Meeting strongly endorsed that Scheme 2 should be urgently explored

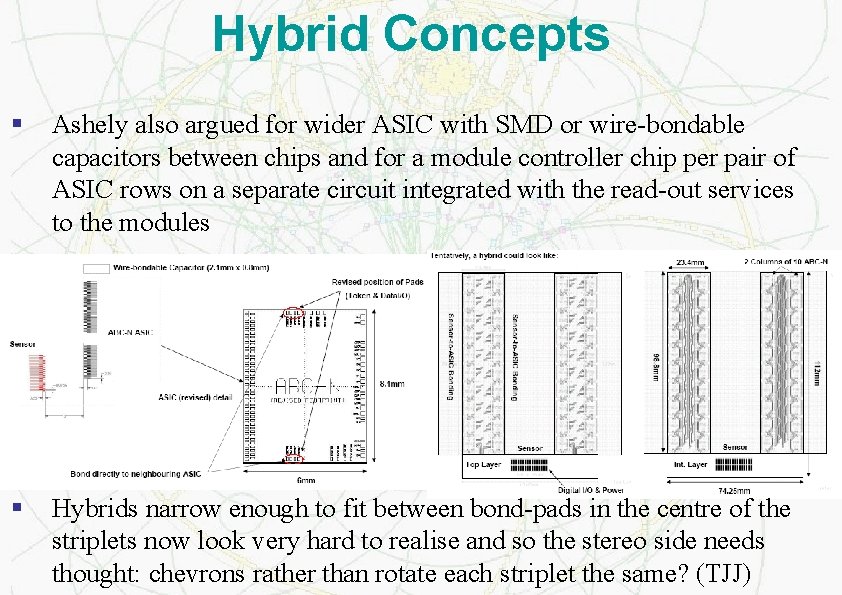

Hybrid Concepts § Ashely also argued for wider ASIC with SMD or wire-bondable capacitors between chips and for a module controller chip per pair of ASIC rows on a separate circuit integrated with the read-out services to the modules § Hybrids narrow enough to fit between bond-pads in the centre of the striplets now look very hard to realise and so the stereo side needs thought: chevrons rather than rotate each striplet the same? (TJJ)

Conclusions • We need to know whether the occupancy will be such that we can read out 6 or 10 or 20 ASICs serially • We need to coordinate hybrid designs with the HPK sensor order assuming module prototyping for the next 18/24 months will depend on this order (and include plenty of “mechanicals”) • We should design the ASIC to match the pitches appropriate for LHC and do away with the need for pitch adaptors saving bonding time, assembly complexity, hybrid length (how much? ) and material • We should specify and try to see how best to realise a Module Controller Chip (MCC)

- Slides: 8