HWSW Codesign Lecture 1 Basic Concepts Lab Environment

HW/SW Co-design Lecture 1: Basic Concepts & Lab Environment Course material designed by Professor Yarsun Hsu, EE Dept, NTHU RA: Yi-Chiun Fang, EE Dept, NTHU

Outline Introduction to HW/SW Co-design Introduction to the Hardware Environment Introduction to the Software Environment

INTRODUCTION TO HW/SW CO -DESIGN

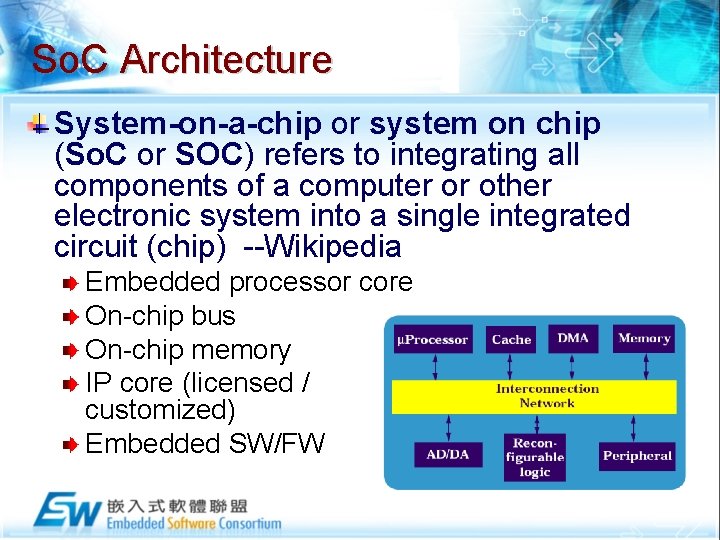

So. C Architecture System-on-a-chip or system on chip (So. C or SOC) refers to integrating all components of a computer or other electronic system into a single integrated circuit (chip) --Wikipedia Embedded processor core On-chip bus On-chip memory IP core (licensed / customized) Embedded SW/FW

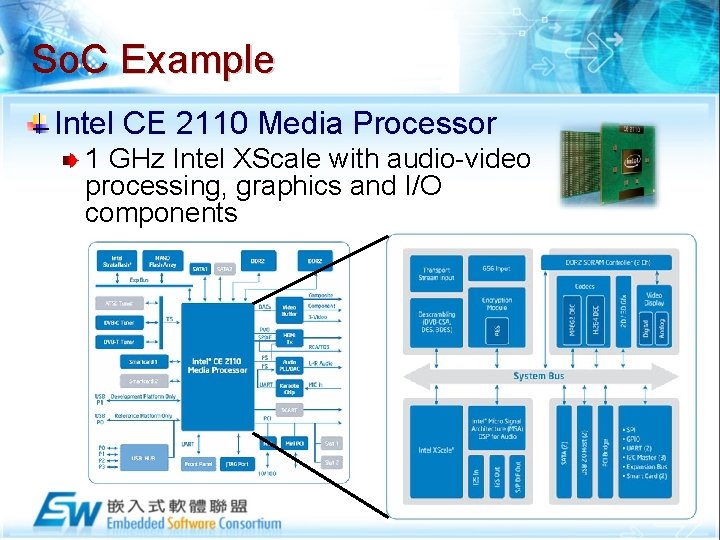

So. C Example Intel CE 2110 Media Processor 1 GHz Intel XScale with audio-video processing, graphics and I/O components

HW/SW Co-design (1/2) Embedded systems are systems which are designed to meet certain application objectives Design of embedded systems may have many different types of constraints Timing, size, weight, power consumption, reliability, cost, …

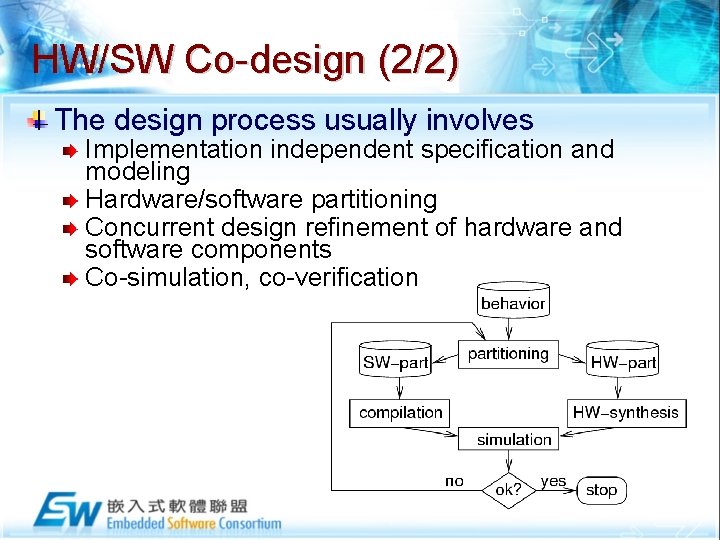

HW/SW Co-design (2/2) The design process usually involves Implementation independent specification and modeling Hardware/software partitioning Concurrent design refinement of hardware and software components Co-simulation, co-verification

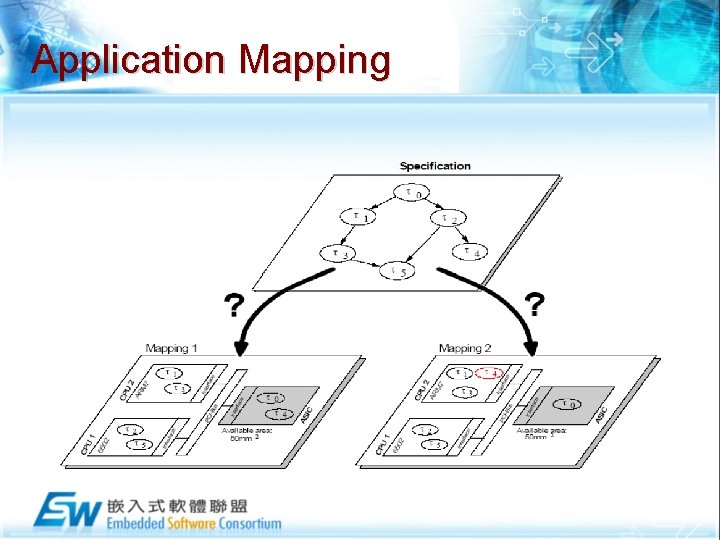

Application Mapping

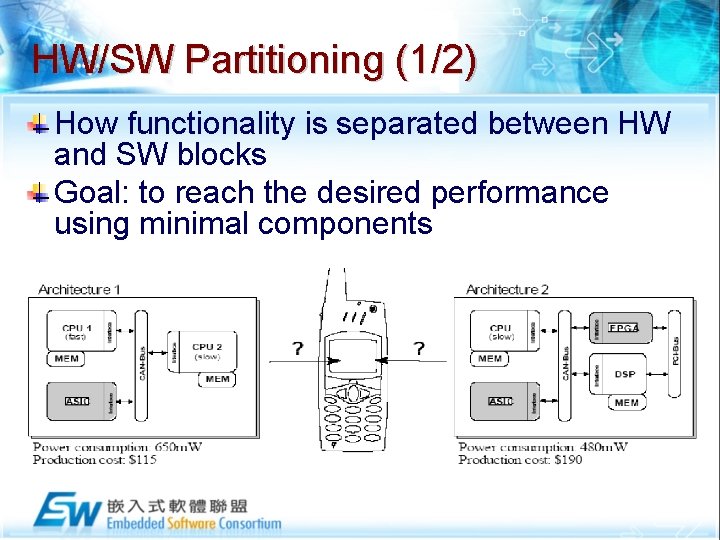

HW/SW Partitioning (1/2) How functionality is separated between HW and SW blocks Goal: to reach the desired performance using minimal components

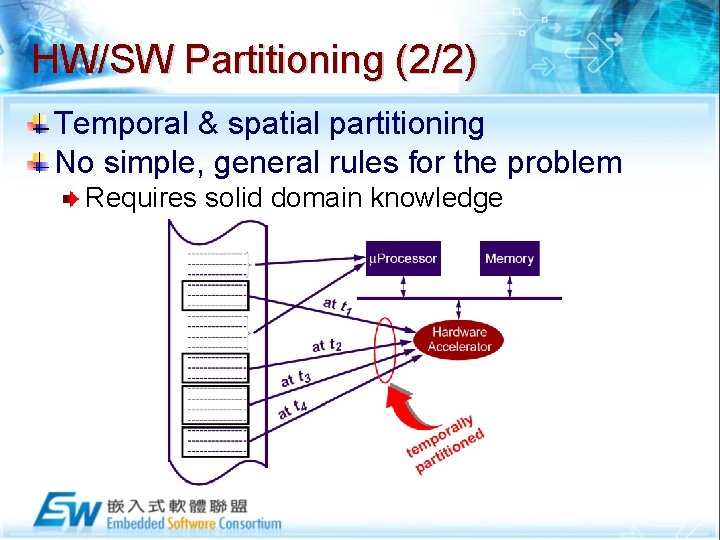

HW/SW Partitioning (2/2) Temporal & spatial partitioning No simple, general rules for the problem Requires solid domain knowledge

Communication Needed when two components of a system need to interact with each other SW communication Function call, global variable, network message, etc. HW communication Interconnection wire, shared memory, register file, mailbox, etc.

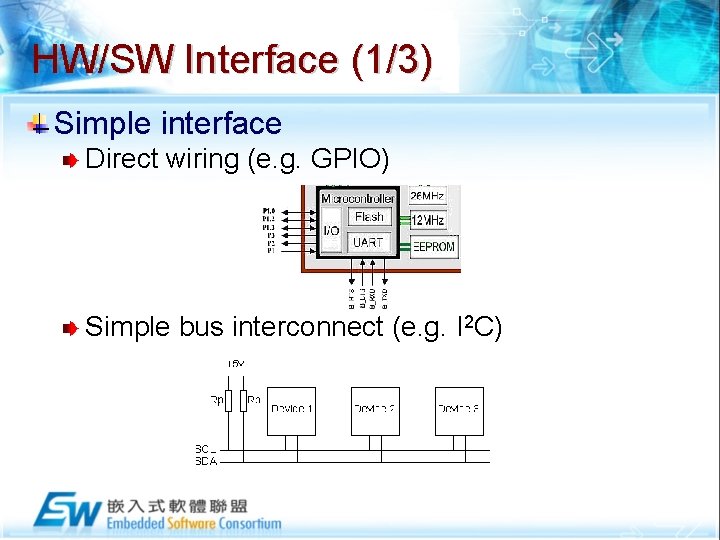

HW/SW Interface (1/3) Simple interface Direct wiring (e. g. GPIO) Simple bus interconnect (e. g. I 2 C)

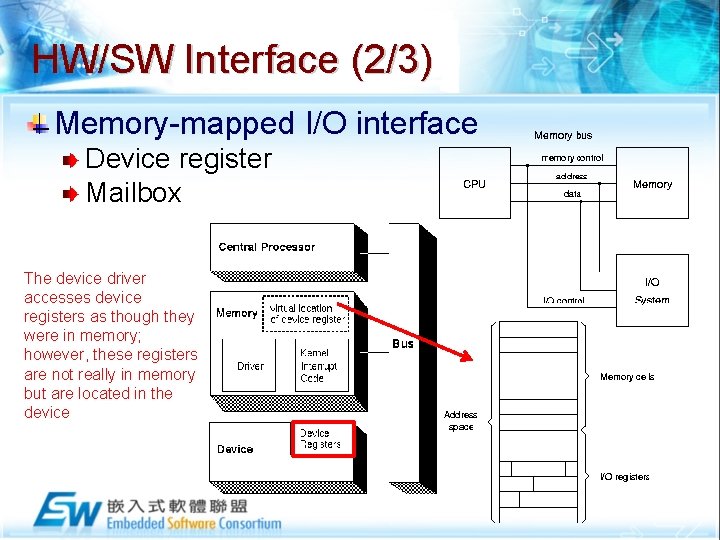

HW/SW Interface (2/3) Memory-mapped I/O interface Device register Mailbox The device driver accesses device registers as though they were in memory; however, these registers are not really in memory but are located in the device

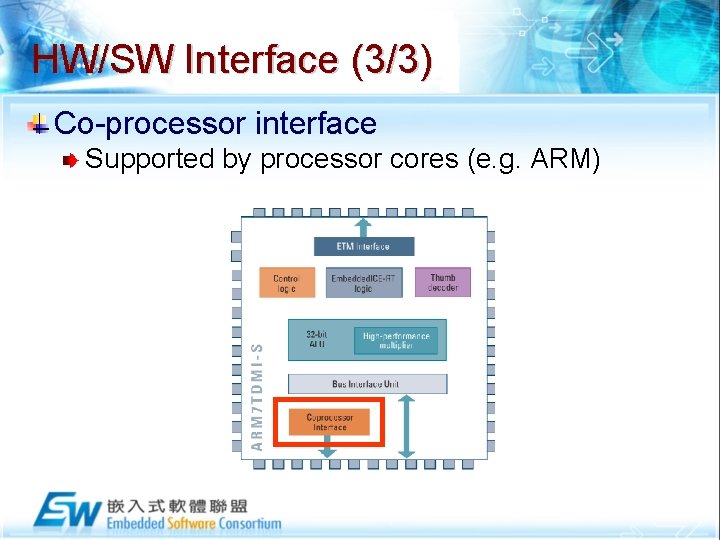

HW/SW Interface (3/3) Co-processor interface Supported by processor cores (e. g. ARM)

INTRODUCTION TO THE HARDWARE ENVIRONMENT

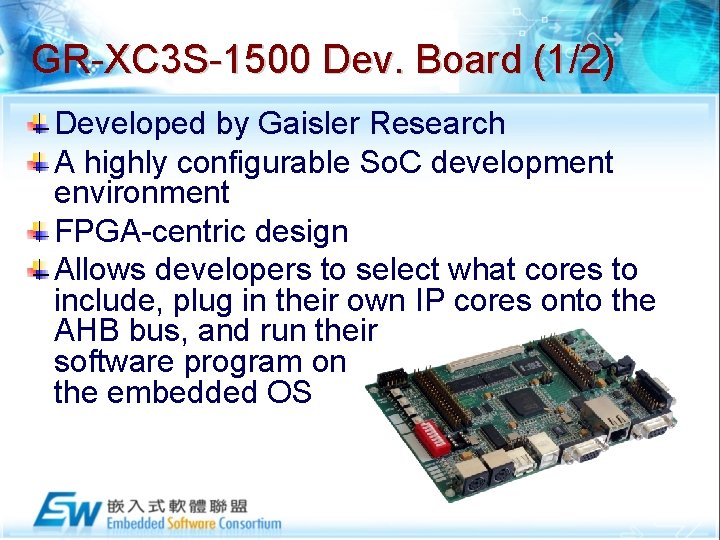

GR-XC 3 S-1500 Dev. Board (1/2) Developed by Gaisler Research A highly configurable So. C development environment FPGA-centric design Allows developers to select what cores to include, plug in their own IP cores onto the AHB bus, and run their software program on the embedded OS

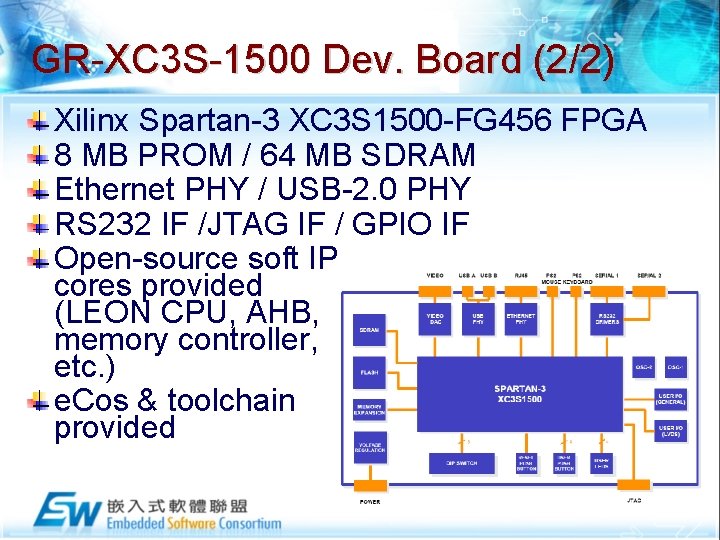

GR-XC 3 S-1500 Dev. Board (2/2) Xilinx Spartan-3 XC 3 S 1500 -FG 456 FPGA 8 MB PROM / 64 MB SDRAM Ethernet PHY / USB-2. 0 PHY RS 232 IF /JTAG IF / GPIO IF Open-source soft IP cores provided (LEON CPU, AHB, memory controller, etc. ) e. Cos & toolchain provided

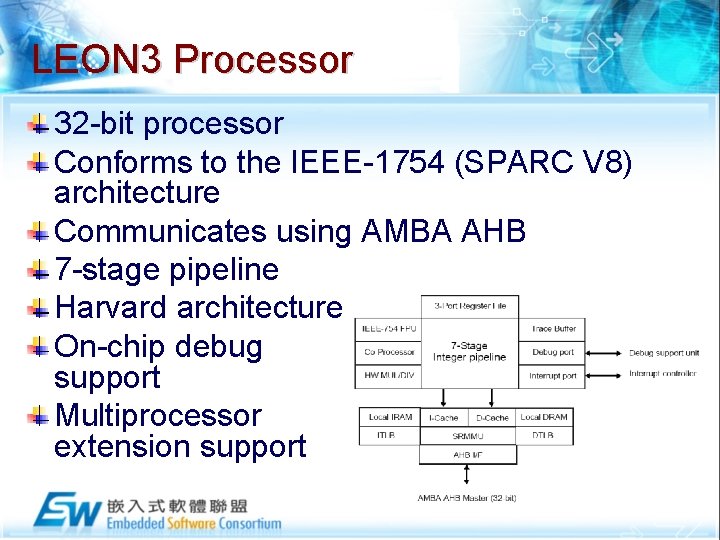

LEON 3 Processor 32 -bit processor Conforms to the IEEE-1754 (SPARC V 8) architecture Communicates using AMBA AHB 7 -stage pipeline Harvard architecture On-chip debug support Multiprocessor extension support

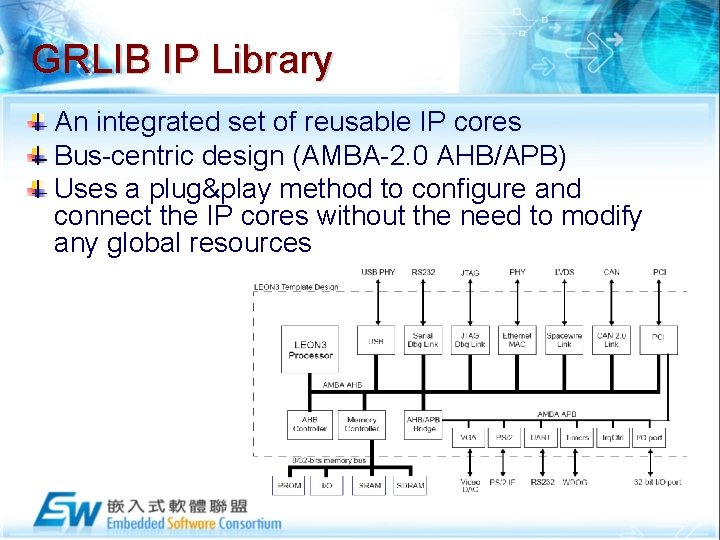

GRLIB IP Library An integrated set of reusable IP cores Bus-centric design (AMBA-2. 0 AHB/APB) Uses a plug&play method to configure and connect the IP cores without the need to modify any global resources

INTRODUCTION TO THE SOFTWARE ENVIRONMENT

Xilinx ISE A complete FPGA/CPLD programmable logic design suite Specification of programmable logic, via schematic capture or Verilog/VHDL Synthesis and fit of specified logic into Xilinx Spartan devices Behavioral and post-fit simulation Download of configuration into target device via communications cable (ISE i. MPACT)

Cygwin A free software that provides a Linux-like environment and software tool set for Windows A DLL (cygwin 1. dll) which acts as a Linux API emulation layer providing substantial Linux API functionality A vast set of GNU and other free software applications organized into a large number of optional packages

LEON Bare-C Cross Compilation System (BCC) Used for cross-compilation A GNU-based cross-compilation system for LEON 2 and LEON 3 processors GNU C/C++ cross-compiler (3. 2. 3 and 3. 4. 4) GNU Binutils-2. 16. 1 (assembler, linker. . . ) Newlib 1. 13. 0 Embedded C-library Bare-C run-time system with interrupt support and tasking Pthreads library Boot-prom builder GNU debugger (gdb)

GRMON A general debug monitor for the LEON processor, and for SOC designs based on the GRLIB IP library Read/write access to all system registers and memory Built-in disassembler and trace buffer management Downloading and execution of LEON applications Breakpoint and watchpoint management Remote connection to GNU debugger (gdb) Support for USB, JTAG, RS 232, PCI, Ethernet and Space. Wire debug links

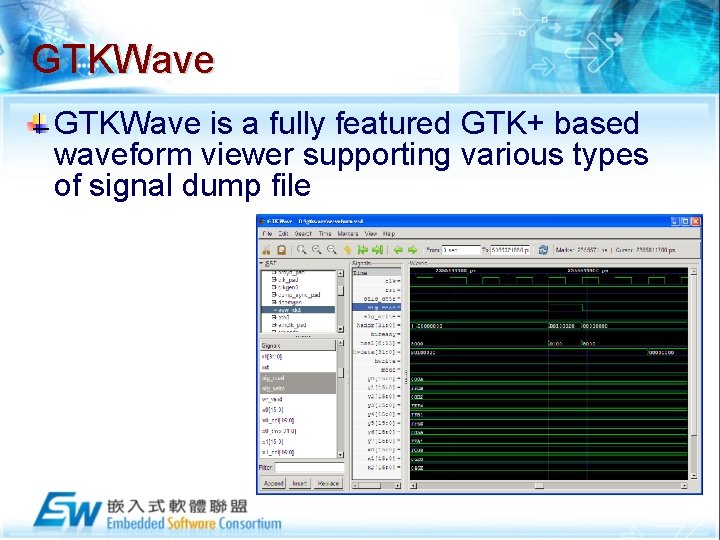

GHDL is a complete VHDL simulator, using the GCC technology GHDL does not do synthesis: it cannot translate your design into a netlist GHDL compiles VHDL files and creates a binary, which simulates (or executes) your design and creates a VCD file that may be visually inspected with a waveform viewer

GTKWave is a fully featured GTK+ based waveform viewer supporting various types of signal dump file

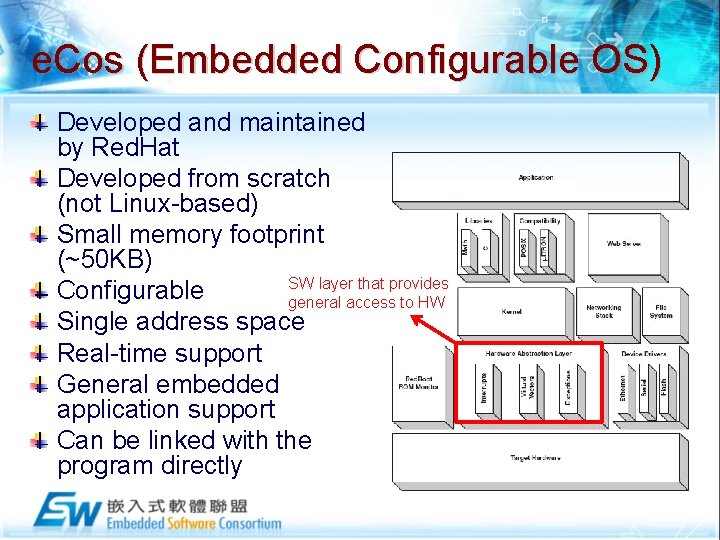

e. Cos (Embedded Configurable OS) Developed and maintained by Red. Hat Developed from scratch (not Linux-based) Small memory footprint (~50 KB) SW layer that provides Configurable general access to HW Single address space Real-time support General embedded application support Can be linked with the program directly

- Slides: 27