HW SW HardwareSoftware Codesign TrongYen Lee Graduate Institute

- Slides: 33

HW SW Hardware-Software Codesign 軟硬體共同設計 Trong-Yen Lee 李宗演 Graduate Institute of Computer, Communication, and Control National Taipei University of Technology Taipei 106, Taiwan, R. O. C. 1

HW Course Grading SW l Assignments and Paper Reading: 30% l Mid-Term Test: 35% l Final Exam: 35% 2

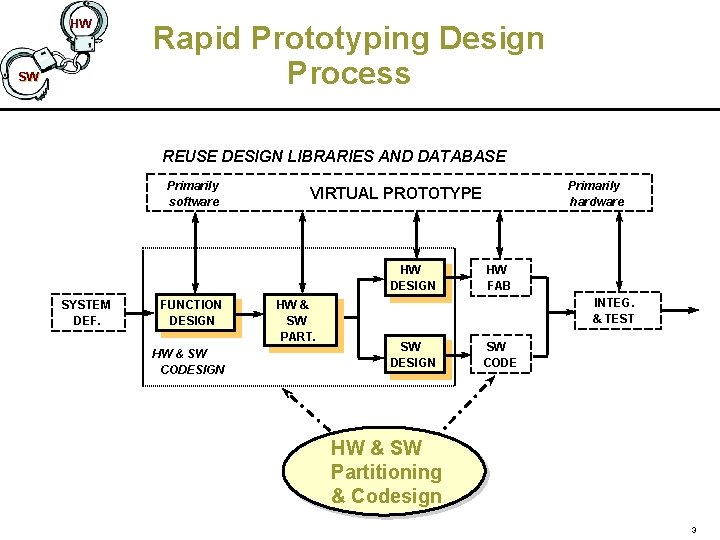

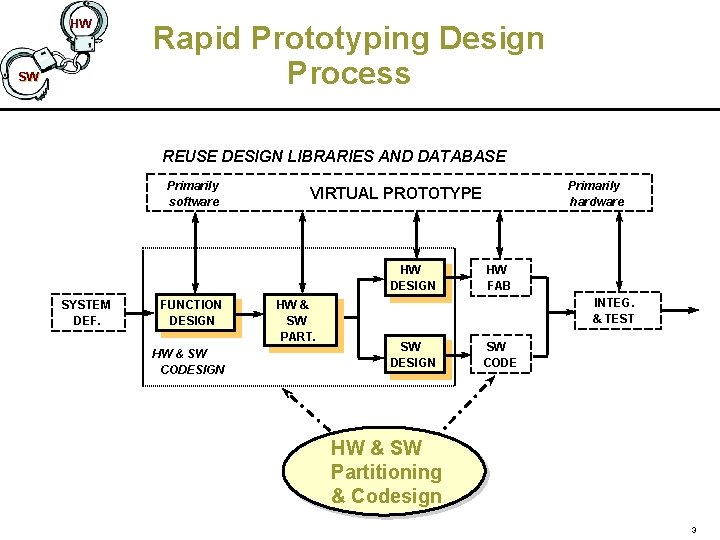

HW SW Rapid Prototyping Design Process REUSE DESIGN LIBRARIES AND DATABASE Primarily software HW DESIGN SYSTEM DEF. FUNCTION DESIGN HW & SW CODESIGN Primarily hardware VIRTUAL PROTOTYPE HW & SW PART. HW FAB INTEG. & TEST SW DESIGN SW CODE HW & SW Partitioning & Codesign 3

HW SW Hardware-Software Codesign Man-Woman Marriage ? 4

HW Course Goals SW l Introduce the fundamentals of HW/SW codesign and partitioning concepts in designing embedded systems m Discuss the current trends in the codesign of embedded systems m Provide information on the goals of and methodology for partitioning hardware/software in systems l Show benefits of the codesign approach over current design process m Provide information on how to incorporate these techniques into a general digital design methodology for embedded systems l Illustrate how codesign concepts are being introduced into design methodologies m Several example codesign systems are discussed 5

HW Course Outline SW l Introduction to Embedded Systems and Hardware-Software Codesign Models and Architectures for System Specification Languages for System Design A Specification Example: Telephone Answering Machine Translation to VHDL System Partitioning l Design Quality Estimation l Specification Refinement l System-Design Methodology l Codesign Examples l l l 6

HW Outline SW l l l l l Introduction to Hardware-Software Codesign System Modeling, Architectures, Languages Partitioning Methods Design Quality Estimation Specification Refinement Co-synthesis Techniques Function-Architecture Codesign Paradigm Coverification Methodology & Tools Codesign Case Studies m m ATM Virtual Private Network Digital Camera and JPEG 7

HW SW Introduction to Embedded Systems and Hardware-Software Codesign l Introduction l Unified HW/SW Representations l HW/SW Partitioning Techniques l Integrated HW/SW Modeling Methodologies l HW and SW Synthesis Methodologies l Industry Approaches to HW/SW Codesign l Hardware/Software Codesign Research l Summary 8

HW Codesign Definition and Key Concepts SW l Codesign m The meeting of system-level objectives by exploiting the trade-offs between hardware and software in a system through their concurrent design l Key concepts m Concurrent: hardware and software developed at the same time on parallel paths m Integrated: interaction between hardware and software developments to produce designs that meet performance criteria and functional specifications 9

HW Motivations for Codesign SW l Factors driving codesign (hardware/software systems): m Instruction Set Processors (ISPs) available as cores in many design kits (386 s, DSPs, microcontrollers, etc. ) m Systems on Silicon - many transistors available in typical processes (> 10 million transistors available in IBM ASIC process, etc. ) m Increasing capacity of field programmable devices some devices even able to be reprogrammed on-the-fly (FPGAs, CPLDs, etc. ) m Efficient C compilers for embedded processors m Hardware synthesis capabilities 10

HW SW l Motivations for Codesign (cont. ) The importance of codesign in designing hardware/software systems: m Improves design quality, design cycle time, and cost q Reduces integration and test time m Supports growing complexity of embedded systems m Takes advantage of advances in tools and technologies q Processor cores q High-level hardware synthesis capabilities q ASIC development 11

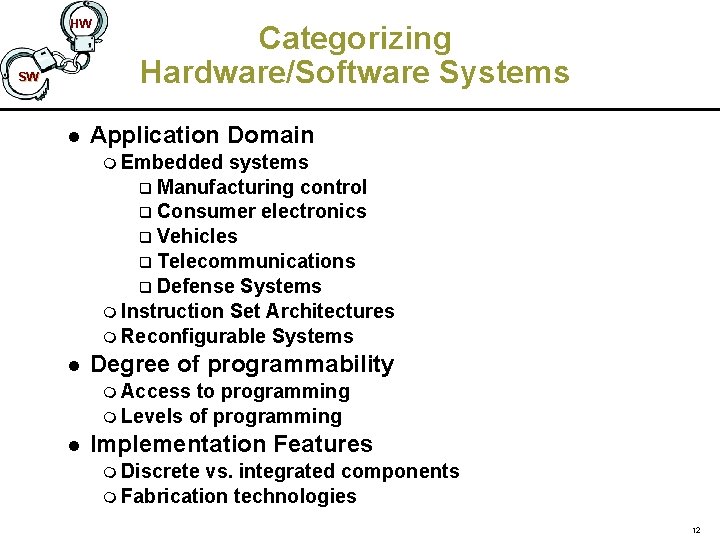

HW SW l Categorizing Hardware/Software Systems Application Domain m Embedded systems q Manufacturing control q Consumer electronics q Vehicles q Telecommunications q Defense Systems m Instruction Set Architectures m Reconfigurable Systems l Degree of programmability m Access to programming m Levels of programming l Implementation Features m Discrete vs. integrated components m Fabrication technologies 12

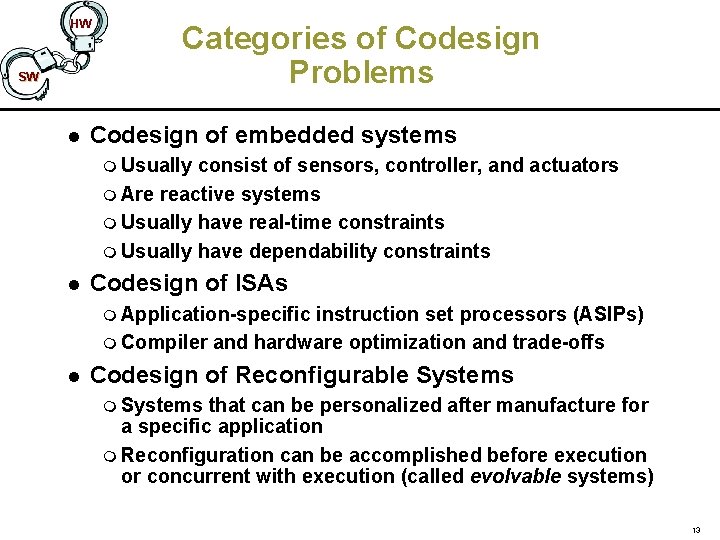

HW SW l Categories of Codesign Problems Codesign of embedded systems m Usually consist of sensors, controller, and actuators m Are reactive systems m Usually have real-time constraints m Usually have dependability constraints l Codesign of ISAs m Application-specific instruction set processors (ASIPs) m Compiler and hardware optimization and trade-offs l Codesign of Reconfigurable Systems m Systems that can be personalized after manufacture for a specific application m Reconfiguration can be accomplished before execution or concurrent with execution (called evolvable systems) 13

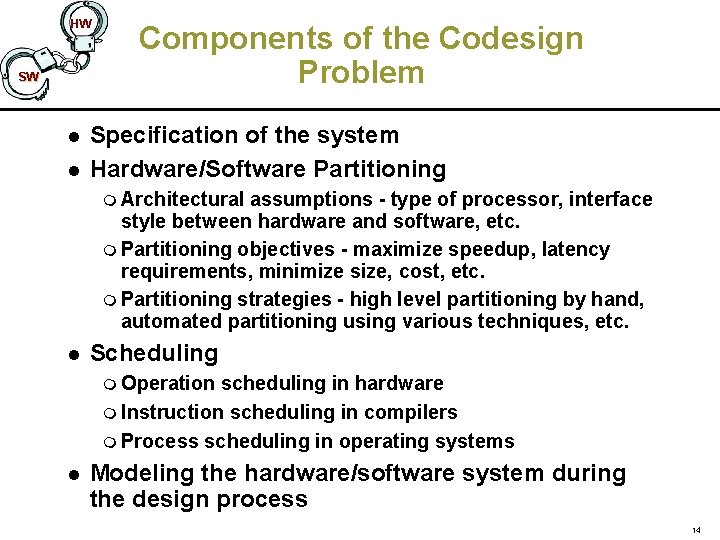

HW SW l l Components of the Codesign Problem Specification of the system Hardware/Software Partitioning m Architectural assumptions - type of processor, interface style between hardware and software, etc. m Partitioning objectives - maximize speedup, latency requirements, minimize size, cost, etc. m Partitioning strategies - high level partitioning by hand, automated partitioning using various techniques, etc. l Scheduling m Operation scheduling in hardware m Instruction scheduling in compilers m Process scheduling in operating systems l Modeling the hardware/software system during the design process 14

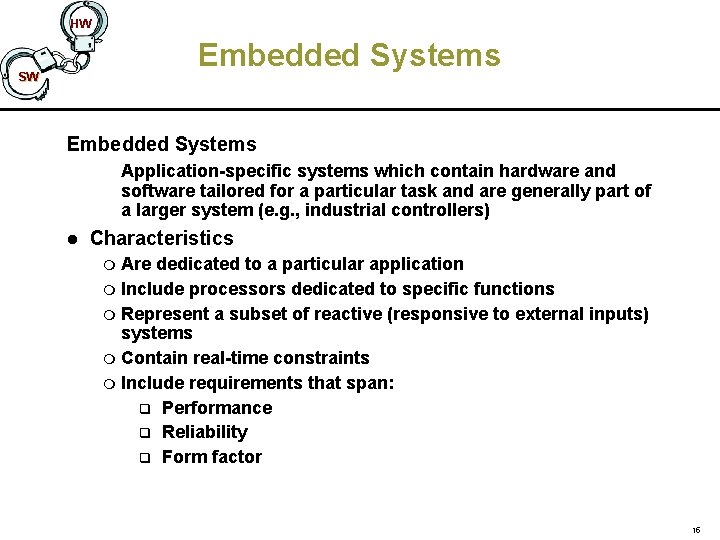

HW Embedded Systems SW Embedded Systems Application-specific systems which contain hardware and software tailored for a particular task and are generally part of a larger system (e. g. , industrial controllers) l Characteristics Are dedicated to a particular application m Include processors dedicated to specific functions m Represent a subset of reactive (responsive to external inputs) systems m Contain real-time constraints m Include requirements that span: q Performance q Reliability q Form factor m 15

HW Embedded Systems: Specific Trends SW l Use of microprocessors only one or two generations behind state-of-the-art for desktops m E. g. N/2 bit width where N is the bit width of current desktop systems l l l Contain limited amount of memory Must satisfy strict real-time and/or performance constraints Must optimize additional design objectives: m m m l Cost Reliability Design time Increased use of hardware/software codesign principles to meet constraints 16

HW SW Embedded Systems: Examples l Banking and transaction processing applications l Automobile engine control units l Signal processing applications l Home appliances (microwave ovens) l Industrial controllers in factories l Cellular communications 17

HW SW l l l Embedded Systems: Complexity Issues Complexity of embedded systems is continually increasing Number of states in these systems (especially in the software) is very large Description of a system can be complex, making system analysis extremely hard Complexity management techniques are necessary to model and analyze these systems Systems becoming too complex to achieve accurate “first pass” design using conventional techniques New issues rapidly emerging from new implementation technologies 18

HW SW l Techniques to Support Complexity Management Delayed HW/SW partitioning m Postpone as many decisions as possible that place constraints on the design l l Abstractions and decomposition techniques Incremental development m “Growing” software m Requiring top-down design l l Description languages Simulation Standards Design methodology management framework 19

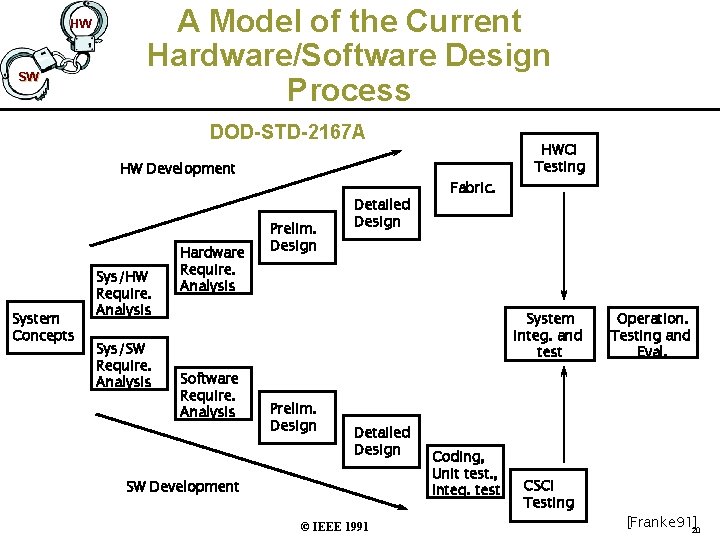

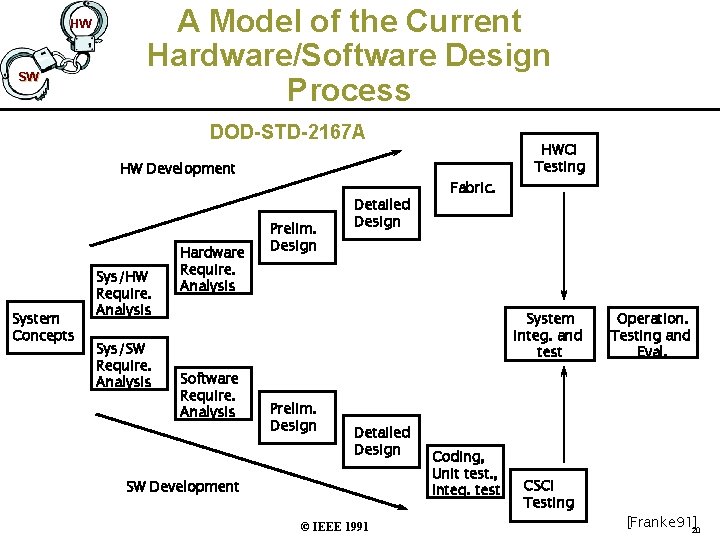

HW SW A Model of the Current Hardware/Software Design Process DOD-STD-2167 A HW Development System Concepts Sys/HW Require. Analysis Sys/SW Require. Analysis Hardware Require. Analysis Prelim. Design Detailed Design HWCI Testing Fabric. System Integ. and test Software Require. Analysis Prelim. Design Detailed Design SW Development © IEEE 1991 Coding, Unit test. , Integ. test CSCI Testing Operation. Testing and Eval. [Franke 91]20

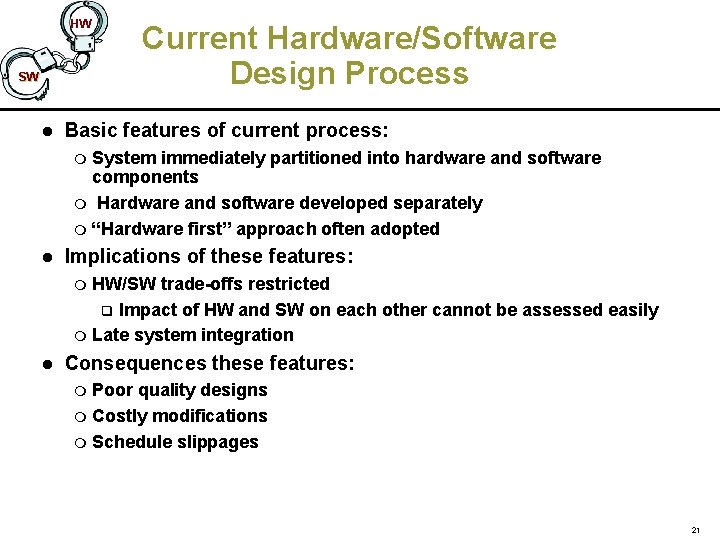

HW SW l Current Hardware/Software Design Process Basic features of current process: System immediately partitioned into hardware and software components m Hardware and software developed separately m “Hardware first” approach often adopted m l Implications of these features: HW/SW trade-offs restricted q Impact of HW and SW on each other cannot be assessed easily m Late system integration m l Consequences these features: Poor quality designs m Costly modifications m Schedule slippages m 21

HW SW Incorrect Assumptions in Current Hardware/Software Design Process l Hardware and software can be acquired separately and independently, with successful and easy integration of the two later l Hardware problems can be fixed with simple software modifications l Once operational, software rarely needs modification or maintenance l Valid and complete software requirements are easy to state and implement in code 22

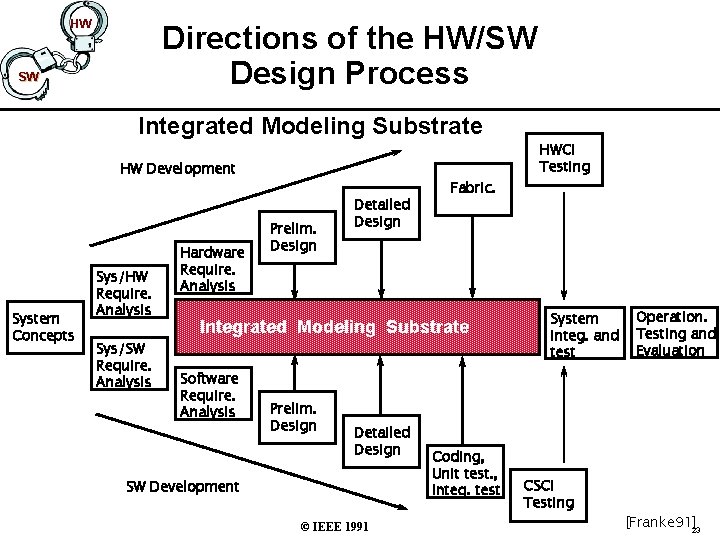

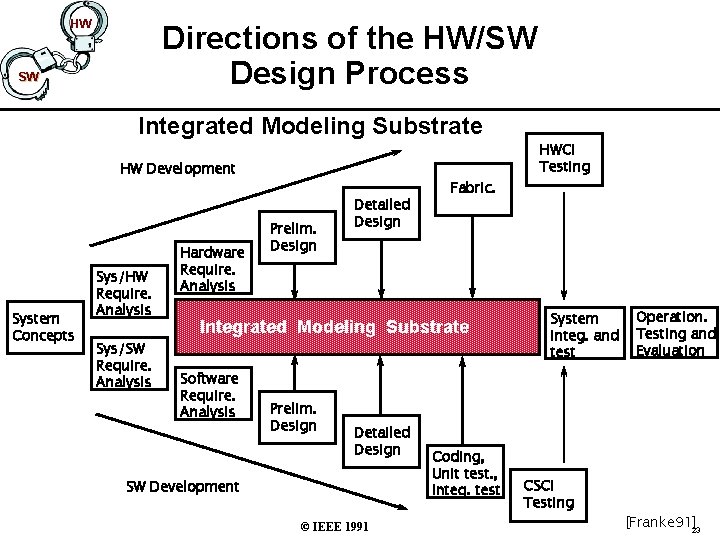

HW Directions of the HW/SW Design Process SW Integrated Modeling Substrate HWCI Testing HW Development System Concepts Sys/HW Require. Analysis Sys/SW Require. Analysis Hardware Require. Analysis Prelim. Design Detailed Design Fabric. Integrated Modeling Substrate Software Require. Analysis Prelim. Design Detailed Design SW Development © IEEE 1991 Coding, Unit test. , Integ. test System Integ. and test CSCI Testing Operation. Testing and Evaluation [Franke 91]23

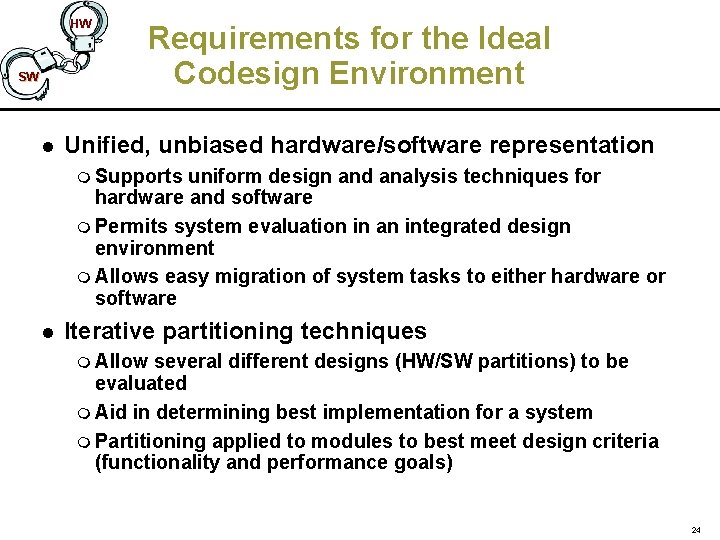

HW SW l Requirements for the Ideal Codesign Environment Unified, unbiased hardware/software representation m Supports uniform design and analysis techniques for hardware and software m Permits system evaluation in an integrated design environment m Allows easy migration of system tasks to either hardware or software l Iterative partitioning techniques m Allow several different designs (HW/SW partitions) to be evaluated m Aid in determining best implementation for a system m Partitioning applied to modules to best meet design criteria (functionality and performance goals) 24

HW SW l Requirements for the Ideal Codesign Environment (cont. ) Integrated modeling substrate m Supports evaluation at several stages of the design process m Supports step-wise development and integration of hardware and software l Validation Methodology m Insures that system implemented meets initial system requirements 25

HW SW l Cross-fertilization Between Hardware and Software Design Fast growth in both VLSI design and software engineering has raised awareness of similarities between the two m Hardware synthesis m Programmable logic m Description languages l Explicit attempts have been made to “transfer technology” between the domains 26

HW SW Cross-fertilization Between Hardware and Software Design (cont. ) VLSI DESIGN l SOFTWARE ENGINEERING EDA tool technology has been transferred to SW CAD systems m Designer support (not automation) m Graphics-driven m Central m Tools design database for design information to check design behavior early in process 27

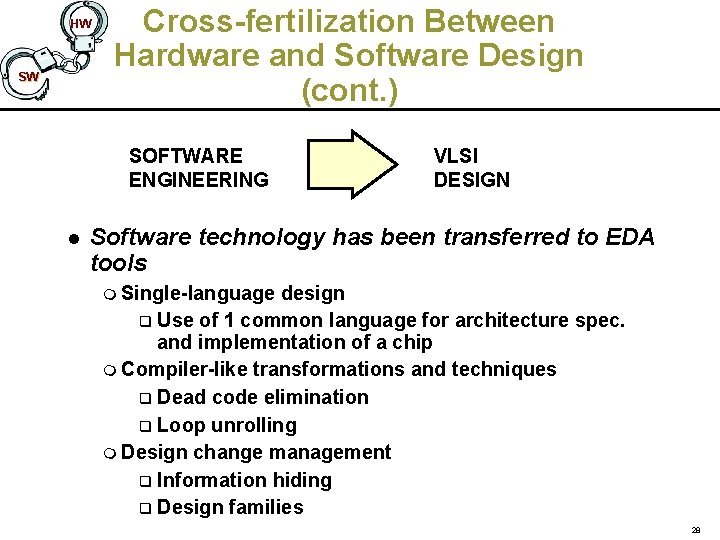

HW SW Cross-fertilization Between Hardware and Software Design (cont. ) SOFTWARE ENGINEERING l VLSI DESIGN Software technology has been transferred to EDA tools m Single-language design q Use of 1 common language for architecture spec. and implementation of a chip m Compiler-like transformations and techniques q Dead code elimination q Loop unrolling m Design change management q Information hiding q Design families 28

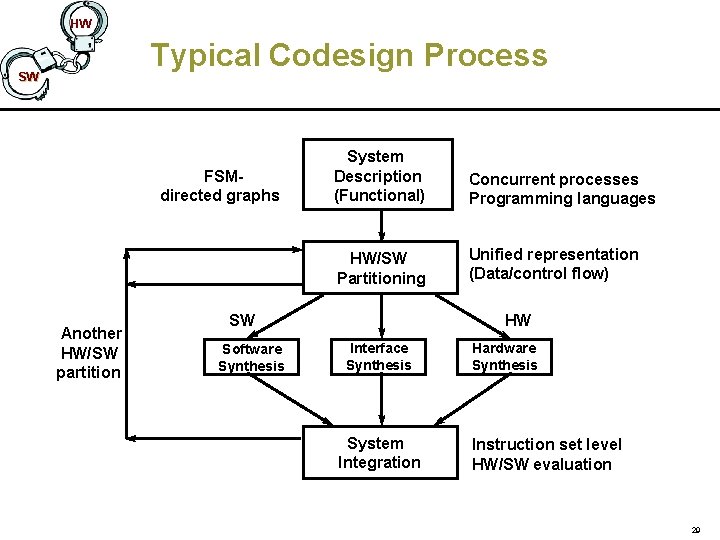

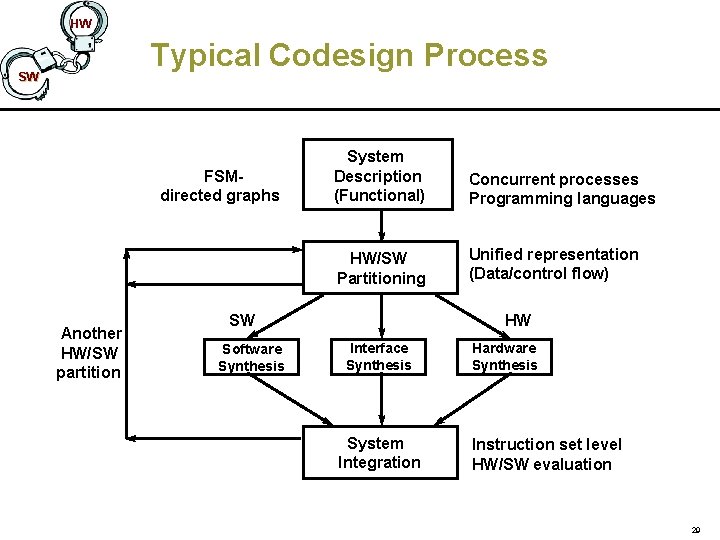

HW Typical Codesign Process SW FSMdirected graphs Another HW/SW partition System Description (Functional) Concurrent processes Programming languages HW/SW Partitioning Unified representation (Data/control flow) SW Software Synthesis HW Interface Synthesis System Integration Hardware Synthesis Instruction set level HW/SW evaluation 29

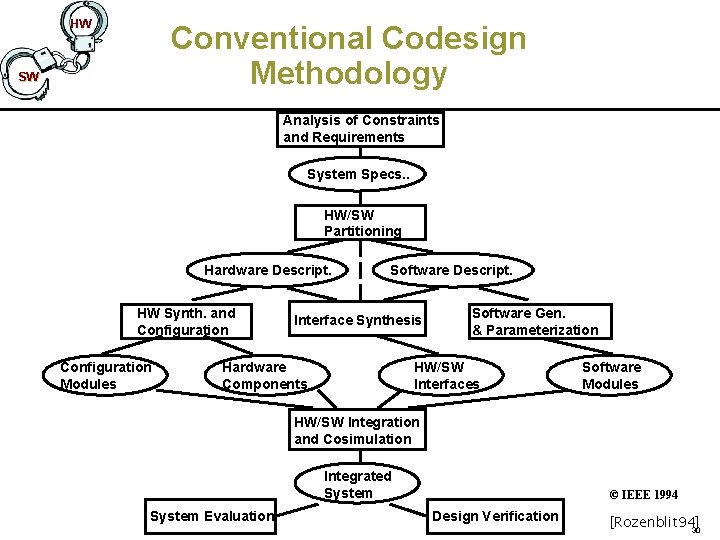

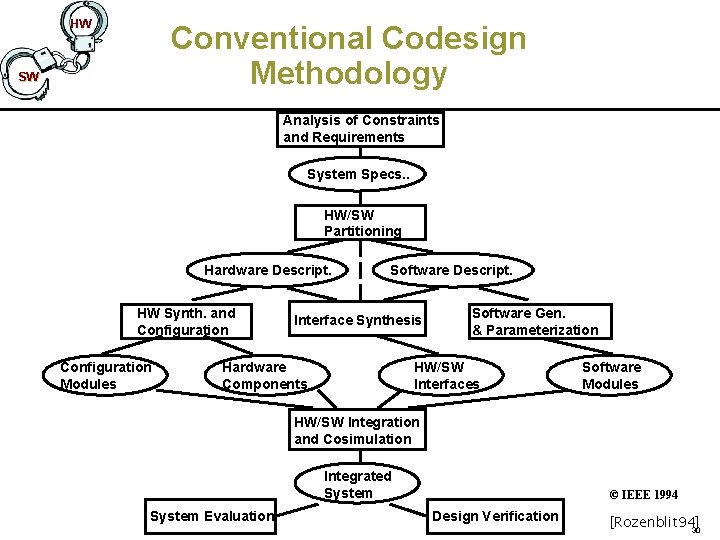

HW Conventional Codesign Methodology SW Analysis of Constraints and Requirements System Specs. . HW/SW Partitioning Hardware Descript. HW Synth. and Configuration Modules Software Descript. Interface Synthesis Hardware Components Software Gen. & Parameterization HW/SW Interfaces Software Modules HW/SW Integration and Cosimulation Integrated System Evaluation © IEEE 1994 Design Verification [Rozenblit 94] 30

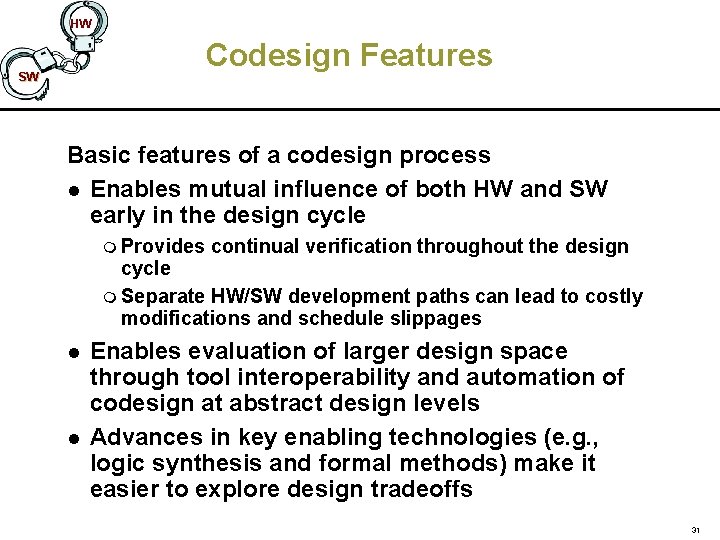

HW Codesign Features SW Basic features of a codesign process l Enables mutual influence of both HW and SW early in the design cycle m Provides continual verification throughout the design cycle m Separate HW/SW development paths can lead to costly modifications and schedule slippages l l Enables evaluation of larger design space through tool interoperability and automation of codesign at abstract design levels Advances in key enabling technologies (e. g. , logic synthesis and formal methods) make it easier to explore design tradeoffs 31

HW State of Codesign Technology SW l Current use limited by: m Lack of a standardized representation m Lack of good validation and evaluation methods l Possible solutions: m Extend existing hardware/software languages to the use of heterogeneous paradigms m Extend formal verification techniques to the HW/SW domain 32

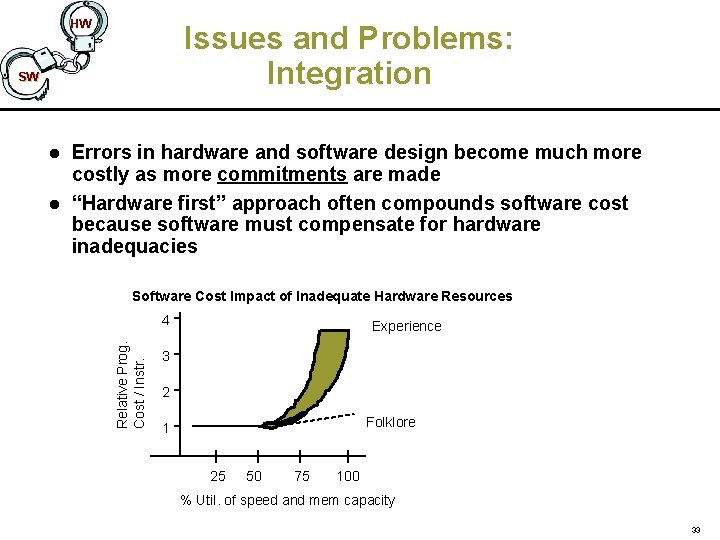

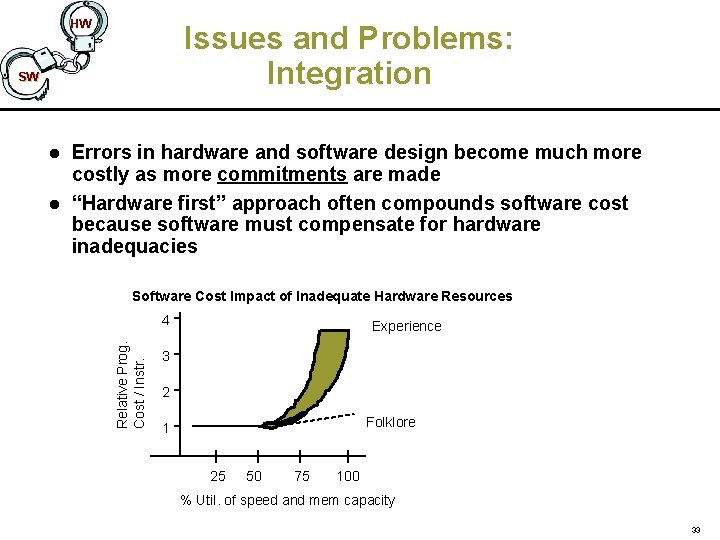

HW Issues and Problems: Integration SW l Errors in hardware and software design become much more costly as more commitments are made “Hardware first” approach often compounds software cost because software must compensate for hardware inadequacies Software Cost Impact of Inadequate Hardware Resources 4 Relative Prog. Cost / Instr. l Experience 3 2 Folklore 1 25 50 75 100 % Util. of speed and mem capacity 33