HVCMOS ACTIVITIES AT IRFU FOR ATLAS UPGRADES UPDATE

- Slides: 3

HVCMOS ACTIVITIES AT IRFU FOR ATLAS UPGRADES (UPDATE) Y. Degerli, F. Balli, F. Guilloux, C. Guyot, F. J. Iguaz, M. Lachkar, J. P. Meyer, A. Ouraou, Ph. Schwemling, M. Vandenbroucke

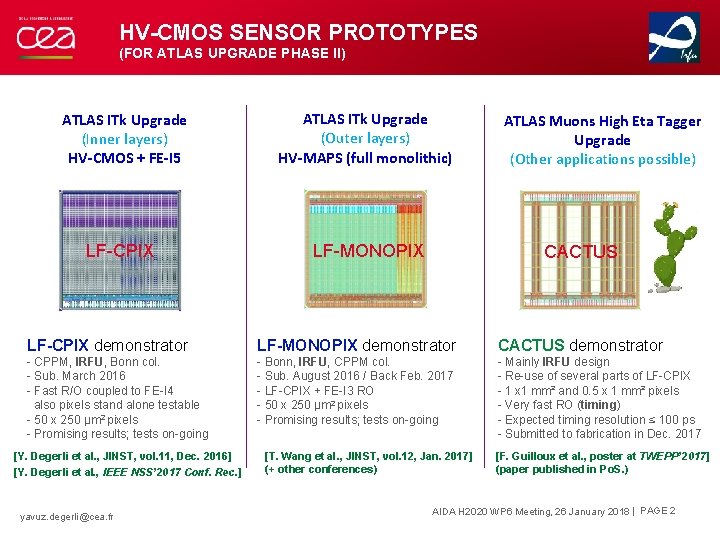

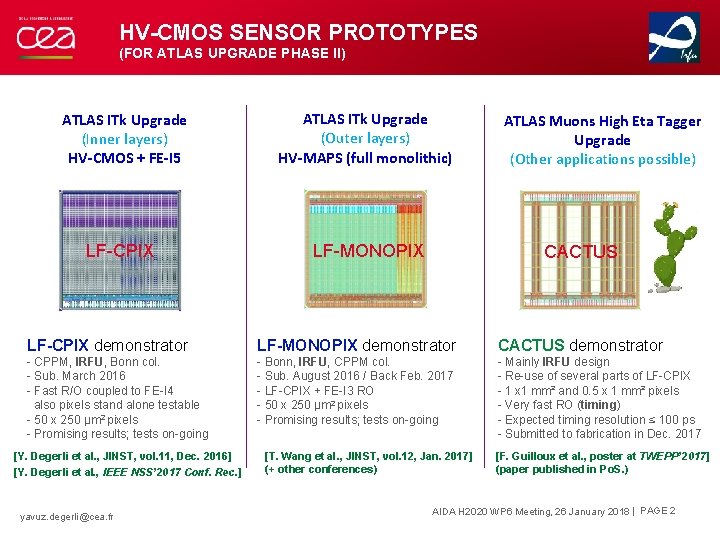

HV-CMOS SENSOR PROTOTYPES (FOR ATLAS UPGRADE PHASE II) ATLAS ITk Upgrade (Inner layers) HV-CMOS + FE-I 5 ATLAS ITk Upgrade (Outer layers) HV-MAPS (full monolithic) LF-CPIX LF-MONOPIX ATLAS Muons High Eta Tagger Upgrade (Other applications possible) CACTUS LF-CPIX demonstrator LF-MONOPIX demonstrator CACTUS demonstrator - CPPM, IRFU, Bonn col. - Sub. March 2016 - Fast R/O coupled to FE-I 4 also pixels stand alone testable - 50 x 250 µm 2 pixels - Promising results; tests on-going - Bonn, IRFU, CPPM col. - Sub. August 2016 / Back Feb. 2017 - LF-CPIX + FE-I 3 RO - 50 x 250 µm 2 pixels - Promising results; tests on-going - Mainly IRFU design - Re-use of several parts of LF-CPIX - 1 x 1 mm² and 0. 5 x 1 mm² pixels - Very fast RO (timing) - Expected timing resolution ≤ 100 ps - Submitted to fabrication in Dec. 2017 [Y. Degerli et al. , JINST, vol. 11, Dec. 2016] [Y. Degerli et al. , IEEE NSS’ 2017 Conf. Rec. ] yavuz. degerli@cea. fr [T. Wang et al. , JINST, vol. 12, Jan. 2017] (+ other conferences) [F. Guilloux et al. , poster at TWEPP’ 2017] (paper published in Po. S. ) AIDA H 2020 WP 6 Meeting, 26 January 2018 | PAGE 2

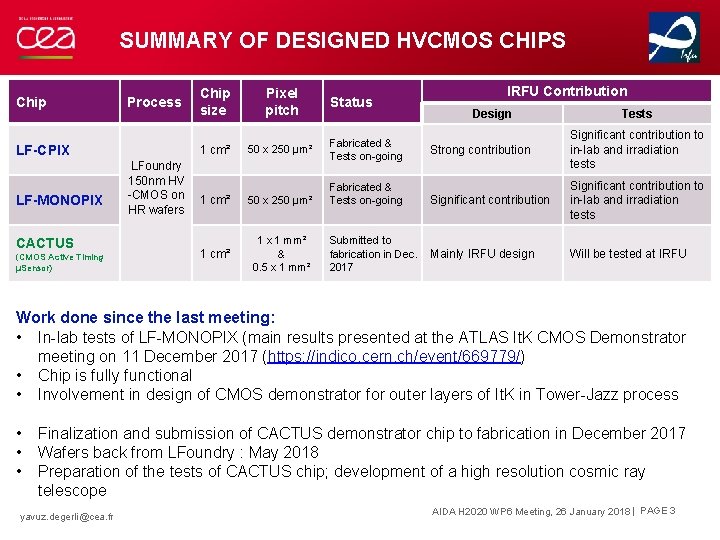

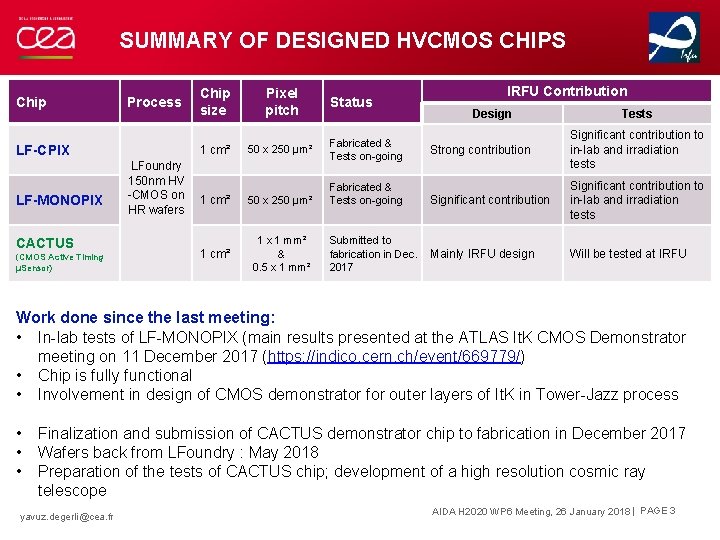

SUMMARY OF DESIGNED HVCMOS CHIPS Chip Process LF-CPIX LF-MONOPIX CACTUS (CMOS Active Timing µSensor) LFoundry 150 nm HV -CMOS on HR wafers Chip size Pixel pitch 1 cm² 50 x 250 µm² 1 cm² 1 x 1 mm² & 0. 5 x 1 mm² Status Fabricated & Tests on-going Submitted to fabrication in Dec. 2017 IRFU Contribution Design Tests Strong contribution Significant contribution to in-lab and irradiation tests Mainly IRFU design Will be tested at IRFU Work done since the last meeting: • In-lab tests of LF-MONOPIX (main results presented at the ATLAS It. K CMOS Demonstrator meeting on 11 December 2017 (https: //indico. cern. ch/event/669779/) • Chip is fully functional • Involvement in design of CMOS demonstrator for outer layers of It. K in Tower-Jazz process • • • Finalization and submission of CACTUS demonstrator chip to fabrication in December 2017 Wafers back from LFoundry : May 2018 Preparation of the tests of CACTUS chip; development of a high resolution cosmic ray telescope yavuz. degerli@cea. fr AIDA H 2020 WP 6 Meeting, 26 January 2018 | PAGE 3