Huffman Encoder Activity Report 2 Advisor Dr Goudarzi

- Slides: 25

Huffman Encoder Activity Report 2 Advisor: Dr. Goudarzi Advanced topics in design hardware January 2006

What is the aim? l l l Implement an embedded system both in hardware and software (Codesign) Tools to be used : EDK as a platform to evolve a complete system in hardware and software simoultaineusly Hardware language: VHDL, Verilog Software language: C Simulation: Modelsim

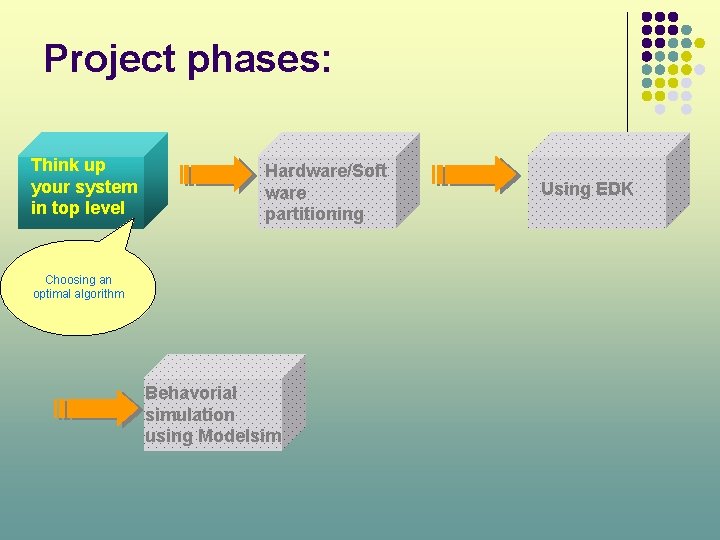

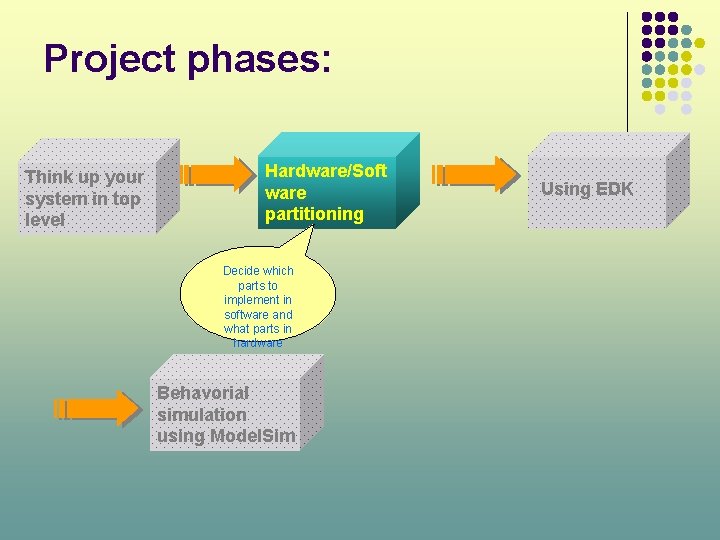

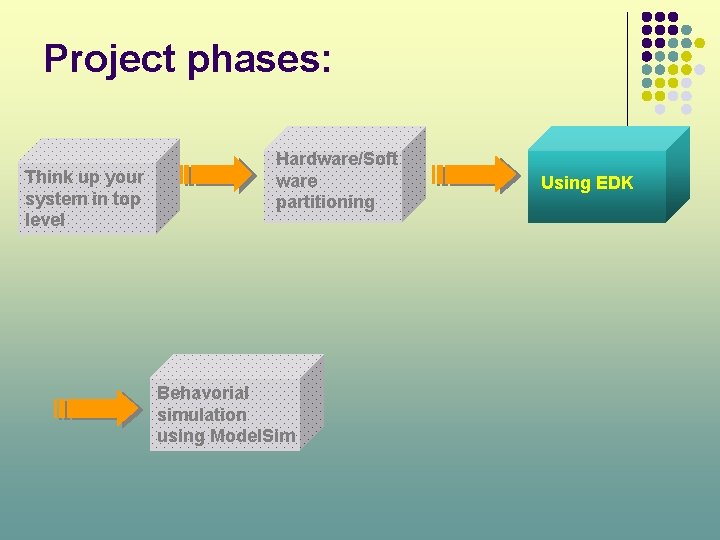

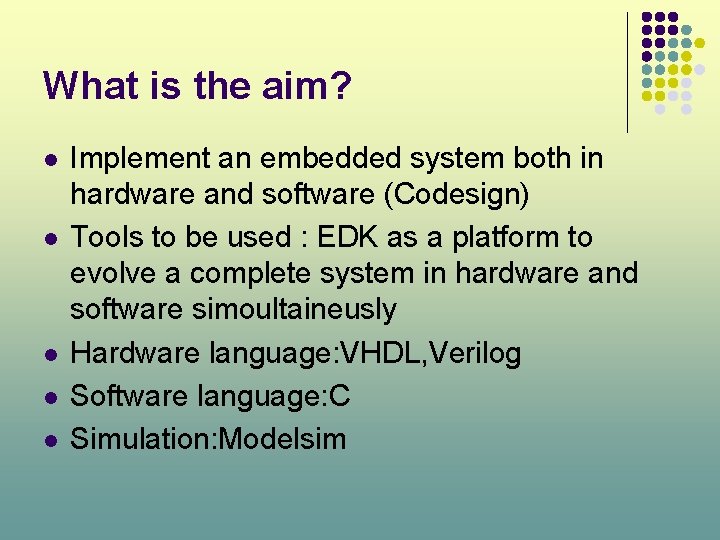

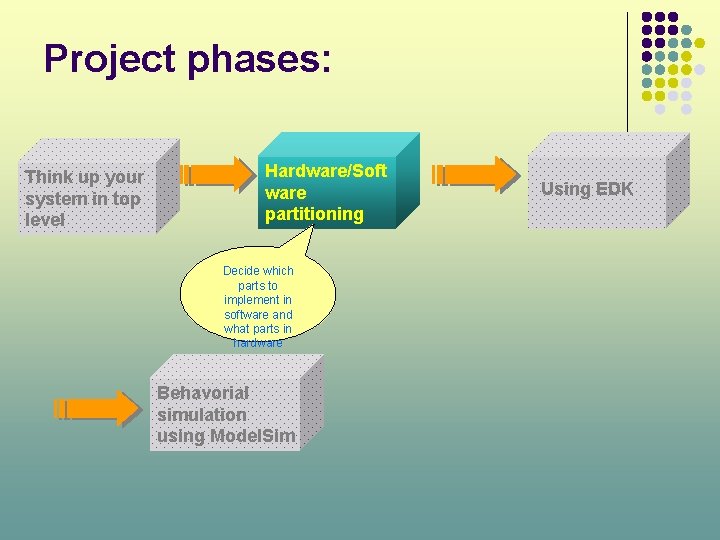

Project phases: Think up your system in top level Hardware/Soft ware partitioning Choosing an optimal algorithm Behavorial simulation using Modelsim Using EDK

Algorithm l l l Almost 15 source codes for Huffman algorithm were investigated but most of them weren’t optimized for hardware implementation Writing the code from scratch was our final decision Using a simple static huffman instead of the dynamic one

Huffman encoding: A Brief Overview Data Compression Classification: • Lossy vs Lossless • Fixed vs Variable Length

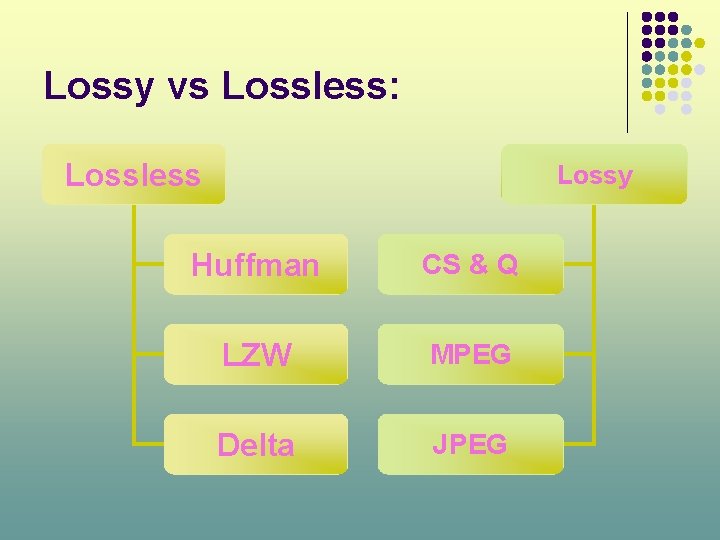

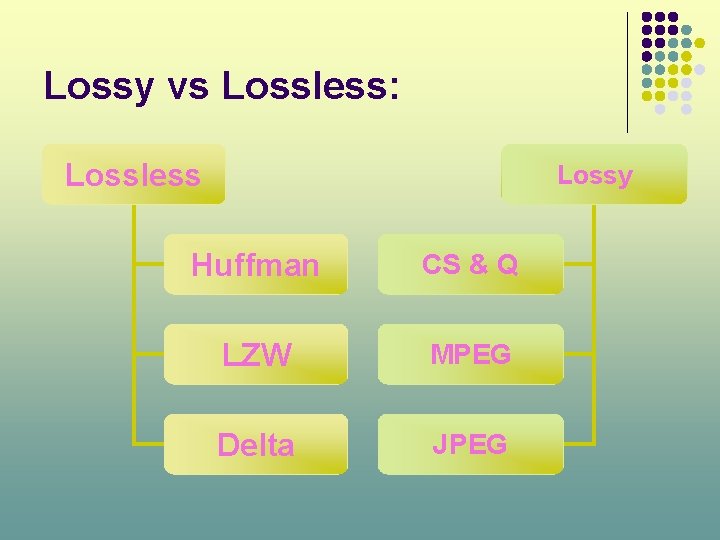

Lossy vs Lossless: Lossless Lossy Huffman CS & Q LZW MPEG Delta JPEG

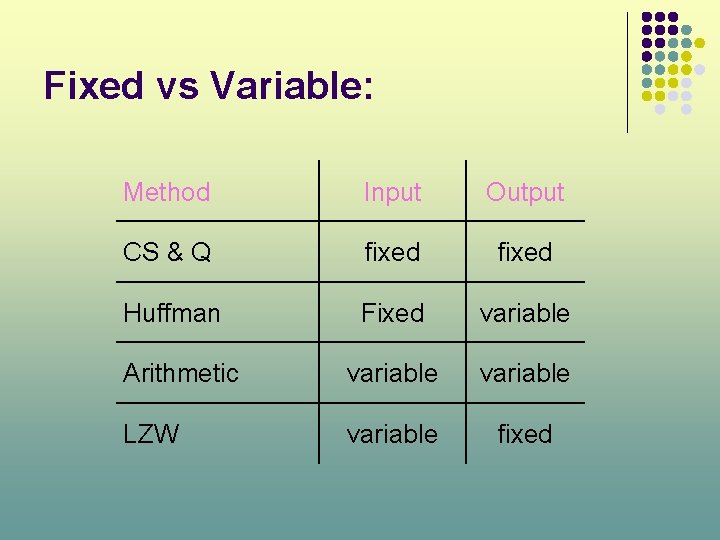

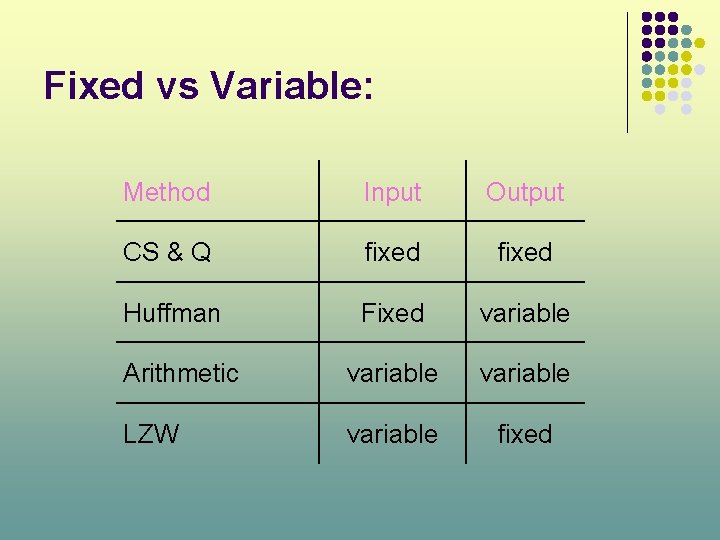

Fixed vs Variable: Method Input Output CS & Q fixed Huffman Fixed variable Arithmetic variable LZW variable fixed

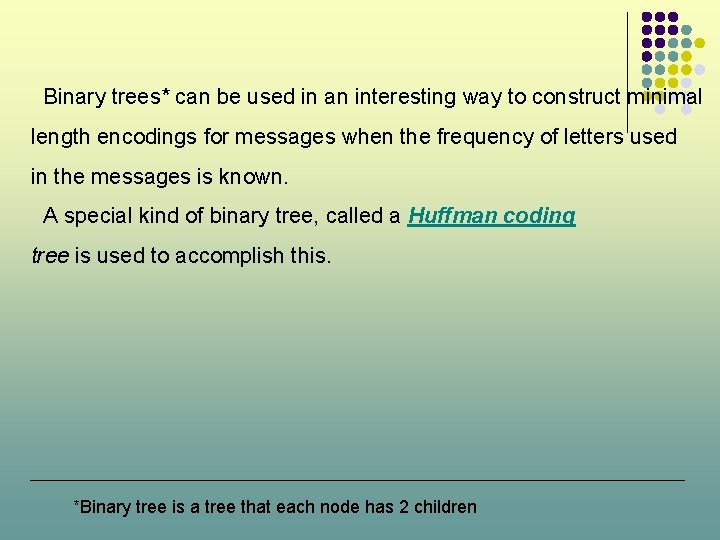

Binary trees* can be used in an interesting way to construct minimal length encodings for messages when the frequency of letters used in the messages is known. A special kind of binary tree, called a Huffman coding tree is used to accomplish this. *Binary tree is a tree that each node has 2 children

To build the Huffman tree : 1. sort the frequencies into increasing order. 2. choose the two smallest values. 3. construct a binary tree with labeled edges. 4. replace the two smallest values with their sum. 5. getting a new sequence 6. again take the two smallest values and construct a labeled binary tree. 7. Go to step 2 until remain no letter. 8. Finish!

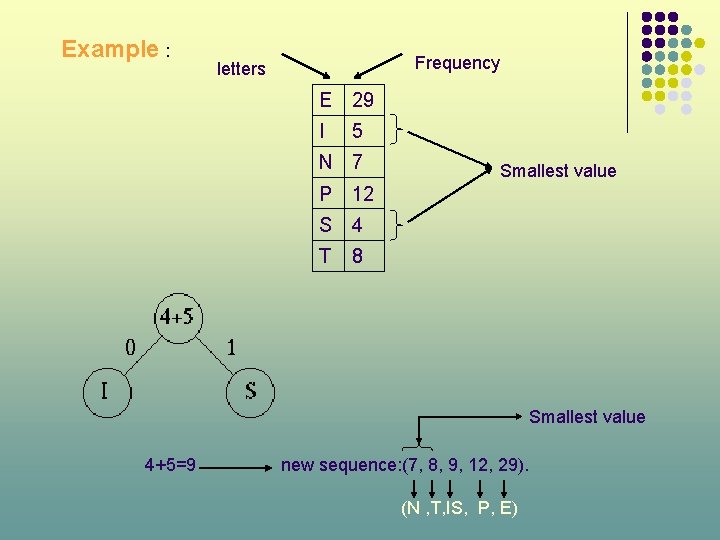

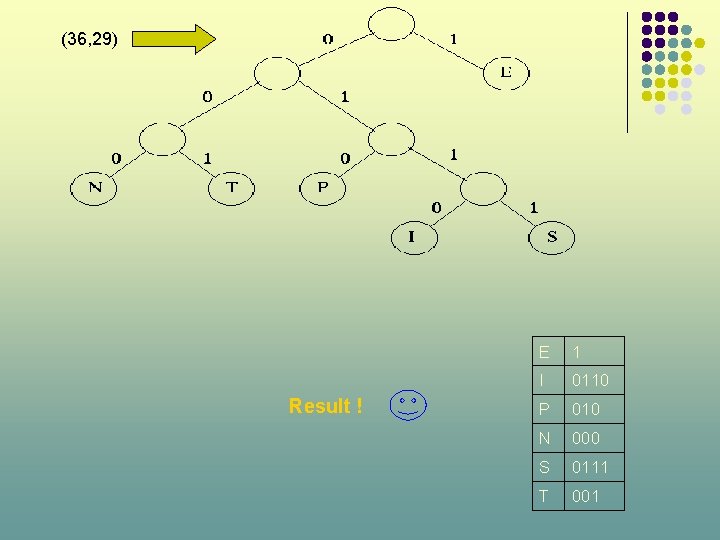

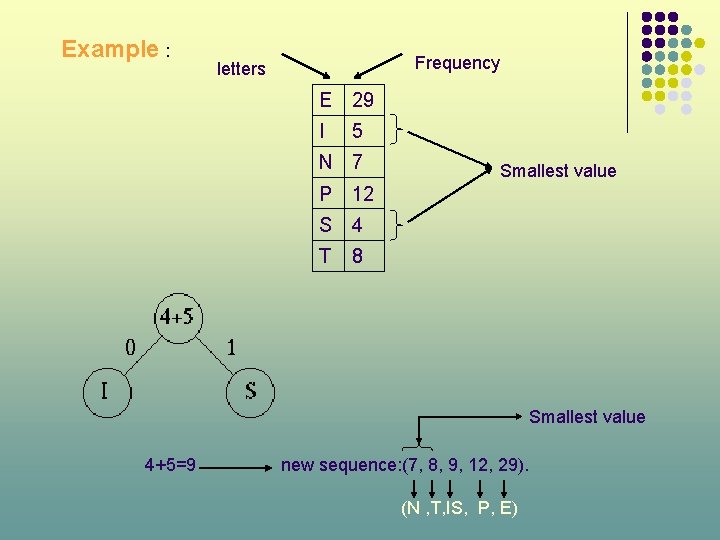

Example : Frequency letters E 29 I 5 N 7 Smallest value P 12 S 4 T 8 Smallest value 4+5=9 new sequence: (7, 8, 9, 12, 29). (N , T, IS, P, E)

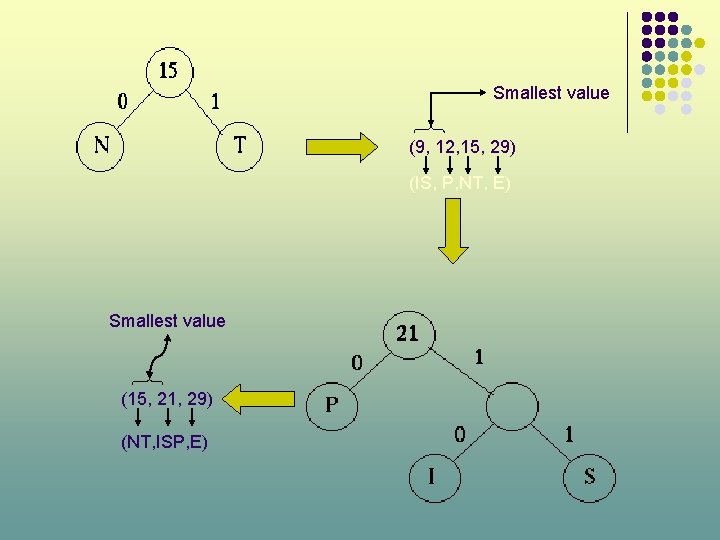

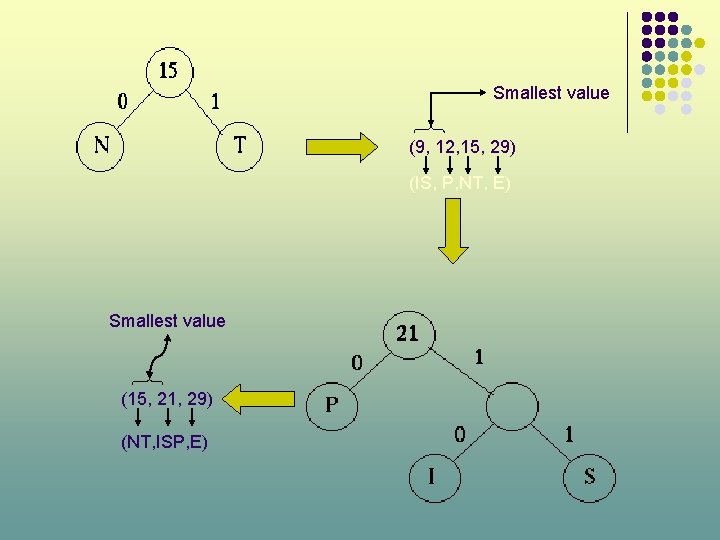

Smallest value (9, 12, 15, 29) (IS, P, NT, E) Smallest value (15, 21, 29) (NT, ISP, E)

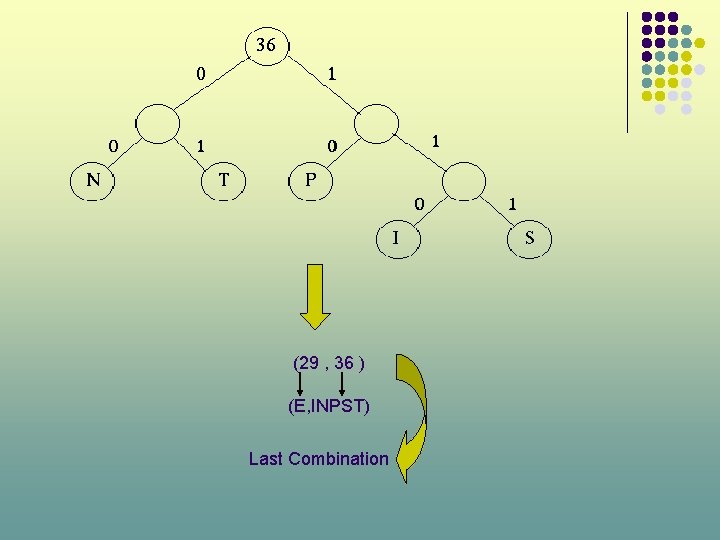

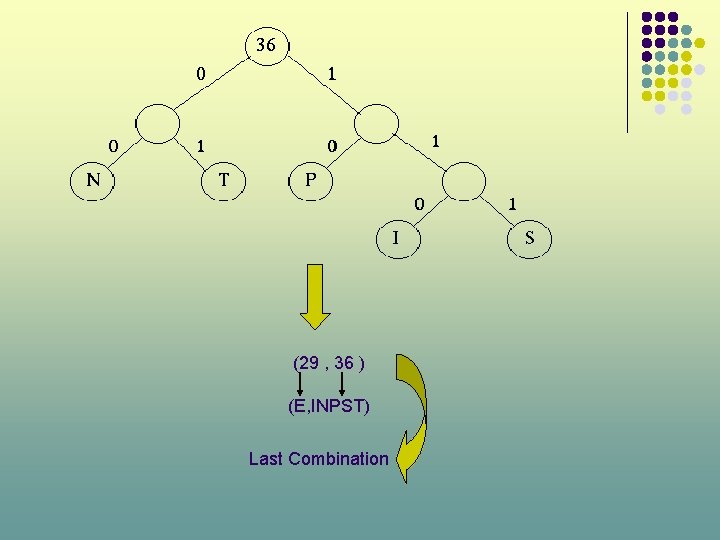

(29 , 36 ) (E, INPST) Last Combination

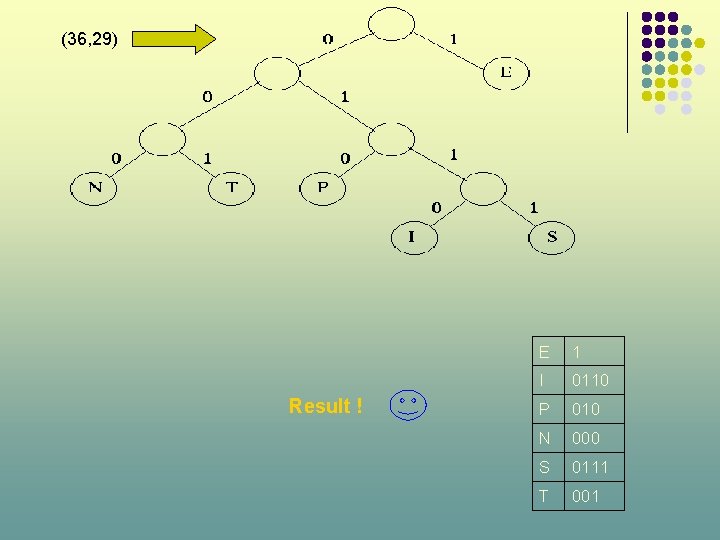

(36, 29) Result ! E 1 I 0110 P 010 N 000 S 0111 T 001

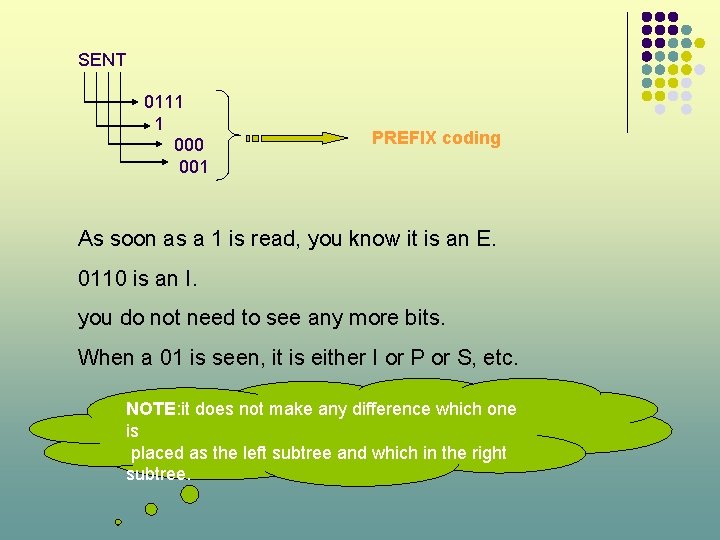

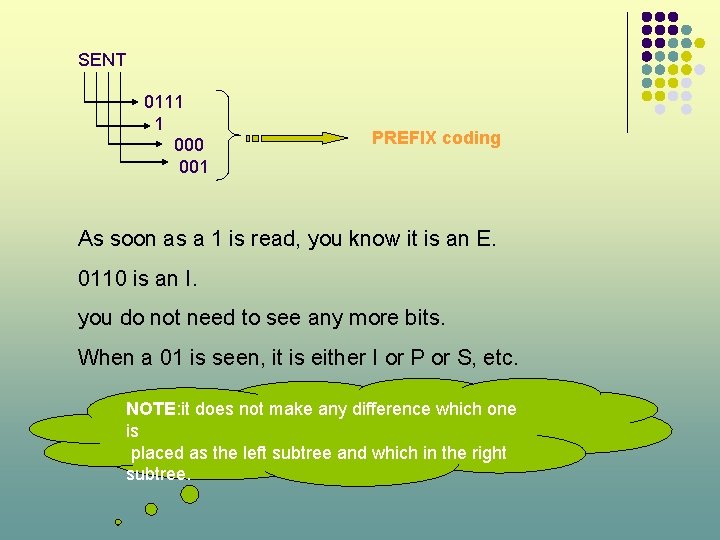

SENT 0111 1 000 001 PREFIX coding As soon as a 1 is read, you know it is an E. 0110 is an I. you do not need to see any more bits. When a 01 is seen, it is either I or P or S, etc. NOTE: it does not make any difference which one is placed as the left subtree and which in the right subtree.

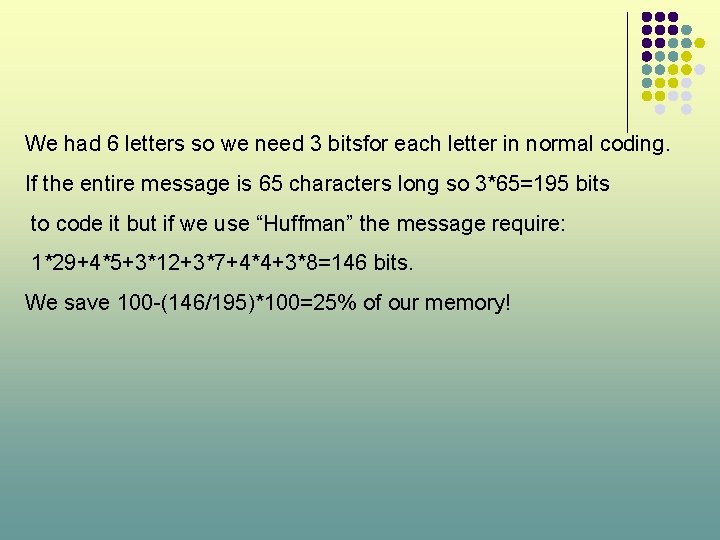

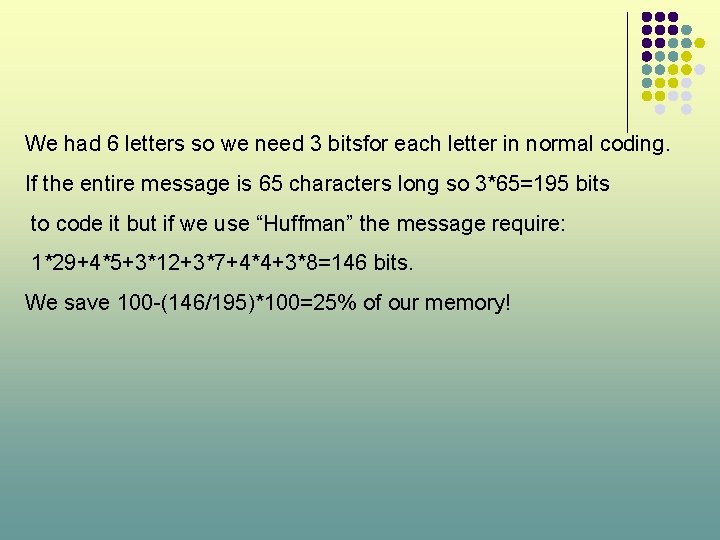

We had 6 letters so we need 3 bitsfor each letter in normal coding. If the entire message is 65 characters long so 3*65=195 bits to code it but if we use “Huffman” the message require: 1*29+4*5+3*12+3*7+4*4+3*8=146 bits. We save 100 -(146/195)*100=25% of our memory!

Project phases: Think up your system in top level Hardware/Soft ware partitioning Decide which parts to implement in software and what parts in hardware Behavorial simulation using Model. Sim Using EDK

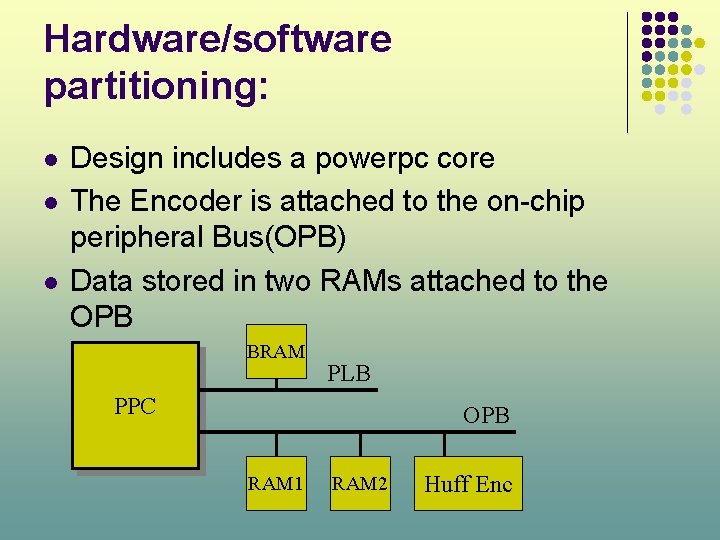

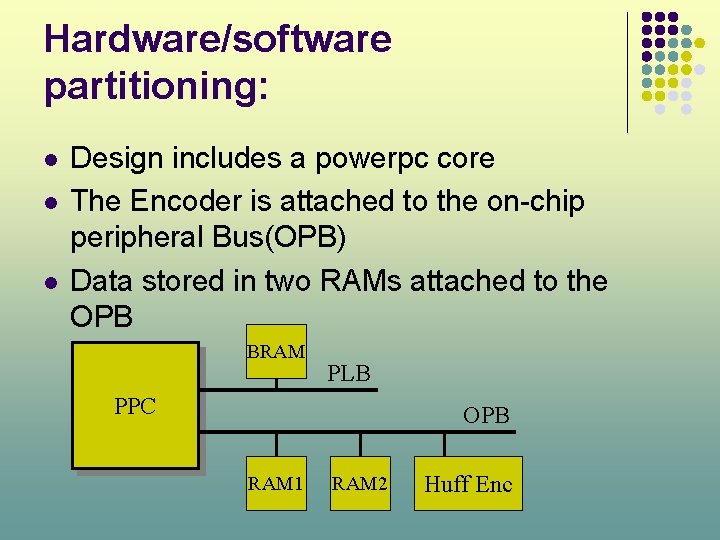

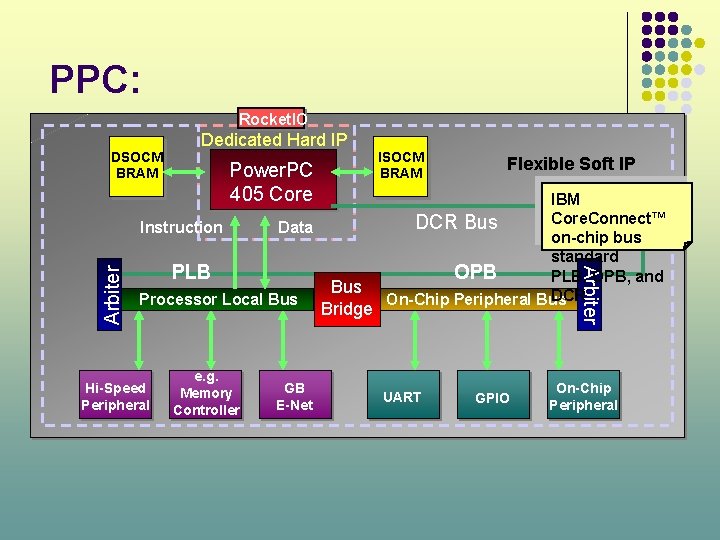

Hardware/software partitioning: l l l Design includes a powerpc core The Encoder is attached to the on-chip peripheral Bus(OPB) Data stored in two RAMs attached to the OPB BRAM PLB PPC OPB RAM 1 RAM 2 Huff Enc

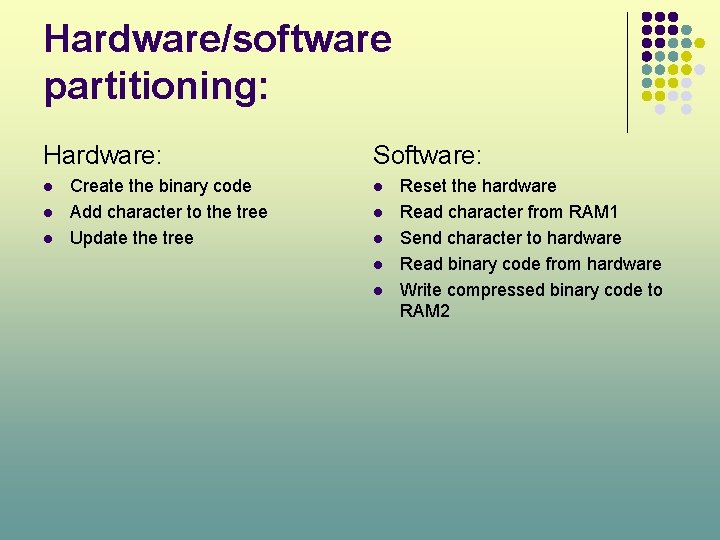

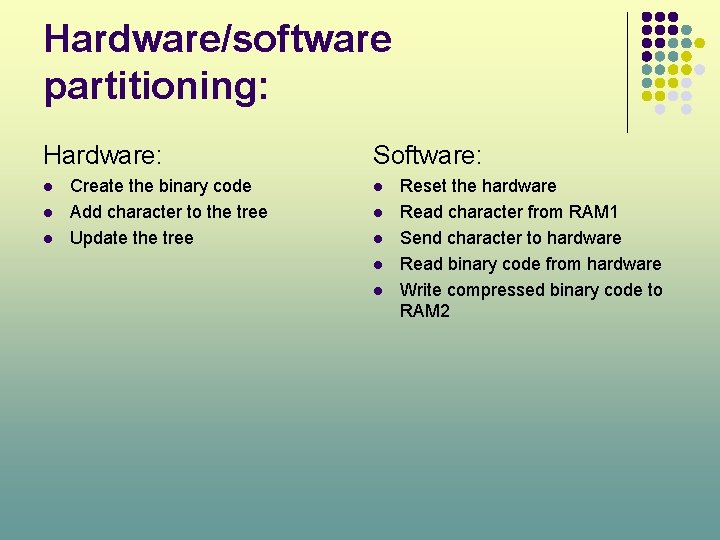

Hardware/software partitioning: Hardware: l l l Create the binary code Add character to the tree Update the tree Software: l l l Reset the hardware Read character from RAM 1 Send character to hardware Read binary code from hardware Write compressed binary code to RAM 2

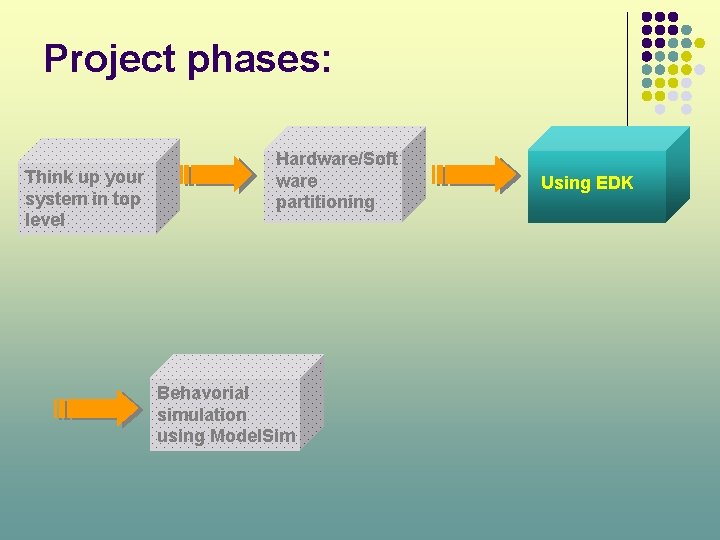

Project phases: Think up your system in top level Hardware/Soft ware partitioning Behavorial simulation using Model. Sim Using EDK

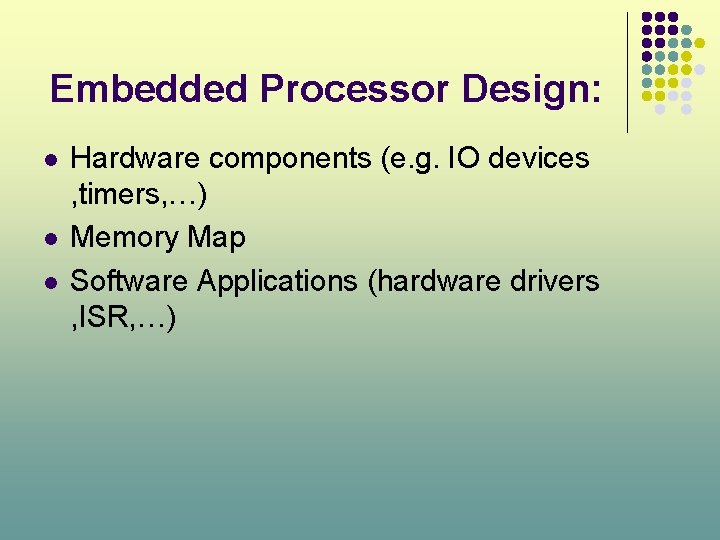

Embedded Processor Design: l l l Hardware components (e. g. IO devices , timers, …) Memory Map Software Applications (hardware drivers , ISR, …)

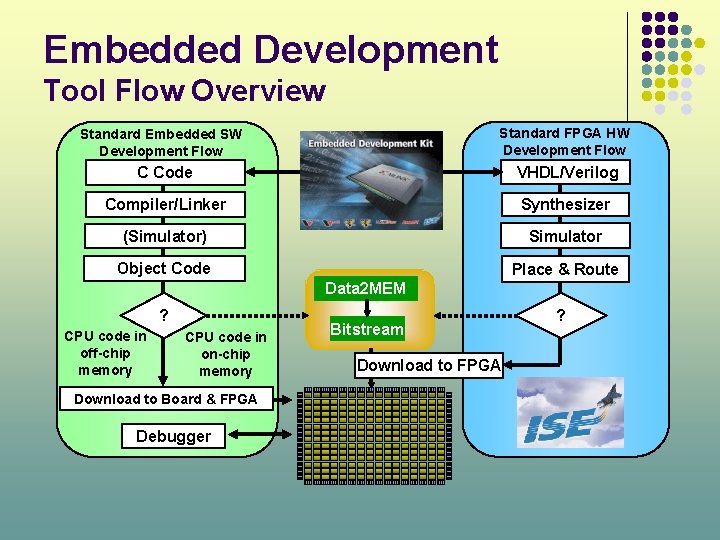

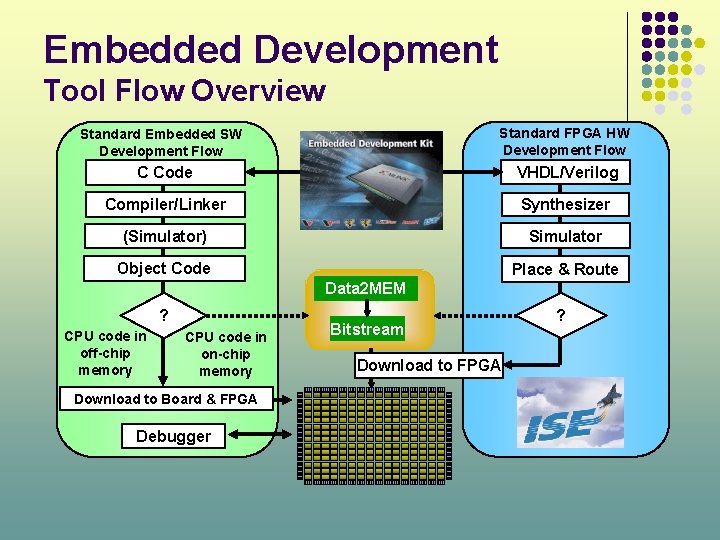

Embedded Development Tool Flow Overview Standard Embedded SW Development Flow Standard FPGA HW Development Flow C Code VHDL/Verilog Compiler/Linker Synthesizer (Simulator) Simulator Object Code Place & Route Data 2 MEM ? CPU code in off-chip memory CPU code in on-chip memory Download to Board & FPGA Debugger Bitstream Download to FPGA ?

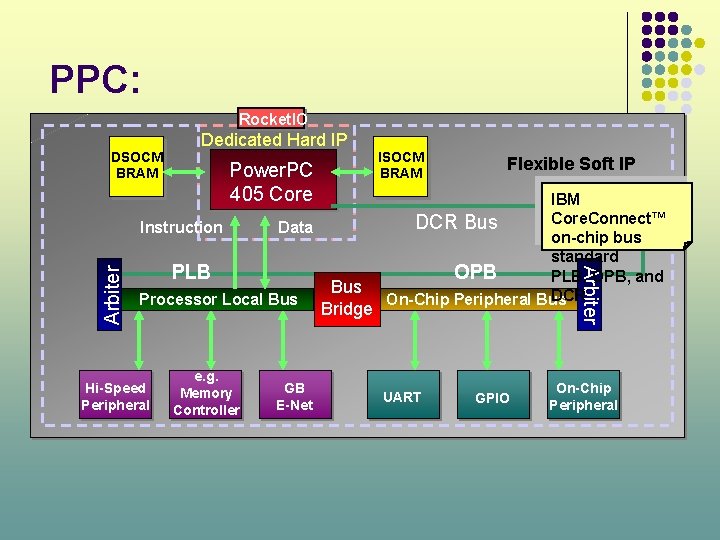

PPC: Rocket. IO DSOCM BRAM Dedicated Hard IP Power. PC 405 Core Data PLB Processor Local Bus Hi-Speed Peripheral e. g. Memory Controller GB E-Net Bus Bridge Flexible Soft IP IBM Core. Connect™ DCR Bus on-chip bus standard OPB PLB, OPB, and DCR On-Chip Peripheral Bus Arbiter Instruction ISOCM BRAM UART GPIO On-Chip Peripheral

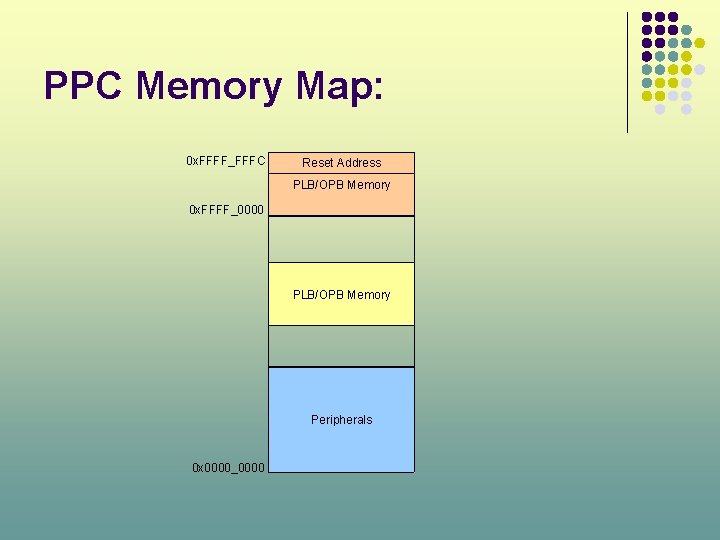

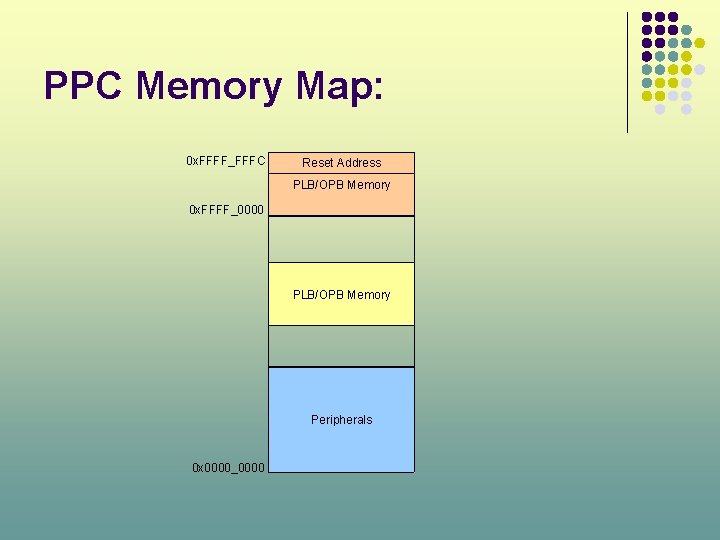

PPC Memory Map: 0 x. FFFF_FFFC Reset Address PLB/OPB Memory 0 x. FFFF_0000 PLB/OPB Memory Peripherals 0 x 0000_0000

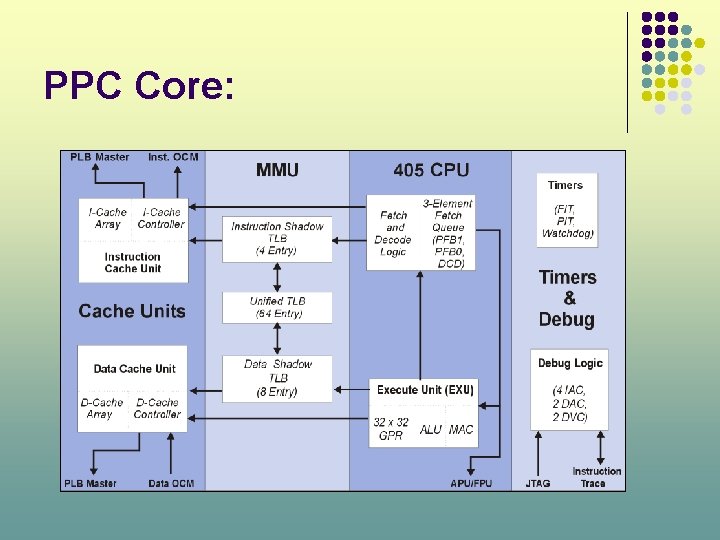

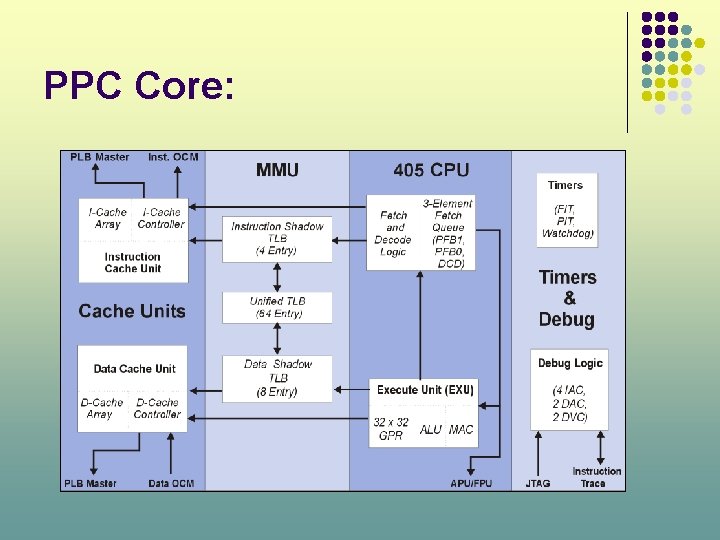

PPC Core:

We are at the beginning The project is underway and going on… Thanks for your attention Maryam. Moghaddas Arezoo. Erfanifard