How to Configure and Generate a Basic HPS

How to Configure and Generate a Basic HPS system for the Altera So. C Dev. Kit WW 4’ 15 Elfarabi Razali – Embedded System Application Engineer Global Support Center, Altera Penang

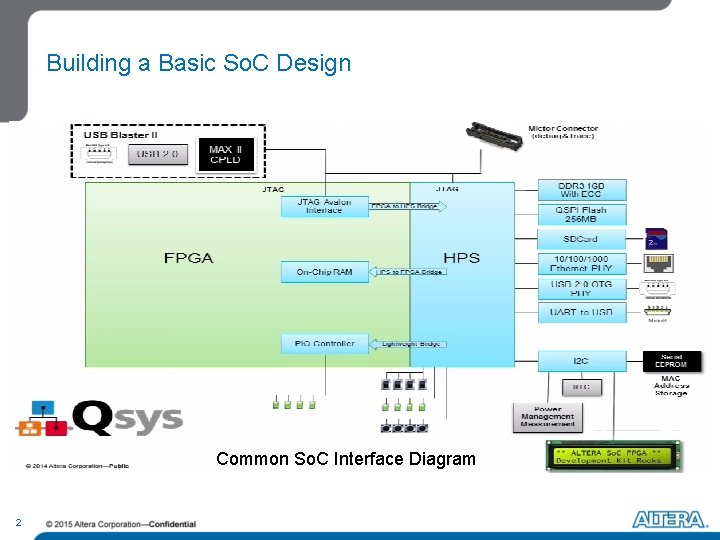

Building a Basic So. C Design Common So. C Interface Diagram 2

Pre-requisites This is the step-by-step guide on how to build a basic So. C design on FPGA, so you may need at least below knowledge/skills: 1. Know how to build design in Quartus II software : YES! 2. Know how to build IP using Qsys : YES! 3. Knowledge in Linux shell command : YES! 3

What is not covered in this training(will cover in future Tech Sharing) 1. 2. 3. 4. 5. ARM Cortex-A 9 v 7 Architecture Software development using ARM DS-5 environment Bare-metal debugging Linux Kernel debugging Linux Application development All these topics will be covered in future Technical Sharing! 4

Agenda Chapter 1 : Instantiating the HPS in Quartus II and Qsys Chapter 2 : Pin Assignments and Timing Constraints Chapter 3 : Introduction to So. C FPGA Boot Sequence Chapter 4 : Generating Pre-Loader and U-Boot files Chapter 5 : Starting up a functional So. C FPGA board 5

Chapter 1: Start from building design in Quartus II software Step 1: Create the top design in Quartus II 6

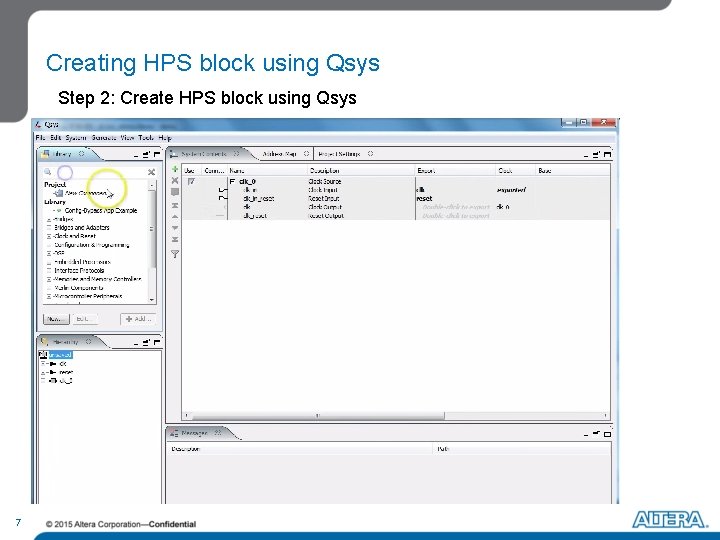

Creating HPS block using Qsys Step 2: Create HPS block using Qsys 7

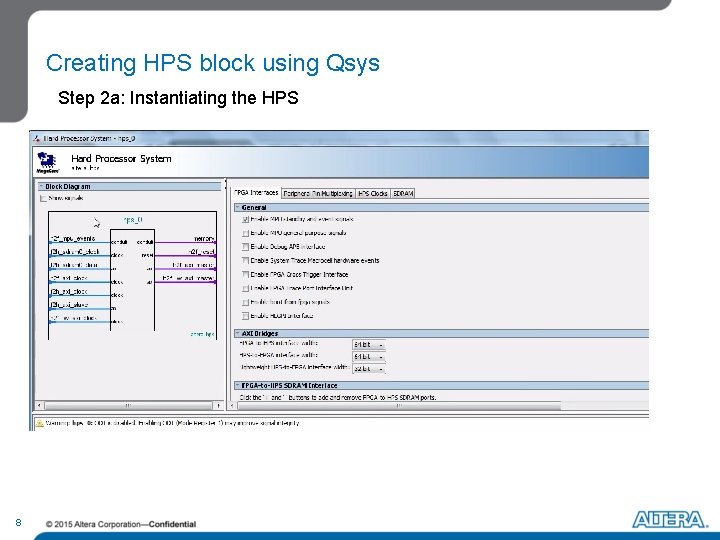

Creating HPS block using Qsys Step 2 a: Instantiating the HPS 8

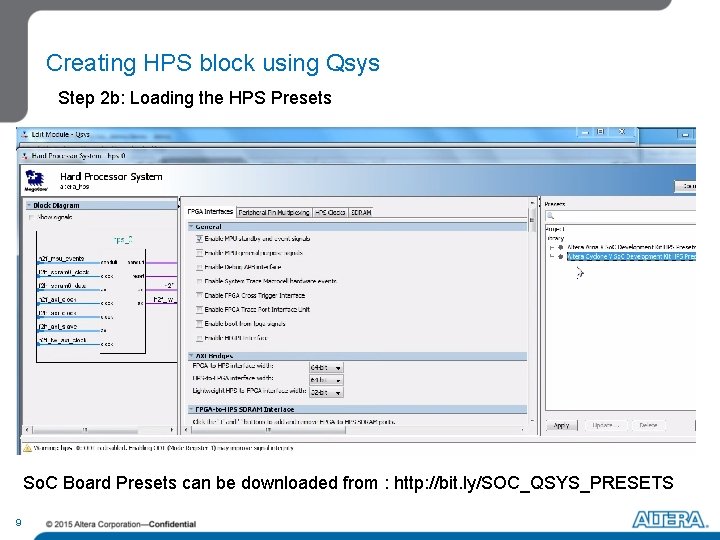

Creating HPS block using Qsys Step 2 b: Loading the HPS Presets So. C Board Presets can be downloaded from : http: //bit. ly/SOC_QSYS_PRESETS 9

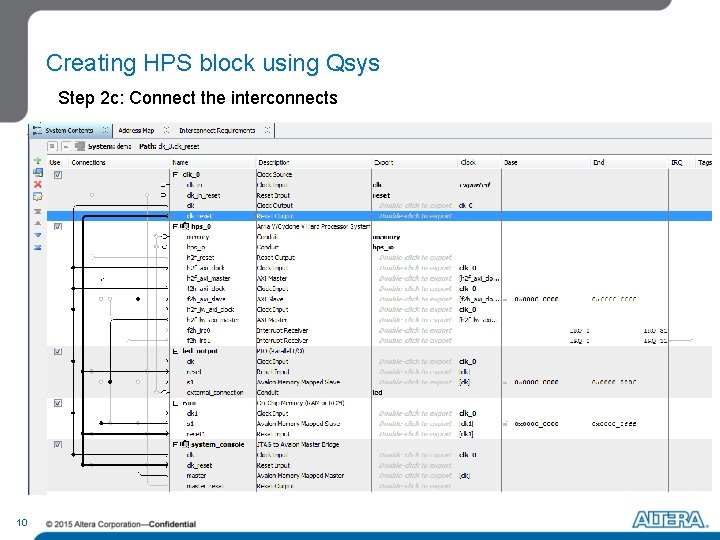

Creating HPS block using Qsys Step 2 c: Connect the interconnects 10

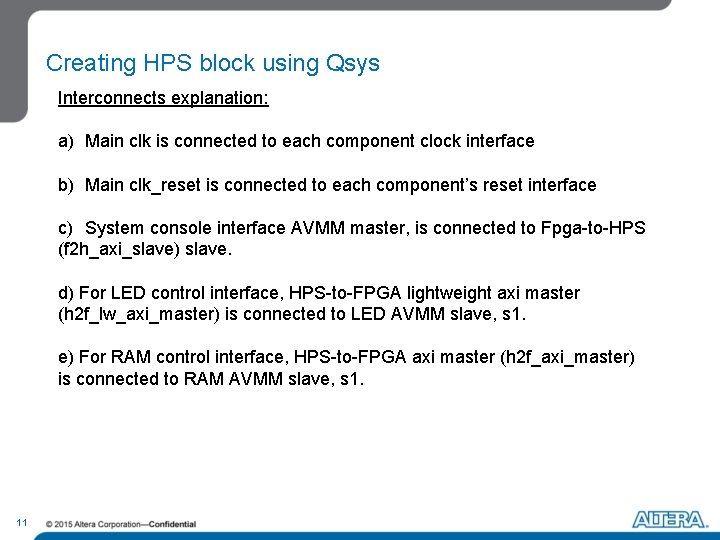

Creating HPS block using Qsys Interconnects explanation: a) Main clk is connected to each component clock interface b) Main clk_reset is connected to each component’s reset interface c) System console interface AVMM master, is connected to Fpga-to-HPS (f 2 h_axi_slave) slave. d) For LED control interface, HPS-to-FPGA lightweight axi master (h 2 f_lw_axi_master) is connected to LED AVMM slave, s 1. e) For RAM control interface, HPS-to-FPGA axi master (h 2 f_axi_master) is connected to RAM AVMM slave, s 1. 11

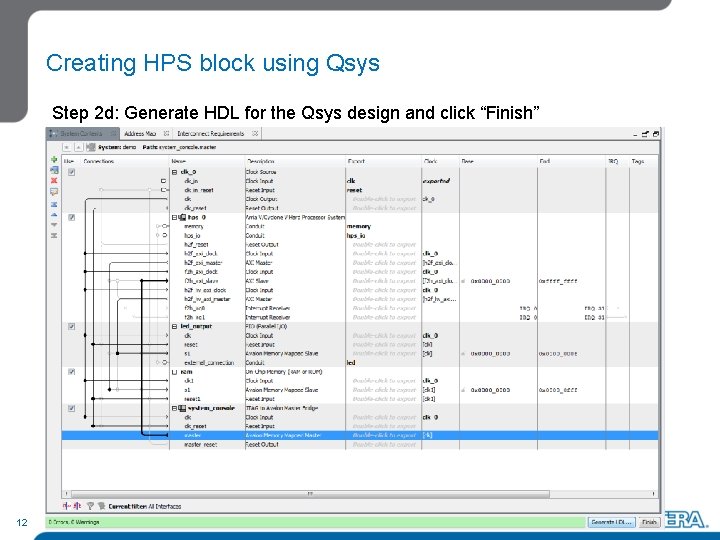

Creating HPS block using Qsys Step 2 d: Generate HDL for the Qsys design and click “Finish” 12

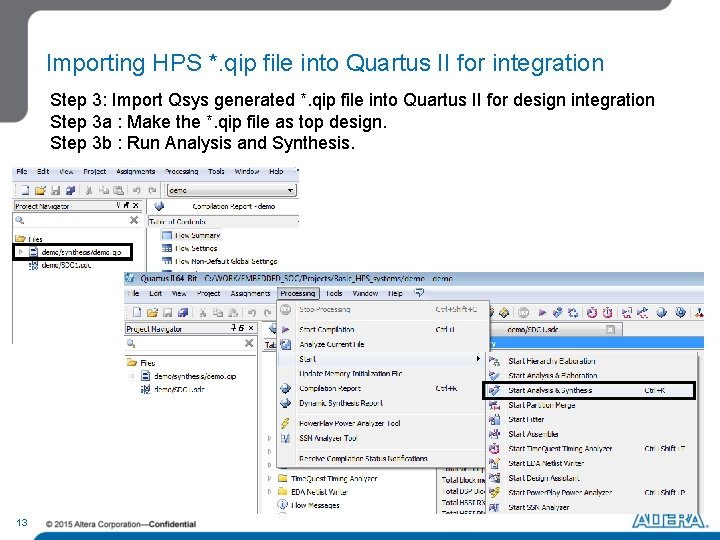

Importing HPS *. qip file into Quartus II for integration Step 3: Import Qsys generated *. qip file into Quartus II for design integration Step 3 a : Make the *. qip file as top design. Step 3 b : Run Analysis and Synthesis. 13

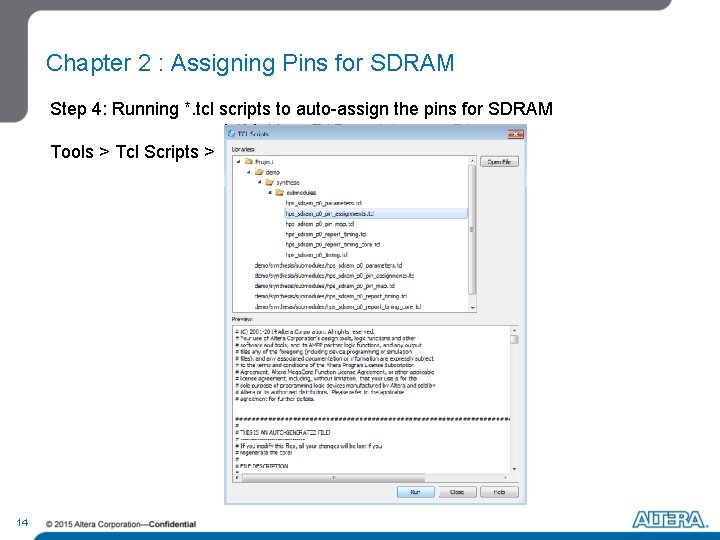

Chapter 2 : Assigning Pins for SDRAM Step 4: Running *. tcl scripts to auto-assign the pins for SDRAM Tools > Tcl Scripts > 14

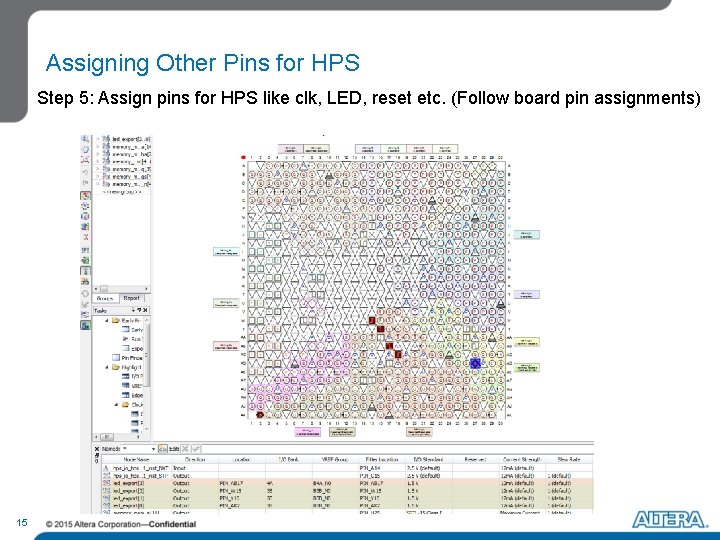

Assigning Other Pins for HPS Step 5: Assign pins for HPS like clk, LED, reset etc. (Follow board pin assignments) 15

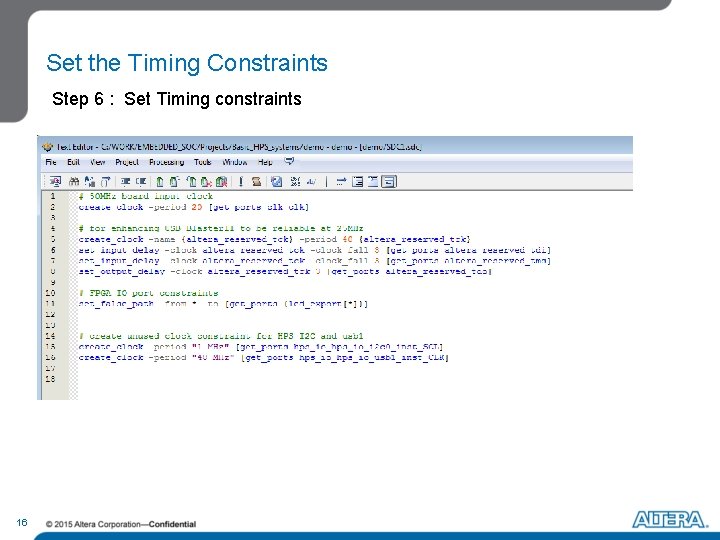

Set the Timing Constraints Step 6 : Set Timing constraints 16

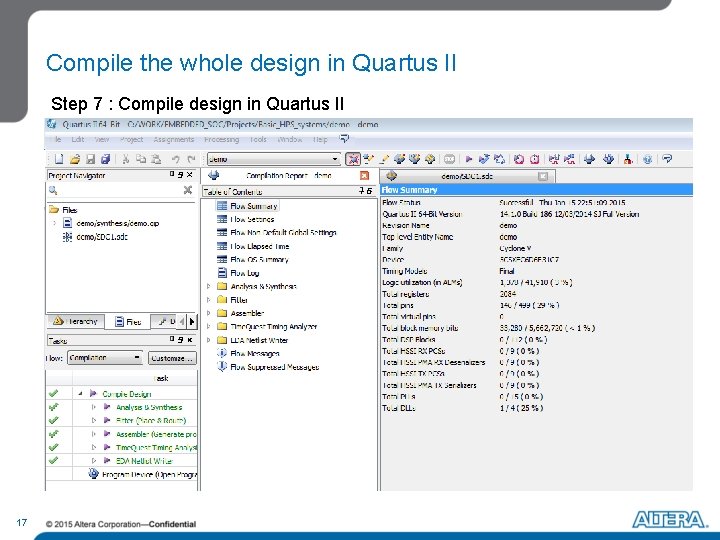

Compile the whole design in Quartus II Step 7 : Compile design in Quartus II 17

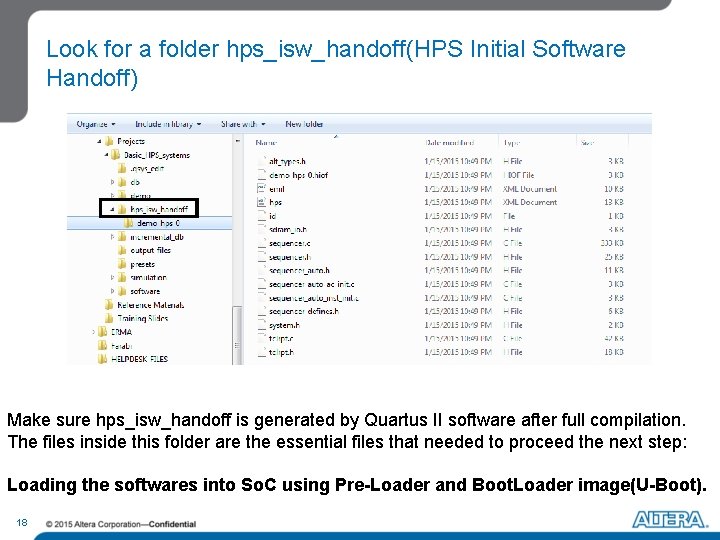

Look for a folder hps_isw_handoff(HPS Initial Software Handoff) Make sure hps_isw_handoff is generated by Quartus II software after full compilation. The files inside this folder are the essential files that needed to proceed the next step: Loading the softwares into So. C using Pre-Loader and Boot. Loader image(U-Boot). 18

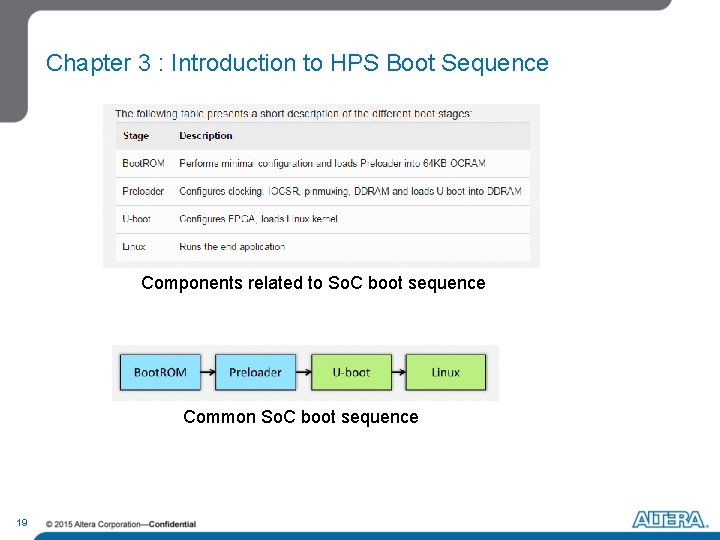

Chapter 3 : Introduction to HPS Boot Sequence Components related to So. C boot sequence Common So. C boot sequence 19

What is U-Boot ? U-Boot is an open source, primary boot loader used in embedded devices. U-boot is licensed under GPL as it is an open source framework. More details on U-Boot, refer to : http: //www. denx. de/wiki/U-Boot/Documentation Main Functions of U-Boot are: a) Setting up the OS environment b) Fetching the OS image from NAND, SD/MMC, serial NOR Flash, Ethernet through TFTP, USB mass storage. c) Storing the boot image to SDRAM and pass control over to subsequent bootloader. d) Providing a console that can be used for user operations such as modifying the Device Tree Blob(DTB) and boot arguments. Notes: Like in x 86 intel system, the OS is booted by BIOS. In Linux system, it is equal to U-Boot. 20

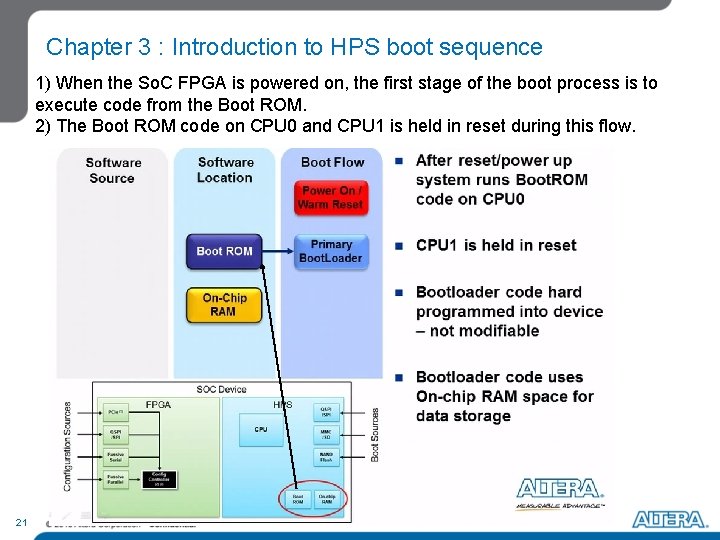

Chapter 3 : Introduction to HPS boot sequence 1) When the So. C FPGA is powered on, the first stage of the boot process is to execute code from the Boot ROM. 2) The Boot ROM code on CPU 0 and CPU 1 is held in reset during this flow. 21

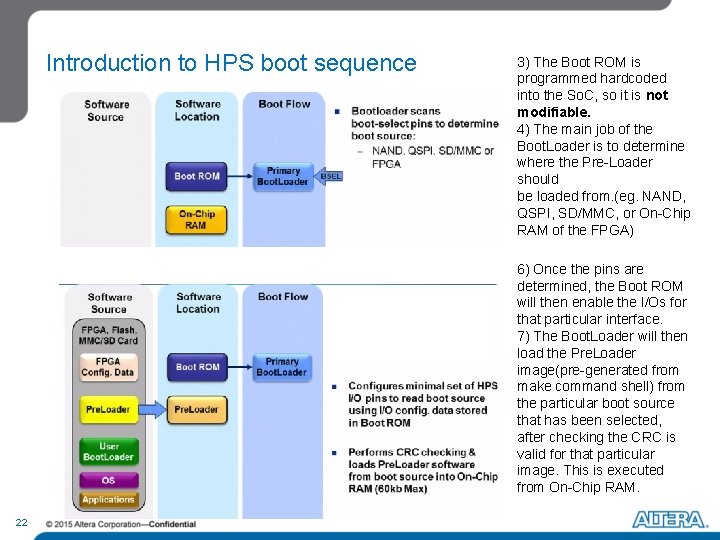

Introduction to HPS boot sequence 3) The Boot ROM is programmed hardcoded into the So. C, so it is not modifiable. 4) The main job of the Boot. Loader is to determine where the Pre-Loader should be loaded from. (eg. NAND, QSPI, SD/MMC, or On-Chip RAM of the FPGA) 6) Once the pins are determined, the Boot ROM will then enable the I/Os for that particular interface. 7) The Boot. Loader will then load the Pre. Loader image(pre-generated from make command shell) from the particular boot source that has been selected, after checking the CRC is valid for that particular image. This is executed from On-Chip RAM. 22

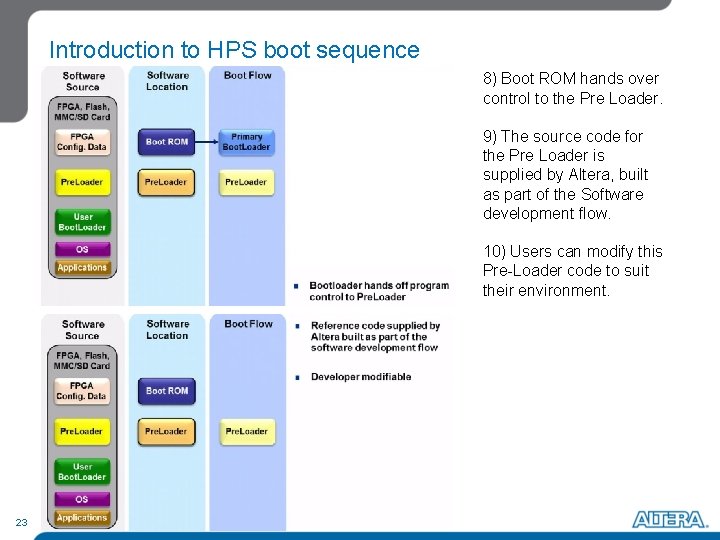

Introduction to HPS boot sequence 8) Boot ROM hands over control to the Pre Loader. 9) The source code for the Pre Loader is supplied by Altera, built as part of the Software development flow. 10) Users can modify this Pre-Loader code to suit their environment. 23

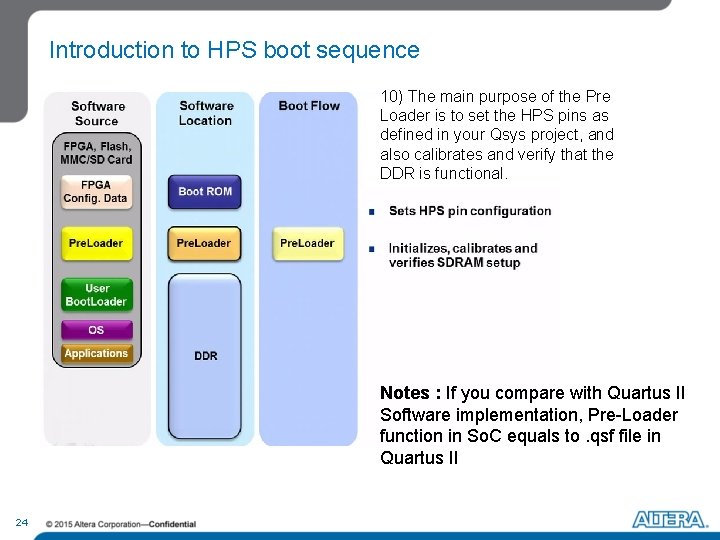

Introduction to HPS boot sequence 10) The main purpose of the Pre Loader is to set the HPS pins as defined in your Qsys project, and also calibrates and verify that the DDR is functional. Notes : If you compare with Quartus II Software implementation, Pre-Loader function in So. C equals to. qsf file in Quartus II 24

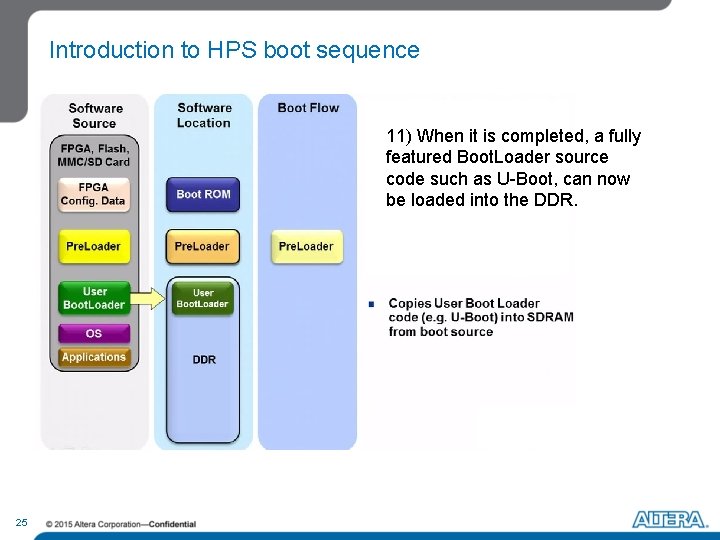

Introduction to HPS boot sequence 11) When it is completed, a fully featured Boot. Loader source code such as U-Boot, can now be loaded into the DDR. 25

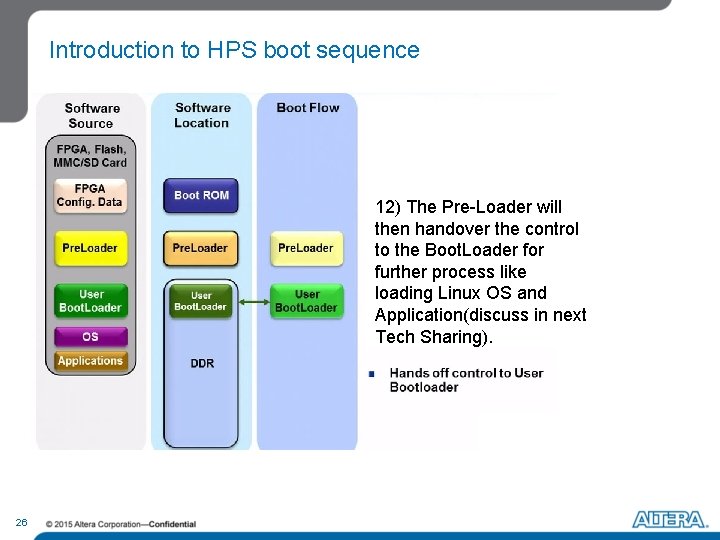

Introduction to HPS boot sequence 12) The Pre-Loader will then handover the control to the Boot. Loader for further process like loading Linux OS and Application(discuss in next Tech Sharing). 26

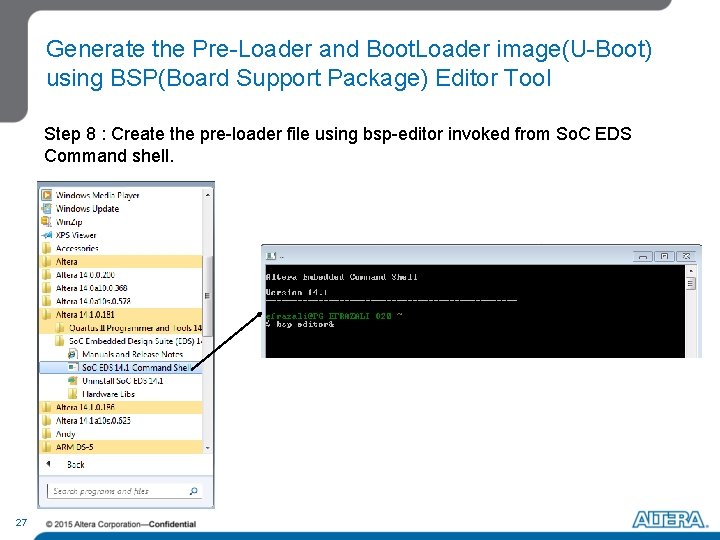

Generate the Pre-Loader and Boot. Loader image(U-Boot) using BSP(Board Support Package) Editor Tool Step 8 : Create the pre-loader file using bsp-editor invoked from So. C EDS Command shell. 27

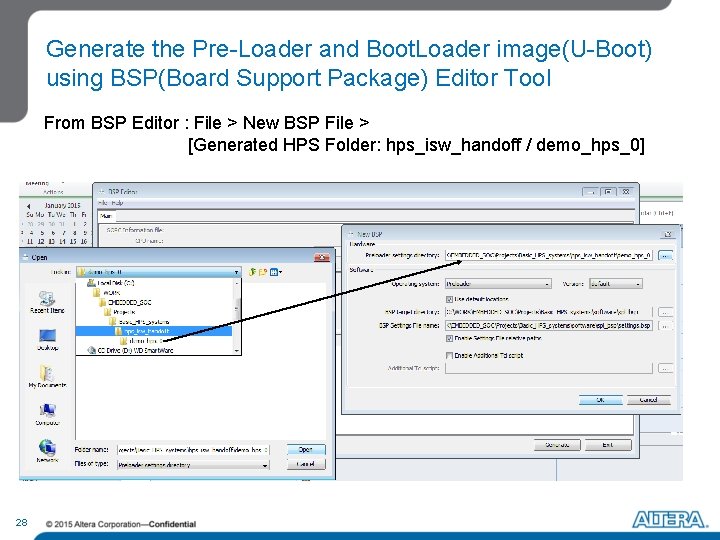

Generate the Pre-Loader and Boot. Loader image(U-Boot) using BSP(Board Support Package) Editor Tool From BSP Editor : File > New BSP File > [Generated HPS Folder: hps_isw_handoff / demo_hps_0] 28

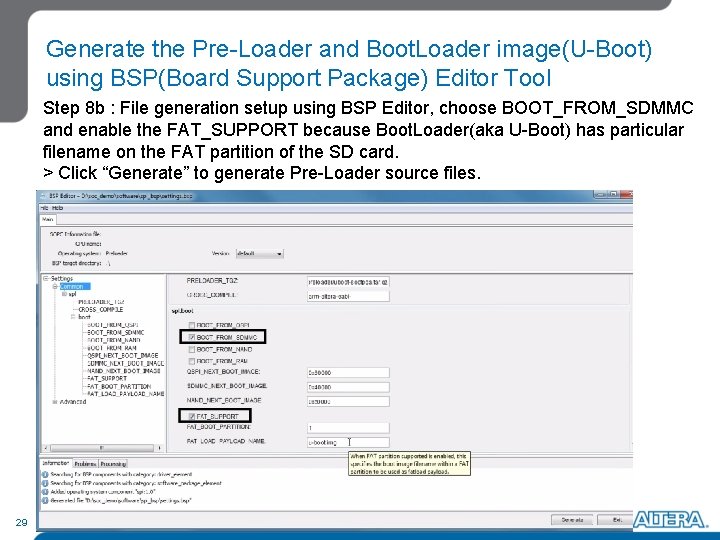

Generate the Pre-Loader and Boot. Loader image(U-Boot) using BSP(Board Support Package) Editor Tool Step 8 b : File generation setup using BSP Editor, choose BOOT_FROM_SDMMC and enable the FAT_SUPPORT because Boot. Loader(aka U-Boot) has particular filename on the FAT partition of the SD card. > Click “Generate” to generate Pre-Loader source files. 29

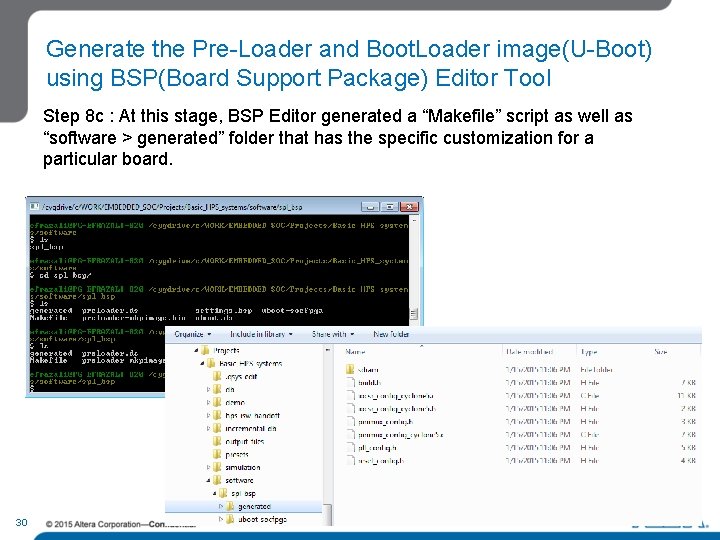

Generate the Pre-Loader and Boot. Loader image(U-Boot) using BSP(Board Support Package) Editor Tool Step 8 c : At this stage, BSP Editor generated a “Makefile” script as well as “software > generated” folder that has the specific customization for a particular board. 30

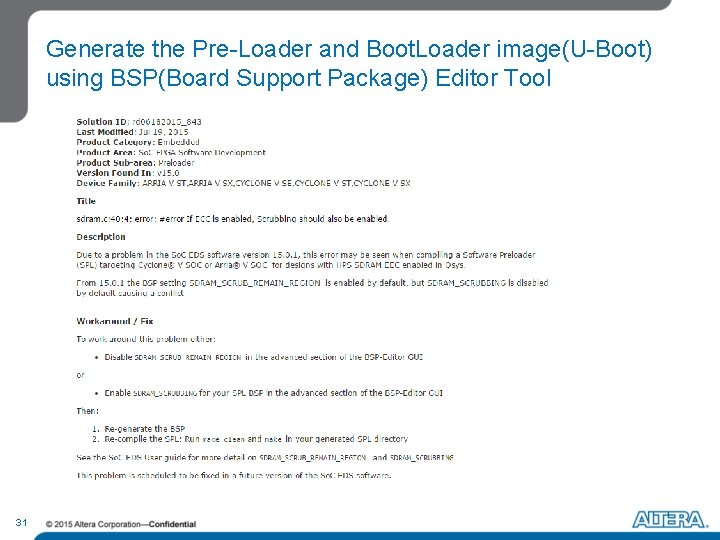

Generate the Pre-Loader and Boot. Loader image(U-Boot) using BSP(Board Support Package) Editor Tool 31

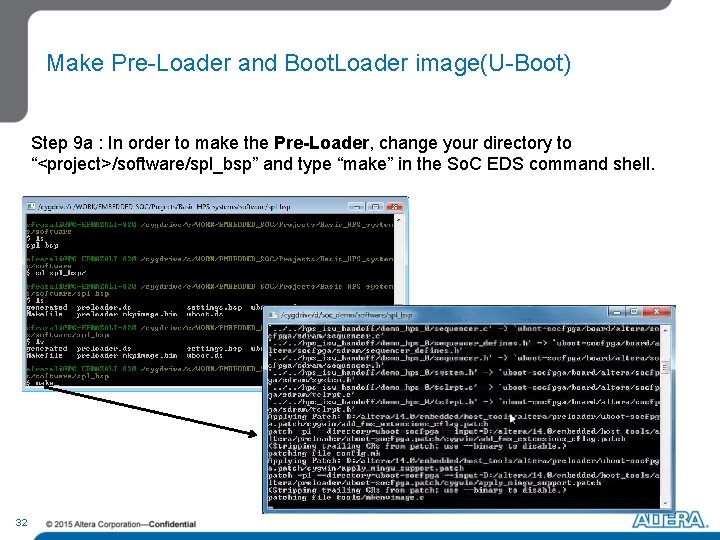

Make Pre-Loader and Boot. Loader image(U-Boot) Step 9 a : In order to make the Pre-Loader, change your directory to “<project>/software/spl_bsp” and type “make” in the So. C EDS command shell. 32

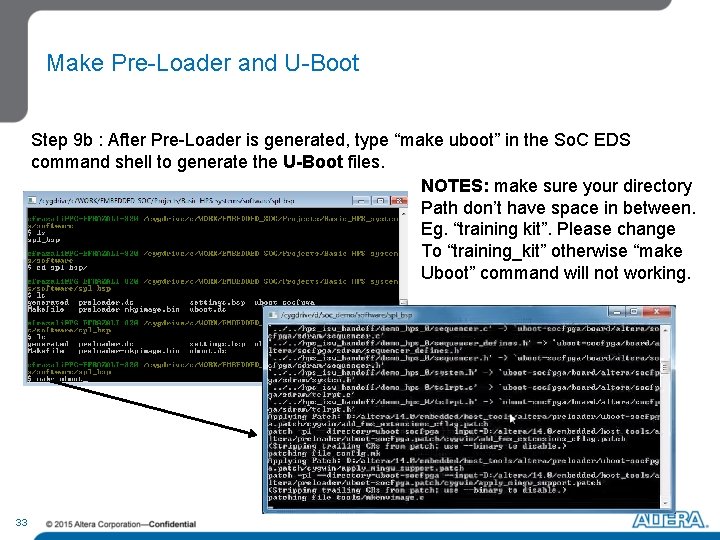

Make Pre-Loader and U-Boot Step 9 b : After Pre-Loader is generated, type “make uboot” in the So. C EDS command shell to generate the U-Boot files. NOTES: make sure your directory Path don’t have space in between. Eg. “training kit”. Please change To “training_kit” otherwise “make Uboot” command will not working. 33

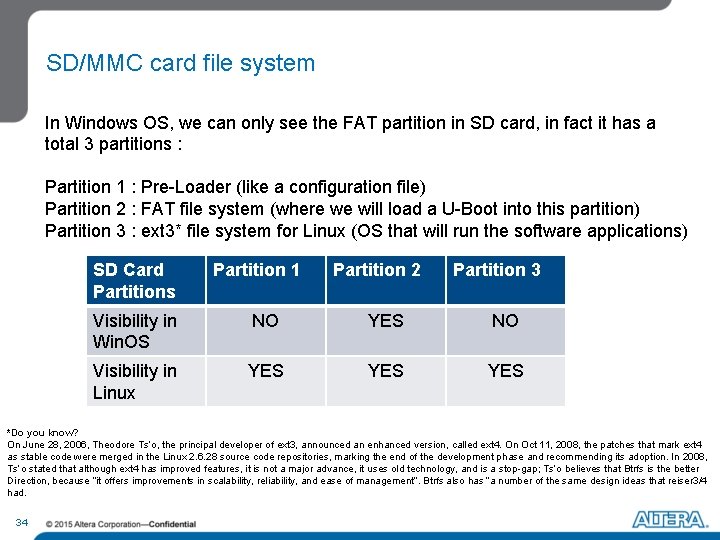

SD/MMC card file system In Windows OS, we can only see the FAT partition in SD card, in fact it has a total 3 partitions : Partition 1 : Pre-Loader (like a configuration file) Partition 2 : FAT file system (where we will load a U-Boot into this partition) Partition 3 : ext 3* file system for Linux (OS that will run the software applications) SD Card Partitions Partition 1 Partition 2 Partition 3 Visibility in Win. OS NO YES NO Visibility in Linux YES YES *Do you know? On June 28, 2006, Theodore Ts’o, the principal developer of ext 3, announced an enhanced version, called ext 4. On Oct 11, 2008, the patches that mark ext 4 as stable code were merged in the Linux 2. 6. 28 source code repositories, marking the end of the development phase and recommending its adoption. In 2008, Ts’o stated that although ext 4 has improved features, it is not a major advance, it uses old technology, and is a stop-gap; Ts’o believes that Btrfs is the better Direction, because “it offers improvements in scalability, reliability, and ease of management”. Btrfs also has “a number of the same design ideas that reiser 3/4 had. 34

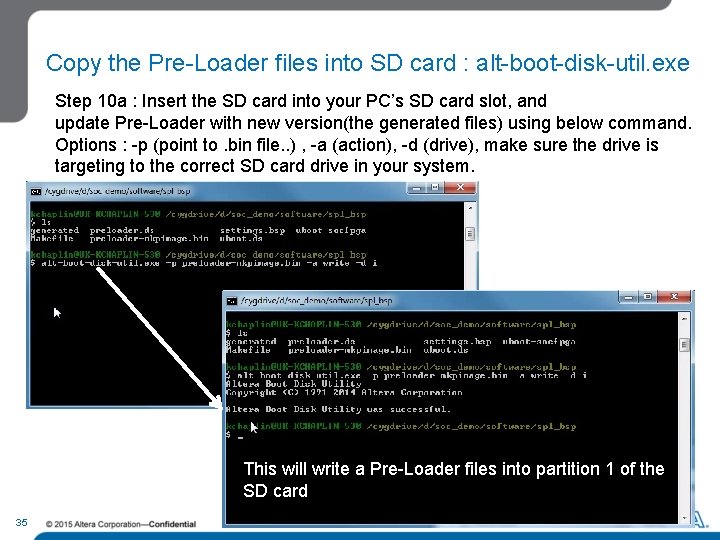

Copy the Pre-Loader files into SD card : alt-boot-disk-util. exe Step 10 a : Insert the SD card into your PC’s SD card slot, and update Pre-Loader with new version(the generated files) using below command. Options : -p (point to. bin file. . ) , -a (action), -d (drive), make sure the drive is targeting to the correct SD card drive in your system. This will write a Pre-Loader files into partition 1 of the SD card 35

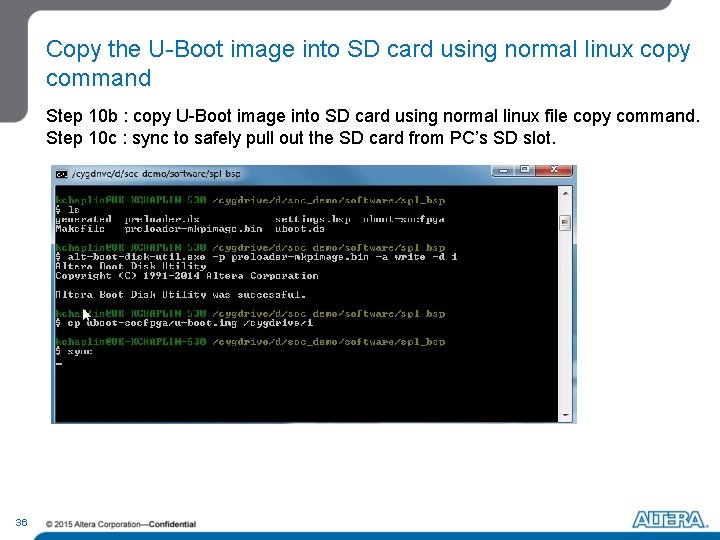

Copy the U-Boot image into SD card using normal linux copy command Step 10 b : copy U-Boot image into SD card using normal linux file copy command. Step 10 c : sync to safely pull out the SD card from PC’s SD slot. This will write a Pre-Loader files into partition 1 of the SD card 36

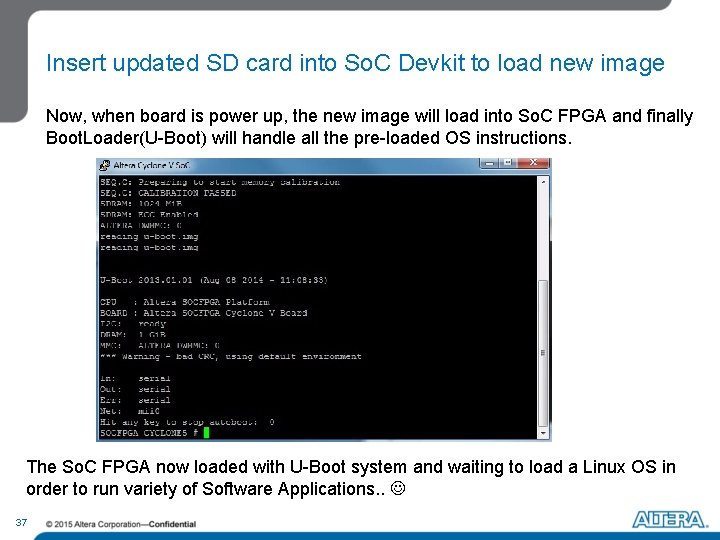

Insert updated SD card into So. C Devkit to load new image Now, when board is power up, the new image will load into So. C FPGA and finally Boot. Loader(U-Boot) will handle all the pre-loaded OS instructions. The So. C FPGA now loaded with U-Boot system and waiting to load a Linux OS in order to run variety of Software Applications. . 37

Training Kit available at mysites(QII v 14. 1 compatible) Training Kit contents : 1) HPS design project archive file *. qar 2) Qsys project file *. qsys 3) So. C devkit preset files. Link : http: //mysitespg/personal/efrazali/Shared%20 Documents/Embedded%20 and%20 So. C/Training%20 Kit. zip 38

Reference Video Links by Kris Chaplin (UK FAE) Video 1 : Creating So. C HPS system using Qsys Video 2 : So. C HPS integration with Quartus II Video 3 : Generate Pre-Loader and U-boot for So. C 39

So. C Boot Loading Reference Documents https: //rocketboards. org and Altera HPS userguide 40

Thank You

- Slides: 41