How the Big Blue Grinch Stole the Apollo

How the Big Blue Grinch Stole the Apollo Guidance Computer … Only They Didn’t! Hugh Blair-Smith MAPLD 2005

Replace MIT’s AGC with IBM’s LVDC? ? • • • IBM FSD’s self-image “Established” Boost Guidance Taking sides: Industry vs. Academe TMR for fault tolerance Consultant role of Bellcomm

LVDC Architecture (1) • Serial logic – – Reduces transistor count Performance penalty Core memory access is still parallel Bits in low-to-high sequence for carry propagation • “Word time” is thus determined by carry propagation rate • My estimate: 3 word times per memory cycle – Forces 2’s complement notation: logical negation is separate – Separate multiplication subsystem, reminiscent of 1940 s • 7 (I think) instructions needed to fill time until product is ready

LVDC Architecture (2) • Pedestrian instruction set – – – No exchange-with-memory No divide No facility for indexing or indirect addressing Not easily supportive of multiple precision Adequate for evaluating Adaptive Polynomials: the “APE” • Mediocre at best as a general purpose computer

LVDC Architecture (3) • Triple Modular Redundancy (TMR) – – – Fail-operational rule (FO) Appropriate for high-risk environment inside booster Forces serial logic to save triplicated transistor count No clear route to a degraded fail-safe (FS) state My guess: this was the clincher for Bellcomm

LVDC Architecture (4) • Interfaces – – Inputs: IMU, ground commands, other? Outputs: IMU, engine on-off & gimbals, other? No general crew interface Not readily expandable beyond boost functions

MIT Reactions to Proposal • General purpose architecture is required – High performance in many applications • Reliability can be achieved – Spacecraft environment is low-risk • Has to be, with humans present! – MIT’s Polaris experience • Interface requires flexibility, expandability – Crew interface, additional subsystems

AGC Architecture (1) • Parallel logic – Greater transistor (or gate) count • Eased by availability of Fairchild NOR-gate ICs – High performance, especially complex instructions • 12 pulse times per memory cycle – Core memory access is parallel anyway – Allows 1’s or 2’s complement notation: MIT took 1’s • Logical negation same as numerical negation • 1’s complement implies end-around carry – Multiply and divide share normal CPU resources

AGC Architecture (2) • Powerful and elegant instruction set – – – XCH to facilitate time-sharing of erasable (RAM) locations DV with signed remainder CCS = (Count, Compare & Skip) for flexible testing & looping INDEX for indexing and indirect addressing Support multiple precision (with independent signs per word) Support general purpose applications, including: • Multitasking “executive” to schedule jobs by priority • Interpretive code for vector-matrix operations

AGC Architecture (3) • Reliable “single string” – No fail-operational (FO) capability for hard failures • Restarts handle transient faults gracefully – – Takes advantage of low-risk spacecraft environment Allows use of parallel logic with moderate gate count Fail-safe (FS) capability provided by AGS Spacecraft has to have a lot of single-string subsystems anyway • IMU and sextant, for instance

AGC Architecture (4) • Interfaces – Inputs: flexible set of subsystems and transfer modes • PINC/MINC counters and timers • UART • Channels – Outputs: flexible set of subsystems and transfer modes • DINC down-counters • UART: SHINC-SHANC • Channels – General crew interface (DSKY) • Also shared by uplink (the “mechanical boy”)

Summary of the Issue’s Resolution • MIT response was nothing if not emphatic – “We are astonished that Bellcomm could have come to this conclusion” – Dick Battin • An odd battlefield for so epic a struggle – MSC wasn’t built yet, nor was IAH – MIT, Bellcomm, and NASA met in a motel room across from Hobby Airport • People and paper slides perched on 2 king beds

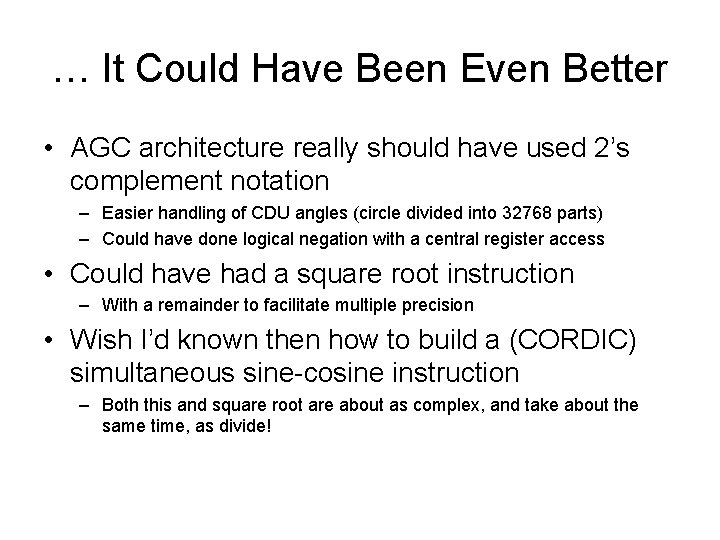

… It Could Have Been Even Better • AGC architecture really should have used 2’s complement notation – Easier handling of CDU angles (circle divided into 32768 parts) – Could have done logical negation with a central register access • Could have had a square root instruction – With a remainder to facilitate multiple precision • Wish I’d known then how to build a (CORDIC) simultaneous sine-cosine instruction – Both this and square root are about as complex, and take about the same time, as divide!

- Slides: 13