How caches take advantage of Temporal locality How

- Slides: 42

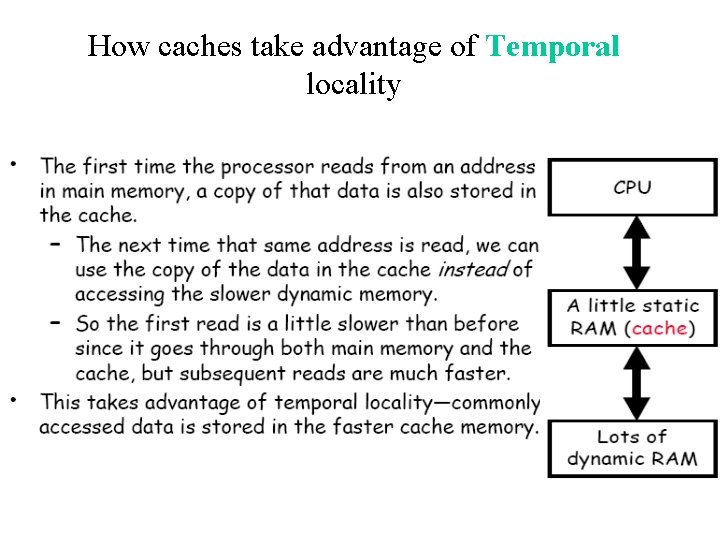

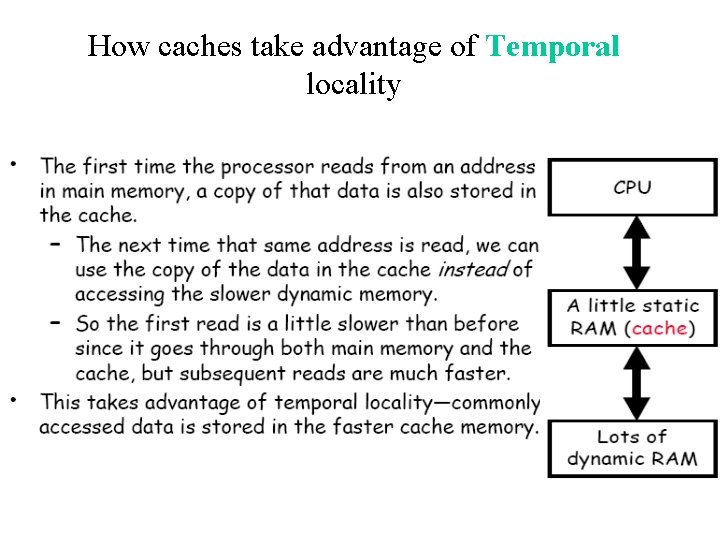

How caches take advantage of Temporal locality

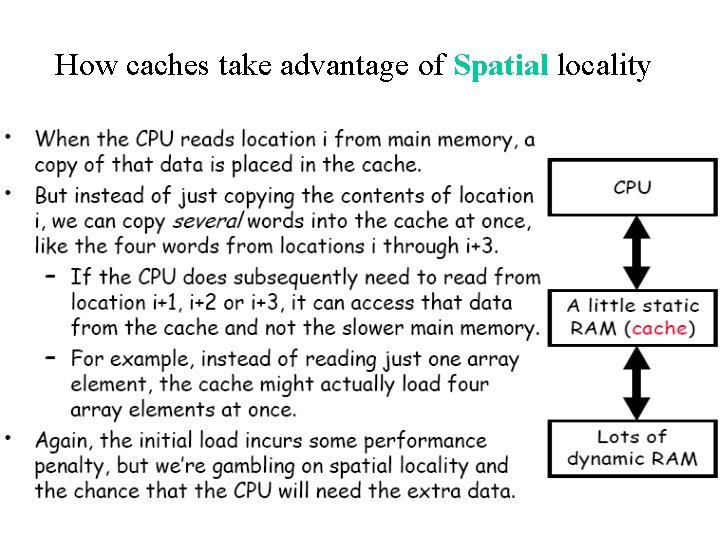

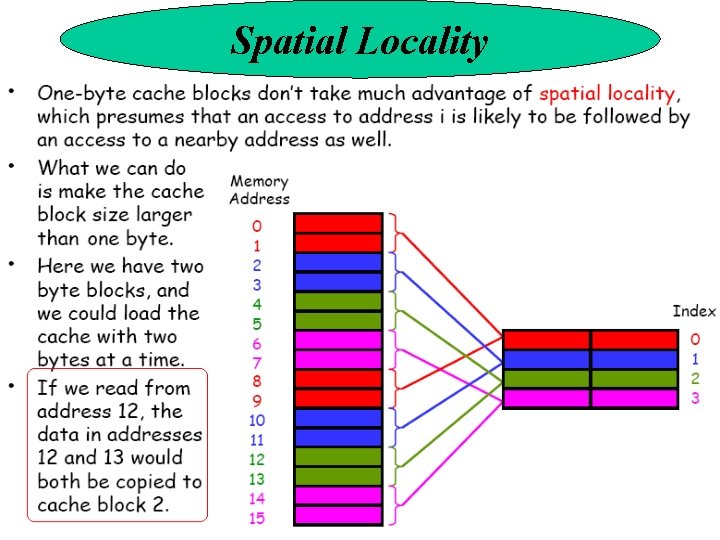

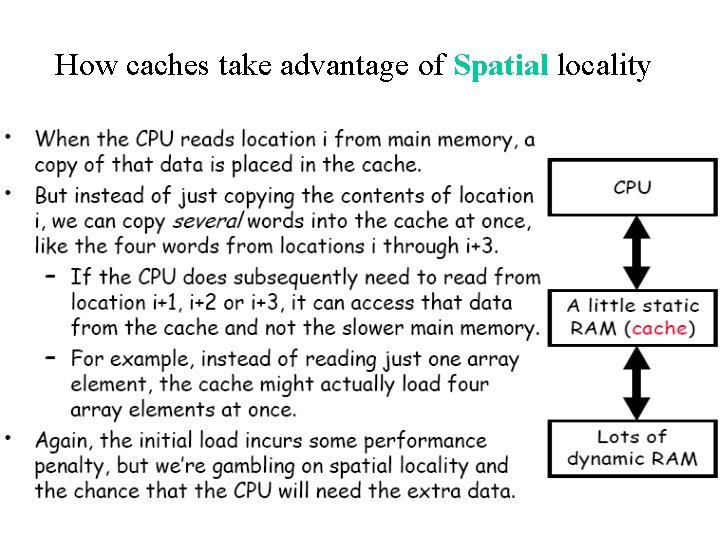

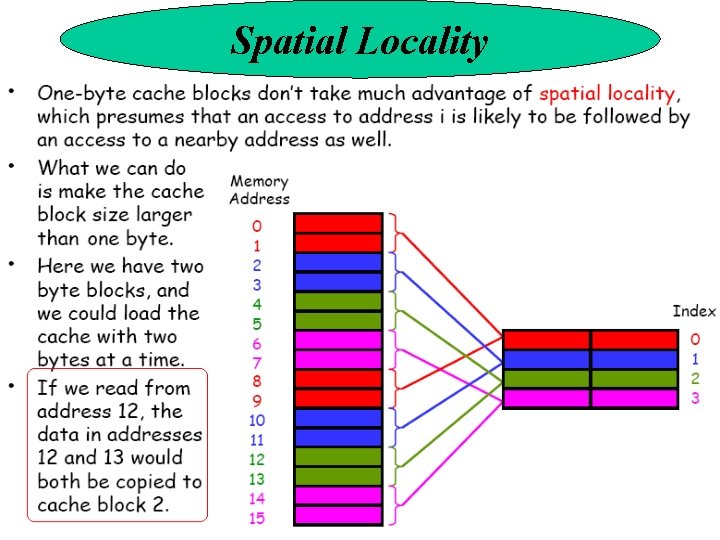

How caches take advantage of Spatial locality

Cache Hits

Cache Misses

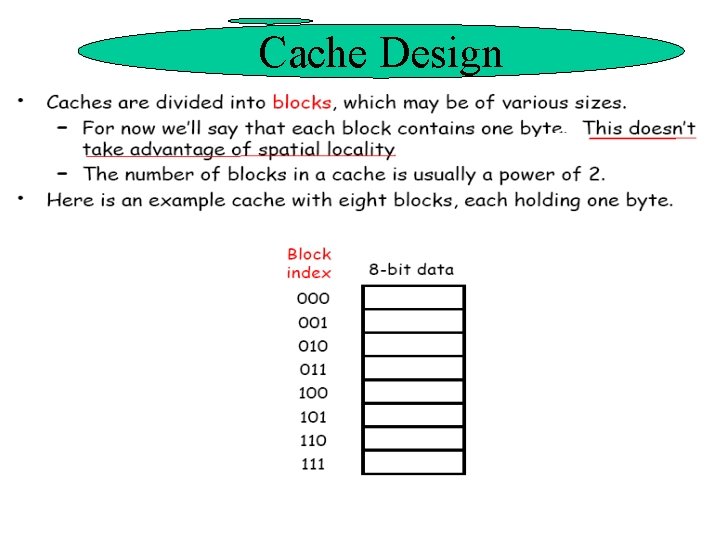

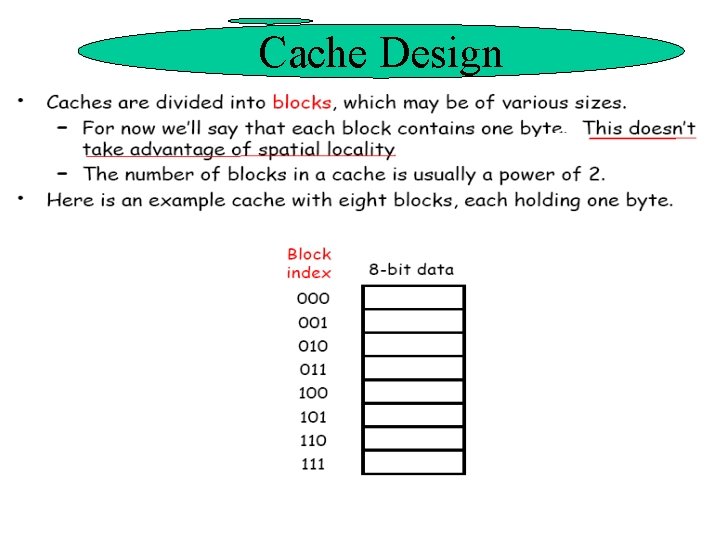

Cache Design

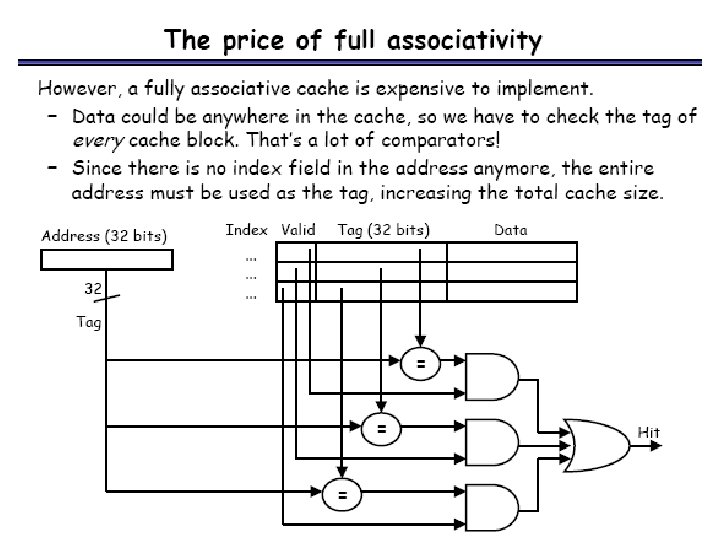

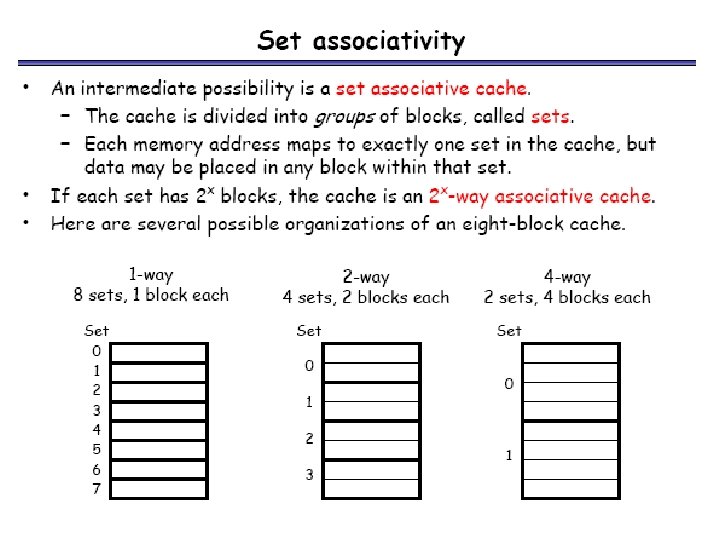

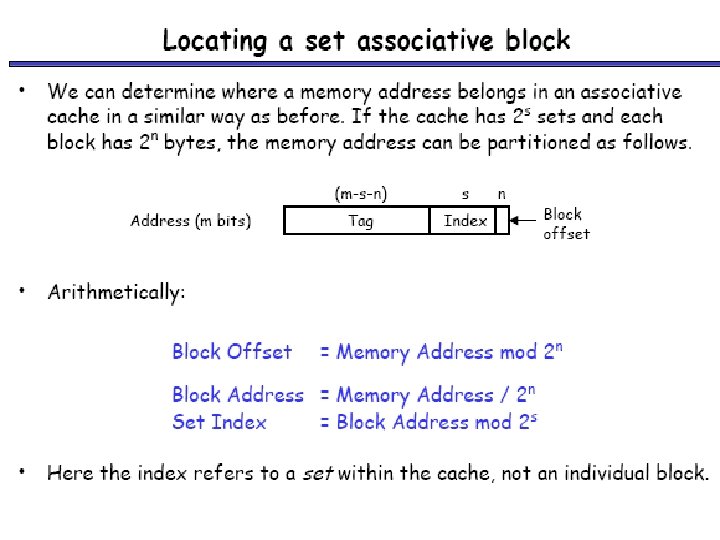

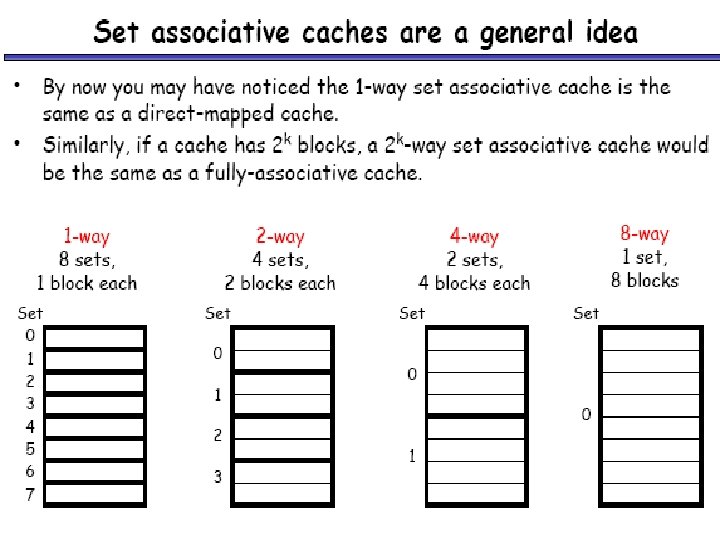

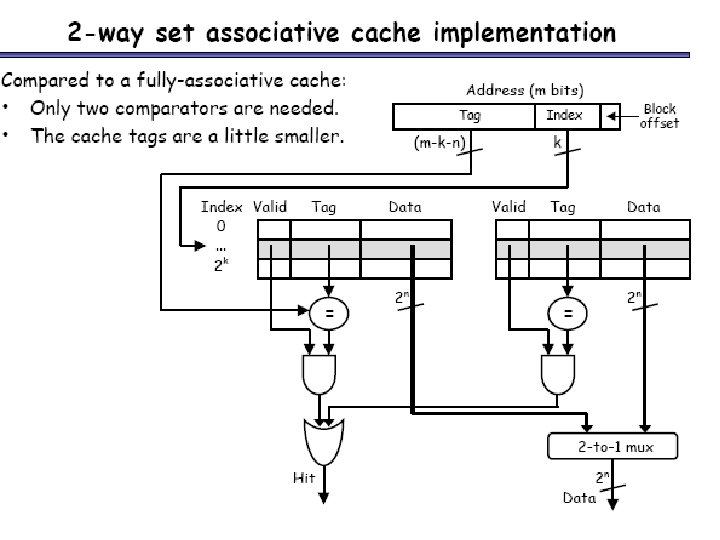

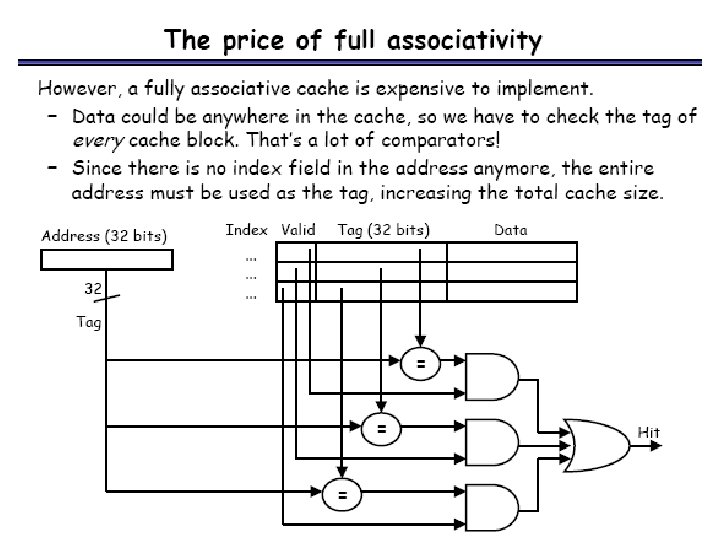

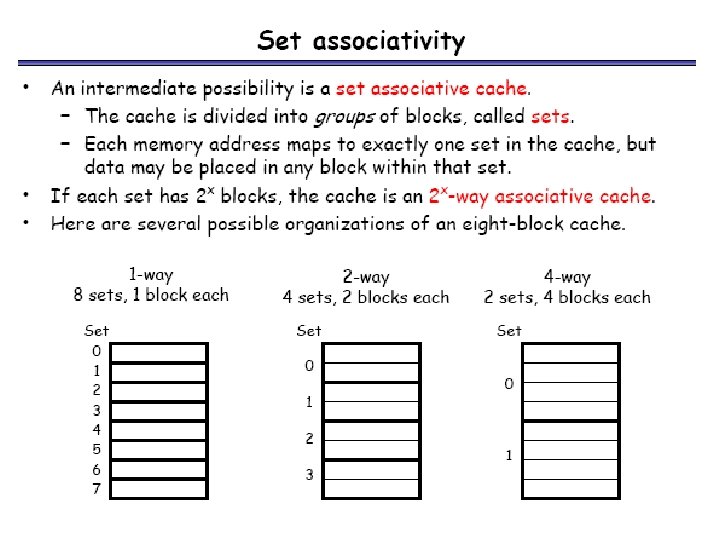

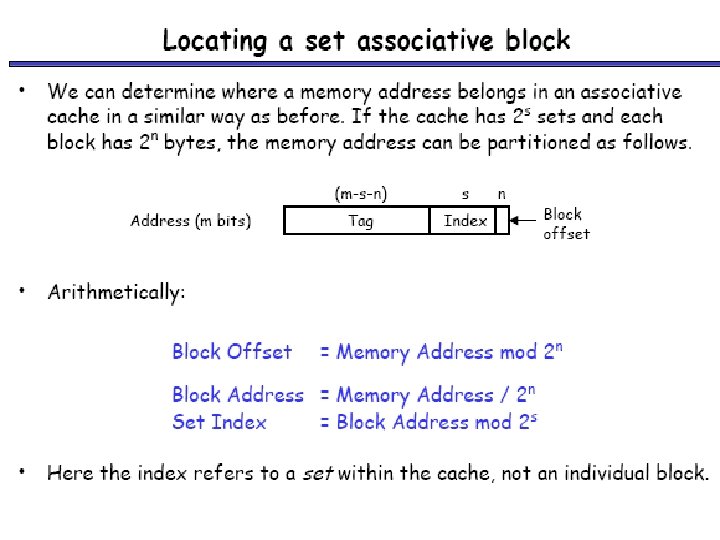

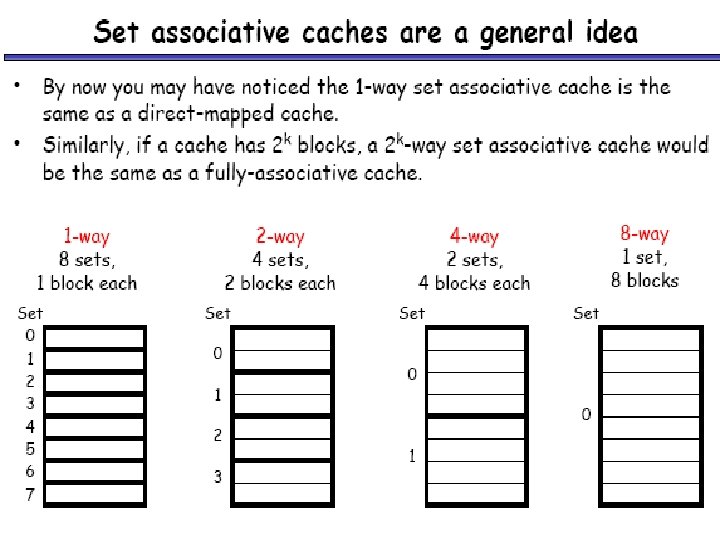

Mapping schemes – Direct Mapped – Set Associative – Fully Associative

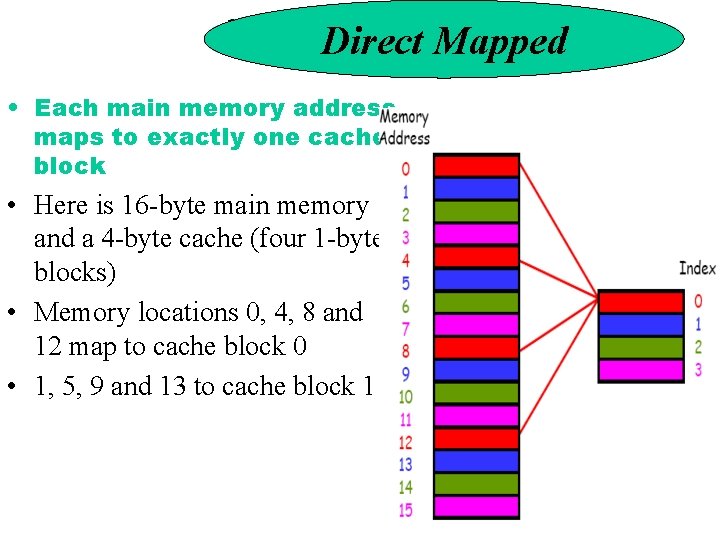

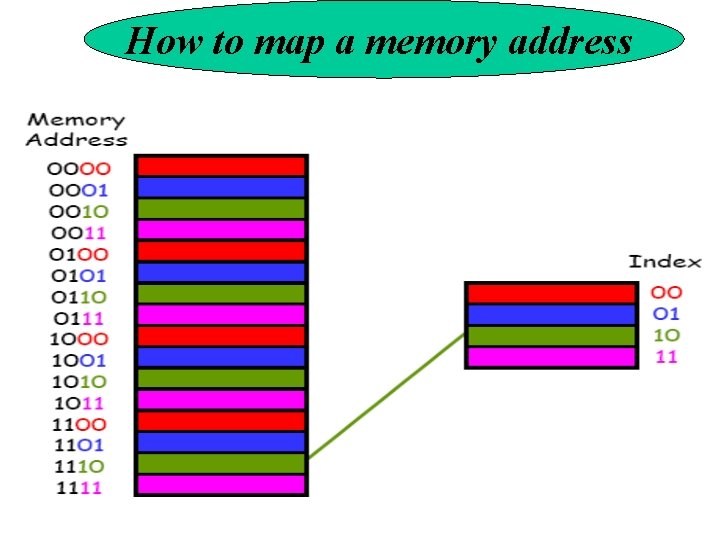

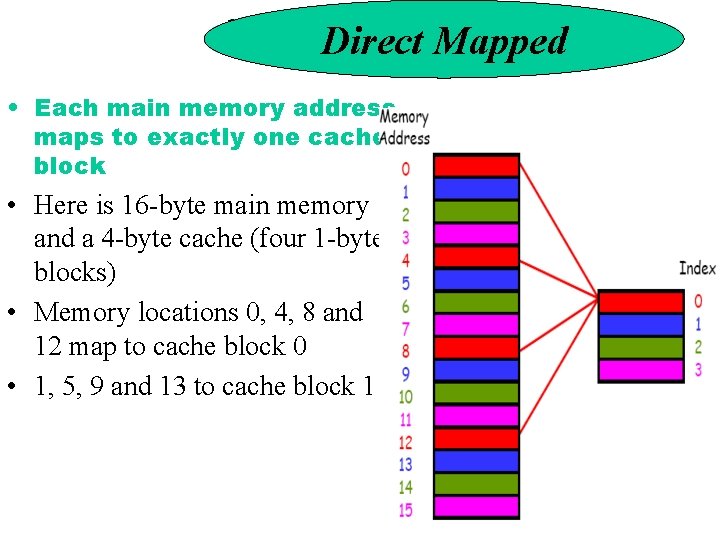

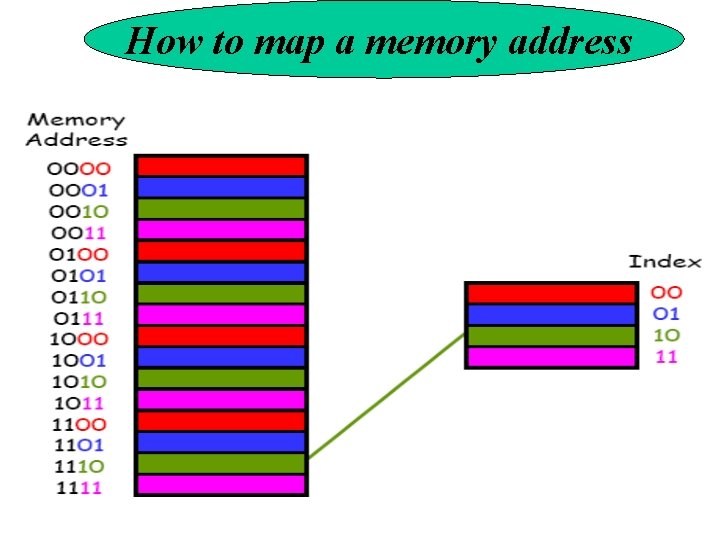

Direct Mapped • Each main memory address maps to exactly one cache block • Here is 16 -byte main memory and a 4 -byte cache (four 1 -byte blocks) • Memory locations 0, 4, 8 and 12 map to cache block 0 • 1, 5, 9 and 13 to cache block 1

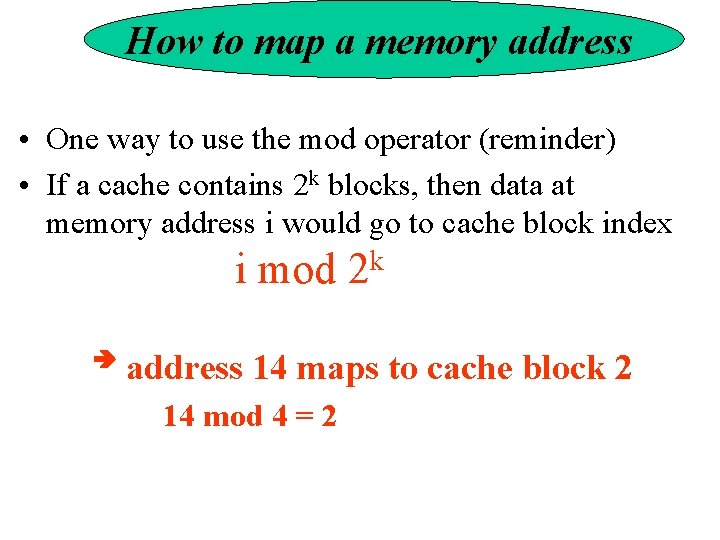

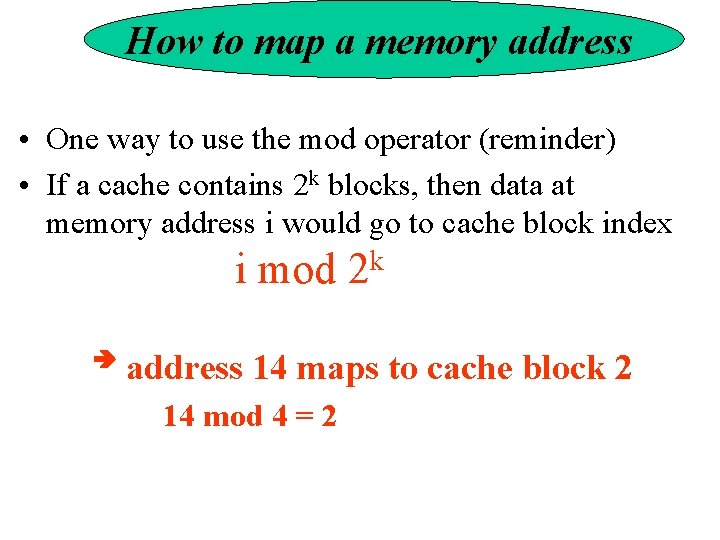

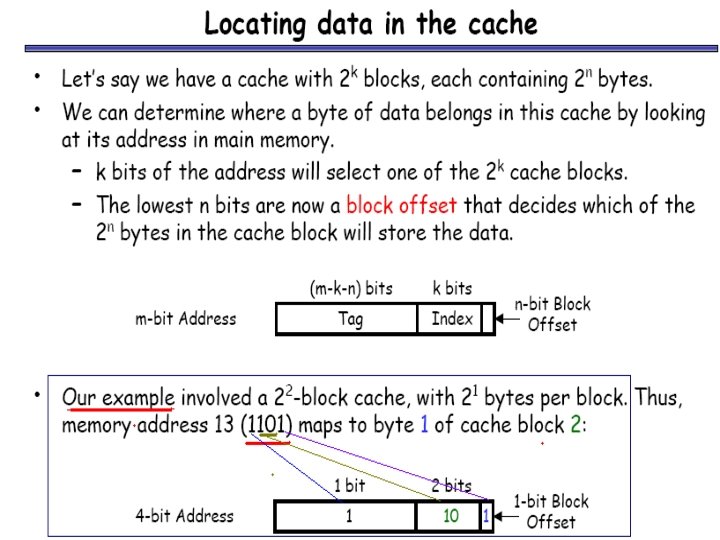

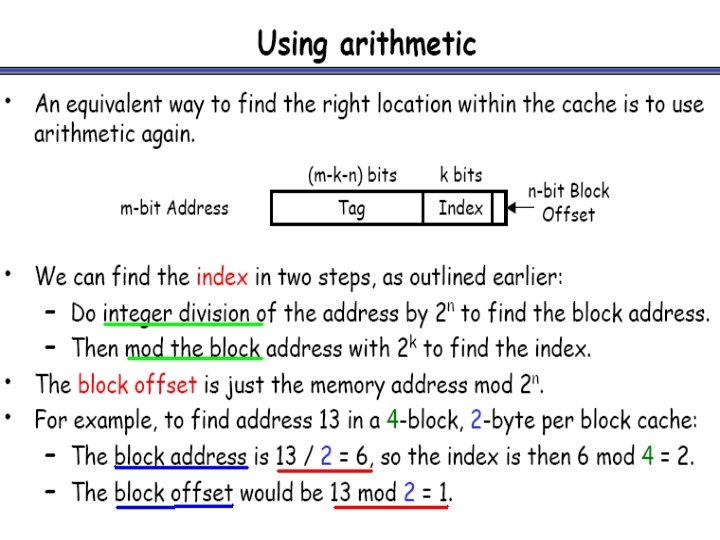

How to map a memory address • One way to use the mod operator (reminder) • If a cache contains 2 k blocks, then data at memory address i would go to cache block index i mod 2 k address 14 maps to cache block 2 14 mod 4 = 2

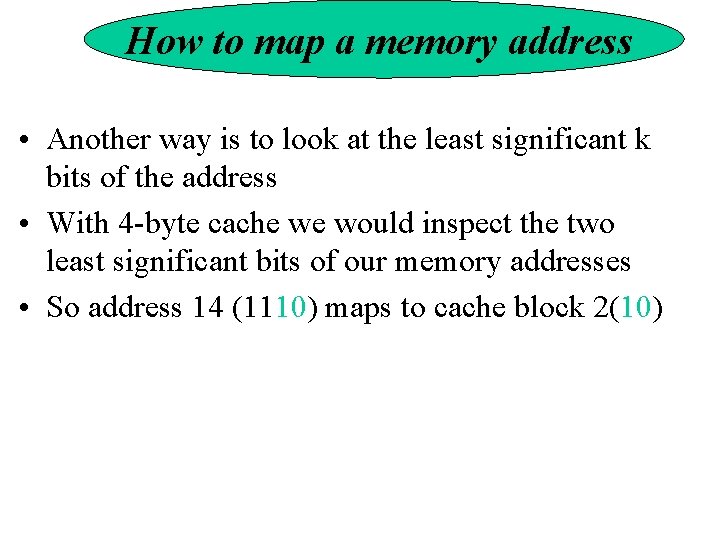

How to map a memory address • Another way is to look at the least significant k bits of the address • With 4 -byte cache we would inspect the two least significant bits of our memory addresses • So address 14 (1110) maps to cache block 2(10)

How to map a memory address

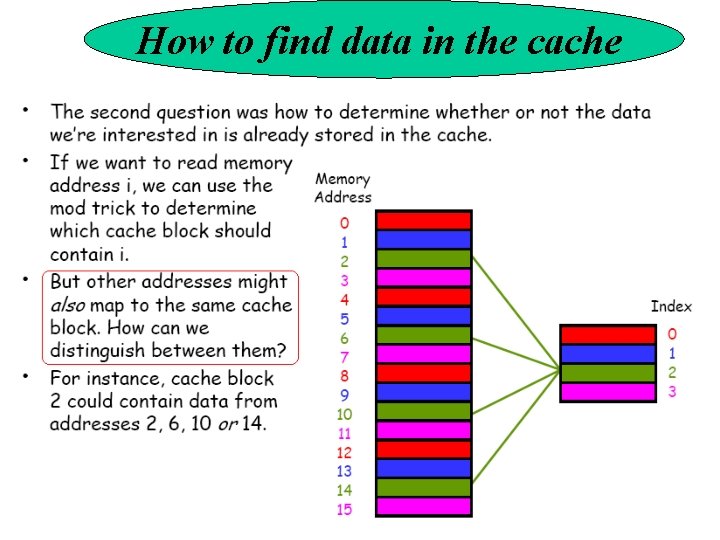

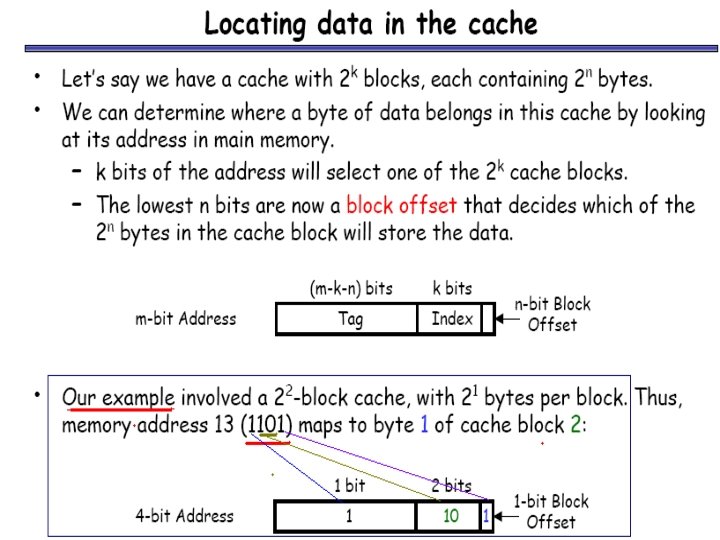

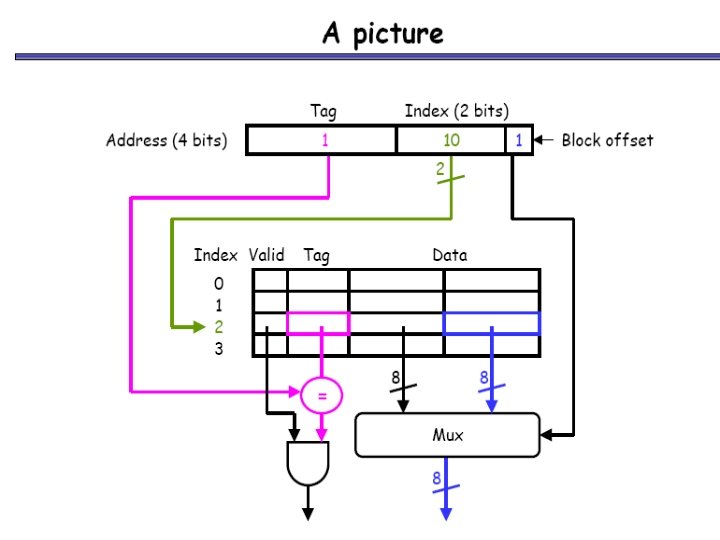

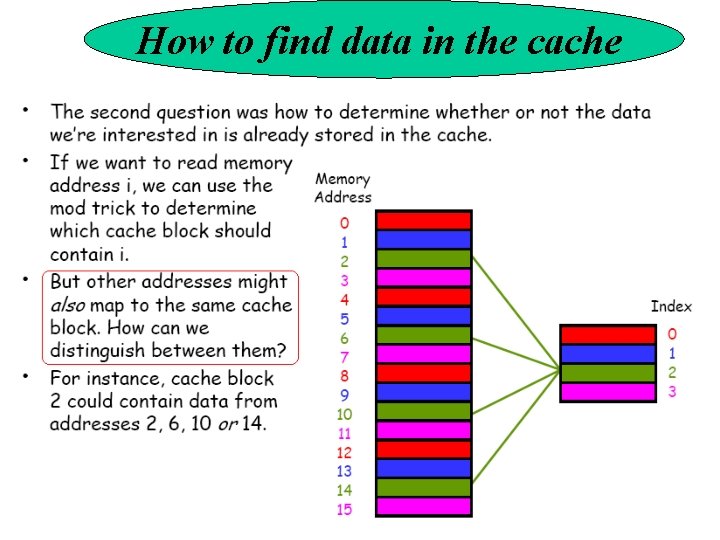

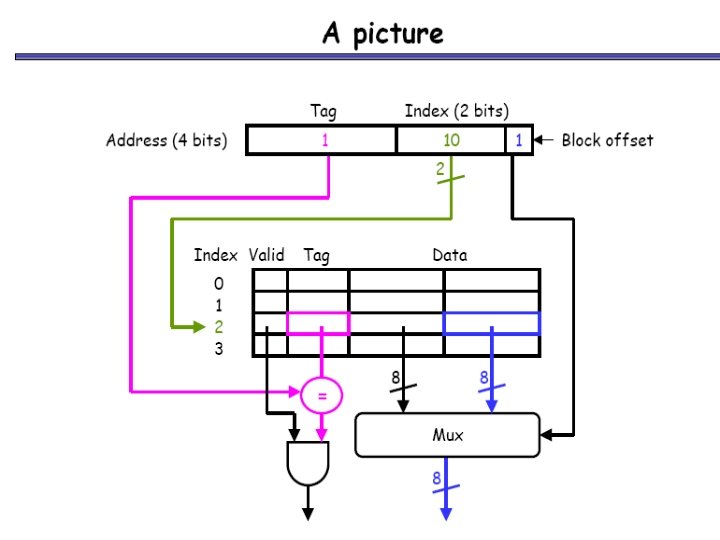

How to find data in the cache

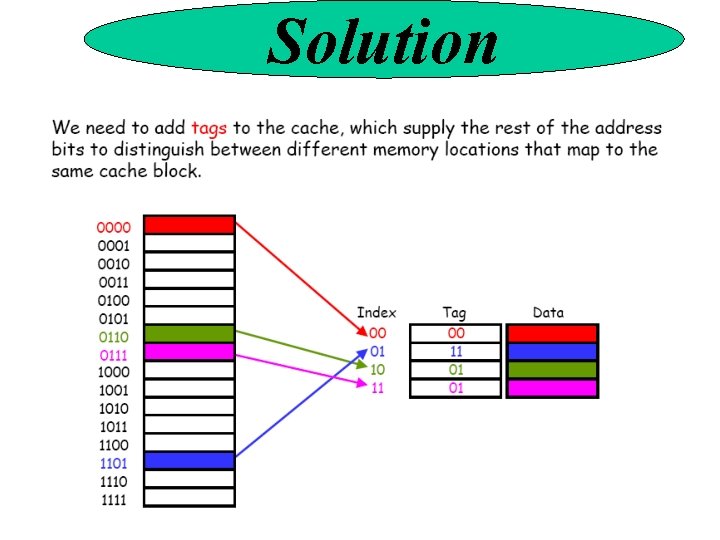

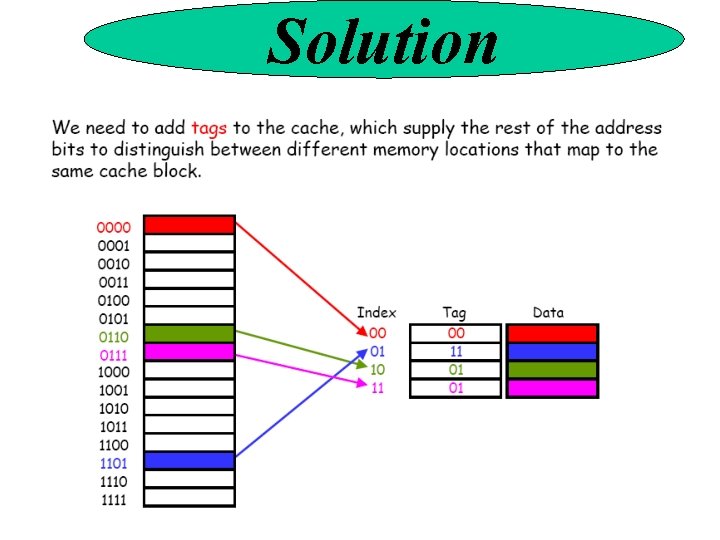

Solution

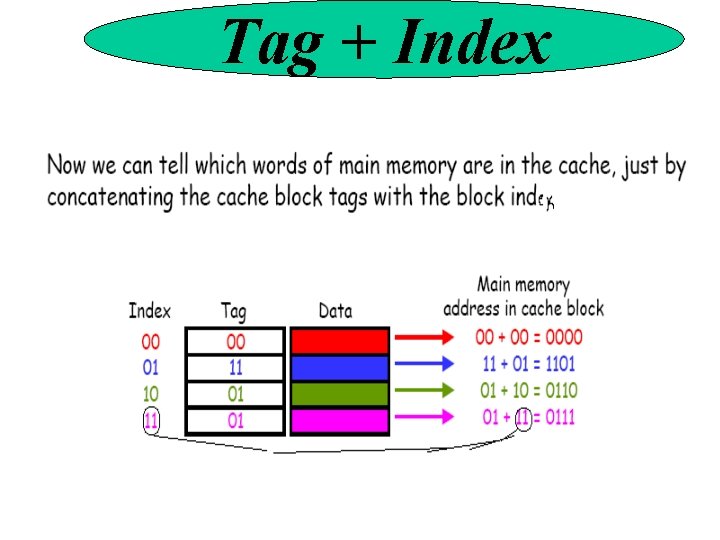

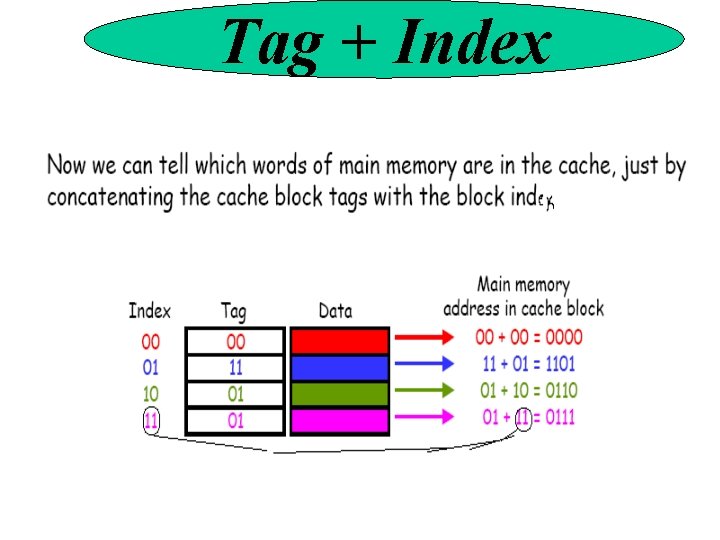

Tag + Index

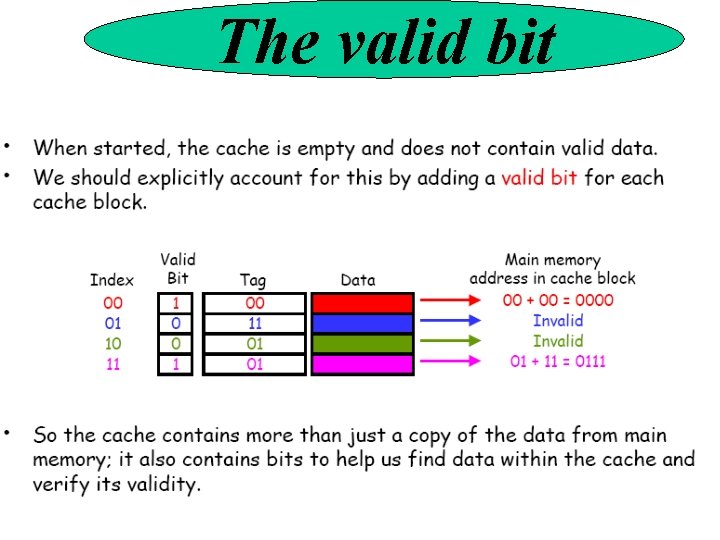

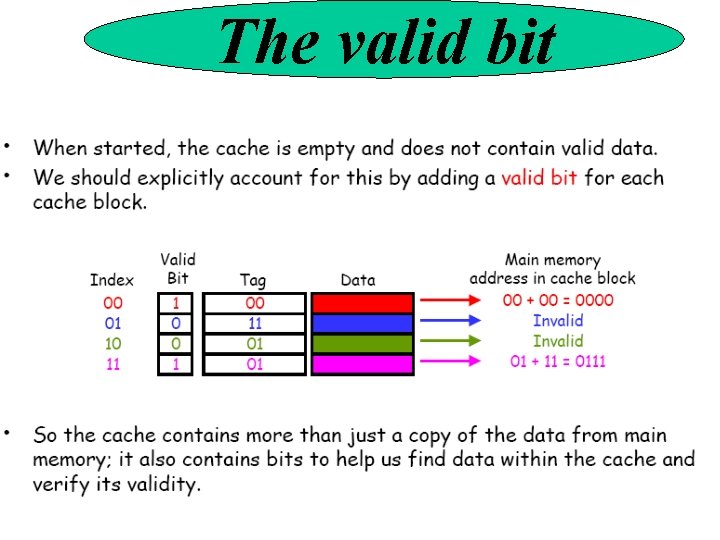

The valid bit

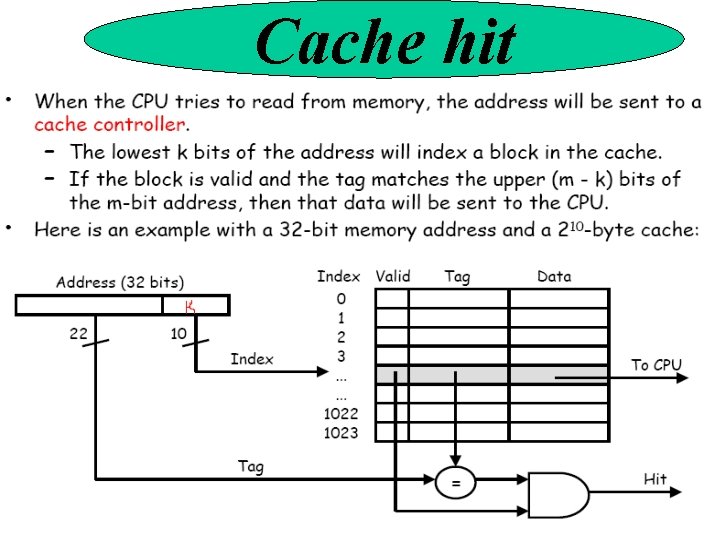

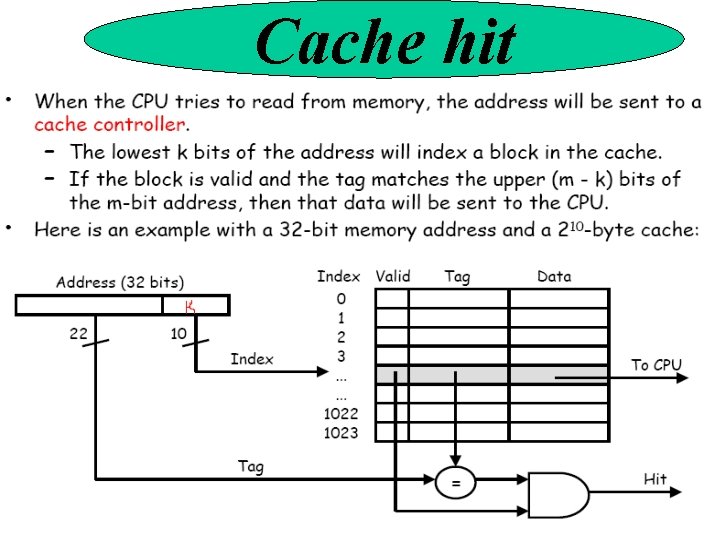

Cache hit

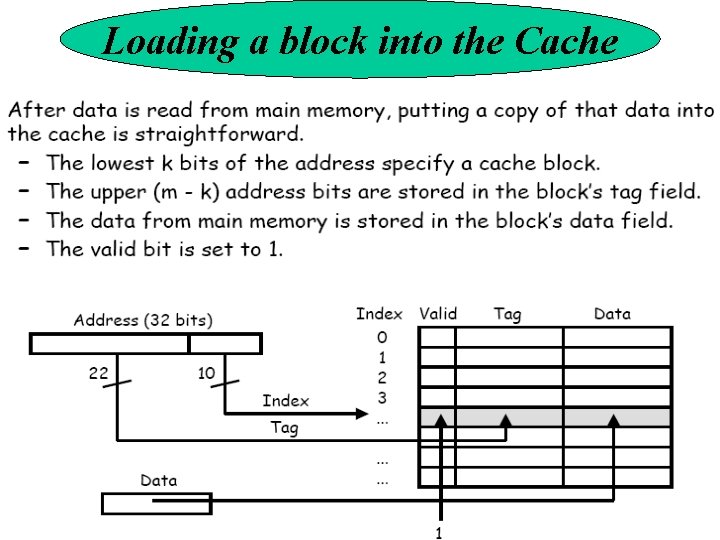

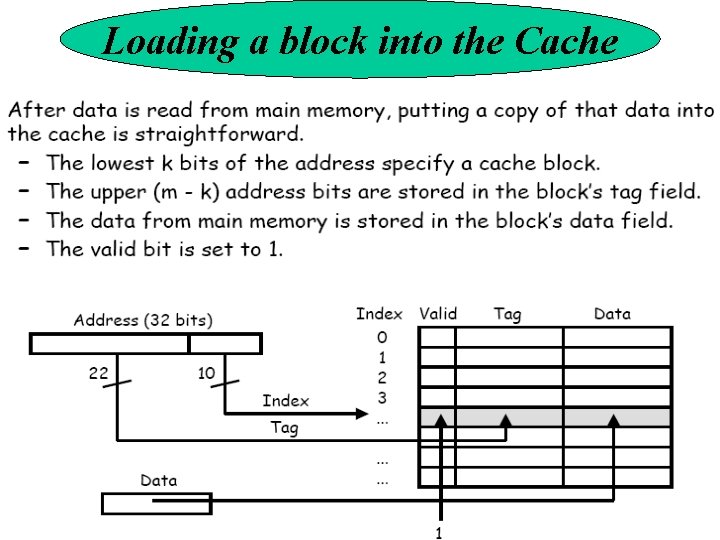

Loading a block into the Cache

Spatial Locality

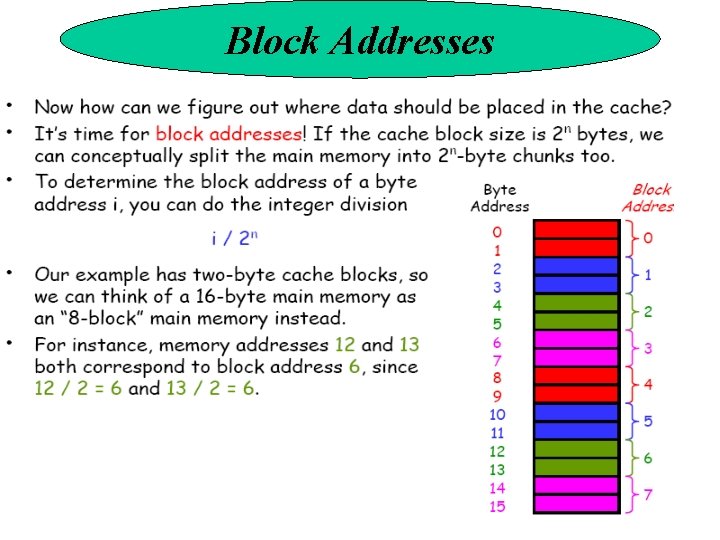

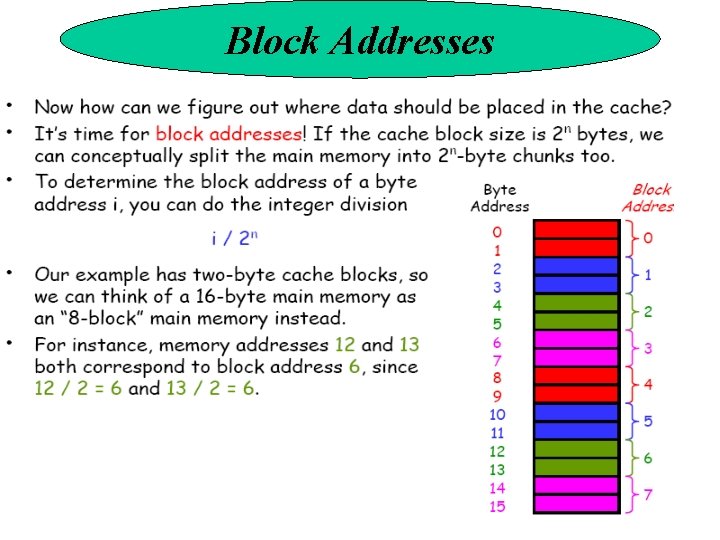

Block Addresses

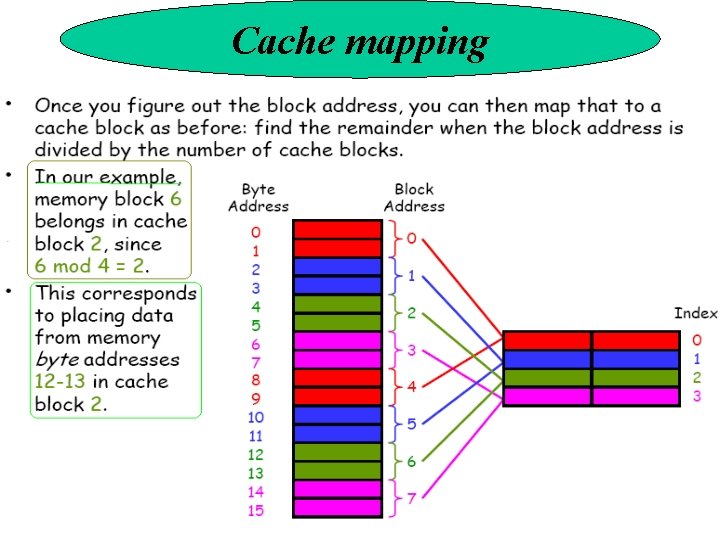

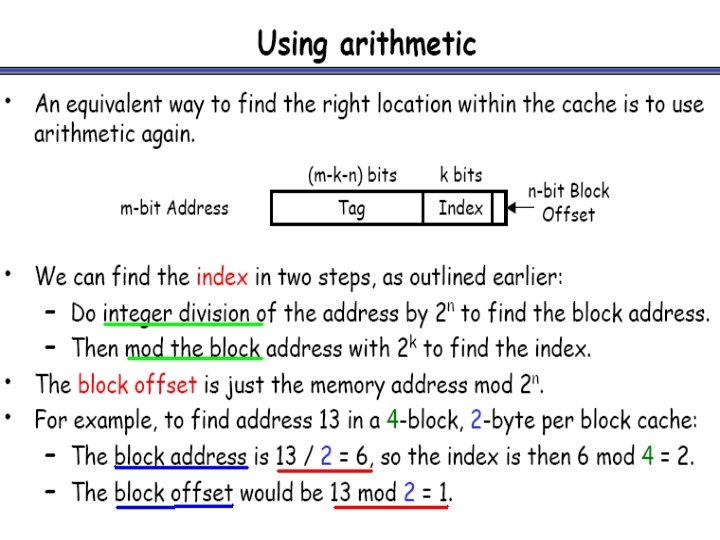

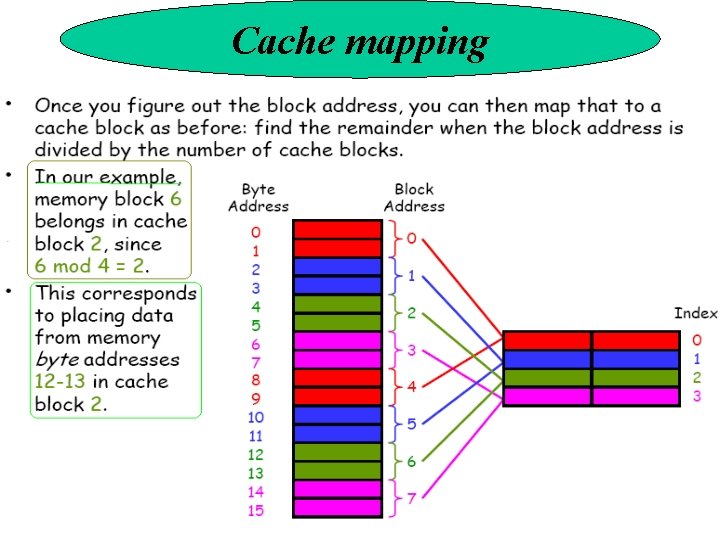

Cache mapping

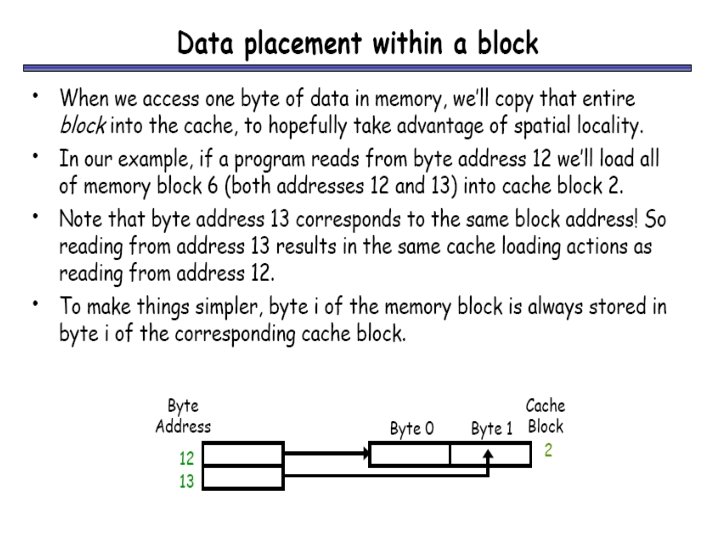

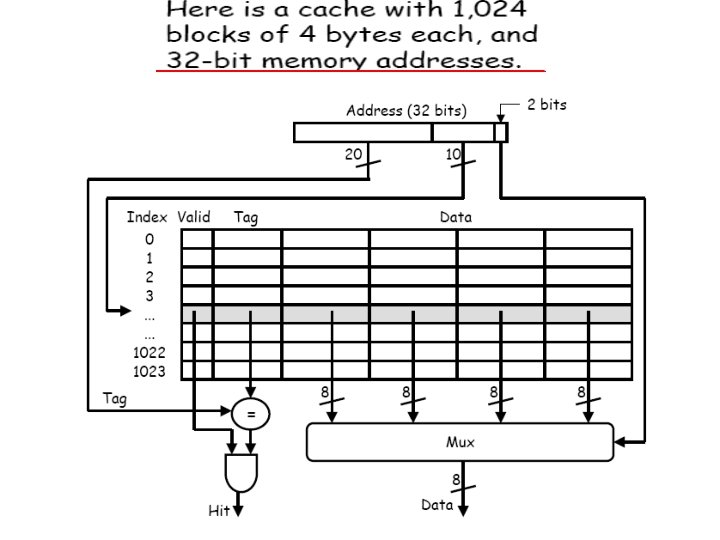

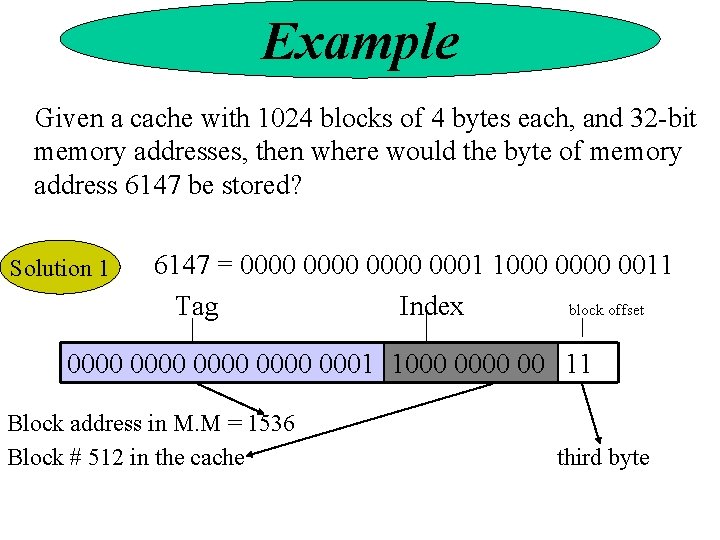

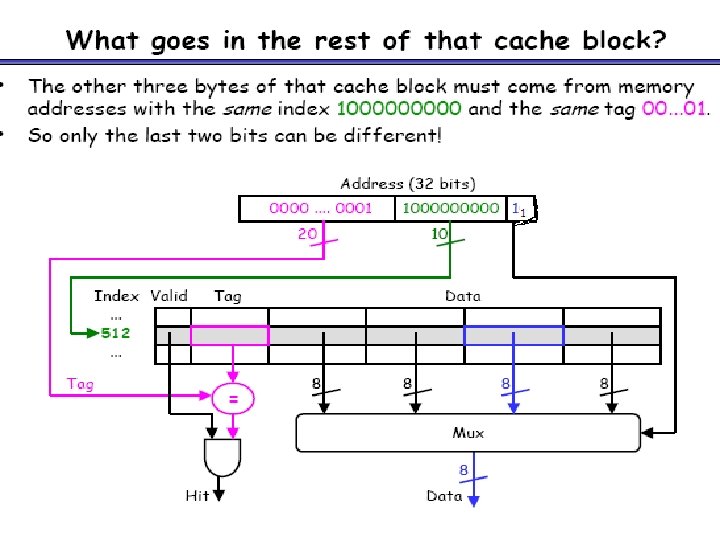

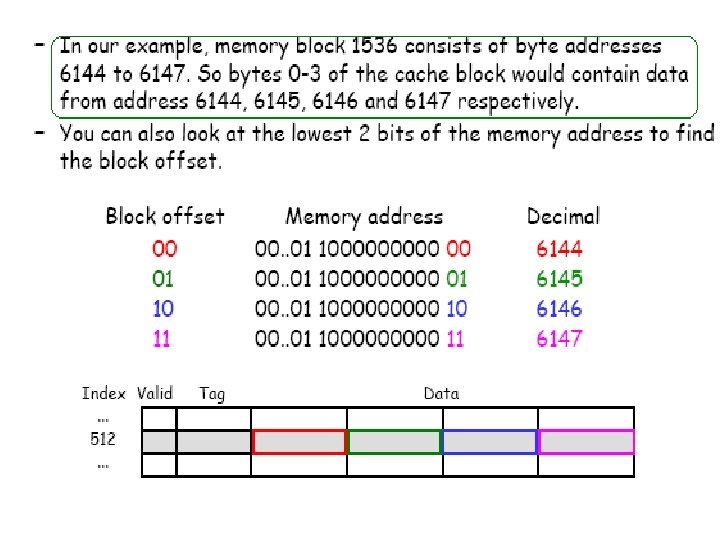

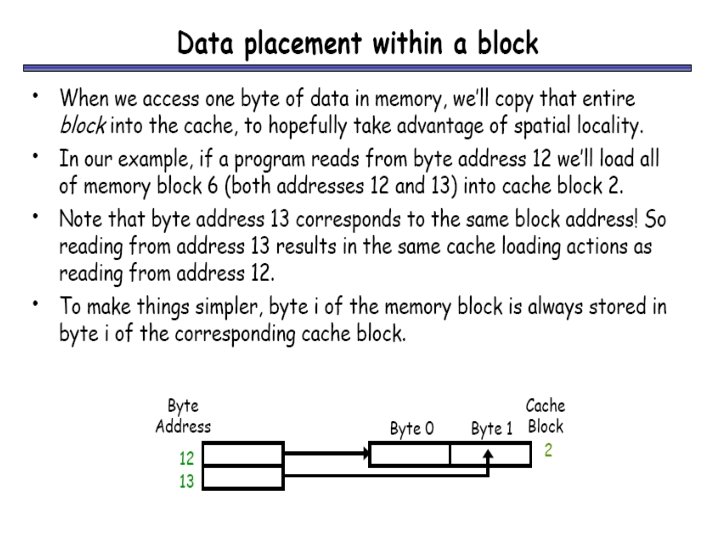

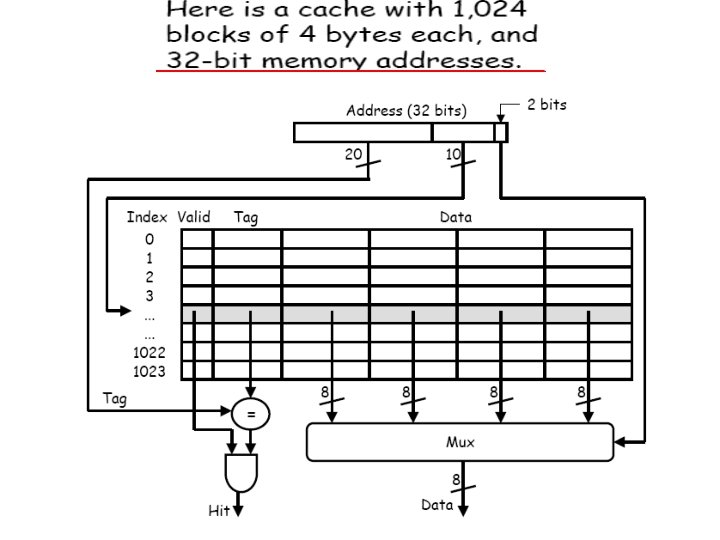

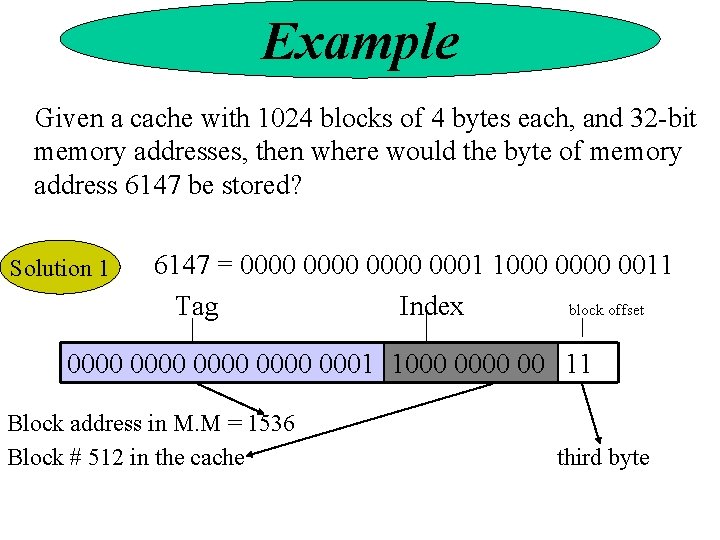

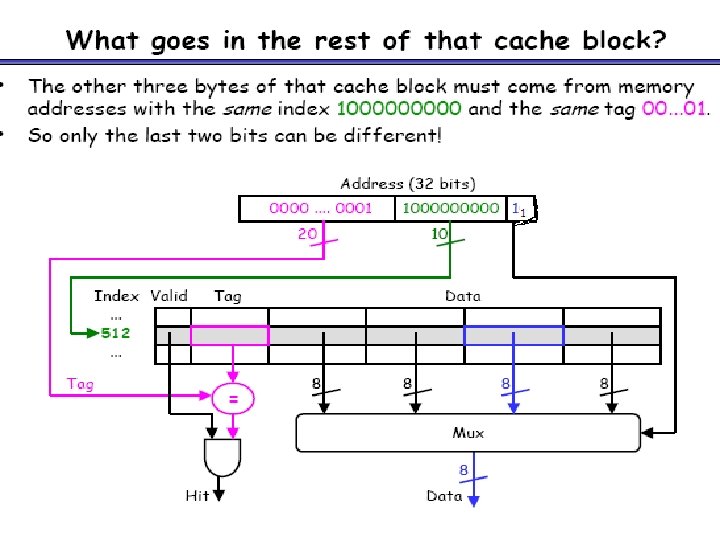

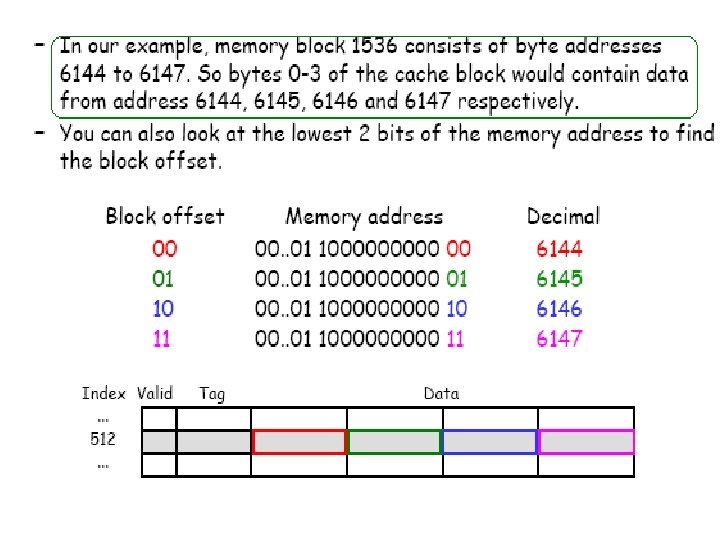

Example Given a cache with 1024 blocks of 4 bytes each, and 32 -bit memory addresses, then where would the byte of memory address 6147 be stored? Solution 1 6147 = 0000 0001 1000 0011 Tag Index block offset 0000 0001 1000 00 11 Block address in M. M = 1536 Block # 512 in the cache third byte

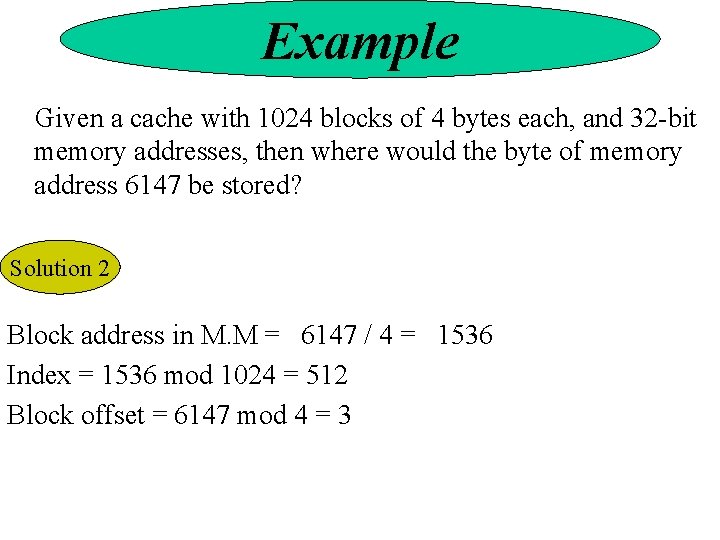

Example Given a cache with 1024 blocks of 4 bytes each, and 32 -bit memory addresses, then where would the byte of memory address 6147 be stored? Solution 2 Block address in M. M = 6147 / 4 = 1536 Index = 1536 mod 1024 = 512 Block offset = 6147 mod 4 = 3

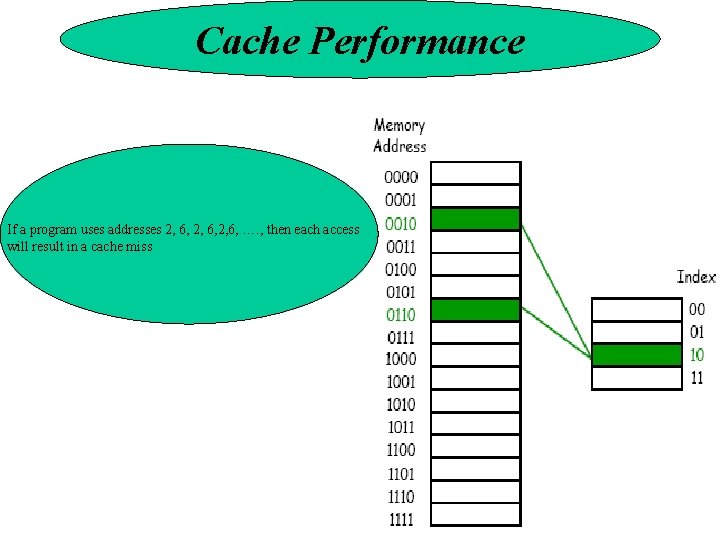

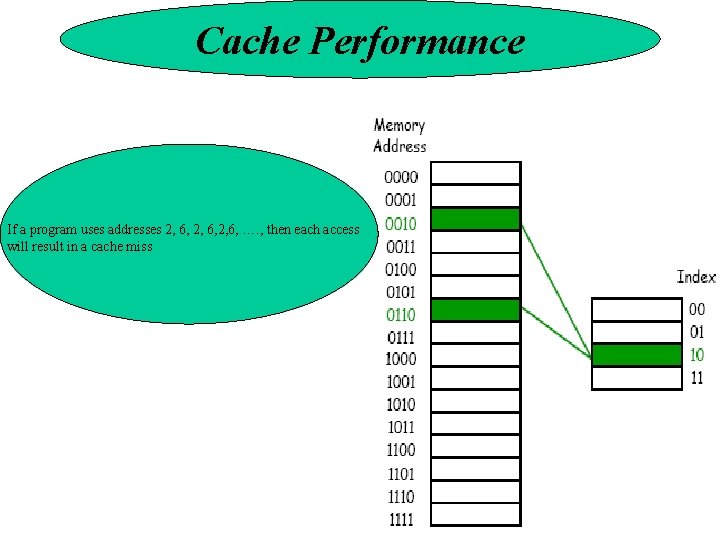

Cache Performance If a program uses addresses 2, 6, …. , then each access will result in a cache miss

Cache Performance

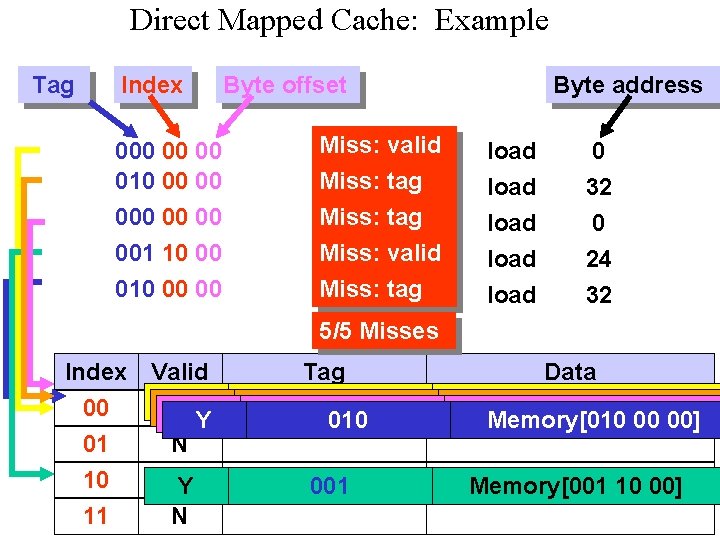

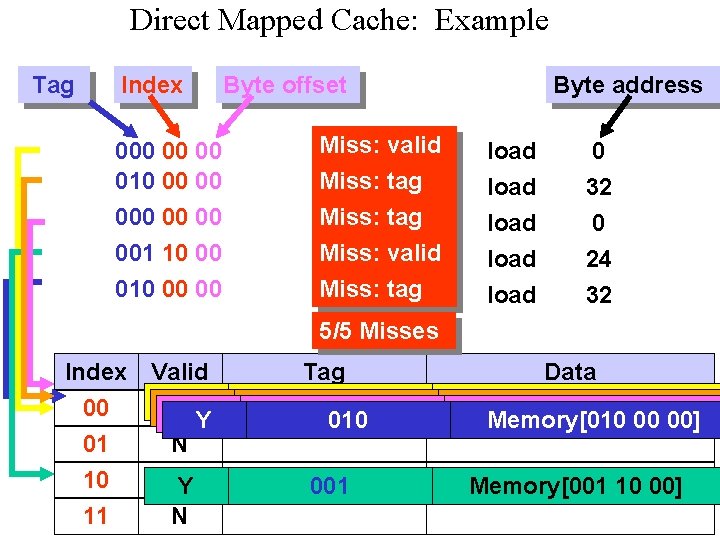

Direct Mapped Cache: Example Tag Index 000 00 00 010 00 00 001 10 00 00 Byte offset Miss: valid Miss: tag Byte address load 0 32 0 load 24 32 5/5 Misses Index 00 01 Valid NYYYY N Tag 000 010 10 11 NY N 001 Data Memory[000 00 00] Memory[010 0000] Memory[001 10 00]

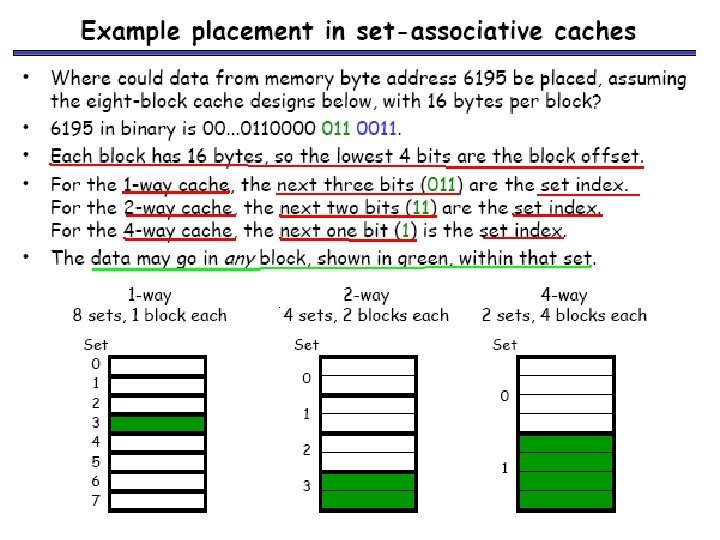

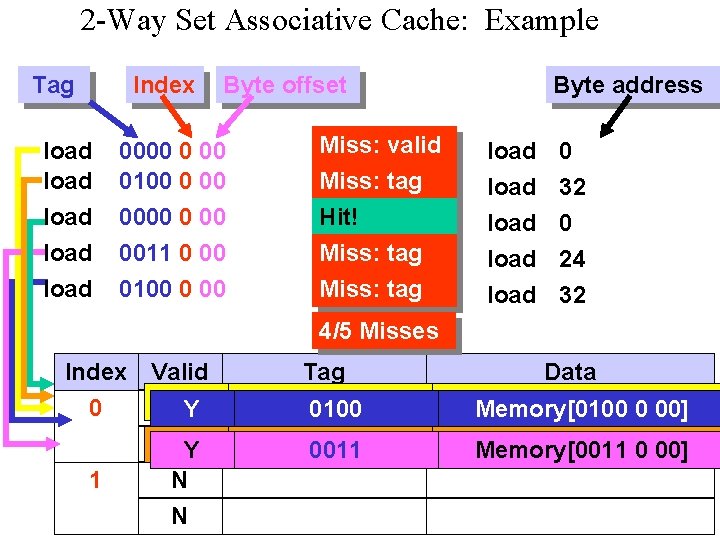

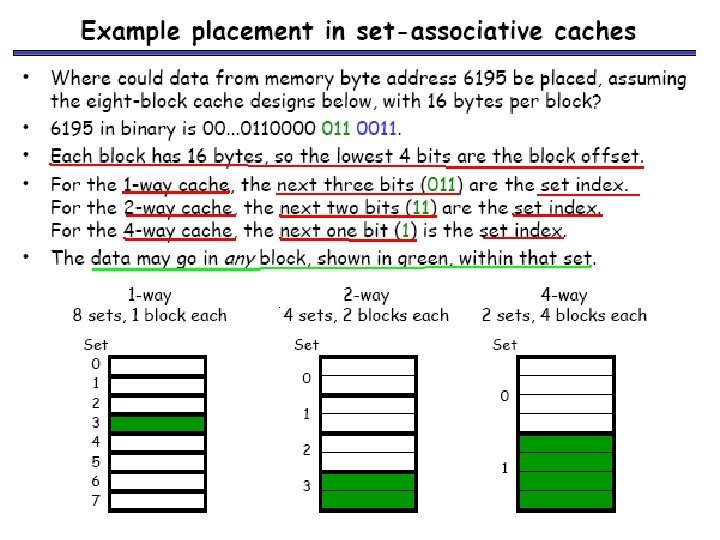

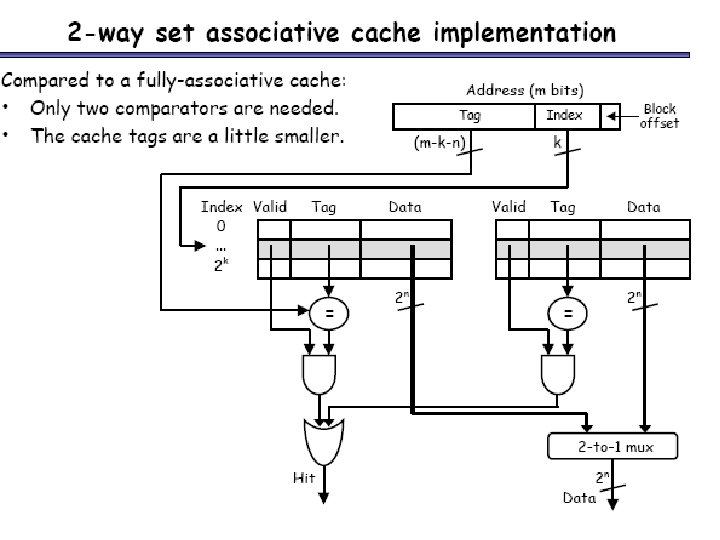

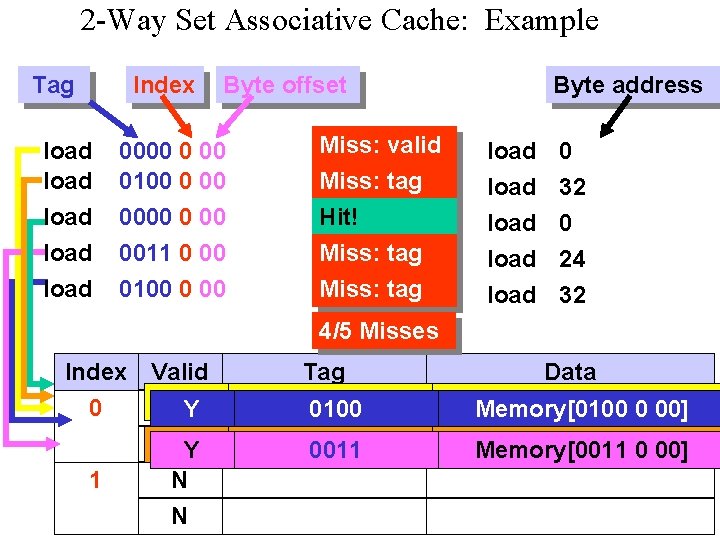

2 -Way Set Associative Cache: Example Tag Index load load Byte offset 0000 0100 0011 0 00 0100 0 00 Miss: valid Miss: tag Hit! Miss: tag Byte address load load 0 32 0 24 32 4/5 Misses Index 0 1 Valid NYY N N Tag 00000 0100 Data Memory[0000 Memory[01000000] 0100 0011 Memory[0100 Memory[00110000]

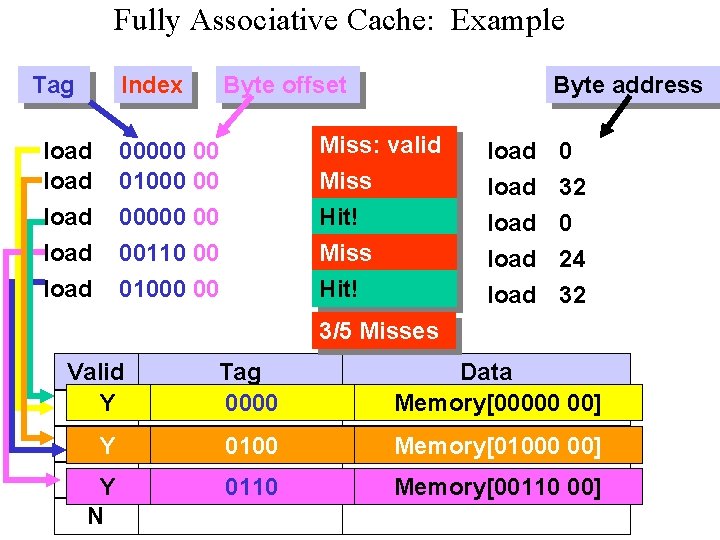

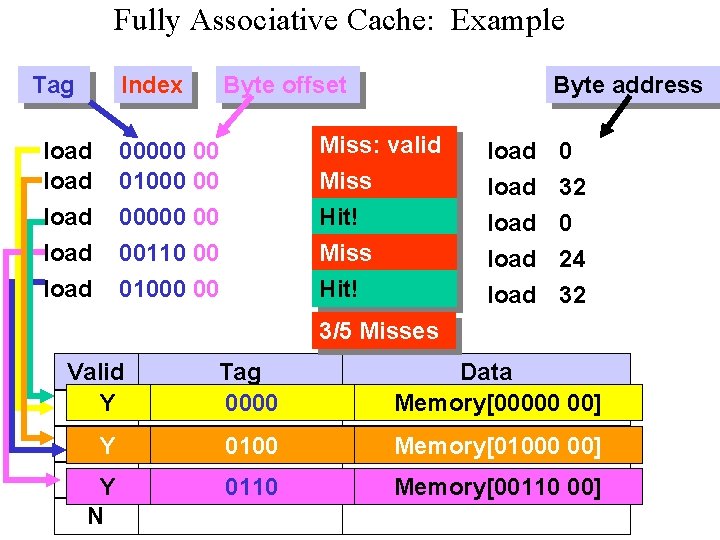

Fully Associative Cache: Example Tag Index load load Byte offset Byte address Miss: valid Miss Hit! 00000 00 01000 00 00110 00 01000 00 load load 0 32 0 24 32 3/5 Misses Valid NY NY Tag 0000 Data Memory[00000 00] 0100 Memory[01000 00] NY N 0110 Memory[00110 00]

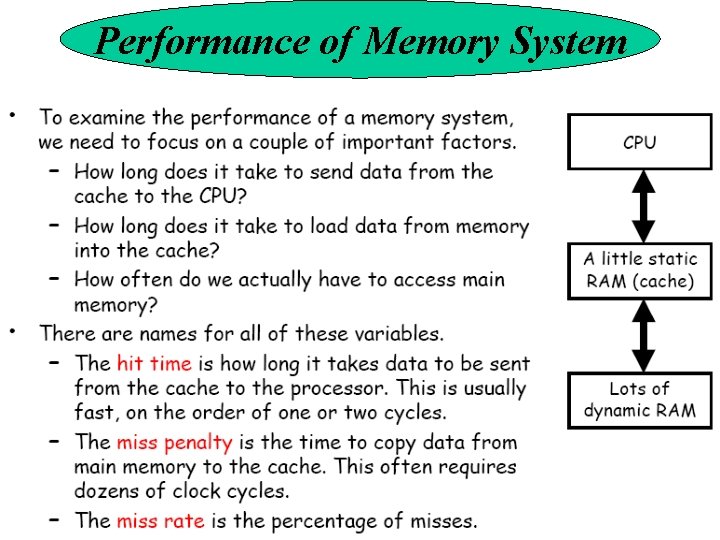

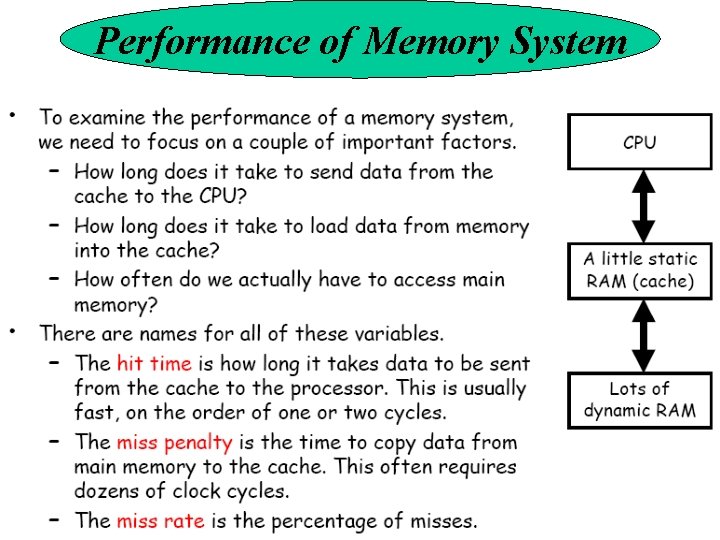

Performance of Memory System