HostMemoryUser Interface Interfacing with the host computer external

- Slides: 17

Host/Memory/User Interface Interfacing with the host computer, external memory, and user

ESU: Extended Parallel Port, Smart Media Card, and User Interfaces

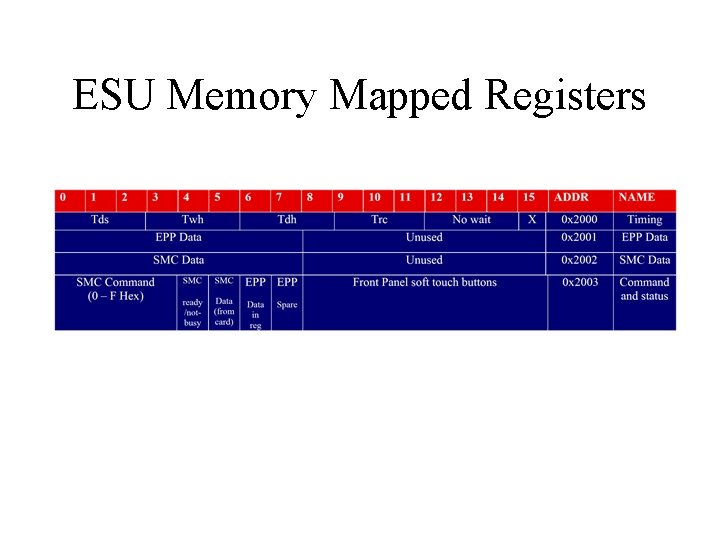

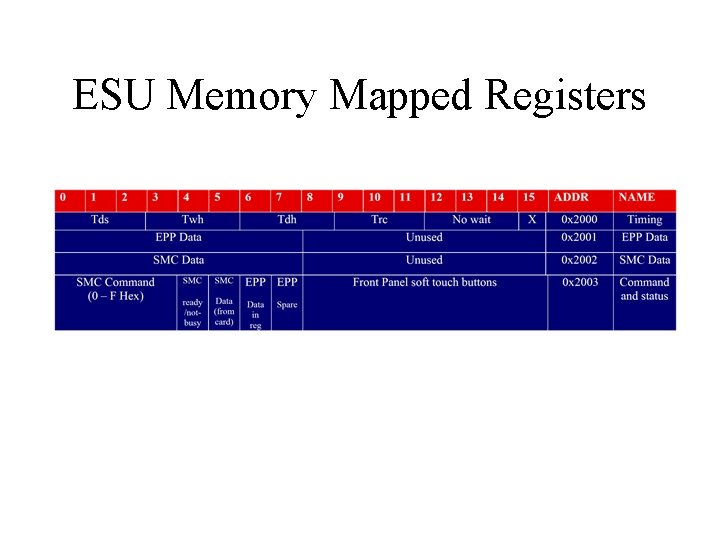

ESU Memory Mapped Registers

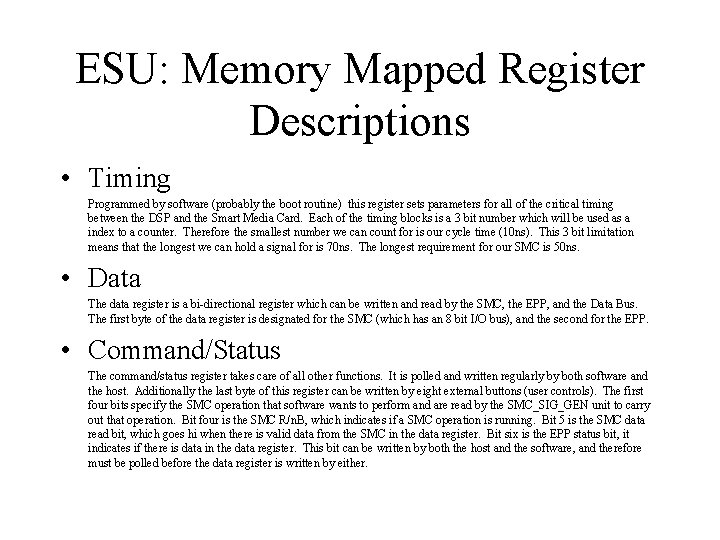

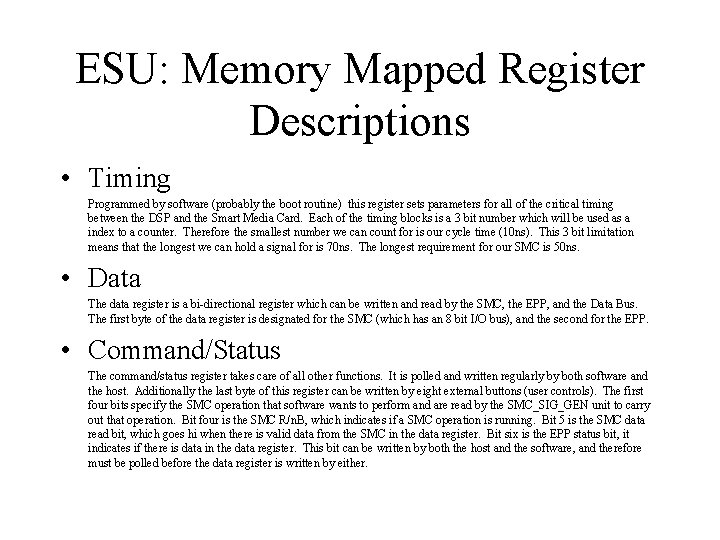

ESU: Memory Mapped Register Descriptions • Timing Programmed by software (probably the boot routine) this register sets parameters for all of the critical timing between the DSP and the Smart Media Card. Each of the timing blocks is a 3 bit number which will be used as a index to a counter. Therefore the smallest number we can count for is our cycle time (10 ns). This 3 bit limitation means that the longest we can hold a signal for is 70 ns. The longest requirement for our SMC is 50 ns. • Data The data register is a bi-directional register which can be written and read by the SMC, the EPP, and the Data Bus. The first byte of the data register is designated for the SMC (which has an 8 bit I/O bus), and the second for the EPP. • Command/Status The command/status register takes care of all other functions. It is polled and written regularly by both software and the host. Additionally the last byte of this register can be written by eight external buttons (user controls). The first four bits specify the SMC operation that software wants to perform and are read by the SMC_SIG_GEN unit to carry out that operation. Bit four is the SMC R/n. B, which indicates if a SMC operation is running. Bit 5 is the SMC data read bit, which goes hi when there is valid data from the SMC in the data register. Bit six is the EPP status bit, it indicates if there is data in the data register. This bit can be written by both the host and the software, and therefore must be polled before the data register is written by either.

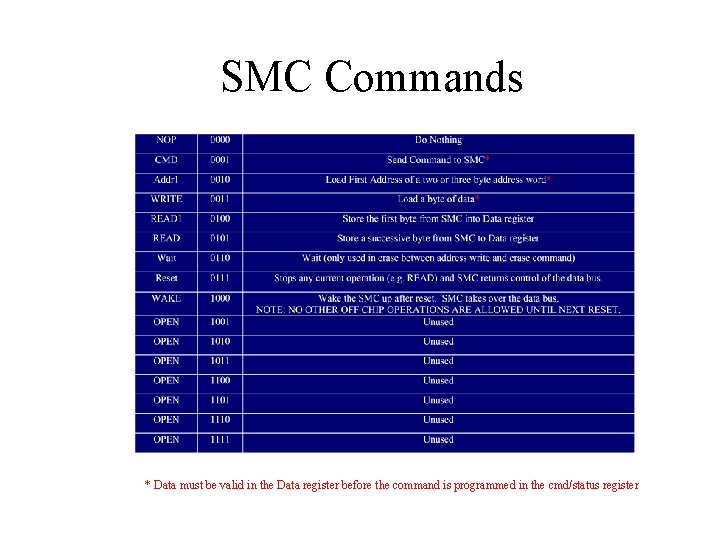

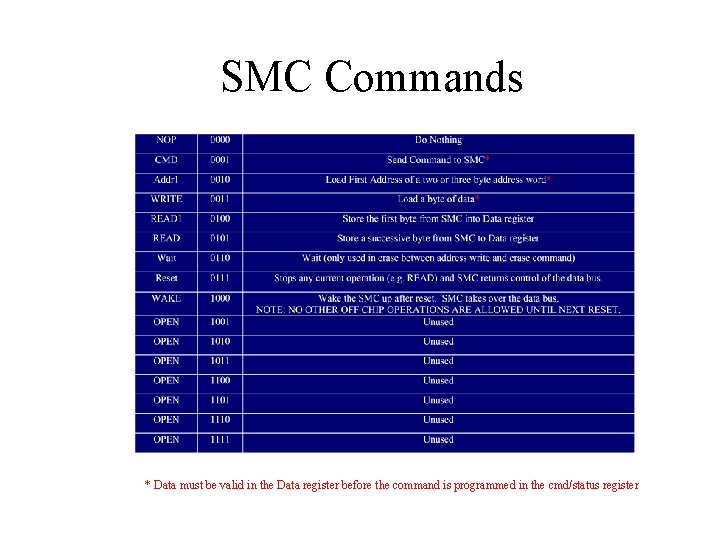

SMC Commands * Data must be valid in the Data register before the command is programmed in the cmd/status register

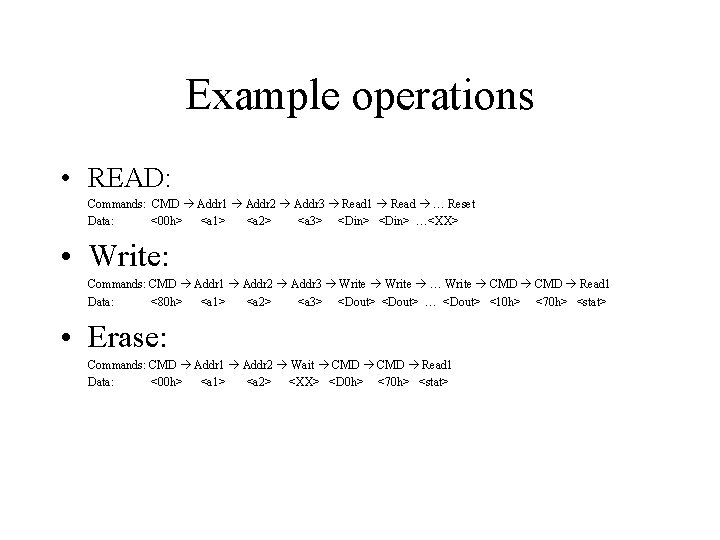

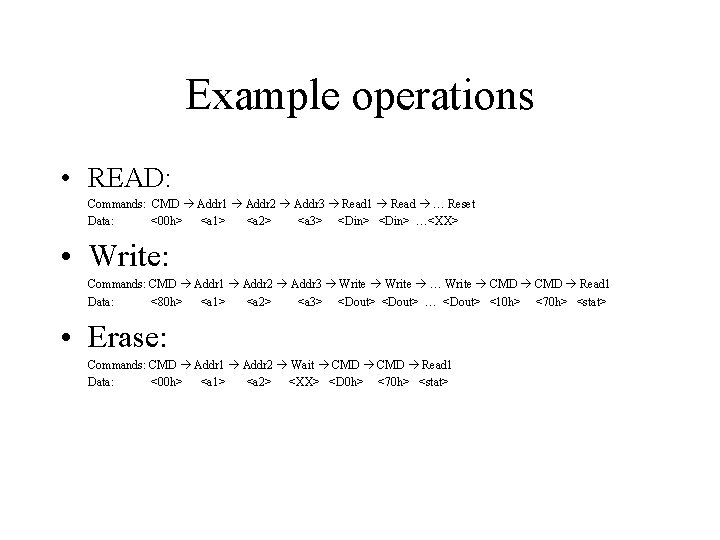

Example operations • READ: Commands: CMD Addr 1 Addr 2 Addr 3 Read 1 Read … Reset Data: <00 h> <a 1> <a 2> <a 3> <Din> …<XX> • Write: Commands: CMD Addr 1 Addr 2 Addr 3 Write … Write CMD Read 1 Data: <80 h> <a 1> <a 2> <a 3> <Dout> … <Dout> <10 h> <70 h> <stat> • Erase: Commands: CMD Addr 1 Addr 2 Wait CMD Read 1 Data: <00 h> <a 1> <a 2> <XX> <D 0 h> <70 h> <stat>

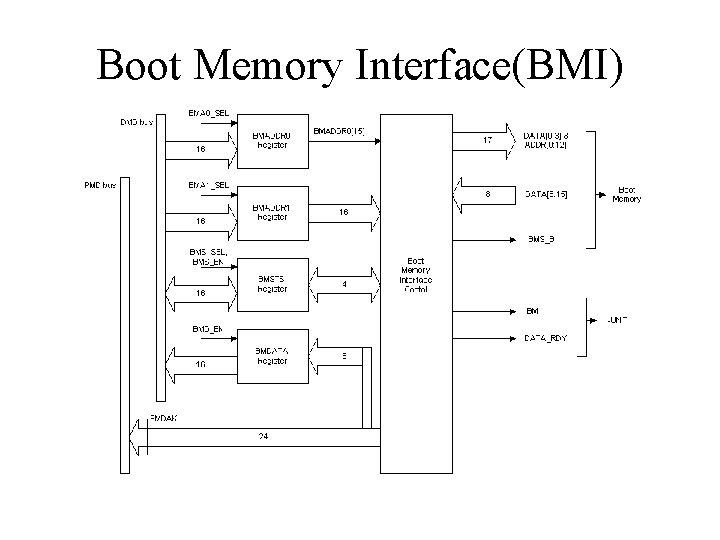

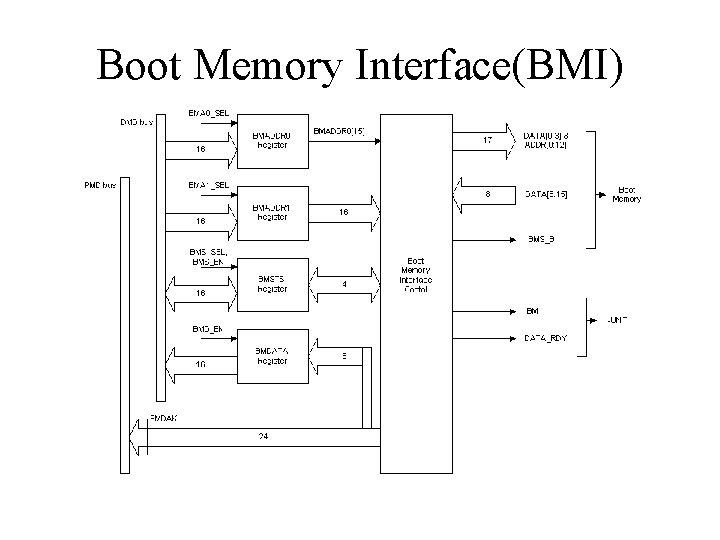

Boot Memory Interface(BMI)

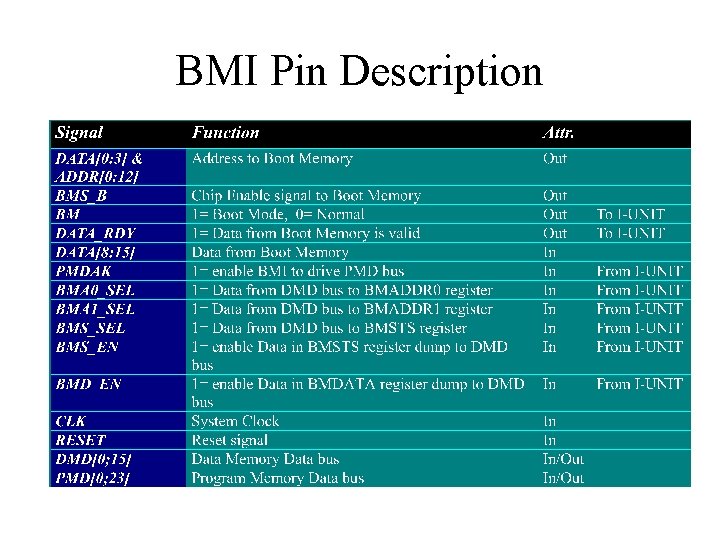

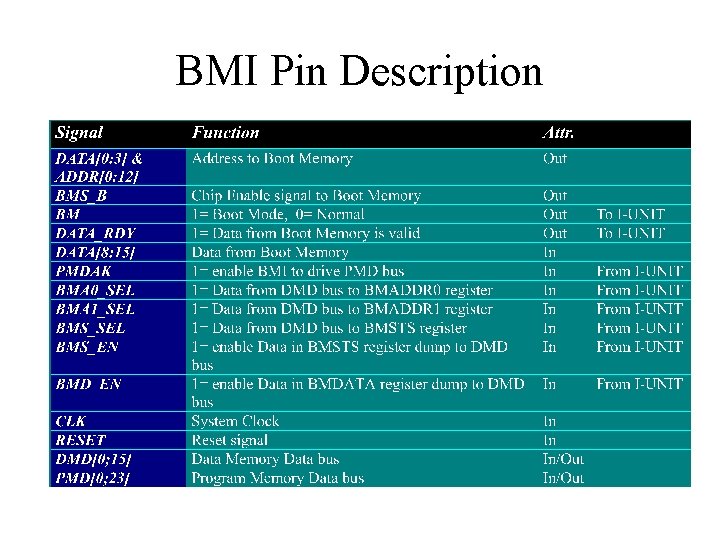

BMI Pin Description

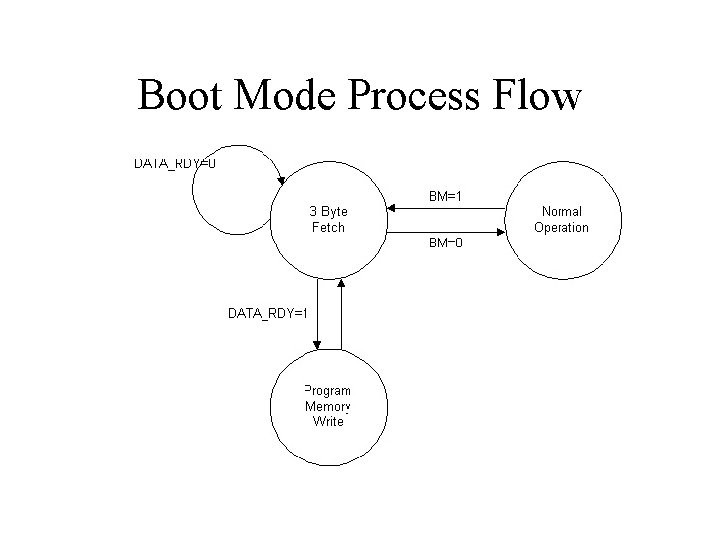

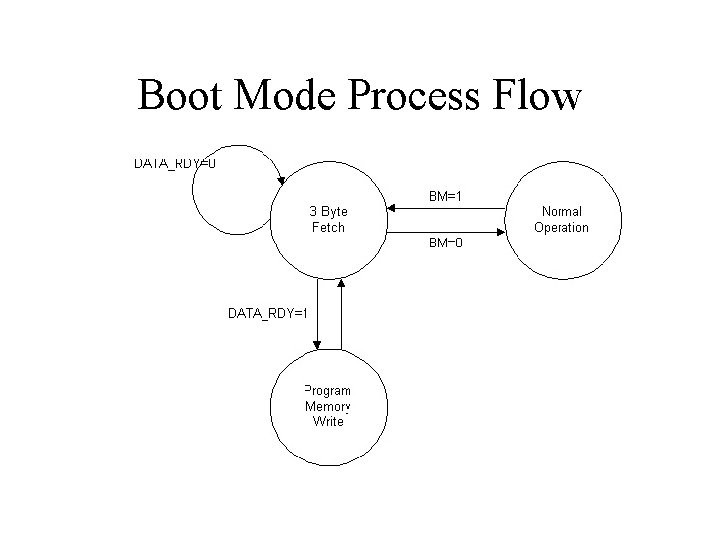

Boot Mode Process Flow

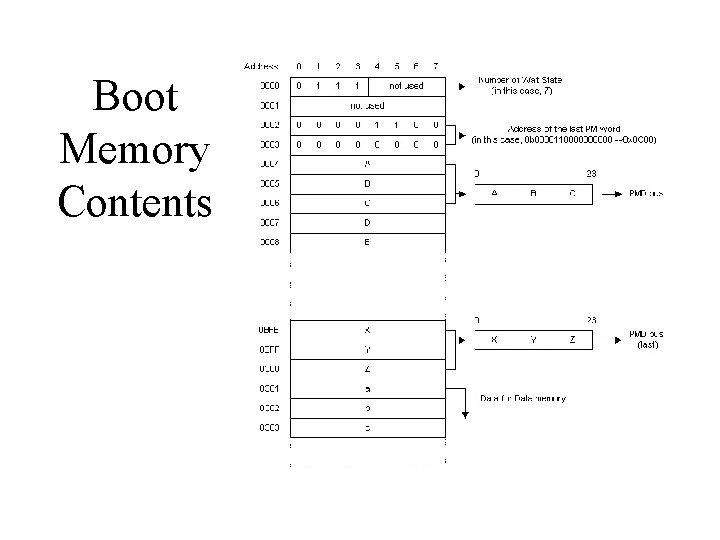

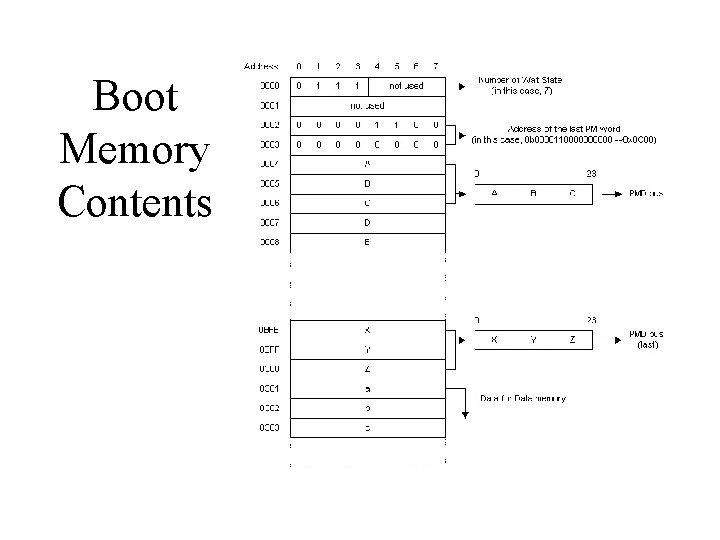

Boot Memory Contents

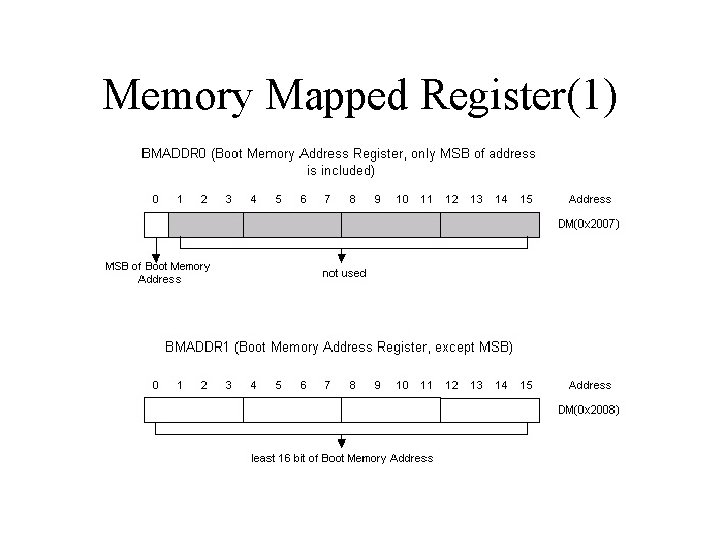

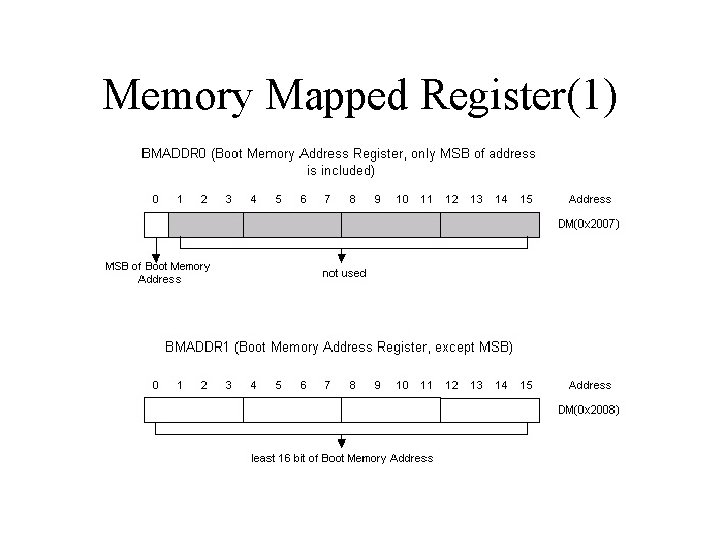

Memory Mapped Register(1)

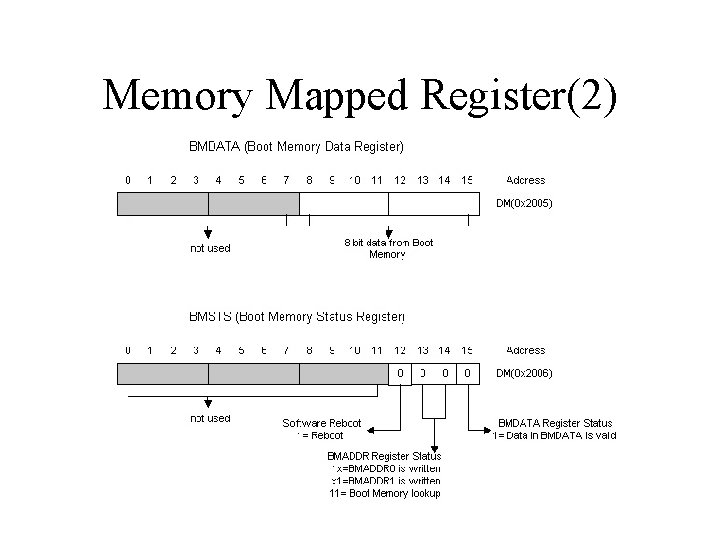

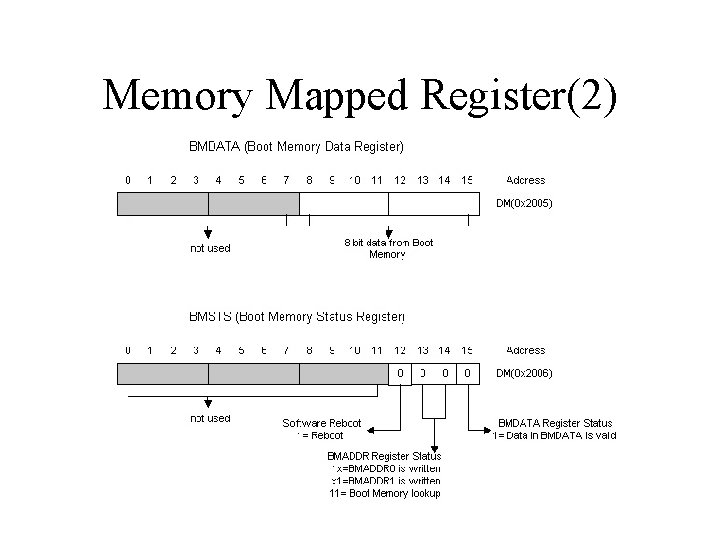

Memory Mapped Register(2)

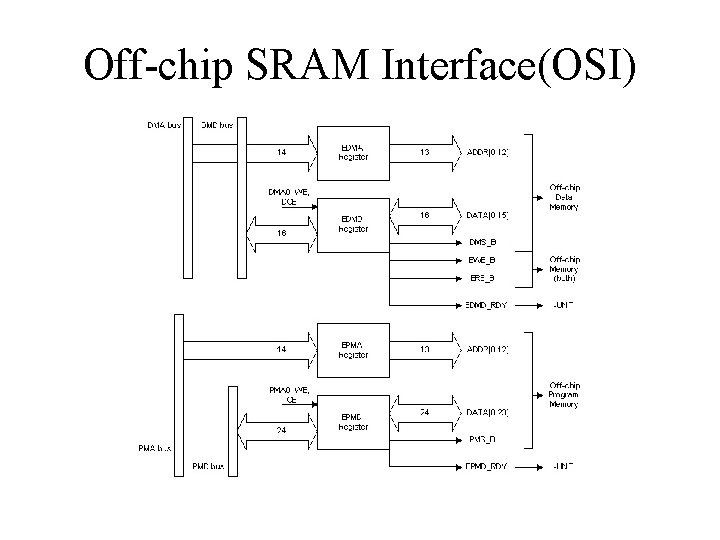

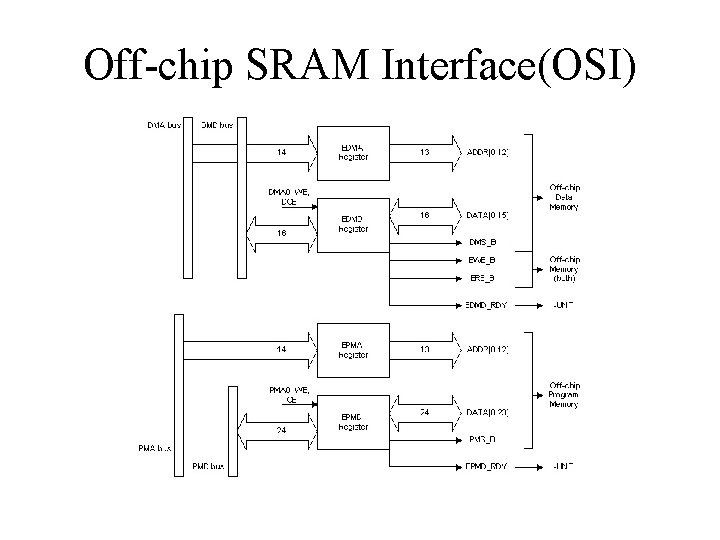

Off-chip SRAM Interface(OSI)

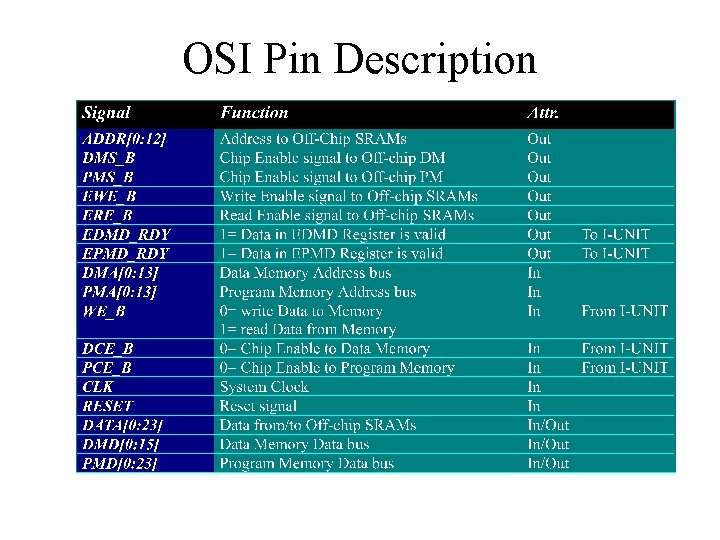

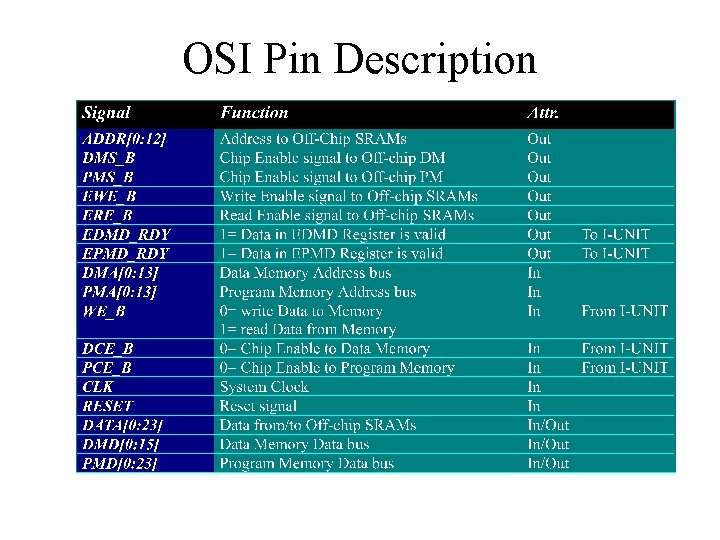

OSI Pin Description

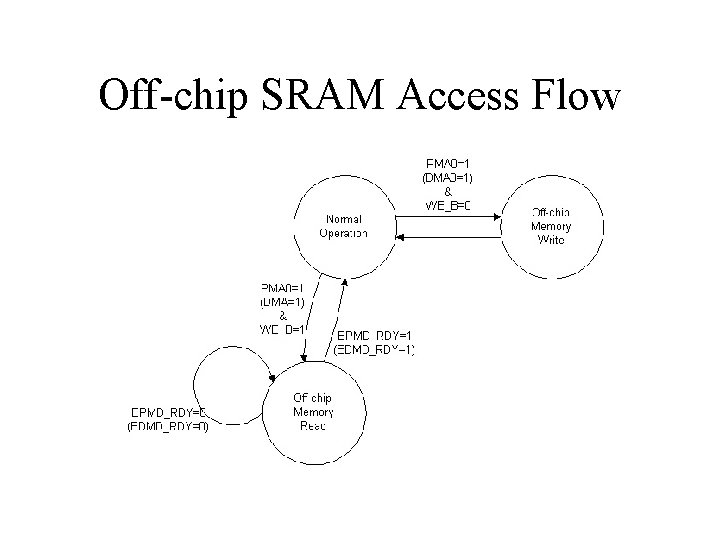

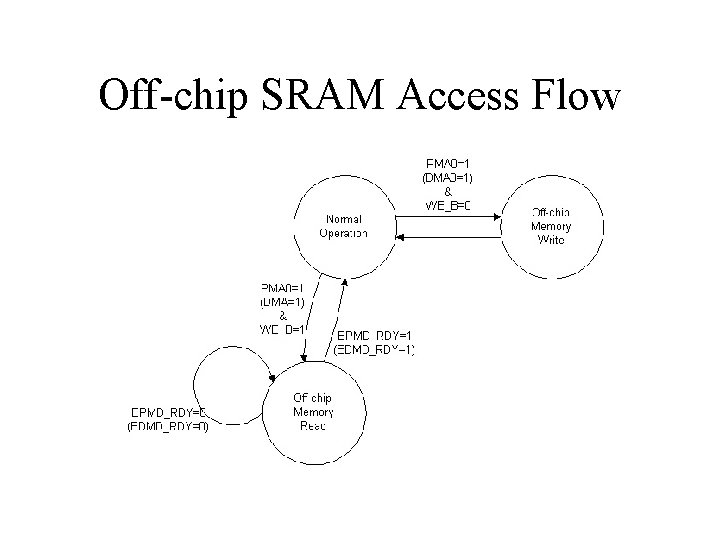

Off-chip SRAM Access Flow

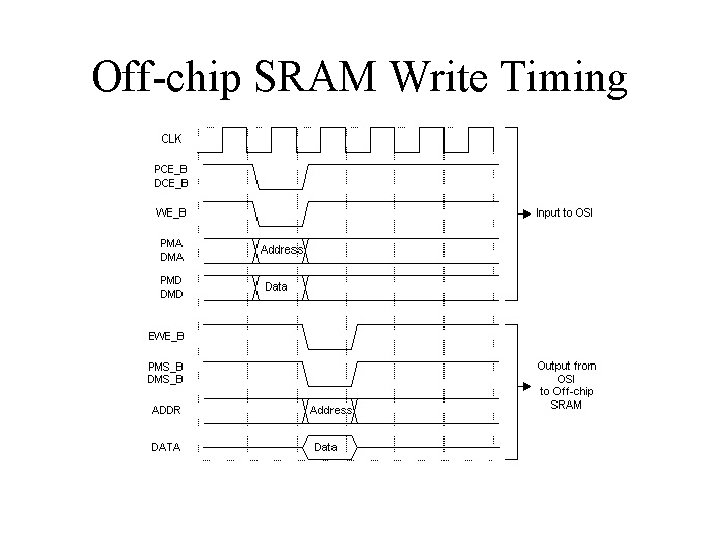

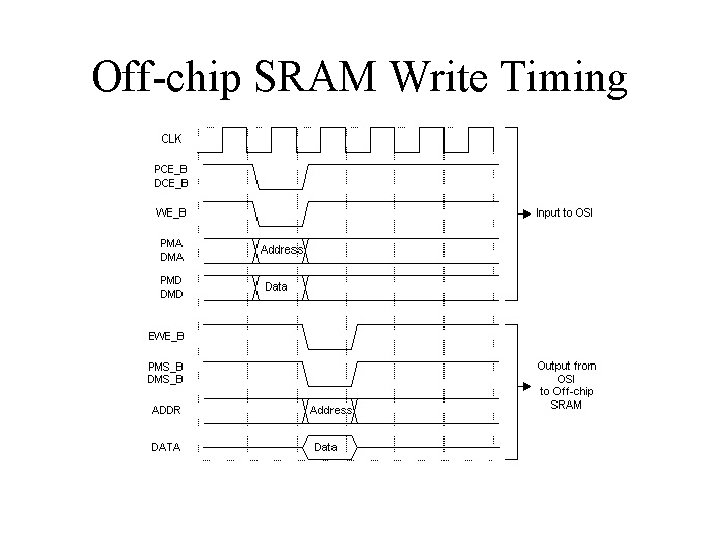

Off-chip SRAM Write Timing

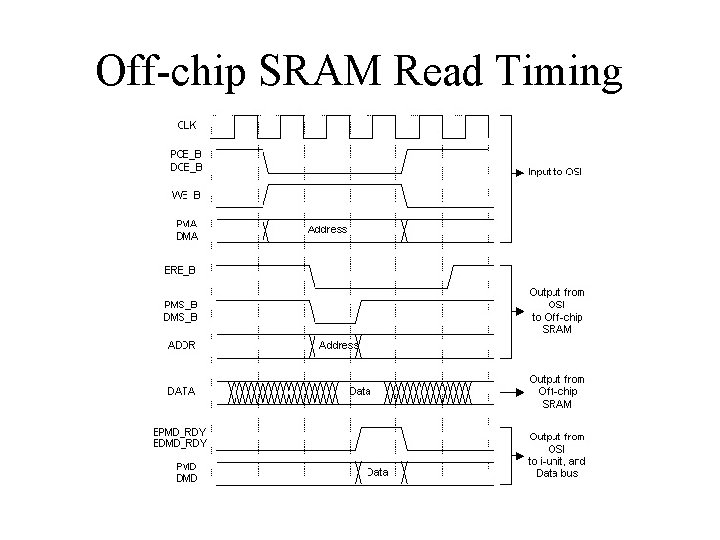

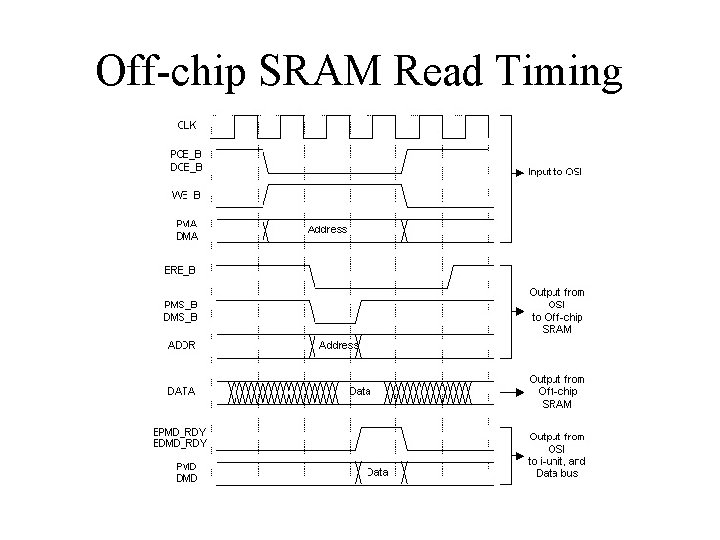

Off-chip SRAM Read Timing