Host Port Interface Expansion Bus Chapter 16 C

Host Port Interface Expansion Bus Chapter 16 C 6000 Integration Workshop T TO Technical Training Organization Copyright © 2005 Texas Instruments. All rights reserved.

Objectives T TO Technical Training Organization HPI Overview HPI on the DSK Host Software Example HPI Hardware Description Optional Discussions

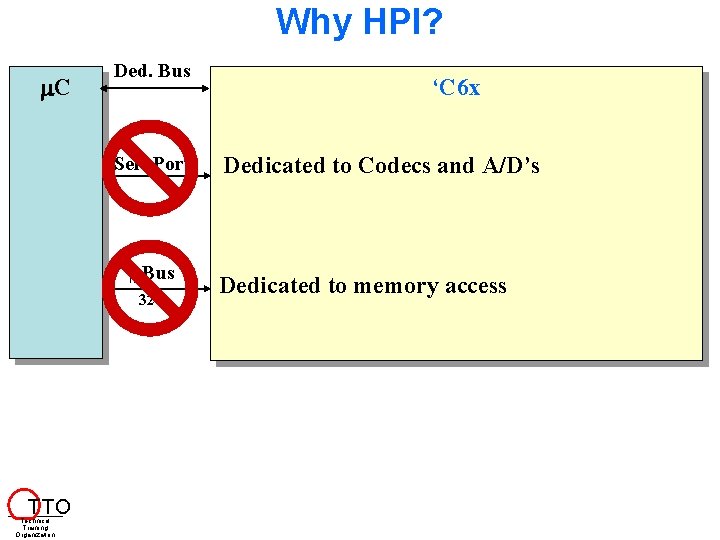

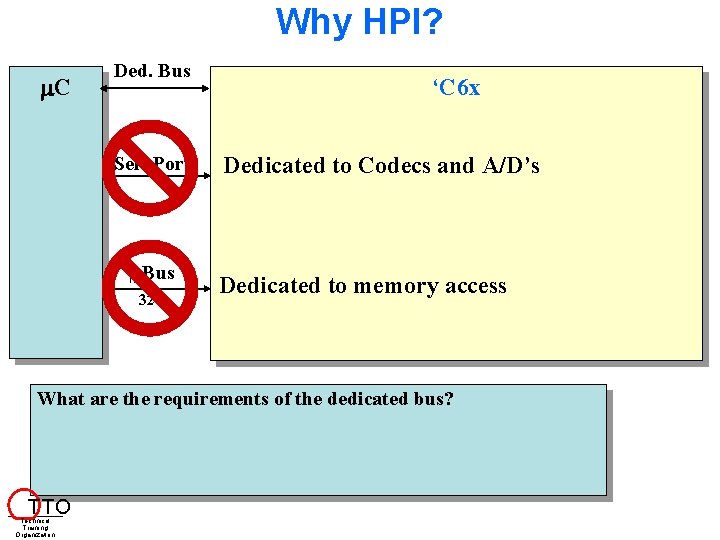

Why HPI? C Ded. Bus Ser. Port || Bus 32 T TO Technical Training Organization ‘C 6 x Dedicated to Codecs and A/D’s Dedicated to memory access

Why HPI for Communication? T TO Technical Training Organization Give host control of the transfer Allow host to access the entire C 6000 memory map Additional parallel bus for data exchange between a host and the C 6000 Provide glueless interface to many different types of hosts

Why HPI? C Ded. Bus Ser. Port || Bus 32 ‘C 6 x Dedicated to Codecs and A/D’s Dedicated to memory access What are the requirements of the dedicated bus? T TO Technical Training Organization

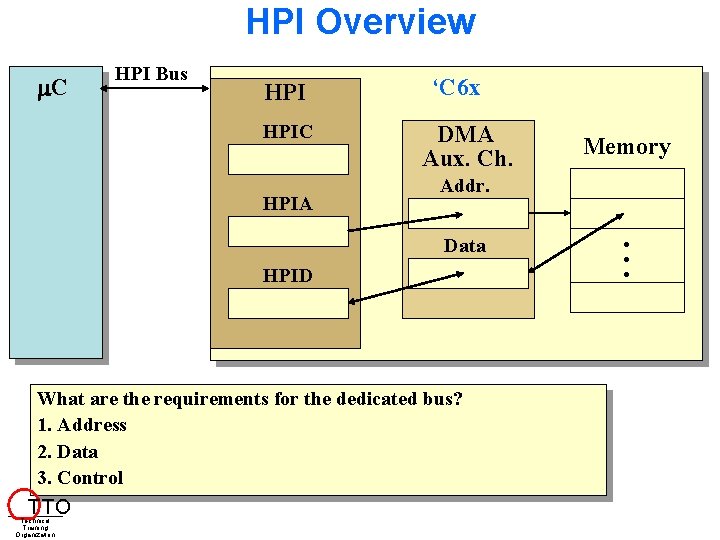

HPI Overview C HPI Bus HPIC HPIA ‘C 6 x DMA Aux. Ch. Addr. Data HPID What are the requirements for the dedicated bus? 1. Address 2. Data 3. Control T TO Technical Training Organization Memory . . .

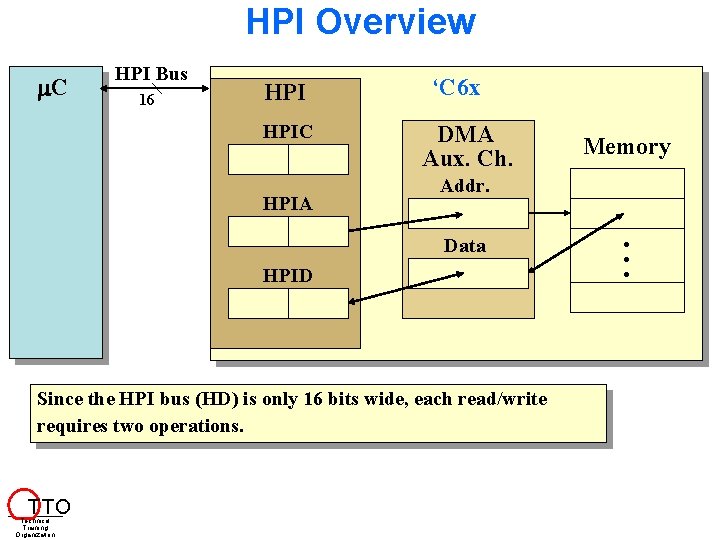

HPI Overview C HPI Bus 16 HPIC HPIA ‘C 6 x DMA Aux. Ch. Addr. Data HPID Since the HPI bus (HD) is only 16 bits wide, each read/write requires two operations. T TO Technical Training Organization Memory . . .

Objectives HPI Overview T TO Technical Training Organization HPI on the DSK Host Software Example HPI Hardware Description Optional Discussions

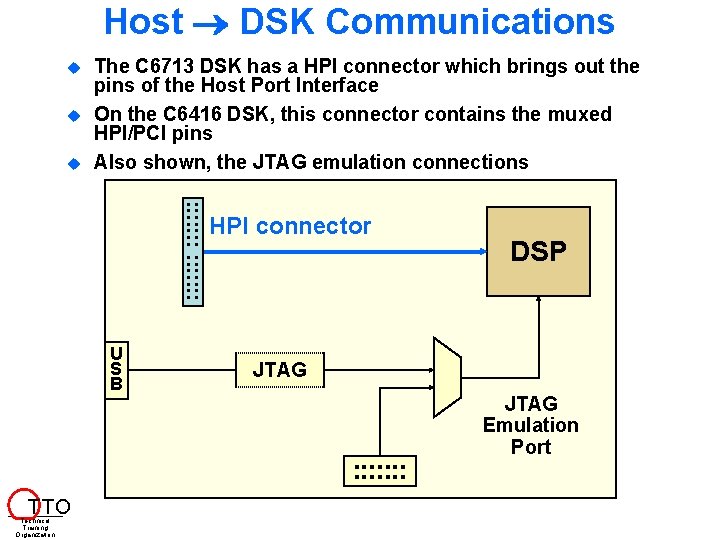

Host DSK Communications The C 6713 DSK has a HPI connector which brings out the pins of the Host Port Interface On the C 6416 DSK, this connector contains the muxed HPI/PCI pins Also shown, the JTAG emulation connections . . . . HPI connector U S B JTAG . . . T TO Technical Training Organization DSP JTAG Emulation Port

Objectives HPI Overview HPI on the DSK T TO Technical Training Organization Host Software Example HPI Hardware Description Optional Discussions

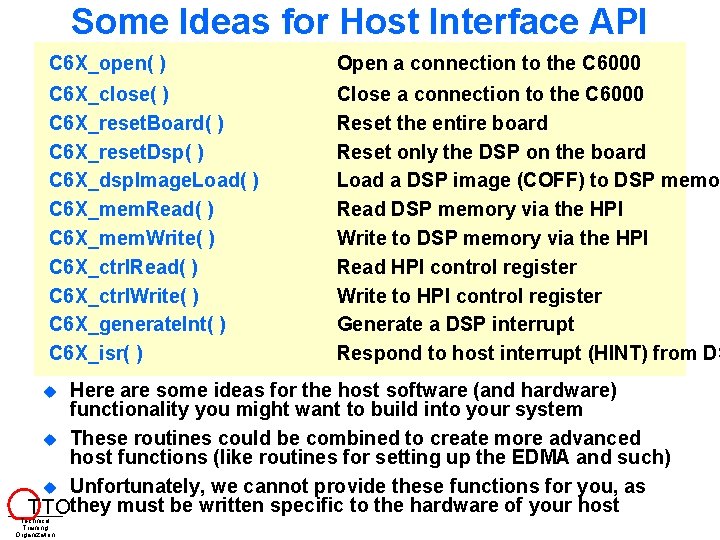

Some Ideas for Host Interface API C 6 X_open( ) Open a connection to the C 6000 C 6 X_close( ) C 6 X_reset. Board( ) C 6 X_reset. Dsp( ) C 6 X_dsp. Image. Load( ) C 6 X_mem. Read( ) C 6 X_mem. Write( ) C 6 X_ctrl. Read( ) C 6 X_ctrl. Write( ) C 6 X_generate. Int( ) C 6 X_isr( ) Close a connection to the C 6000 Reset the entire board Reset only the DSP on the board Load a DSP image (COFF) to DSP memor Read DSP memory via the HPI Write to DSP memory via the HPI Read HPI control register Write to HPI control register Generate a DSP interrupt Respond to host interrupt (HINT) from DS Here are some ideas for the host software (and hardware) functionality you might want to build into your system These routines could be combined to create more advanced host functions (like routines for setting up the EDMA and such) Unfortunately, we cannot provide these functions for you, as T TOthey must be written specific to the hardware of your host Technical Training Organization

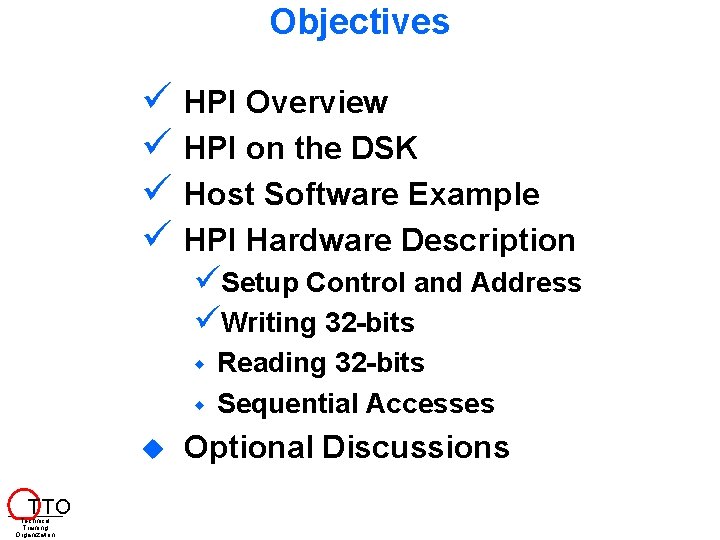

Objectives HPI Overview HPI on the DSK Host Software Example HPI Hardware Description w w T TO Technical Training Organization Setup Control and Address Writing 32 -bits Reading 32 -bits Sequential Accesses Optional Discussions

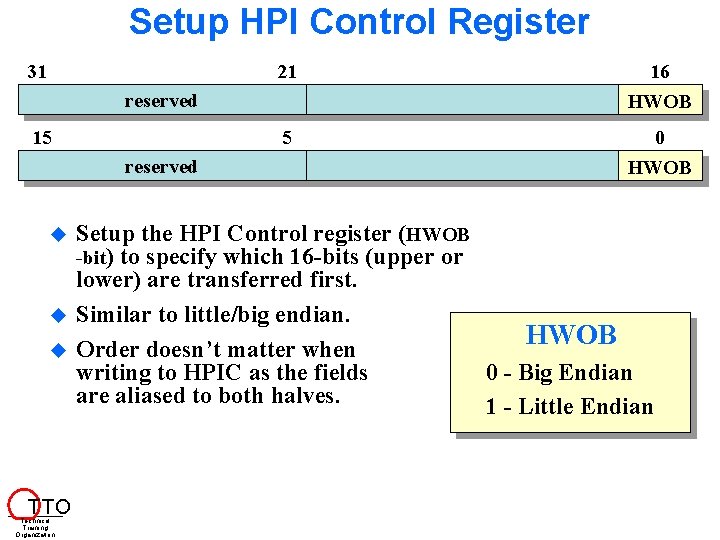

Setup HPI Control Register 31 21 16 HWOB 5 0 HWOB reserved 15 reserved T TO Technical Training Organization Setup the HPI Control register (HWOB -bit) to specify which 16 -bits (upper or lower) are transferred first. Similar to little/big endian. HWOB Order doesn’t matter when writing to HPIC as the fields 0 - Big Endian are aliased to both halves. 1 - Little Endian

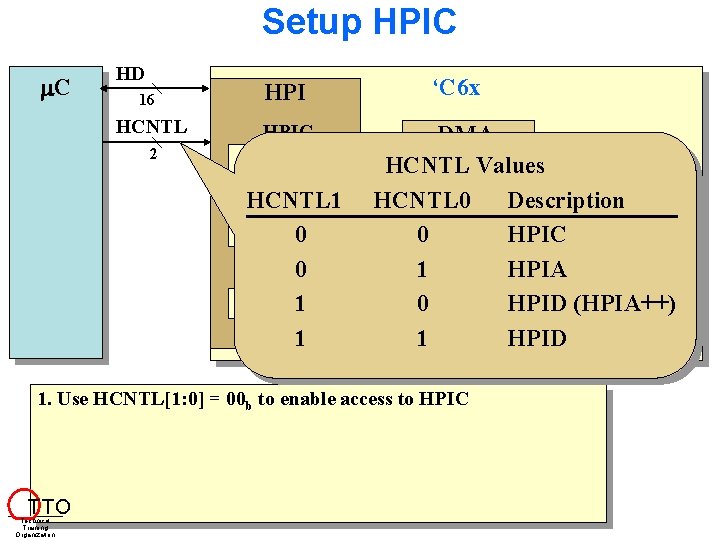

Setup HPIC C HD 16 HPI HCNTL HPIC 2 HCNTL 1 HPIA 0 0 HPID 1 1 ‘C 6 x DMA Memory Aux. Ch. HCNTL Values Addr. HCNTL 0 Description 0 Data HPIC. . 1 HPIA. 0 HPID (HPIA++) 1 HPID 1. Use HCNTL[1: 0] = 00 b to enable access to HPIC T TO Technical Training Organization

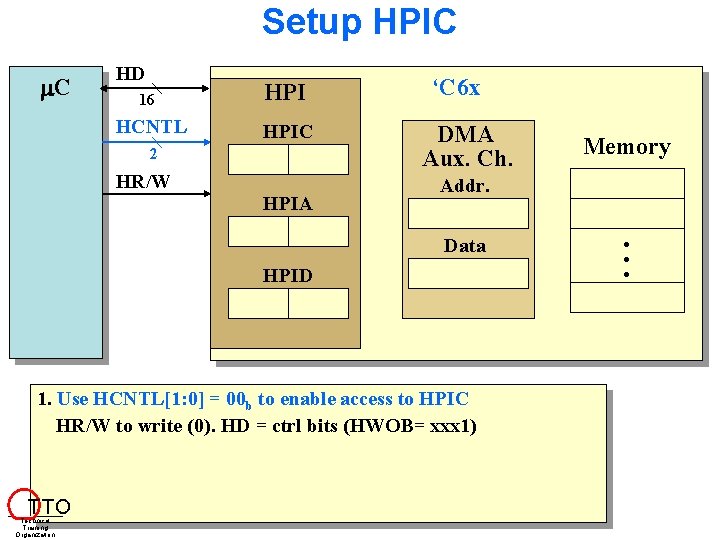

Setup HPIC C HD 16 HPI HCNTL HPIC 2 HR/W HPIA ‘C 6 x DMA Aux. Ch. Addr. Data HPID 1. Use HCNTL[1: 0] = 00 b to enable access to HPIC HR/W to write (0). HD = ctrl bits (HWOB= xxx 1) T TO Technical Training Organization Memory . . .

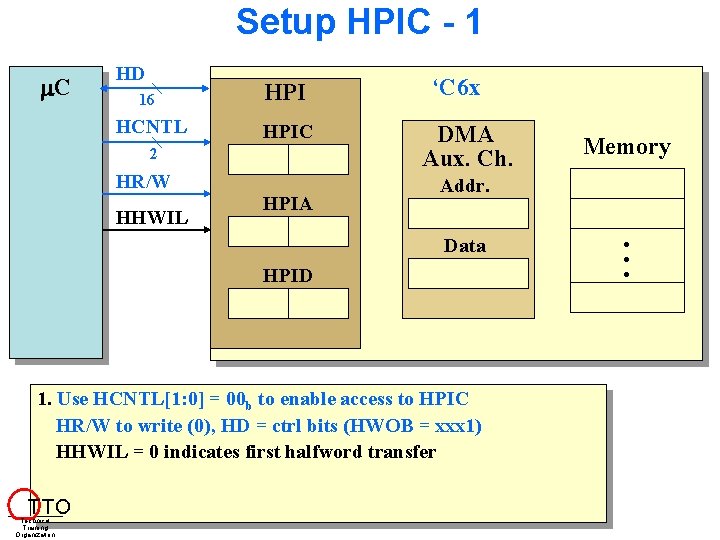

Setup HPIC - 1 C HD 16 HPI HCNTL HPIC 2 HR/W HHWIL HPIA ‘C 6 x DMA Aux. Ch. Addr. Data HPID 1. Use HCNTL[1: 0] = 00 b to enable access to HPIC HR/W to write (0), HD = ctrl bits (HWOB = xxx 1) HHWIL = 0 indicates first halfword transfer T TO Technical Training Organization Memory . . .

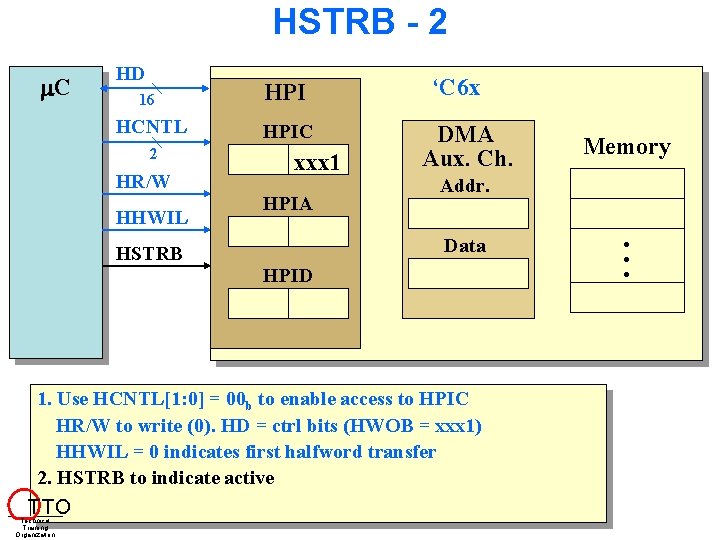

HSTRB - 2 C HD 16 HPI HCNTL HPIC 2 HR/W HHWIL xxx 1 HPIA ‘C 6 x DMA Aux. Ch. Addr. Data HSTRB HPID 1. Use HCNTL[1: 0] = 00 b to enable access to HPIC HR/W to write (0). HD = ctrl bits (HWOB = xxx 1) HHWIL = 0 indicates first halfword transfer 2. HSTRB to indicate active T TO Technical Training Organization Memory . . .

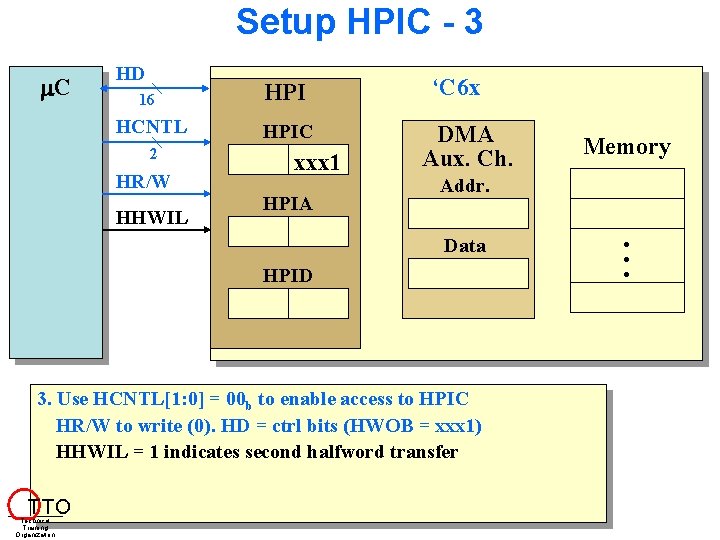

Setup HPIC - 3 C HD 16 HPI HCNTL HPIC 2 HR/W HHWIL xxx 1 HPIA ‘C 6 x DMA Aux. Ch. Addr. Data HPID 3. Use HCNTL[1: 0] = 00 b to enable access to HPIC HR/W to write (0). HD = ctrl bits (HWOB = xxx 1) HHWIL = 1 indicates second halfword transfer T TO Technical Training Organization Memory . . .

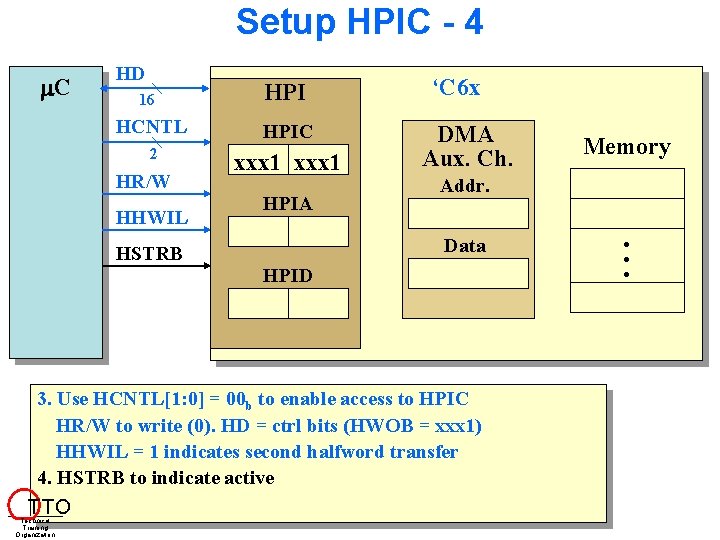

Setup HPIC - 4 C HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HPIA ‘C 6 x DMA Aux. Ch. Addr. Data HSTRB HPID 3. Use HCNTL[1: 0] = 00 b to enable access to HPIC HR/W to write (0). HD = ctrl bits (HWOB = xxx 1) HHWIL = 1 indicates second halfword transfer 4. HSTRB to indicate active T TO Technical Training Organization Memory . . .

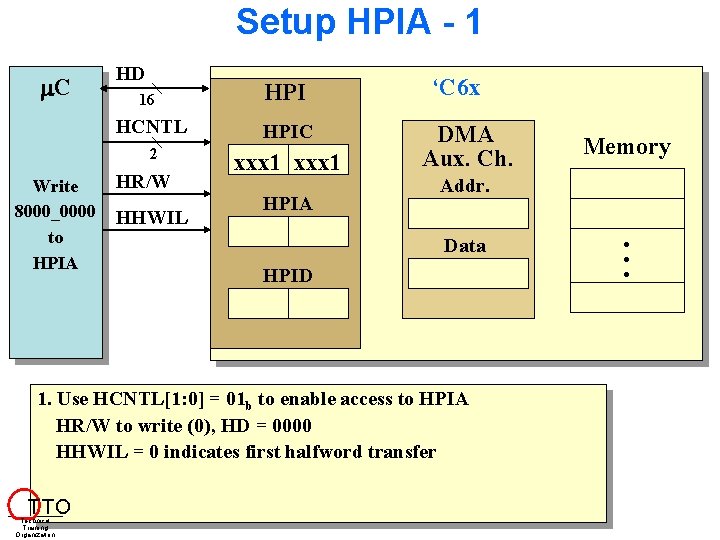

Setup HPIA - 1 C Write 8000_0000 to HPIA HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HPIA ‘C 6 x DMA Aux. Ch. Addr. Data HPID 1. Use HCNTL[1: 0] = 01 b to enable access to HPIA HR/W to write (0), HD = 0000 HHWIL = 0 indicates first halfword transfer T TO Technical Training Organization Memory . . .

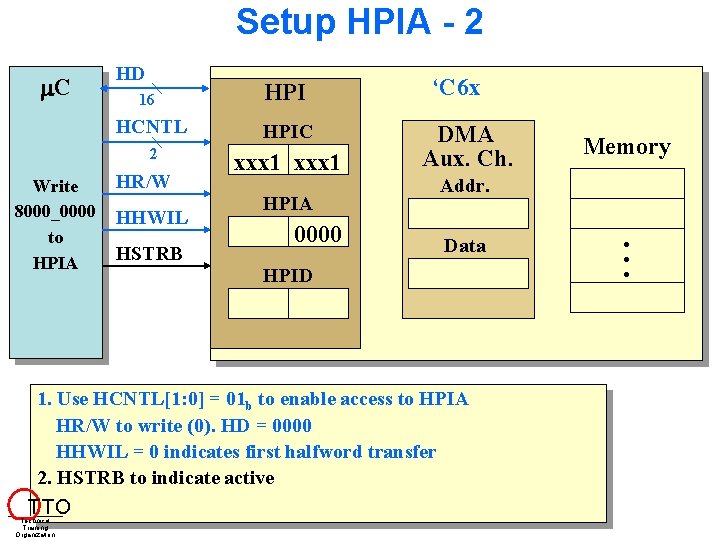

Setup HPIA - 2 C Write 8000_0000 to HPIA HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 0000 ‘C 6 x DMA Aux. Ch. Addr. Data HPID 1. Use HCNTL[1: 0] = 01 b to enable access to HPIA HR/W to write (0). HD = 0000 HHWIL = 0 indicates first halfword transfer 2. HSTRB to indicate active T TO Technical Training Organization Memory . . .

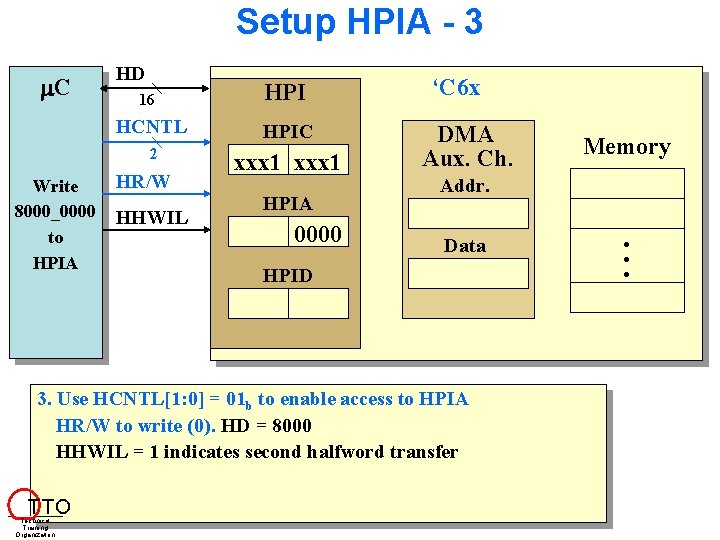

Setup HPIA - 3 C Write 8000_0000 to HPIA HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HPIA 0000 ‘C 6 x DMA Aux. Ch. Addr. Data HPID 3. Use HCNTL[1: 0] = 01 b to enable access to HPIA HR/W to write (0). HD = 8000 HHWIL = 1 indicates second halfword transfer T TO Technical Training Organization Memory . . .

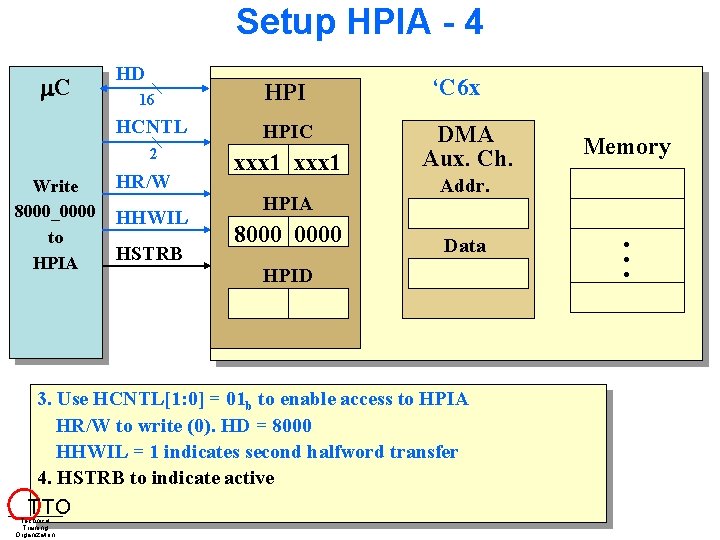

Setup HPIA - 4 C Write 8000_0000 to HPIA HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0000 ‘C 6 x DMA Aux. Ch. Addr. Data HPID 3. Use HCNTL[1: 0] = 01 b to enable access to HPIA HR/W to write (0). HD = 8000 HHWIL = 1 indicates second halfword transfer 4. HSTRB to indicate active T TO Technical Training Organization Memory . . .

Objectives HPI Overview HPI on the DSK Host Software Example HPI Hardware Description Setup Control and Address w w w T TO Technical Training Organization Writing 32 -bits Reading 32 -bits Sequential Accesses Optional Discussions

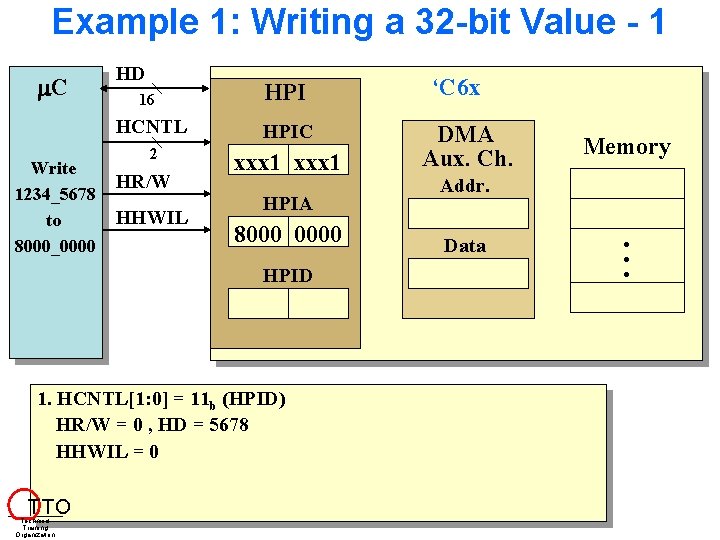

Example 1: Writing a 32 -bit Value - 1 C Write 1234_5678 to 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HPIA 8000 0000 HPID 1. HCNTL[1: 0] = 11 b (HPID) HR/W = 0 , HD = 5678 HHWIL = 0 T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. Data . . .

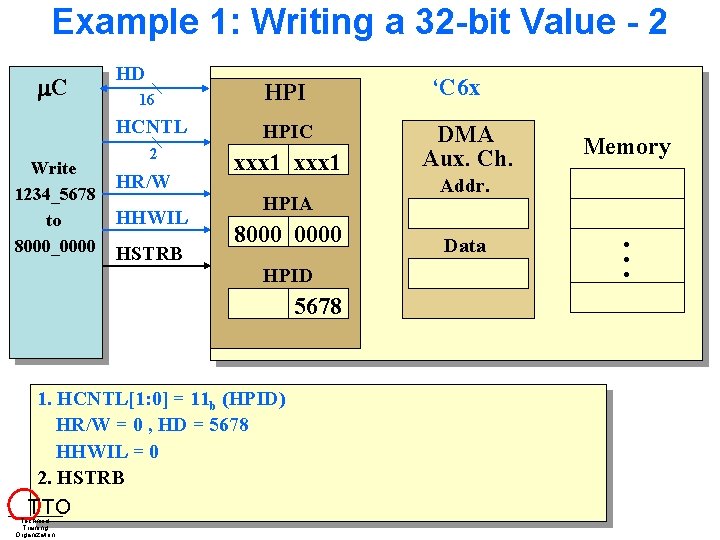

Example 1: Writing a 32 -bit Value - 2 C Write 1234_5678 to 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0000 HPID 5678 1. HCNTL[1: 0] = 11 b (HPID) HR/W = 0 , HD = 5678 HHWIL = 0 2. HSTRB T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. Data . . .

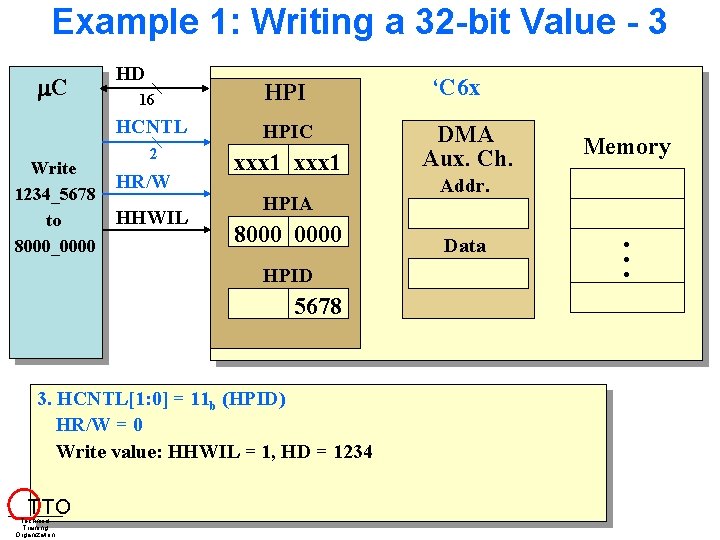

Example 1: Writing a 32 -bit Value - 3 C Write 1234_5678 to 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HPIA 8000 0000 HPID 5678 3. HCNTL[1: 0] = 11 b (HPID) HR/W = 0 Write value: HHWIL = 1, HD = 1234 T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. Data . . .

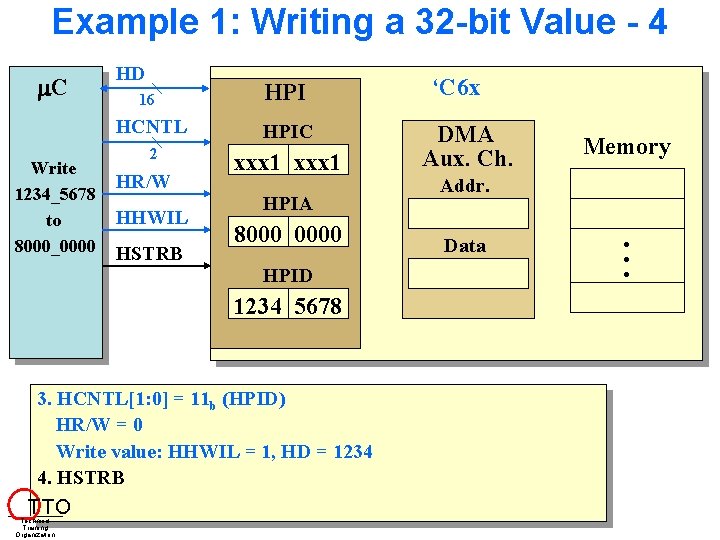

Example 1: Writing a 32 -bit Value - 4 C Write 1234_5678 to 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0000 HPID 1234 5678 3. HCNTL[1: 0] = 11 b (HPID) HR/W = 0 Write value: HHWIL = 1, HD = 1234 4. HSTRB T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. Data . . .

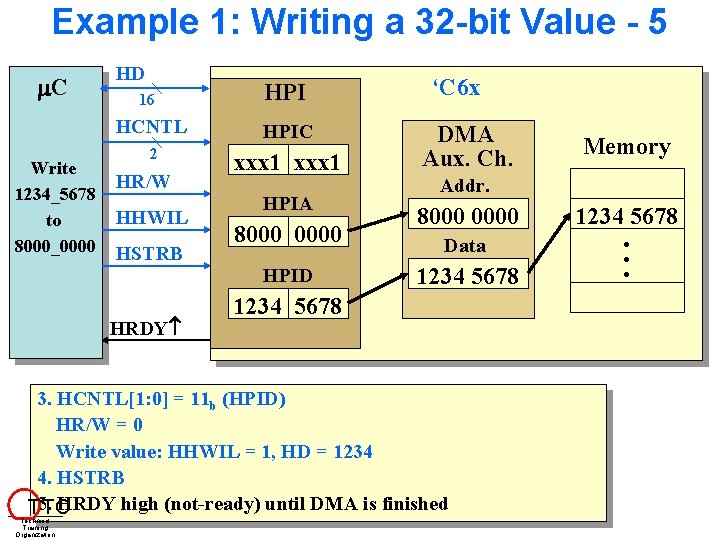

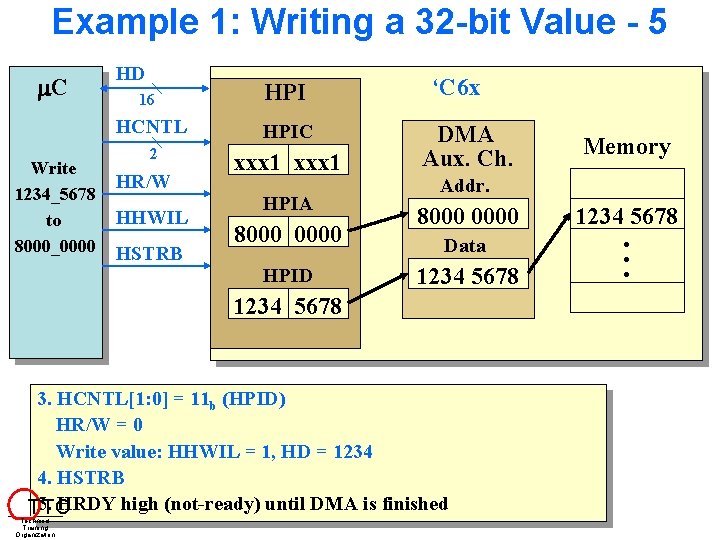

Example 1: Writing a 32 -bit Value - 5 C Write 1234_5678 to 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0000 HPID HRDY ‘C 6 x DMA Aux. Ch. Addr. 8000 0000 Data 1234 5678 3. HCNTL[1: 0] = 11 b (HPID) HR/W = 0 Write value: HHWIL = 1, HD = 1234 4. HSTRB HRDY high (not-ready) until DMA is finished T 5. TO Technical Training Organization Memory 1234 5678 . . .

Example 1: Writing a 32 -bit Value - 5 C Write 1234_5678 to 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0000 HPID ‘C 6 x DMA Aux. Ch. Addr. 8000 0000 Data 1234 5678 3. HCNTL[1: 0] = 11 b (HPID) HR/W = 0 Write value: HHWIL = 1, HD = 1234 4. HSTRB HRDY high (not-ready) until DMA is finished T 5. TO Technical Training Organization Memory 1234 5678 . . .

Objectives HPI Overview HPI on the DSK Host Software Example HPI Hardware Description Setup Control and Address Writing 32 -bits w w T TO Technical Training Organization Reading 32 -bits Sequential Accesses Optional Discussions

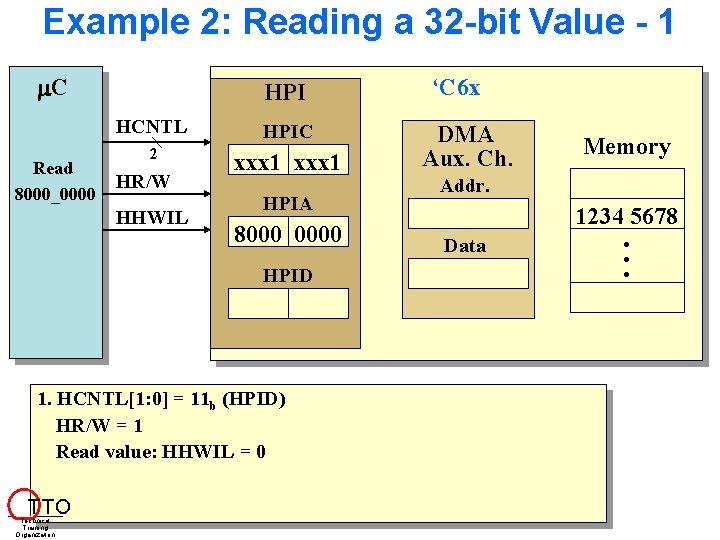

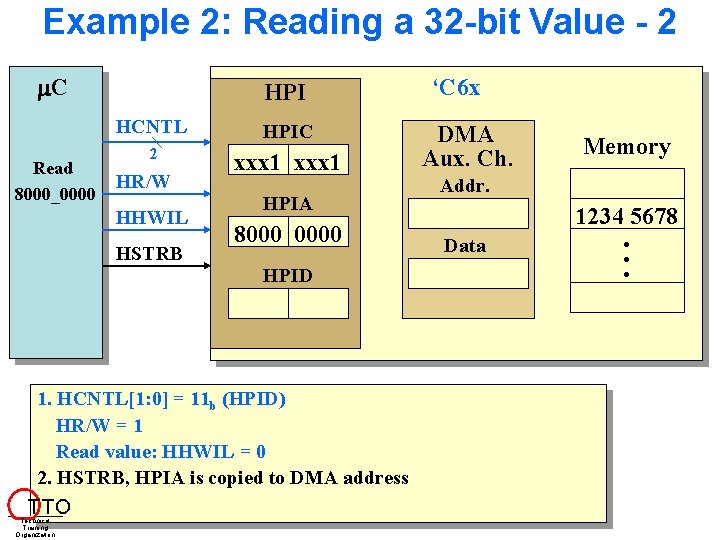

Example 2: Reading a 32 -bit Value - 1 C Read 8000_0000 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HPIA 8000 0000 HPID 1. HCNTL[1: 0] = 11 b (HPID) HR/W = 1 Read value: HHWIL = 0 T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. 1234 5678 Data . . .

Example 2: Reading a 32 -bit Value - 2 C Read 8000_0000 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0000 HPID 1. HCNTL[1: 0] = 11 b (HPID) HR/W = 1 Read value: HHWIL = 0 2. HSTRB, HPIA is copied to DMA address T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. 1234 5678 Data . . .

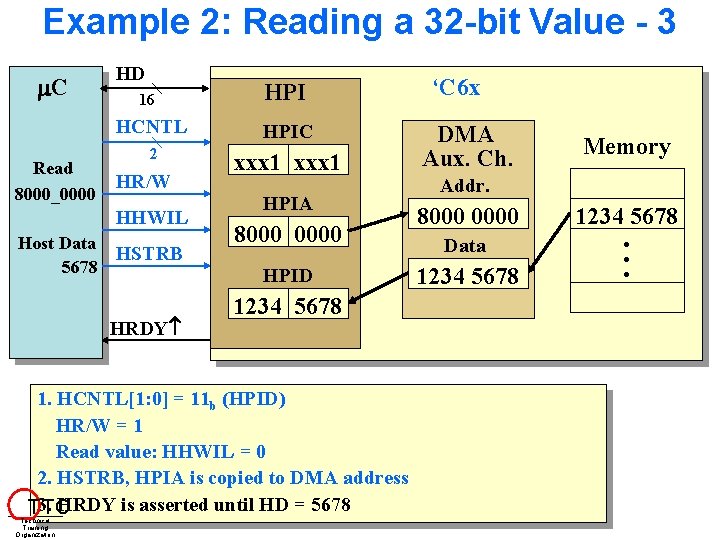

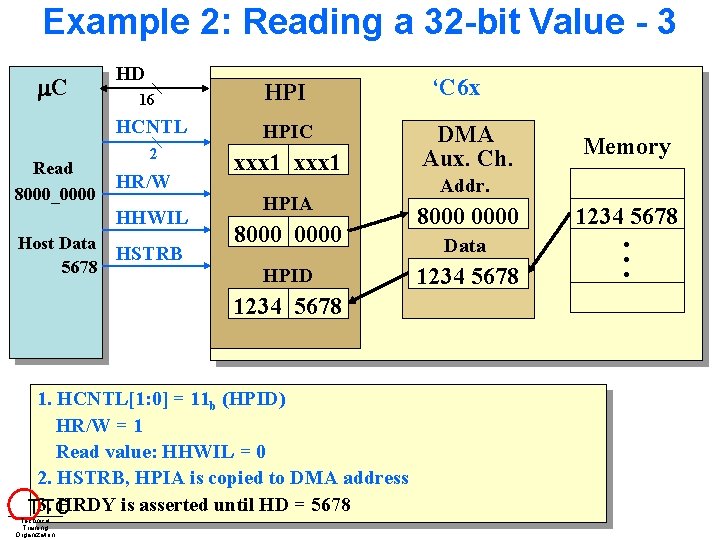

Example 2: Reading a 32 -bit Value - 3 C Read 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL Host Data 5678 HSTRB HPIA 8000 0000 HPID HRDY 1234 5678 1. HCNTL[1: 0] = 11 b (HPID) HR/W = 1 Read value: HHWIL = 0 2. HSTRB, HPIA is copied to DMA address HRDY is asserted until HD = 5678 T 3. TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. 8000 0000 Data 1234 5678 . . .

Example 2: Reading a 32 -bit Value - 3 C Read 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL Host Data 5678 HSTRB HPIA 8000 0000 HPID 1234 5678 1. HCNTL[1: 0] = 11 b (HPID) HR/W = 1 Read value: HHWIL = 0 2. HSTRB, HPIA is copied to DMA address HRDY is asserted until HD = 5678 T 3. TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. 8000 0000 Data 1234 5678 . . .

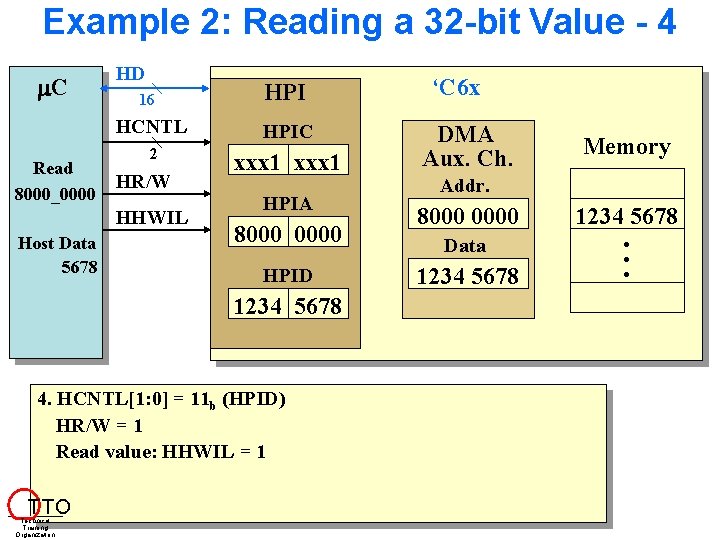

Example 2: Reading a 32 -bit Value - 4 C Read 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL Host Data 5678 HPIA 8000 0000 HPID 1234 5678 4. HCNTL[1: 0] = 11 b (HPID) HR/W = 1 Read value: HHWIL = 1 T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. 8000 0000 Data 1234 5678 . . .

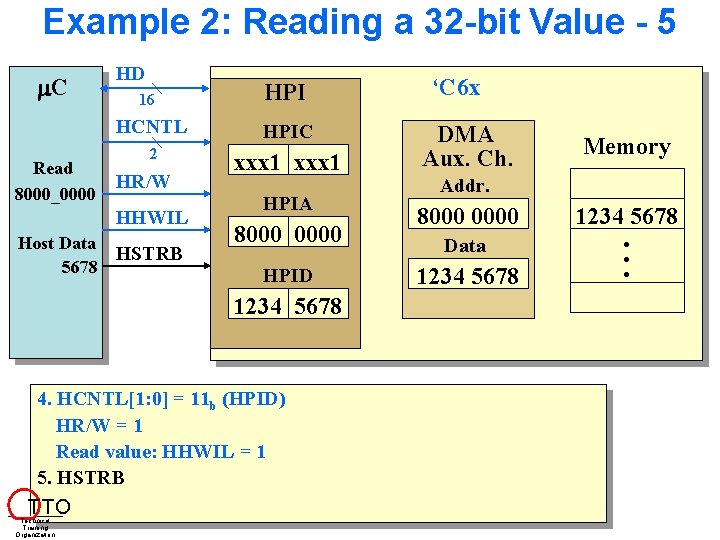

Example 2: Reading a 32 -bit Value - 5 C Read 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL Host Data 5678 HSTRB HPIA 8000 0000 HPID 1234 5678 4. HCNTL[1: 0] = 11 b (HPID) HR/W = 1 Read value: HHWIL = 1 5. HSTRB T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. 8000 0000 Data 1234 5678 . . .

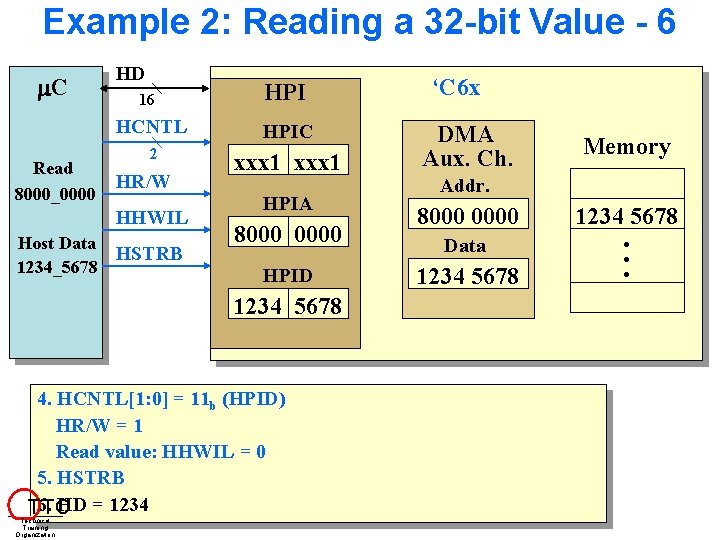

Example 2: Reading a 32 -bit Value - 6 C Read 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL Host Data 1234_5678 HSTRB HPIA 8000 0000 HPID 1234 5678 4. HCNTL[1: 0] = 11 b (HPID) HR/W = 1 Read value: HHWIL = 0 5. HSTRB HD = 1234 T 6. TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. 8000 0000 Data 1234 5678 . . .

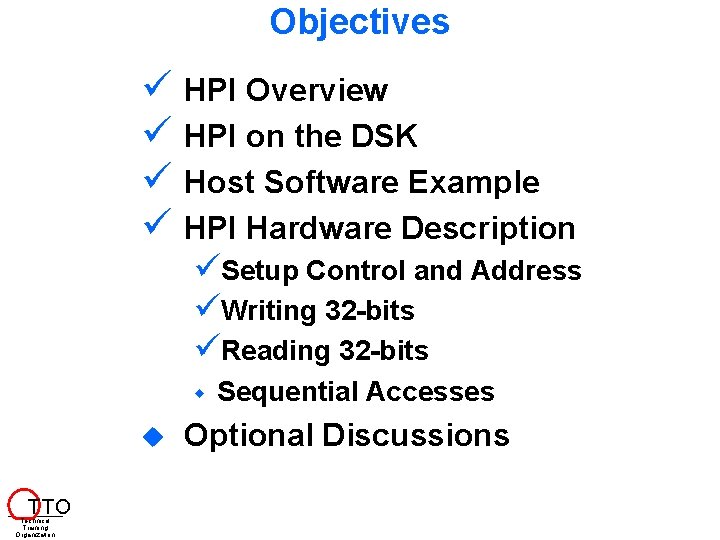

Objectives HPI Overview HPI on the DSK Host Software Example HPI Hardware Description Setup Control and Address Writing 32 -bits Reading 32 -bits w T TO Technical Training Organization Sequential Accesses Optional Discussions

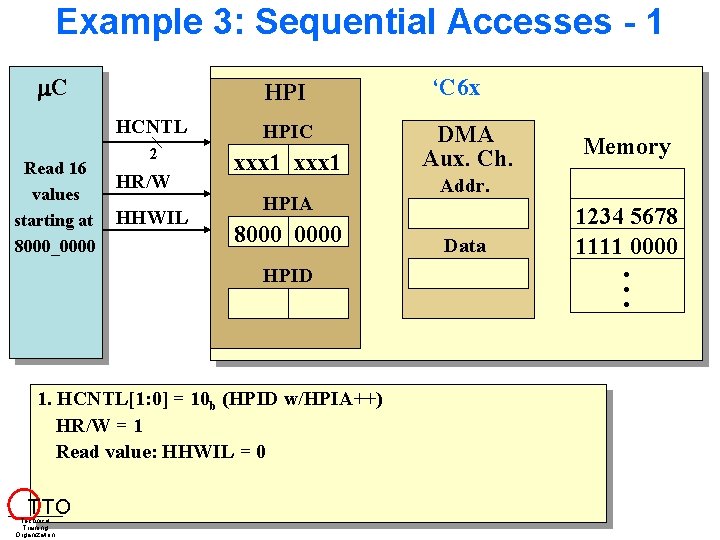

Example 3: Sequential Accesses - 1 C Read 16 values starting at 8000_0000 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HPIA 8000 0000 HPID 1. HCNTL[1: 0] = 10 b (HPID w/HPIA++) HR/W = 1 Read value: HHWIL = 0 T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. Data 1234 5678 1111 0000 . . .

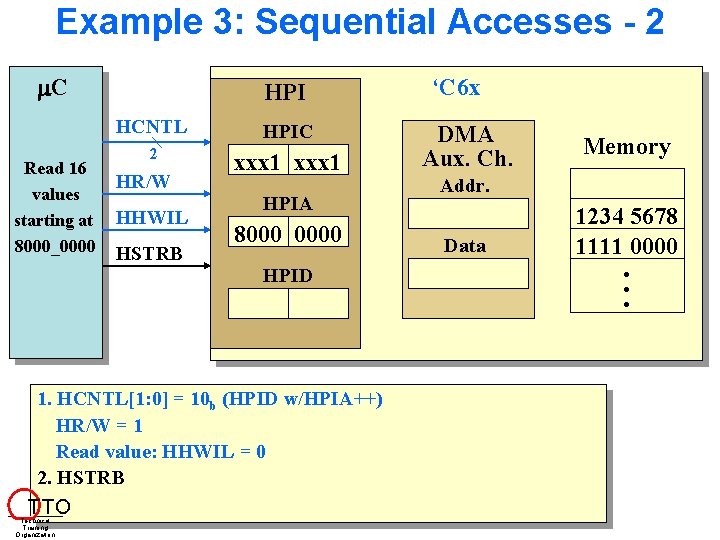

Example 3: Sequential Accesses - 2 C Read 16 values starting at 8000_0000 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0000 HPID 1. HCNTL[1: 0] = 10 b (HPID w/HPIA++) HR/W = 1 Read value: HHWIL = 0 2. HSTRB T TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. Data 1234 5678 1111 0000 . . .

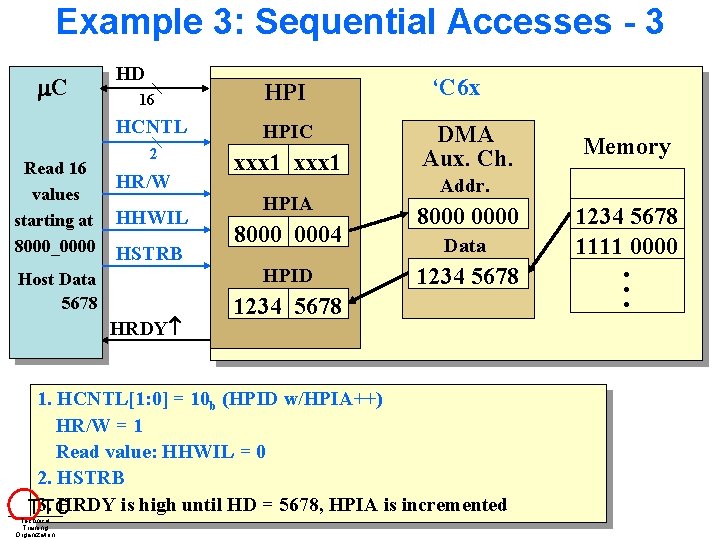

Example 3: Sequential Accesses - 3 C Read 16 values starting at 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0004 HPID Host Data 5678 HRDY ‘C 6 x DMA Aux. Ch. Addr. 8000 0000 Data 1234 5678 1. HCNTL[1: 0] = 10 b (HPID w/HPIA++) HR/W = 1 Read value: HHWIL = 0 2. HSTRB HRDY is high until HD = 5678, HPIA is incremented T 3. TO Technical Training Organization Memory 1234 5678 1111 0000 . . .

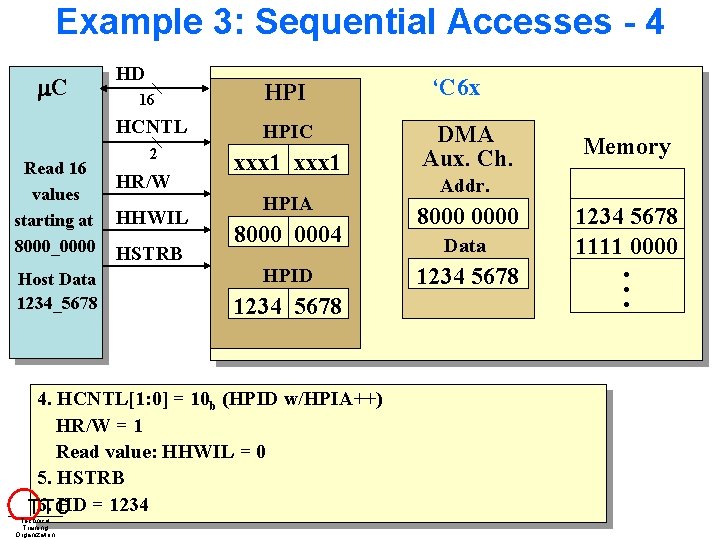

Example 3: Sequential Accesses - 4 C Read 16 values starting at 8000_0000 Host Data 1234_5678 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0004 0000 HPID 1234 5678 4. HCNTL[1: 0] = 10 b (HPID w/HPIA++) HR/W = 1 Read value: HHWIL = 0 5. HSTRB HD = 1234 T 6. TO Technical Training Organization ‘C 6 x DMA Aux. Ch. Memory Addr. 8000 0000 Data 1234 5678 1111 0000 . . .

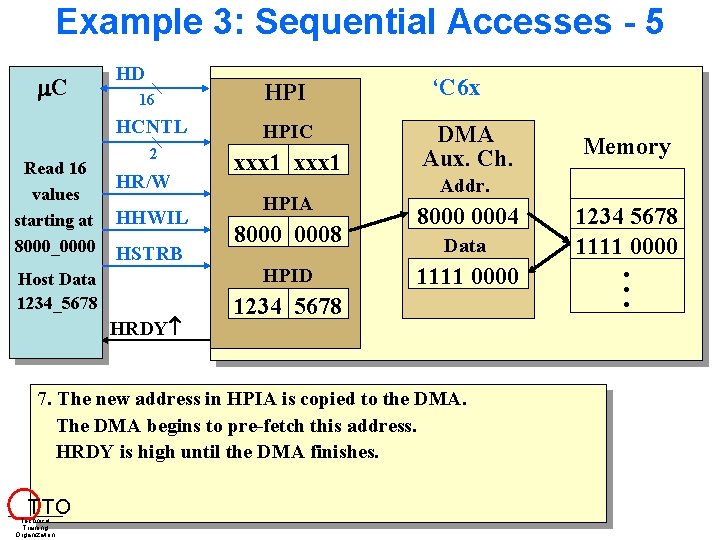

Example 3: Sequential Accesses - 5 C Read 16 values starting at 8000_0000 HD 16 HPI HCNTL HPIC 2 xxx 1 HR/W HHWIL HSTRB HPIA 8000 0008 0000 0004 HPID Host Data 1234_5678 HRDY ‘C 6 x DMA Aux. Ch. Addr. 8000 0004 0000 Data 1111 1234 0000 5678 1234 5678 7. The new address in HPIA is copied to the DMA. The DMA begins to pre-fetch this address. HRDY is high until the DMA finishes. T TO Technical Training Organization Memory 1234 5678 1111 0000 . . .

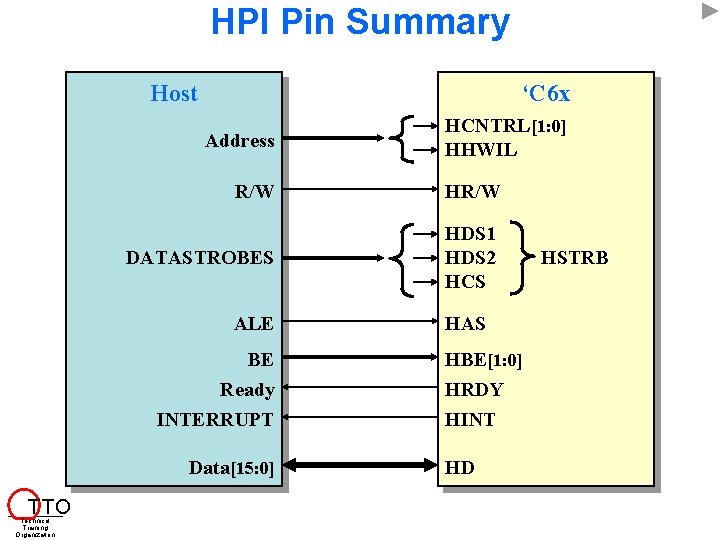

HPI Pin Summary Host ‘C 6 x Address R/W HR/W DATASTROBES HDS 1 HDS 2 HCS ALE BE Ready INTERRUPT Data[15: 0] T TO Technical Training Organization HCNTRL[1: 0] HHWIL HAS HBE[1: 0] HRDY HINT HD HSTRB

![Interface Example MC 68360 ‘C 6 x Data[31: 16] HD[15: 0] R/W A[3: 2] Interface Example MC 68360 ‘C 6 x Data[31: 16] HD[15: 0] R/W A[3: 2]](http://slidetodoc.com/presentation_image/dbd74b12549c9201950ea6410bdef8ec/image-46.jpg)

Interface Example MC 68360 ‘C 6 x Data[31: 16] HD[15: 0] R/W A[3: 2] A[1] HR/W HCNTRL[1: 0] HHWIL HRDY DSACK 1 DSACK 0 Vcc GND HBE[1: 0] GND Vcc HCS HDS 1 HDS 2 HAS CSx Vcc IRQx T TO Technical Training Organization HINT

Objectives HPI Hardware Overview Setup Control and Address Writing 32 -bits Reading 32 -bits Sequential Accesses Optional Discussions Control Register (and CSL for HPI) Expansion Bus (XBUS) T TO Technical Training Organization Next Chapter 17. Wrap Up

Objectives HPI Hardware Overview Setup Control and Address Writing 32 -bits Reading 32 -bits Sequential Accesses Optional Discussions Control Register (and CSL for HPI) Expansion Bus (XBUS) T TO Technical Training Organization Next Chapter 17. Wrap Up

Technical Training Organization T TO Technical Training Organization ti

- Slides: 49