Hoofdstuk 5 Het belang van geheugens Prof dr

Hoofdstuk 5 Het belang van geheugens Prof. dr. ir. Dirk Stroobandt Academiejaar 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen

Inhoud (deel 2) Het belang van interconnecties Het belang van ingebed geheugen Het voorspellen van prestaties Architecturen voor complexe systemen – Processorarchitecturen – Herconfigureerbare hardware – Hergebruik van IP-kernen Interfaces en interface-ontwerp 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 2

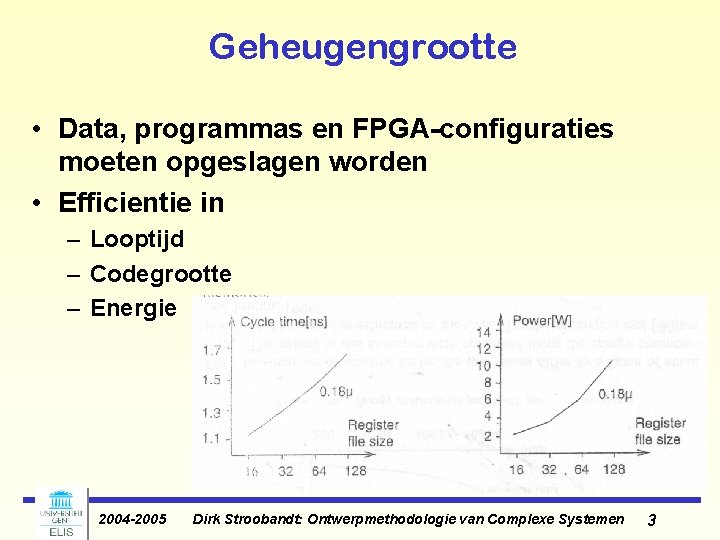

Geheugengrootte • Data, programmas en FPGA-configuraties moeten opgeslagen worden • Efficientie in – Looptijd – Codegrootte – Energie 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 3

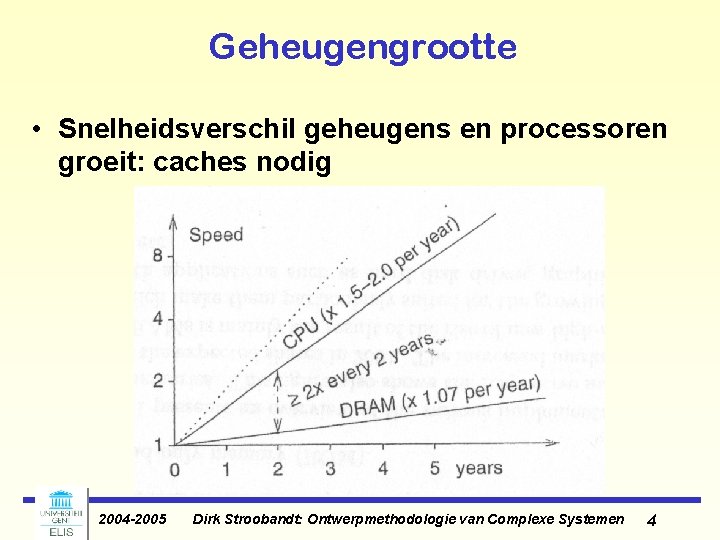

Geheugengrootte • Snelheidsverschil geheugens en processoren groeit: caches nodig 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 4

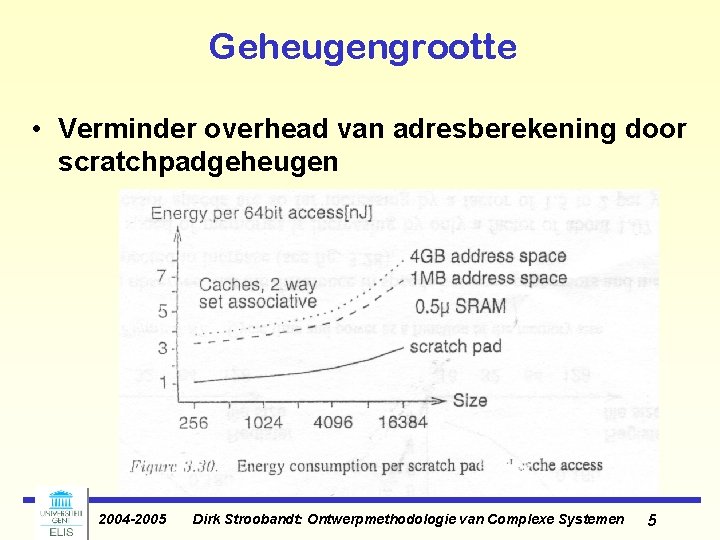

Geheugengrootte • Verminder overhead van adresberekening door scratchpadgeheugen 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 5

Geheugentypes • SRAM – Zeer snel, laag vermogenverbruik, caches in PCs, telecom, multimedia-computers, netwerkingtoepassingen, GSM, supercomputers, ingebedde systeemgeheugens • DRAM – Middelmatige tot hoge snelheid, grote computersystemen, lage kost, grote volumes, PC, hard disk, grafische borden, printers, PDAs, camcorders, ingebedde systeemgeheugens, ingebedde logica 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 6

Geheugentypes • FRAM – Laag vermogen, niet-volatiel, smart cards, RFidentificatie, vervanging van niet-volatiele RAM en hoogdensiteits SRAM • ROM – Grote volumes, videospelletjes, karaktergeneratoren, laser printer fonts, ingebedde geheugens • EPROM – CD-rom, modems, ingebedde systemen 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 7

Geheugentypes • EEPROM – Militair, vliegtuigcontrole, gebruiksvoorwerpen, draagbare apparaten, modems, draadlowe telefoons, disk drives, printers, air bags, abs, autoradio’s, smart card, set-top boxes, ingebedde geheugens • FLASH – Draagbare systemen, communicatiesystemen, codeopslag, geheugenkaarten, BIOS, digitale camera’s, flash-kaarten, palm tops, batterijgevoede apparaten, ingebedde geheugens, MP 3 -spelers • NVRAM, BRAM – Als vermogendips niet mogen, medisch, ruimteschip 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 8

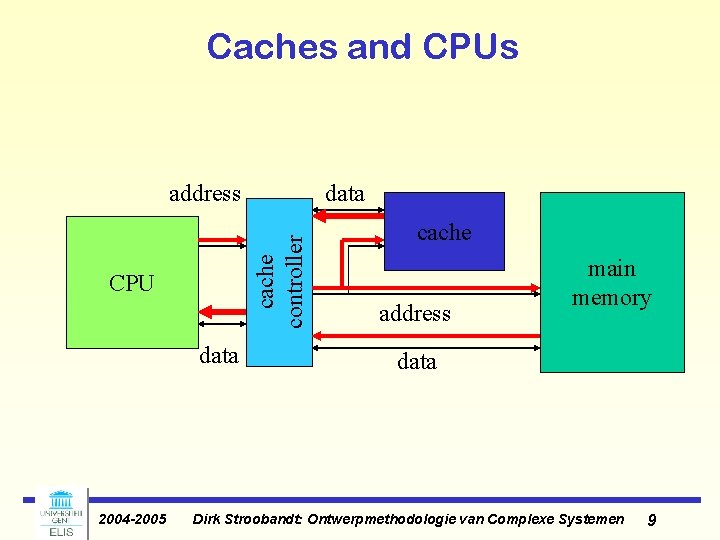

Caches and CPUs CPU data 2004 -2005 data cache controller address cache address main memory data Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 9

Cache operation • Many main memory locations are mapped onto one cache entry. • May have caches for: – instructions; – data + instructions (unified). • Memory access time is no longer deterministic. 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 10

Terms • Cache hit: required location is in cache. • Cache miss: required location is not in cache. • Working set: set of locations used by program in a time interval. 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 11

Types of misses • Compulsory (cold): location has never been accessed. • Capacity: working set is too large. • Conflict: multiple locations in working set map to same cache entry. 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 12

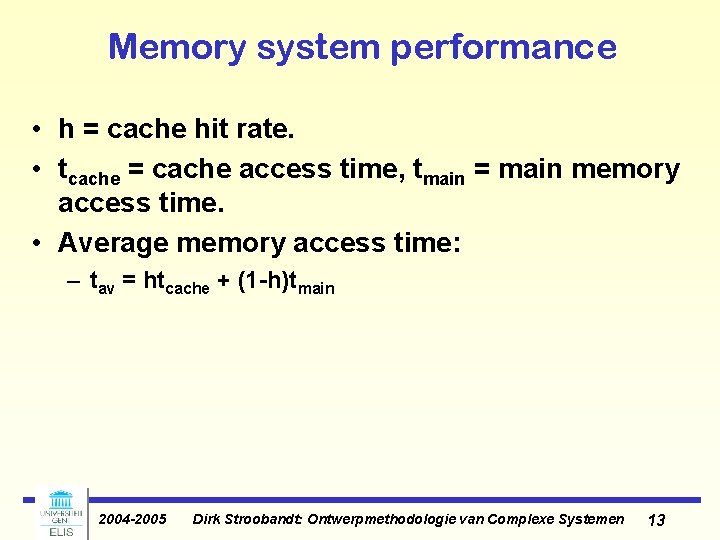

Memory system performance • h = cache hit rate. • tcache = cache access time, tmain = main memory access time. • Average memory access time: – tav = htcache + (1 -h)tmain 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 13

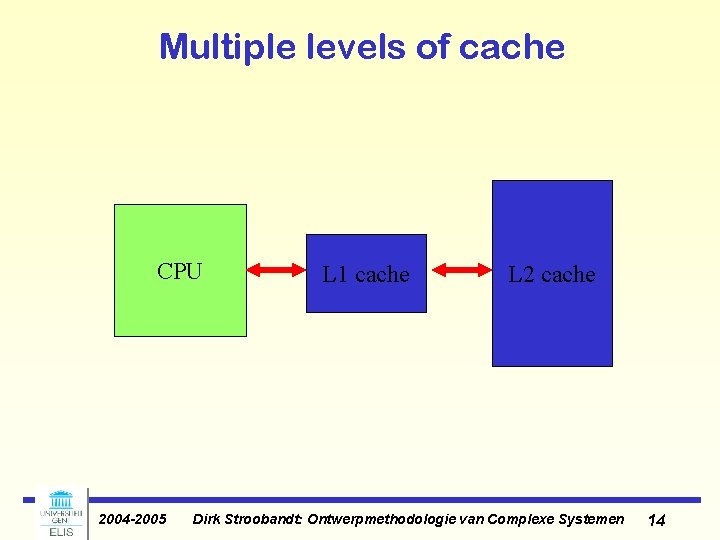

Multiple levels of cache CPU 2004 -2005 L 1 cache L 2 cache Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 14

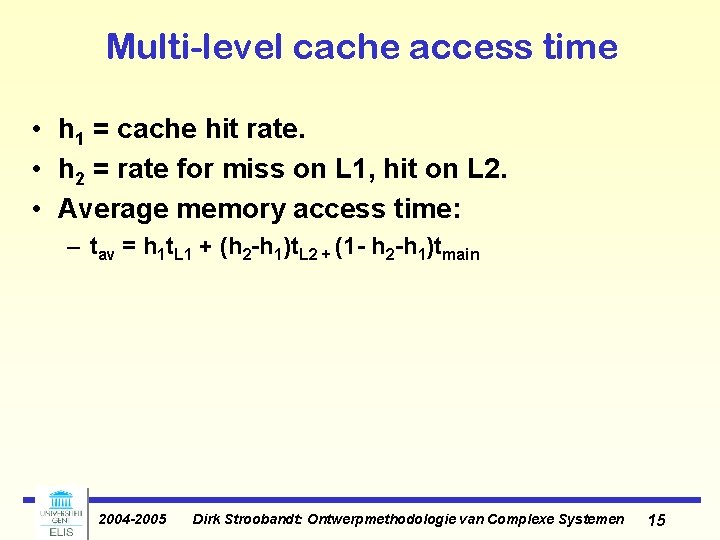

Multi-level cache access time • h 1 = cache hit rate. • h 2 = rate for miss on L 1, hit on L 2. • Average memory access time: – tav = h 1 t. L 1 + (h 2 -h 1)t. L 2 + (1 - h 2 -h 1)tmain 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 15

Replacement policies • Replacement policy: strategy for choosing which cache entry to throw out to make room for a new memory location. • Two popular strategies: – Random. – Least-recently used (LRU). 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 16

Cache organizations • Fully-associative: any memory location can be stored anywhere in the cache (almost never implemented). • Direct-mapped: each memory location maps onto exactly one cache entry. • N-way set-associative: each memory location can go into one of n sets. 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 17

Cache performance benefits • Keep frequently-accessed locations in fast cache. • Cache retrieves more than one word at a time. – Sequential accesses are faster after first access. 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 18

Ingebedde geheugens • In So. C: logica + geheugen op 1 chip – – – Hogere bandbreedte Kleiner aantal pinnen Kleiner systeem Betrouwbaarder systeem Lager vermogenverbruik • Kan gebruik maken van ongebruikte transistoren door de ontwerpskloof • Door samenbouw op chip: dikwijls geen caches maar onmiddellijk (klein) hoofdgeheugen 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 19

Ingebedde geheugens • Drie manieren om ingebedde geheugens te integreren – Geheugens in technologie voor logica • SRAM, DRAM en zelfs EEPROM • Voor SRAM geen bijkomende ontwerpstappen nodig – Logica in technologie voor geheugens (meestal DRAM) • Hoogste densiteit voor geheugens • Gebruiken minder interconnectielagen – Gemengde technologie • Meer interconnectielagen voor de logica 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 20

Ingebedde geheugens • Vooral aandacht voor – Op tijd opvullen van het geheugen op chip met de nodige data (streaming-toepassingen) • Is mogelijk doordat de toepassing gekend is – Goede datalayout om efficiënt geheugengebruik te bevorderen – Gepaste lustransformaties e. d. 2004 -2005 Dirk Stroobandt: Ontwerpmethodologie van Complexe Systemen 21

- Slides: 21