Homework verilog Block Diagram reg testbench reg wire

Homework – verilog補充說明

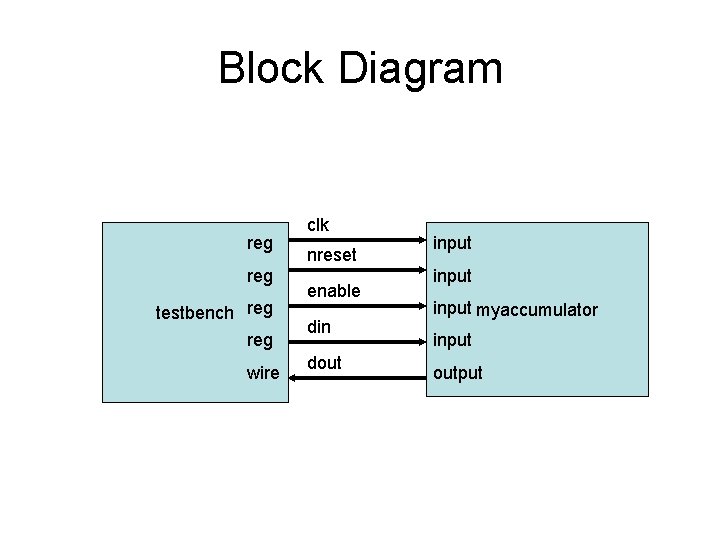

Block Diagram reg testbench reg wire clk nreset enable din dout input myaccumulator input output

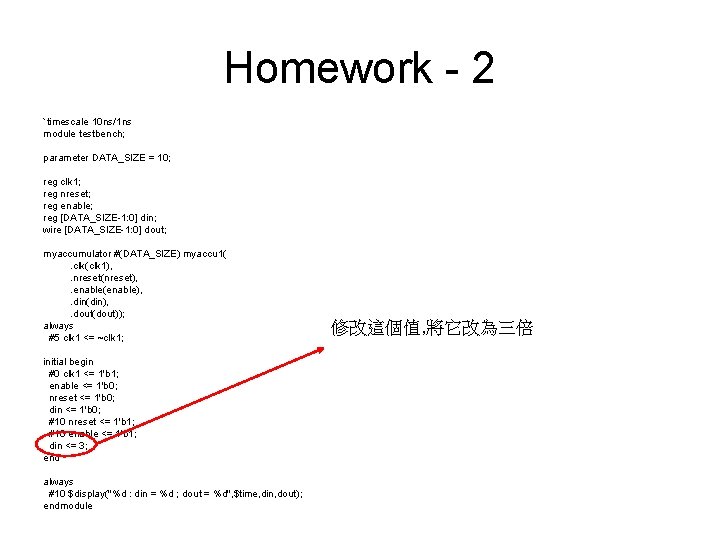

Homework - 2 `timescale 10 ns/1 ns module testbench; parameter DATA_SIZE = 10; reg clk 1; reg nreset; reg enable; reg [DATA_SIZE-1: 0] din; wire [DATA_SIZE-1: 0] dout; myaccumulator #(DATA_SIZE) myaccu 1(. clk(clk 1), . nreset(nreset), . enable(enable), . din(din), . dout(dout)); always #5 clk 1 <= ~clk 1; initial begin #0 clk 1 <= 1'b 1; enable <= 1'b 0; nreset <= 1'b 0; din <= 1'b 0; #10 nreset <= 1'b 1; #10 enable <= 1'b 1; din <= 3; end always #10 $display("%d : din = %d ; dout = %d", $time, din, dout); endmodule 修改這個值, 將它改為三倍

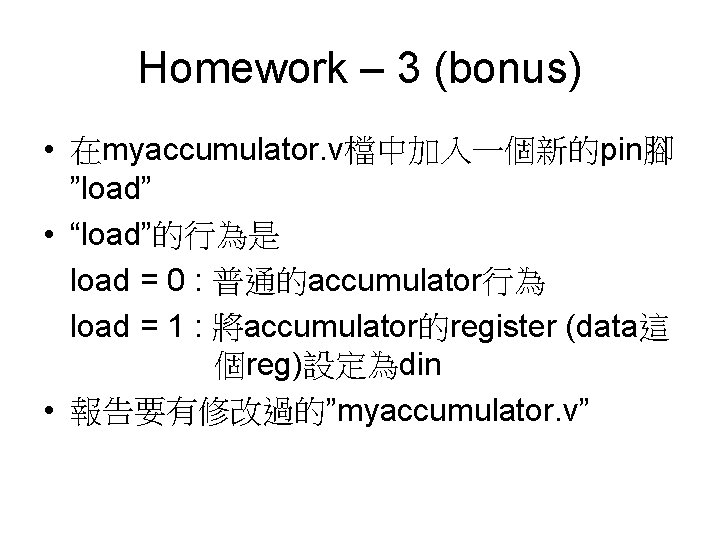

Homework – 3 (bonus) • 在myaccumulator. v檔中加入一個新的pin腳 ”load” • “load”的行為是 load = 0 : 普通的accumulator行為 load = 1 : 將accumulator的register (data這 個reg)設定為din • 報告要有修改過的”myaccumulator. v”

Homework – 3 (bonus) block diagram reg testbench reg reg wire clk nreset enable din load dout input myaccumulator input output

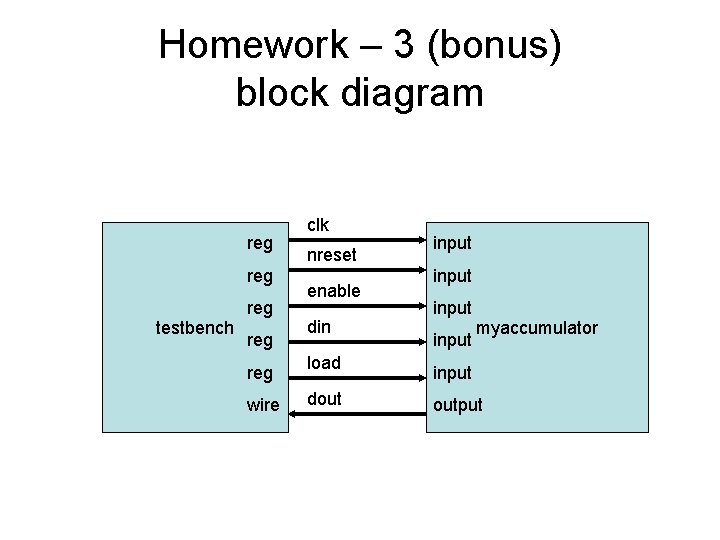

Homework - 3 (bonus) `timescale 10 ns/1 ns module myaccumulator( clk, nreset, enable, din, dout); parameter DATA_SIZE = 8; 類似C function宣告, “load”對這個module 就像是一 個參數, 所以要將它加到module 的中port list reg [DATA_SIZE - 1: 0] data; port list 中哪些是input 哪些是 output 要宣告, ”load”對 accumulator是一個input , 所以這 邊要宣告 input load; assign dout = data; 在這邊定義出”load”的行為 always @(posedge clk) begin if(nreset == 1'b 0) begin data <= 0; end else if(enable == 1'b 1) begin data <= din + data; end else begin data <= data; end Priority的順序是 nreset > load > enable input clk; input nreset; input enable; input [DATA_SIZE - 1: 0] din; output [DATA_SIZE - 1: 0] dout; endmodule 所以在這邊加入 else if( load == 1) begin data <= din; end

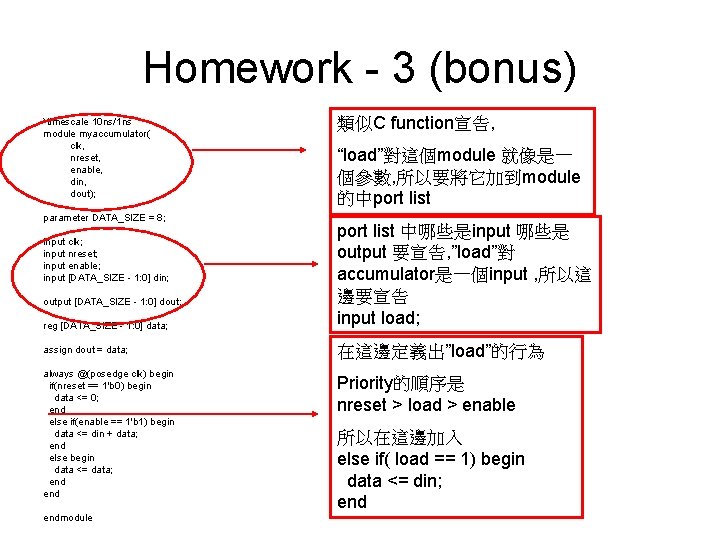

Homework - 4 (bonus) • 修改”testbench. v” 來看看load是否是正確的 運作 • 報告要有修改過的”testbench. v”, waveform

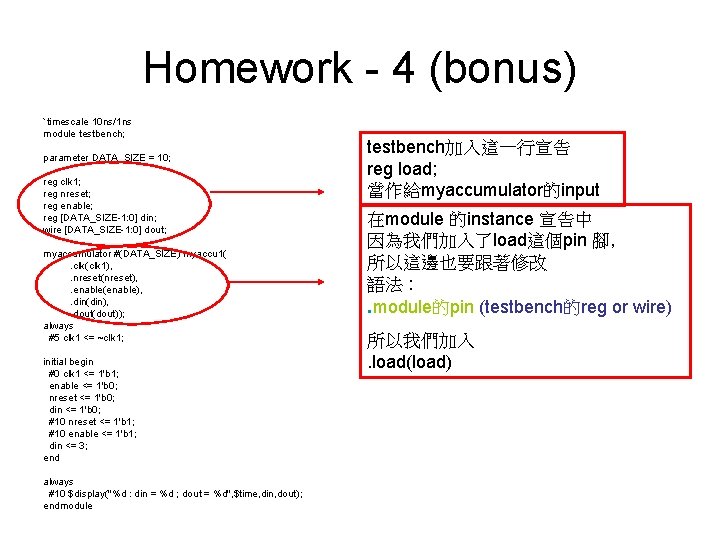

Homework - 4 (bonus) `timescale 10 ns/1 ns module testbench; parameter DATA_SIZE = 10; reg clk 1; reg nreset; reg enable; reg [DATA_SIZE-1: 0] din; wire [DATA_SIZE-1: 0] dout; myaccumulator #(DATA_SIZE) myaccu 1(. clk(clk 1), . nreset(nreset), . enable(enable), . din(din), . dout(dout)); always #5 clk 1 <= ~clk 1; initial begin #0 clk 1 <= 1'b 1; enable <= 1'b 0; nreset <= 1'b 0; din <= 1'b 0; #10 nreset <= 1'b 1; #10 enable <= 1'b 1; din <= 3; end always #10 $display("%d : din = %d ; dout = %d", $time, din, dout); endmodule testbench加入這一行宣告 reg load; 當作給myaccumulator的input 在module 的instance 宣告中 因為我們加入了load這個pin 腳, 所以這邊也要跟著修改 語法 : . module的pin (testbench的reg or wire) 所以我們加入. load(load)

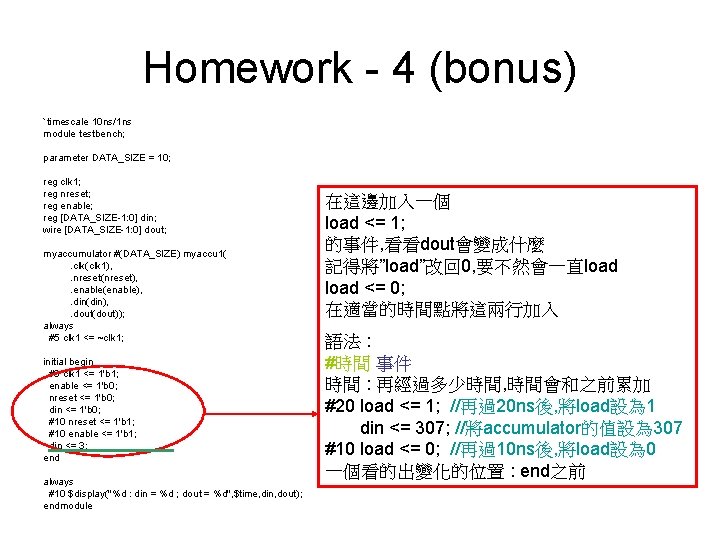

Homework - 4 (bonus) `timescale 10 ns/1 ns module testbench; parameter DATA_SIZE = 10; reg clk 1; reg nreset; reg enable; reg [DATA_SIZE-1: 0] din; wire [DATA_SIZE-1: 0] dout; myaccumulator #(DATA_SIZE) myaccu 1(. clk(clk 1), . nreset(nreset), . enable(enable), . din(din), . dout(dout)); always #5 clk 1 <= ~clk 1; initial begin #0 clk 1 <= 1'b 1; enable <= 1'b 0; nreset <= 1'b 0; din <= 1'b 0; #10 nreset <= 1'b 1; #10 enable <= 1'b 1; din <= 3; end always #10 $display("%d : din = %d ; dout = %d", $time, din, dout); endmodule 在這邊加入一個 load <= 1; 的事件, 看看dout會變成什麼 記得將”load”改回 0, 要不然會一直load <= 0; 在適當的時間點將這兩行加入 語法 : #時間 事件 時間 : 再經過多少時間, 時間會和之前累加 #20 load <= 1; //再過20 ns後, 將load設為 1 din <= 307; //將accumulator的值設為 307 #10 load <= 0; //再過10 ns後, 將load設為 0 一個看的出變化的位置 : end之前

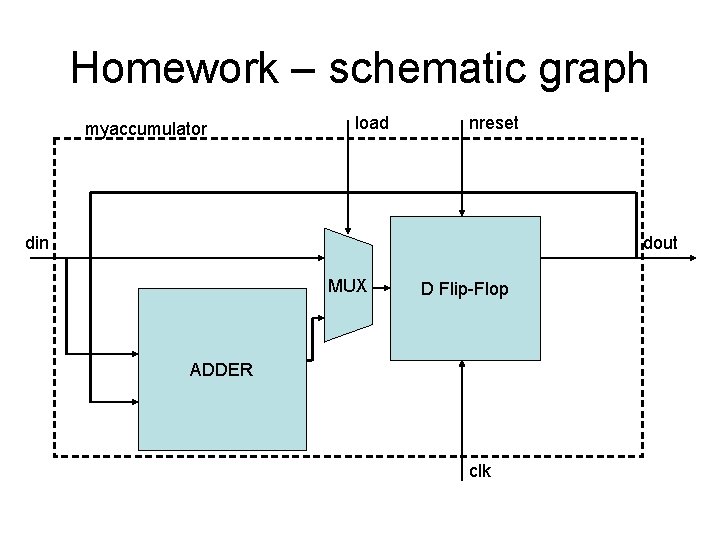

Homework – schematic graph myaccumulator load nreset din dout MUX D Flip-Flop ADDER clk

- Slides: 12