HMEC 3 2 define Verilogdefine verilog define printv

![HMEC 3. 3. 4 显式及隐式变量和线网类型 声明语句中,数据类型前没有显式指定对象类型时,则 推断为隐式变量 logic [7 : 0] bus. A; bit HMEC 3. 3. 4 显式及隐式变量和线网类型 声明语句中,数据类型前没有显式指定对象类型时,则 推断为隐式变量 logic [7 : 0] bus. A; bit](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-12.jpg)

![HMEC 3. 5 数据类型规则的放宽 对变量使用的限制可以防止设计错误:多个输出端口驱动一个变量; 对一个变量进行多次连续赋值;对同一个变量同时进行过程赋值和 连续赋值 module add_and_increment(output logic [63 : 0] sum, HMEC 3. 5 数据类型规则的放宽 对变量使用的限制可以防止设计错误:多个输出端口驱动一个变量; 对一个变量进行多次连续赋值;对同一个变量同时进行过程赋值和 连续赋值 module add_and_increment(output logic [63 : 0] sum,](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-18.jpg)

![HMEC 3. 6 有符号和无符号修饰符 integer j; //verilog-1995标准,32位有符号数 reg [63 : 0] u; //无符号 64位数 HMEC 3. 6 有符号和无符号修饰符 integer j; //verilog-1995标准,32位有符号数 reg [63 : 0] u; //无符号 64位数](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-19.jpg)

![HMEC 3. 10 常数 System. Verilog加入了一个类似C语言风格的const声明, 可以将任何变量声明为常数,有确立完成之后才被赋值, 并且可以在自动任务或函数、begin…end、fork…join中 声明 const logic [23 : 0] HMEC 3. 10 常数 System. Verilog加入了一个类似C语言风格的const声明, 可以将任何变量声明为常数,有确立完成之后才被赋值, 并且可以在自动任务或函数、begin…end、fork…join中 声明 const logic [23 : 0]](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-32.jpg)

![HMEC 4. 1. 2 共享typedef定义 module counter(output chip_types : : dtype_t [15 : 0] HMEC 4. 1. 2 共享typedef定义 module counter(output chip_types : : dtype_t [15 : 0]](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-37.jpg)

- Slides: 51

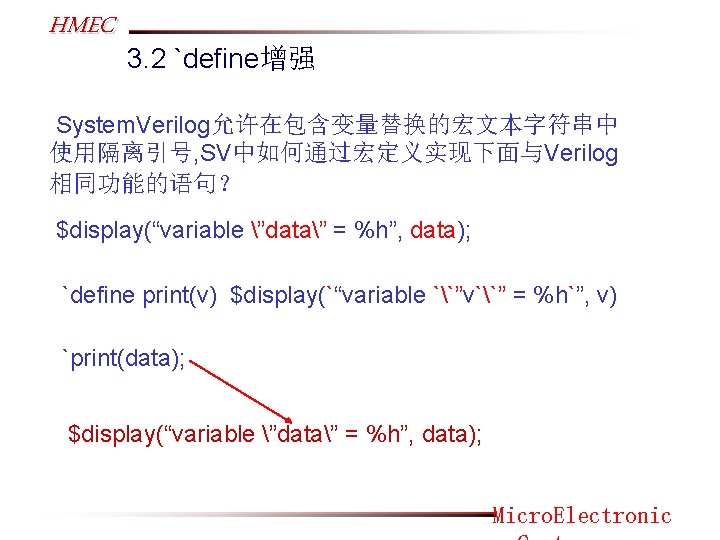

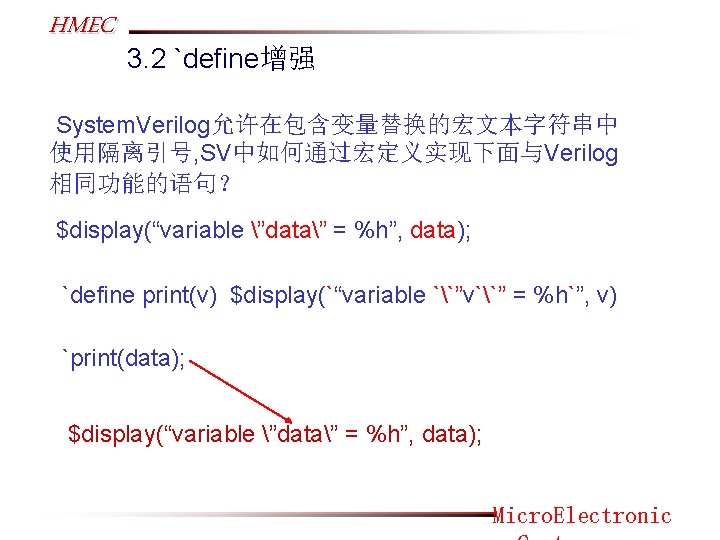

HMEC 3. 2 `define增强 Verilog允许在`define宏中使用双引号,但是双引号内 的文本变成了文本串,即在verilog中不能采用在字符串 中嵌入宏变量的文本替换宏创建字符串 `define print(v) $display(“variable v = %h”, v) `print(data); // $display(“variable v = %h”, data); System. Verilog允许字符串内的宏变量替换! `define print(v) $display(`“variable v = %h`”, v) `print(data); // $display(“variable data = %h”, data); Micro. Electronic

HMEC 3. 2 `define增强 System. Verilog允许在包含变量替换的宏文本字符串中 使用隔离引号, SV中如何通过宏定义实现下面与Verilog 相同功能的语句? $display(“variable ”data” = %h”, data); `define print(v) $display(`“variable ``”v``” = %h`”, v) `print(data); $display(“variable ”data” = %h”, data); Micro. Electronic

HMEC 3. 2 `define增强 System. Verilog可以提供了一个不引入空格的方法,通 过使用两个连续的重音符号,使两个或多个文本宏连接 成一个新名字 bit d 00_bit; wand d 00_net = d 00_bit; bit d 01_bit; wand d 01_net = d 01_bit; …. . bit d 62_bit; wand d 62_net = d 62_bit; bit d 63_bit; wand d 63_net = d 63_bit; `define TWO_STATE_NET(name) bit name``_bit; wand name``_net = name``_bit; `TWO_STATE_NET(d 00); Micro. Electronic

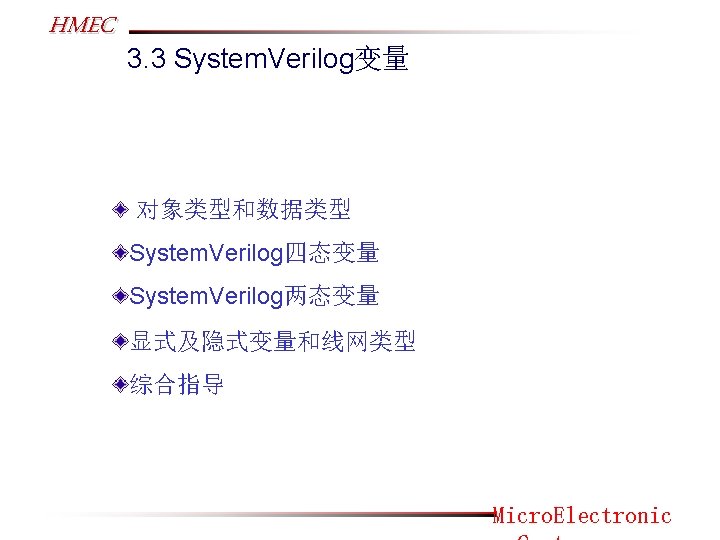

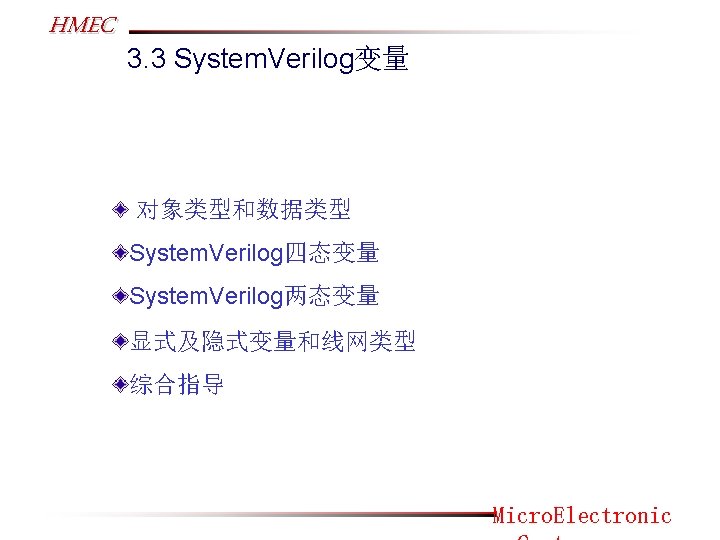

HMEC 3. 3 System. Verilog变量 对象类型和数据类型 System. Verilog四态变量 System. Verilog两态变量 显式及隐式变量和线网类型 综合指导 Micro. Electronic

HMEC 3. 3. 2 System. Verilog四态变量 System. Verilog用logic关键字描述通用的针对硬件的数 据类型,logic数据类型变量与Verilog中的reg类型是大 多数情况下可以互换使用 logic类型变量声明: logic reset. N; //一位四态变量 logic [63 : 0] data; //64位宽变量 logic [0 : 7] array [0 : 255]; //8位数组变量 显式变量或线网声明: var logic [63 : 0] addr; //64位宽变量 wire logic [63 : 0] addr; //64位宽线网 Why logic? Micro. Electronic

![HMEC 3 3 4 显式及隐式变量和线网类型 声明语句中数据类型前没有显式指定对象类型时则 推断为隐式变量 logic 7 0 bus A bit HMEC 3. 3. 4 显式及隐式变量和线网类型 声明语句中,数据类型前没有显式指定对象类型时,则 推断为隐式变量 logic [7 : 0] bus. A; bit](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-12.jpg)

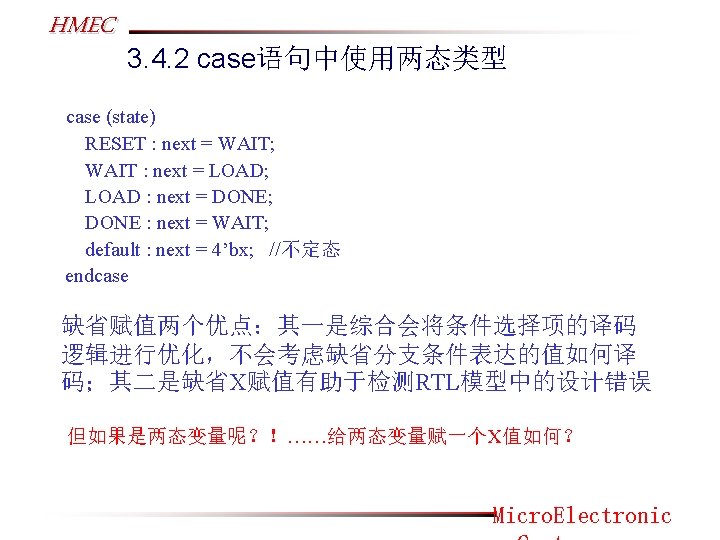

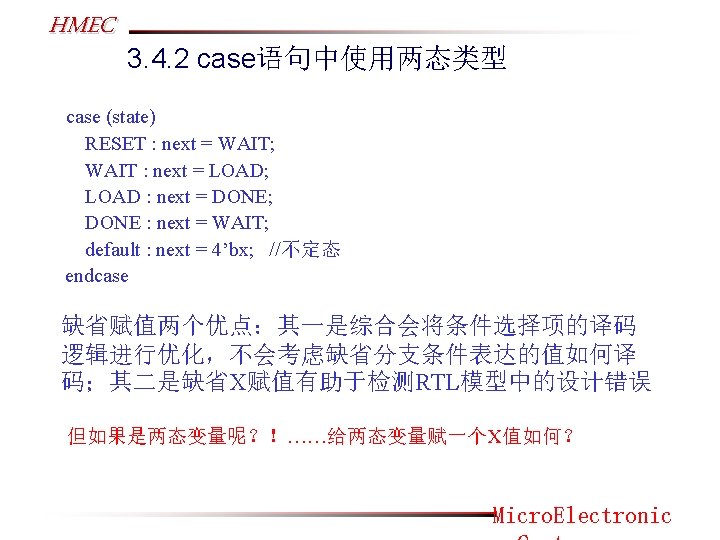

HMEC 3. 3. 4 显式及隐式变量和线网类型 声明语句中,数据类型前没有显式指定对象类型时,则 推断为隐式变量 logic [7 : 0] bus. A; bit [31 : 0] bus. B; var logic [7 : 0] ; var bit [31 : 0] b; 1. 两态线网问题 2. wire reg [31 : 0] bus. D; typedef enum bit {FALSE, TRUE} bool_t; var bool_t c; var [7 : 0] d; //四态8位变量 wire [31 : 0] bus. B; //隐含为四态逻辑数据类型 wire logic [31 : 0] bus. C; Micro. Electronic

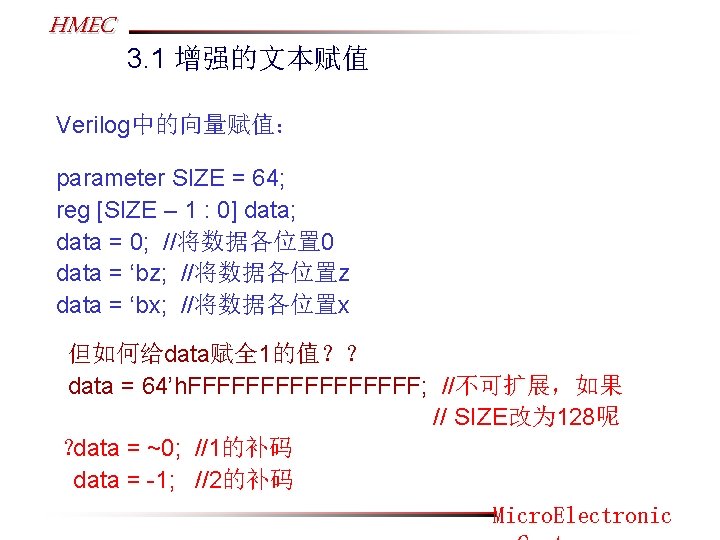

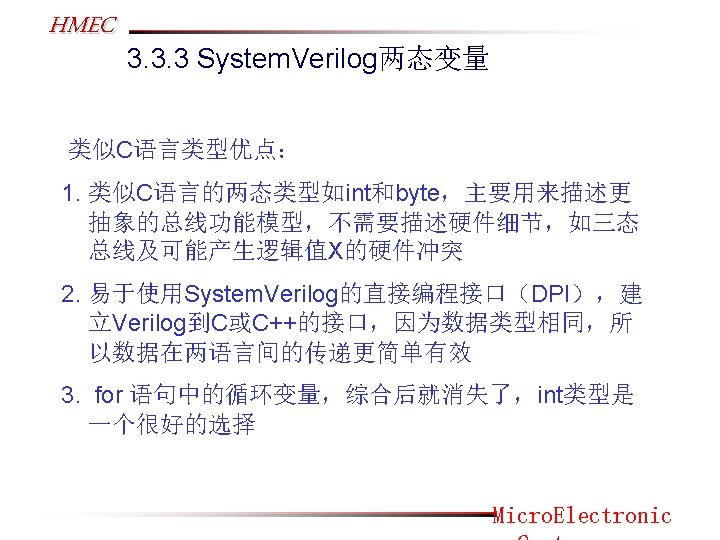

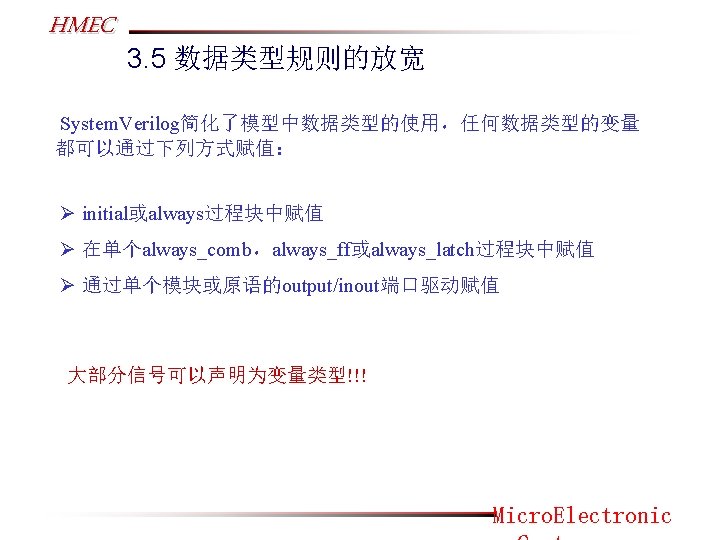

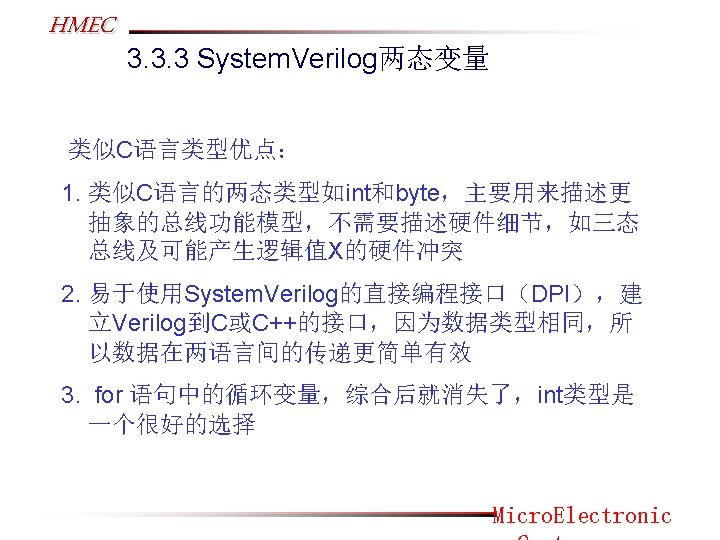

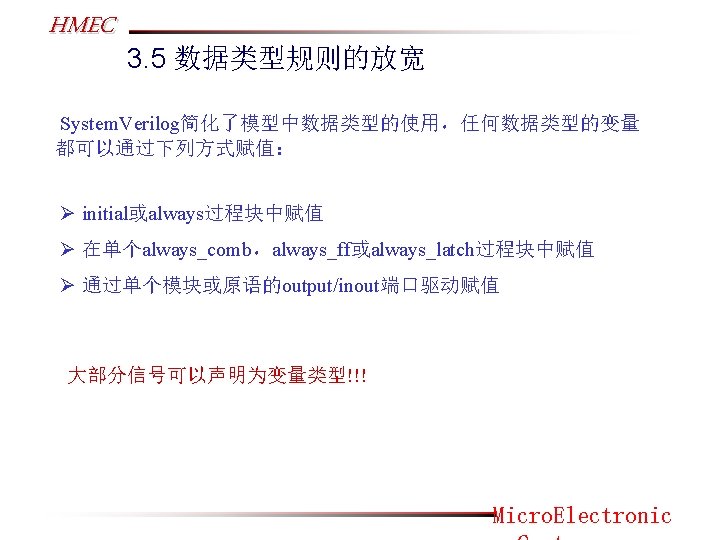

HMEC 3. 5 数据类型规则的放宽 module compare(output logic lt, eq, gt, input logic [63 : 0] a, b); always @(a, b) if (a < b) lt = 1’b 1; //过程赋值 else lt = 1’b 0; assign gt = (a > b); //连续赋值 comparator u 1(eq, a, b); //模块例化 endmodule comparator(output logic eq, input logic [63 : 0 ] a, b); always @(a, b) eq = (a == b); endmodule Micro. Electronic

![HMEC 3 5 数据类型规则的放宽 对变量使用的限制可以防止设计错误多个输出端口驱动一个变量 对一个变量进行多次连续赋值对同一个变量同时进行过程赋值和 连续赋值 module addandincrementoutput logic 63 0 sum HMEC 3. 5 数据类型规则的放宽 对变量使用的限制可以防止设计错误:多个输出端口驱动一个变量; 对一个变量进行多次连续赋值;对同一个变量同时进行过程赋值和 连续赋值 module add_and_increment(output logic [63 : 0] sum,](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-18.jpg)

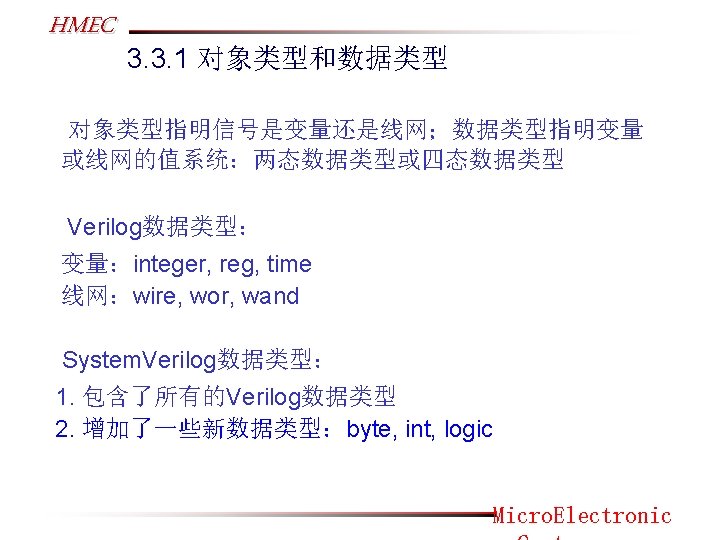

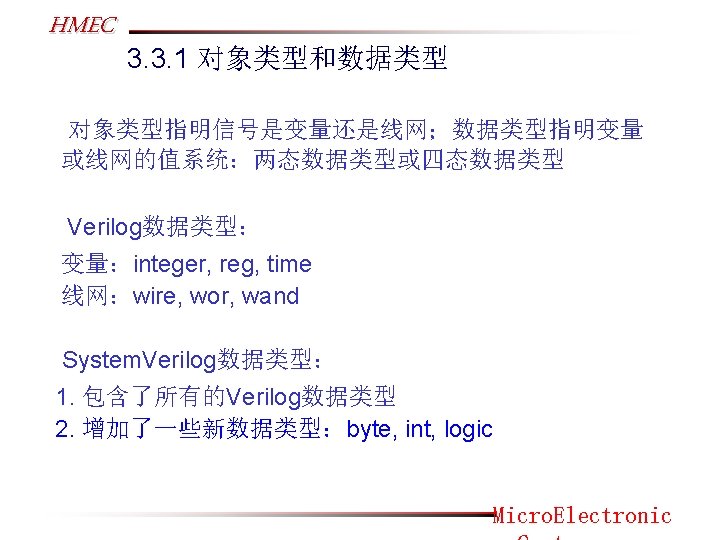

HMEC 3. 5 数据类型规则的放宽 对变量使用的限制可以防止设计错误:多个输出端口驱动一个变量; 对一个变量进行多次连续赋值;对同一个变量同时进行过程赋值和 连续赋值 module add_and_increment(output logic [63 : 0] sum, output logic carry, input logic [63 : 0] a, b); always @(a, b) sum = a + b; //过程赋值 assign sum = sum + 1; //error, sum已经被过程赋值一次 look_ahead i 1(carry, a, b); //carry被驱动一次 overflow_check i 2(carry, a, b); //error, carry再一次被驱动 endmodule loock_ahead(output wire carry, …. endmodule overflow_check(output wire carry, …. endmodule Micro. Electronic

![HMEC 3 6 有符号和无符号修饰符 integer j verilog1995标准32位有符号数 reg 63 0 u 无符号 64位数 HMEC 3. 6 有符号和无符号修饰符 integer j; //verilog-1995标准,32位有符号数 reg [63 : 0] u; //无符号 64位数](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-19.jpg)

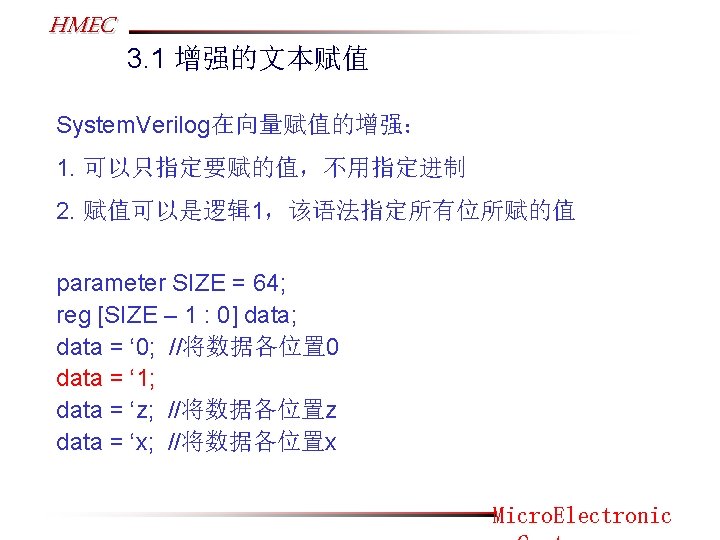

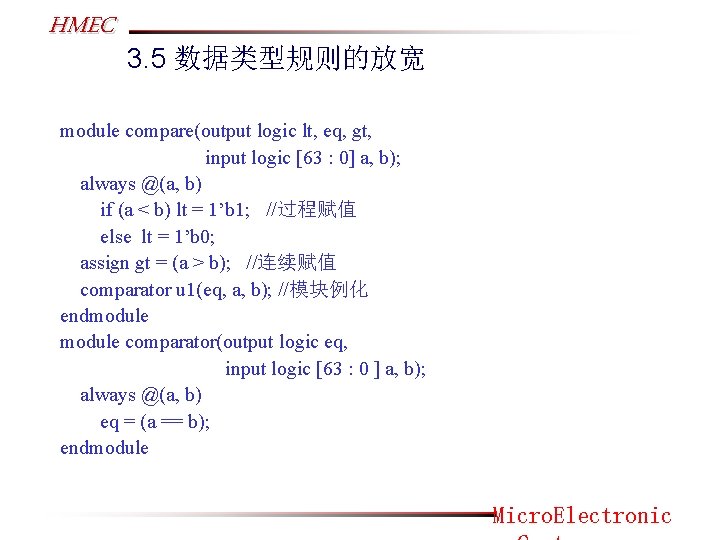

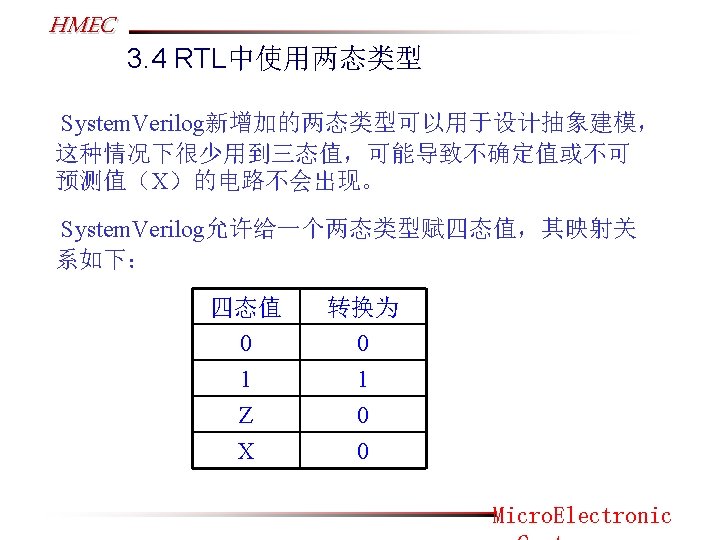

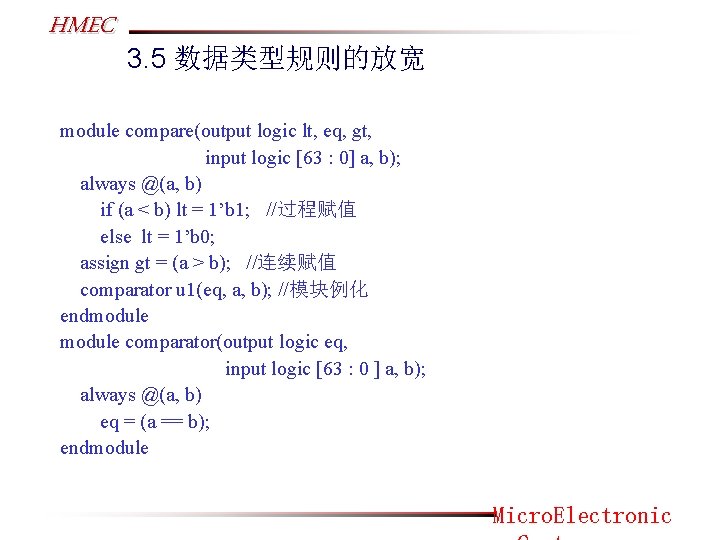

HMEC 3. 6 有符号和无符号修饰符 integer j; //verilog-1995标准,32位有符号数 reg [63 : 0] u; //无符号 64位数 reg signed [63 : 0] s; //有符号 64位数,verilog-2001标准 System. Verilog增加了缺省为有符号数的数据类型:byte, shortint, int 和longint s_int; //有符号 32位变量 int unsigned u_int; //无符号 32位变量 与verilog相同,System. Verilog只能在类型关键字后面指定signed或 unsigned关键字,与C语言不同! Micro. Electronic

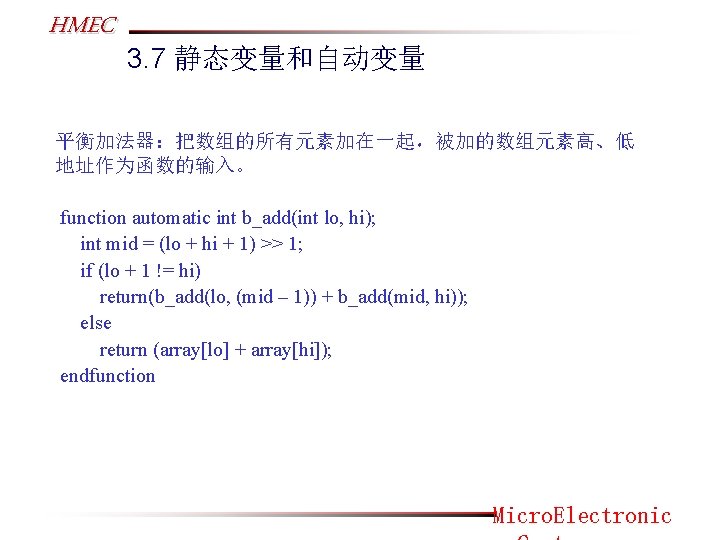

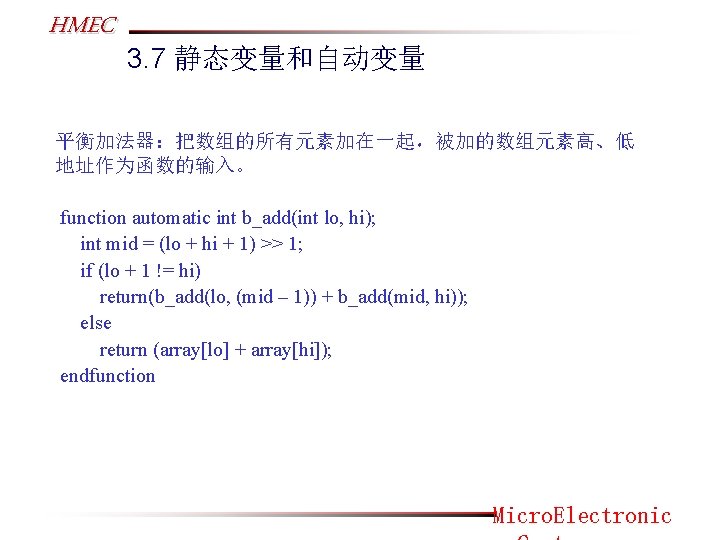

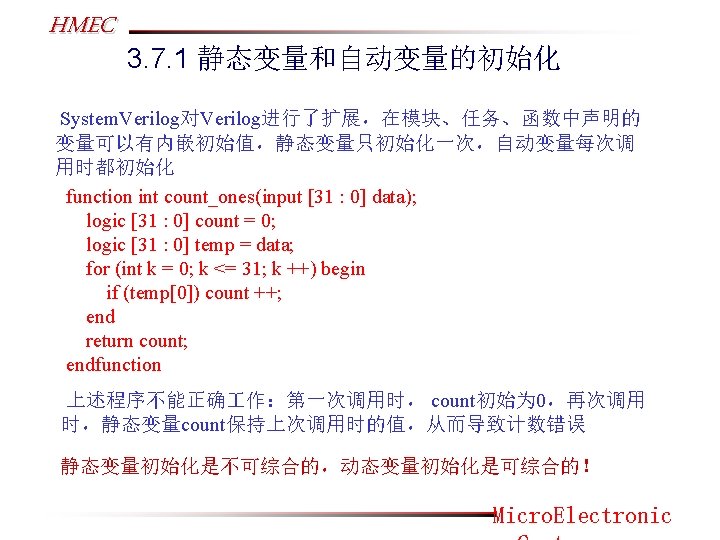

HMEC 3. 7 静态变量和自动变量 平衡加法器:把数组的所有元素加在一起,被加的数组元素高、低 地址作为函数的输入。 function automatic int b_add(int lo, hi); int mid = (lo + hi + 1) >> 1; if (lo + 1 != hi) return(b_add(lo, (mid – 1)) + b_add(mid, hi)); else return (array[lo] + array[hi]); endfunction Micro. Electronic

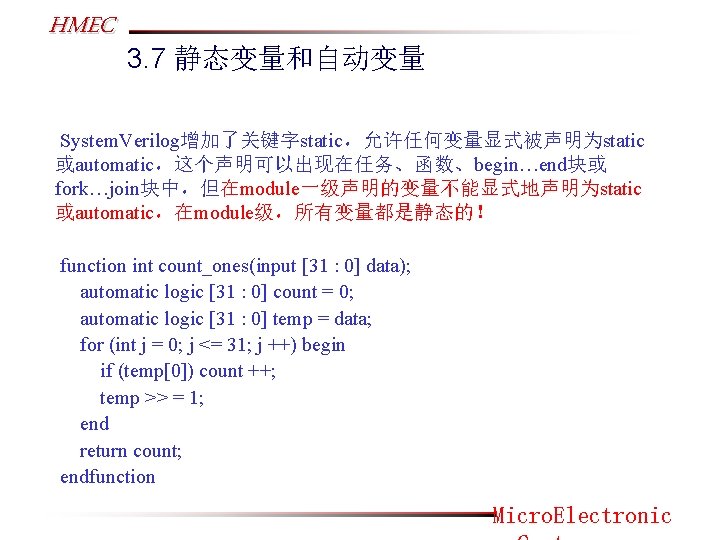

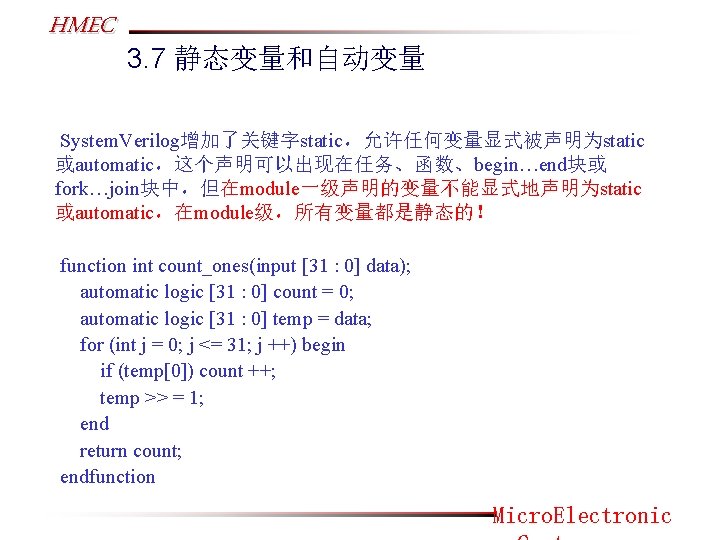

HMEC 3. 7 静态变量和自动变量 System. Verilog增加了关键字static,允许任何变量显式被声明为static 或automatic,这个声明可以出现在任务、函数、begin…end块或 fork…join块中,但在module一级声明的变量不能显式地声明为static 或automatic,在module级,所有变量都是静态的! function int count_ones(input [31 : 0] data); automatic logic [31 : 0] count = 0; automatic logic [31 : 0] temp = data; for (int j = 0; j <= 31; j ++) begin if (temp[0]) count ++; temp >> = 1; end return count; endfunction Micro. Electronic

HMEC 3. 7 静态变量和自动变量 检查程序运行总错误数任务: typedef struct packed {…} packet_t; task automatic check_results(input packet_t sent, received, output int total_errors); static int error_count = 0; … if (sent !== received) error_count ++; total_errors = error_count; endtask System. Verilog缺省存储方式与Verilog兼容,在模块、begin…end块、 fork…join块以及非自动任务和函数中,缺省存储方式为静态的,如 果一个任务和函数被声明自动的,则缺省存储方式的自动的。 Micro. Electronic

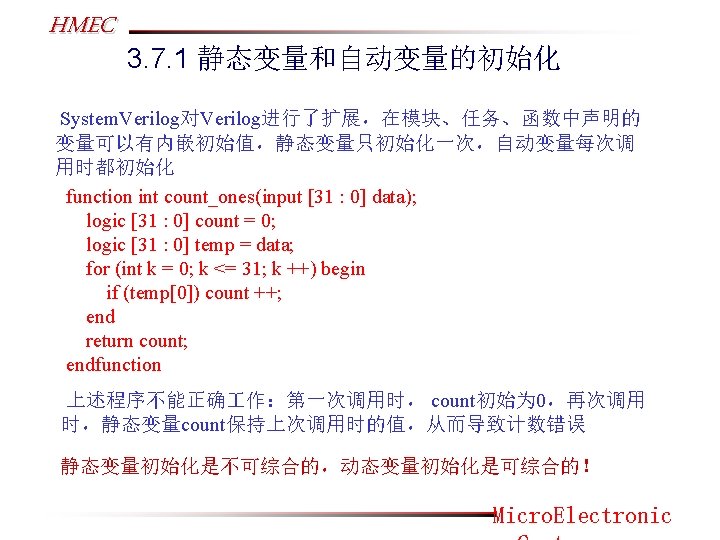

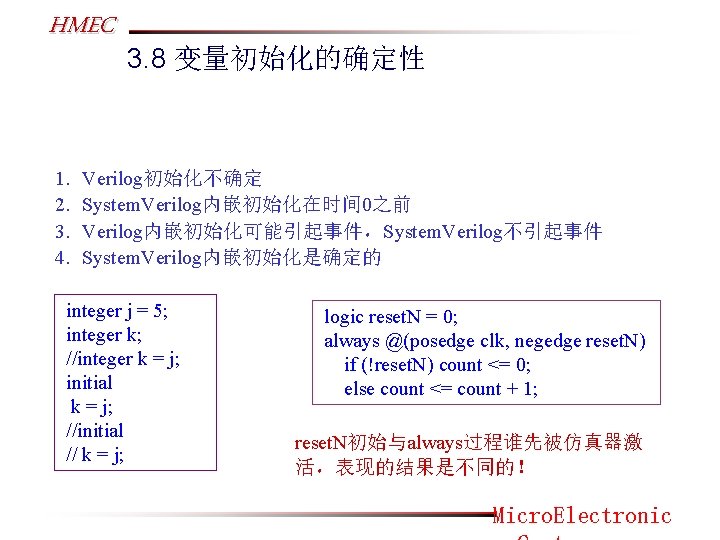

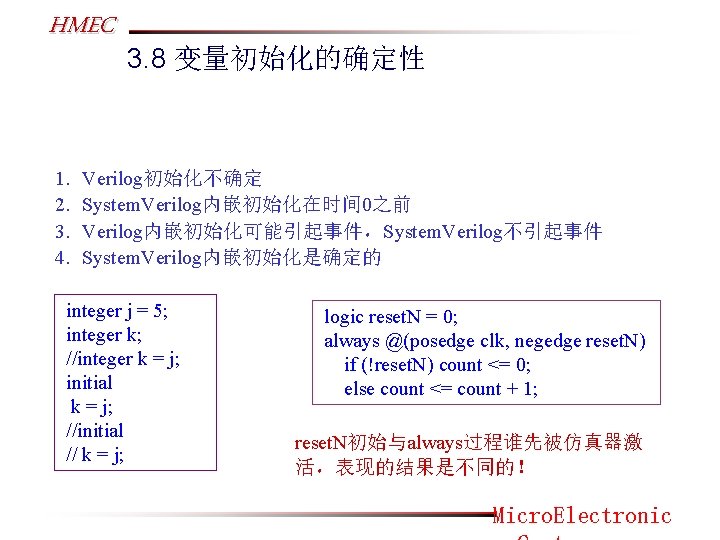

HMEC 1. 2. 3. 4. 3. 8 变量初始化的确定性 Verilog初始化不确定 System. Verilog内嵌初始化在时间 0之前 Verilog内嵌初始化可能引起事件,System. Verilog不引起事件 System. Verilog内嵌初始化是确定的 integer j = 5; integer k; //integer k = j; initial k = j; //initial // k = j; logic reset. N = 0; always @(posedge clk, negedge reset. N) if (!reset. N) count <= 0; else count <= count + 1; reset. N初始与always过程谁先被仿真器激 活,表现的结果是不同的! Micro. Electronic

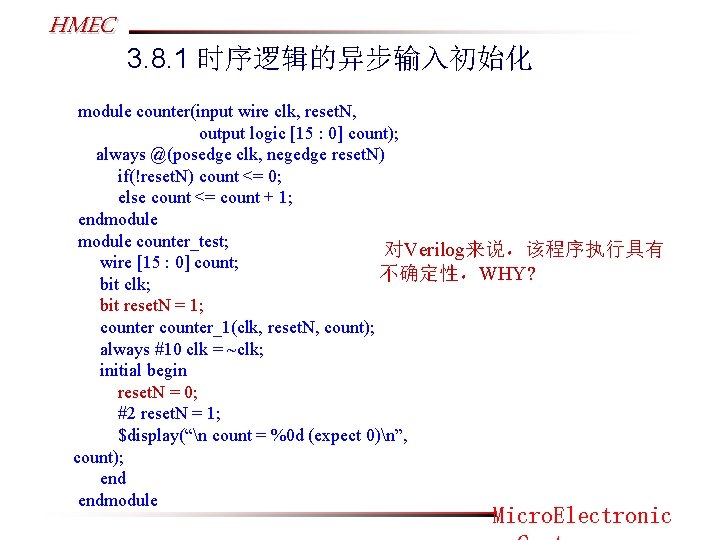

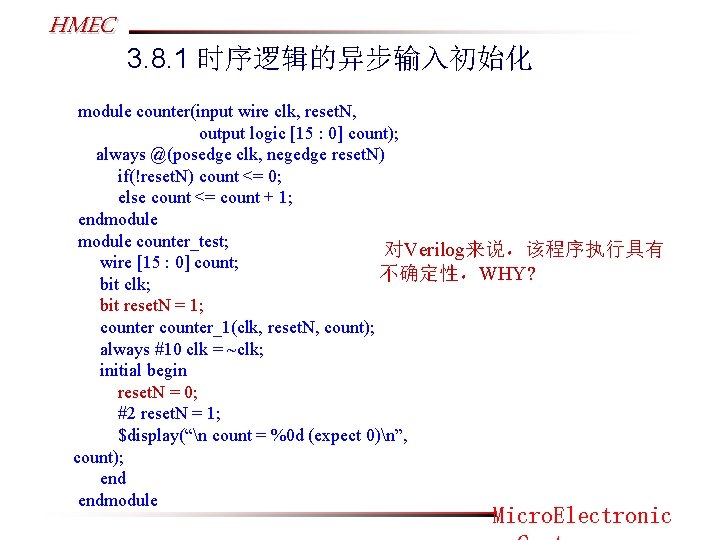

HMEC 3. 8. 1 时序逻辑的异步输入初始化 module counter(input wire clk, reset. N, output logic [15 : 0] count); always @(posedge clk, negedge reset. N) if(!reset. N) count <= 0; else count <= count + 1; endmodule counter_test; 对Verilog来说,该程序执行具有 wire [15 : 0] count; 不确定性,WHY? bit clk; bit reset. N = 1; counter_1(clk, reset. N, count); always #10 clk = ~clk; initial begin reset. N = 0; #2 reset. N = 1; $display(“n count = %0 d (expect 0)n”, count); endmodule Micro. Electronic

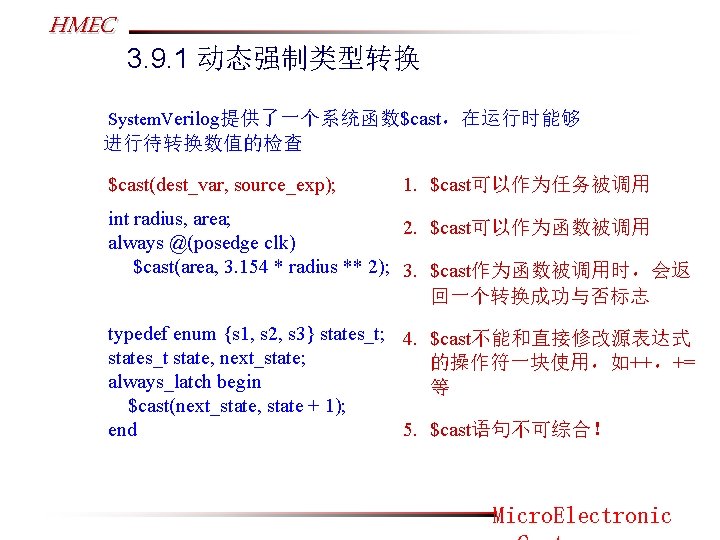

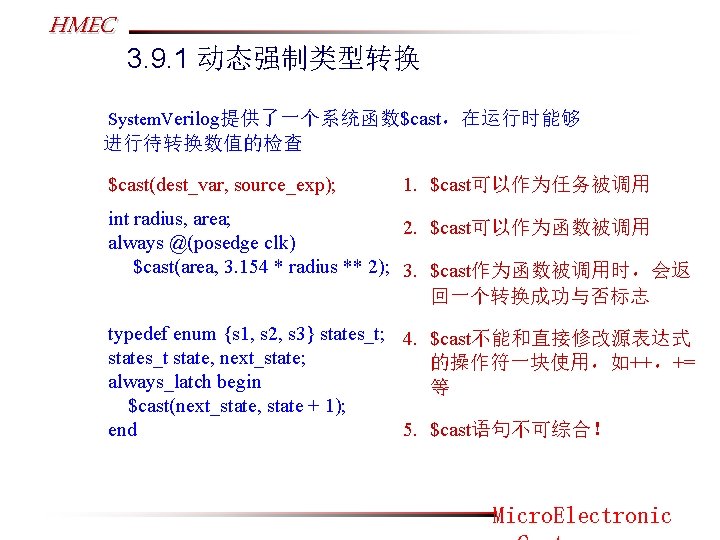

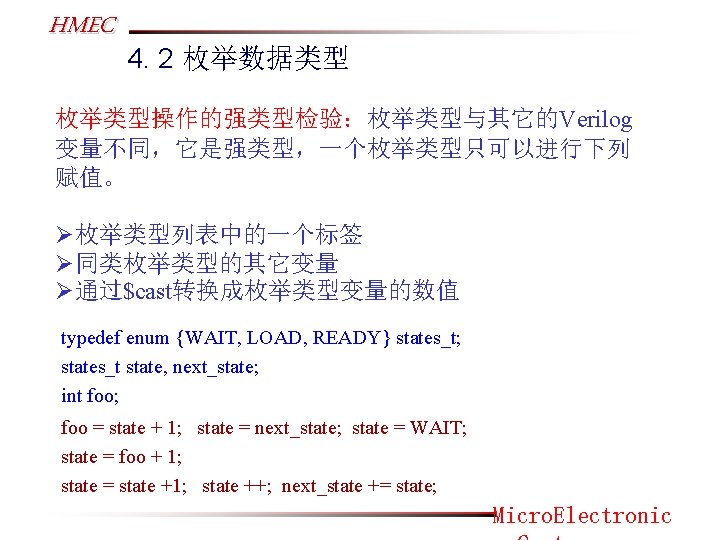

HMEC 3. 9. 1 动态强制类型转换 System. Verilog提供了一个系统函数$cast,在运行时能够 进行待转换数值的检查 $cast(dest_var, source_exp); 1. $cast可以作为任务被调用 int radius, area; 2. $cast可以作为函数被调用 always @(posedge clk) $cast(area, 3. 154 * radius ** 2); 3. $cast作为函数被调用时,会返 回一个转换成功与否标志 typedef enum {s 1, s 2, s 3} states_t; 4. $cast不能和直接修改源表达式 states_t state, next_state; 的操作符一块使用,如++,+= always_latch begin 等 $cast(next_state, state + 1); 5. $cast语句不可综合! end Micro. Electronic

![HMEC 3 10 常数 System Verilog加入了一个类似C语言风格的const声明 可以将任何变量声明为常数有确立完成之后才被赋值 并且可以在自动任务或函数beginendforkjoin中 声明 const logic 23 0 HMEC 3. 10 常数 System. Verilog加入了一个类似C语言风格的const声明, 可以将任何变量声明为常数,有确立完成之后才被赋值, 并且可以在自动任务或函数、begin…end、fork…join中 声明 const logic [23 : 0]](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-32.jpg)

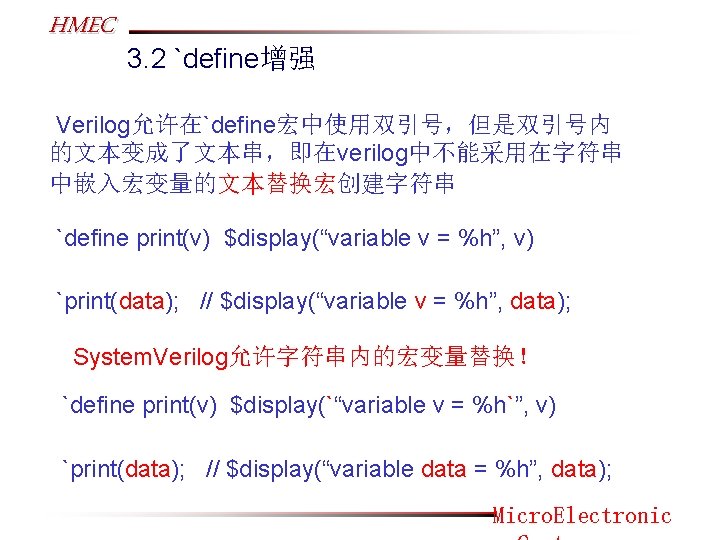

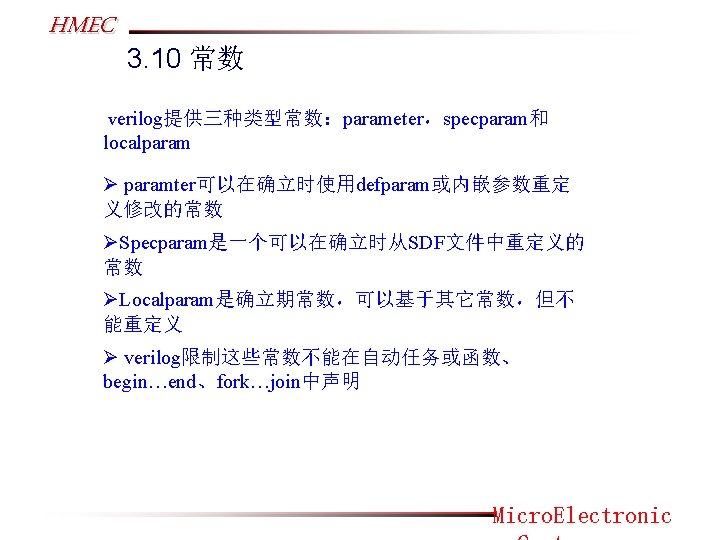

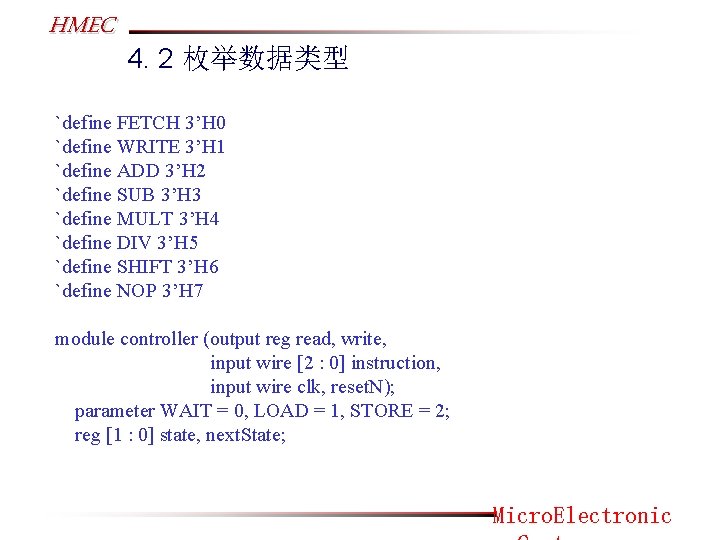

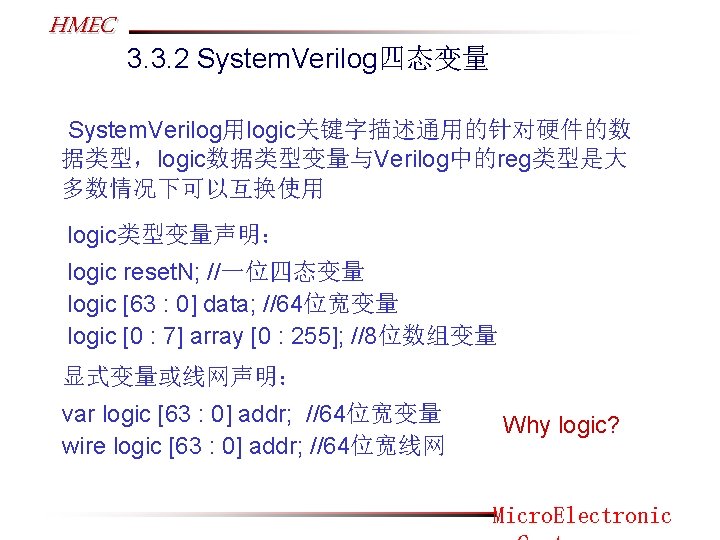

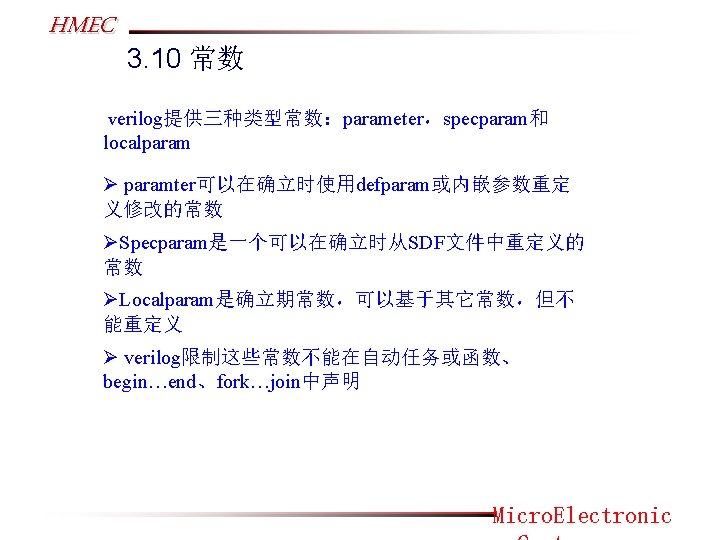

HMEC 3. 10 常数 System. Verilog加入了一个类似C语言风格的const声明, 可以将任何变量声明为常数,有确立完成之后才被赋值, 并且可以在自动任务或函数、begin…end、fork…join中 声明 const logic [23 : 0] c 1 = 7; const int c 2 = 15; const real c 3 = 3. 14; const c 4 = 5; //error, 无数据类型 task automatic C; const int N = 5; … endtask Micro. Electronic

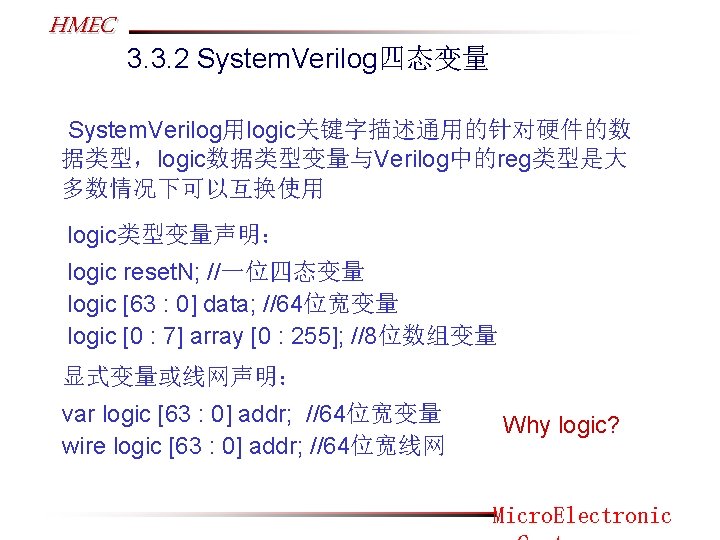

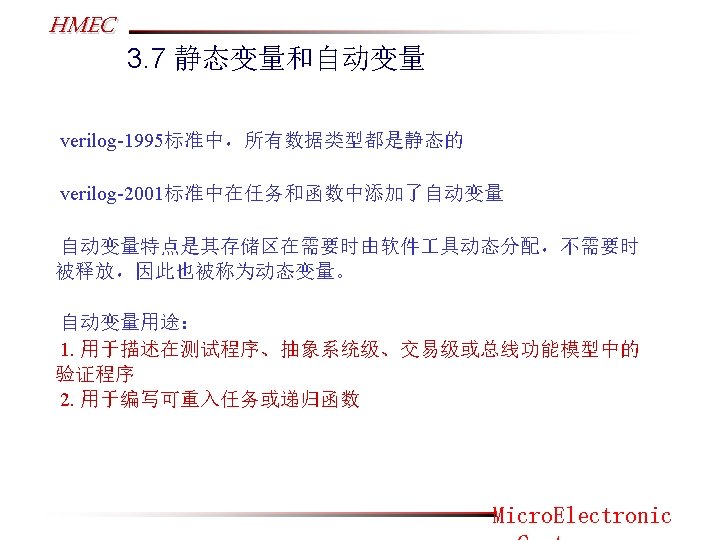

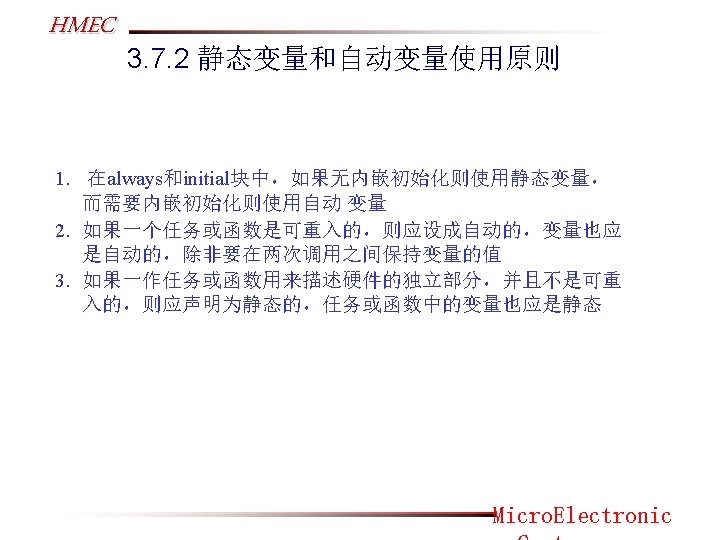

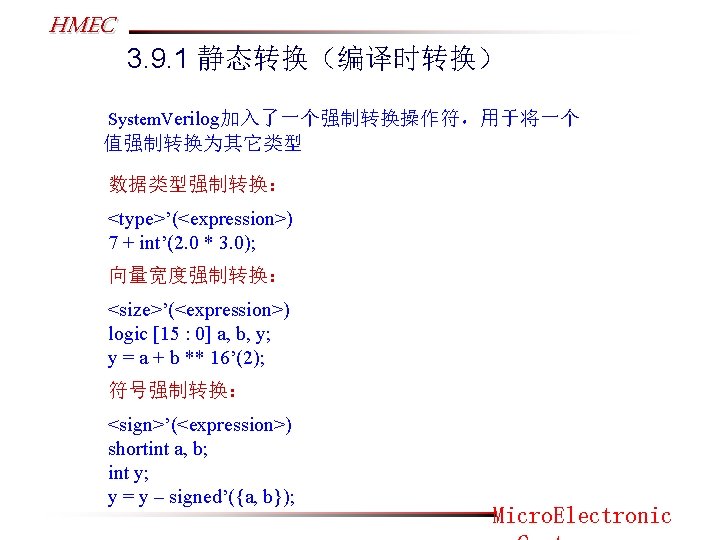

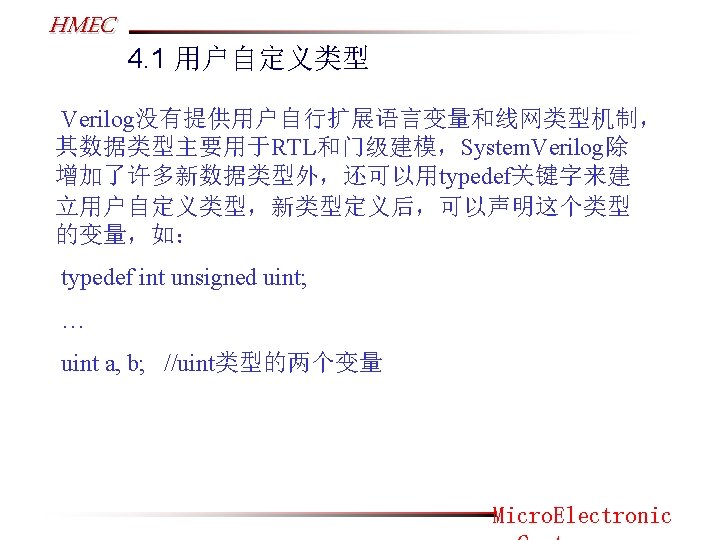

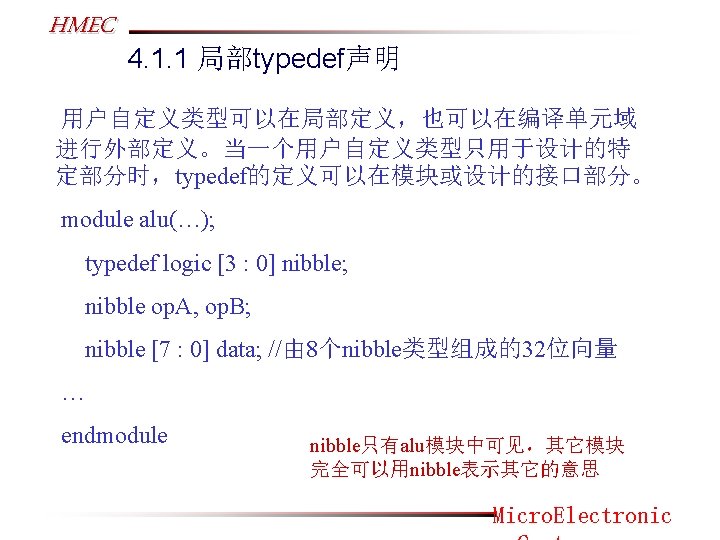

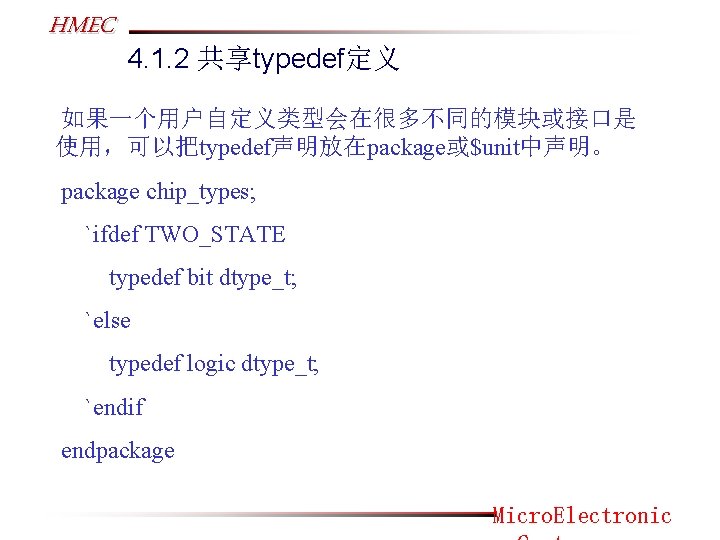

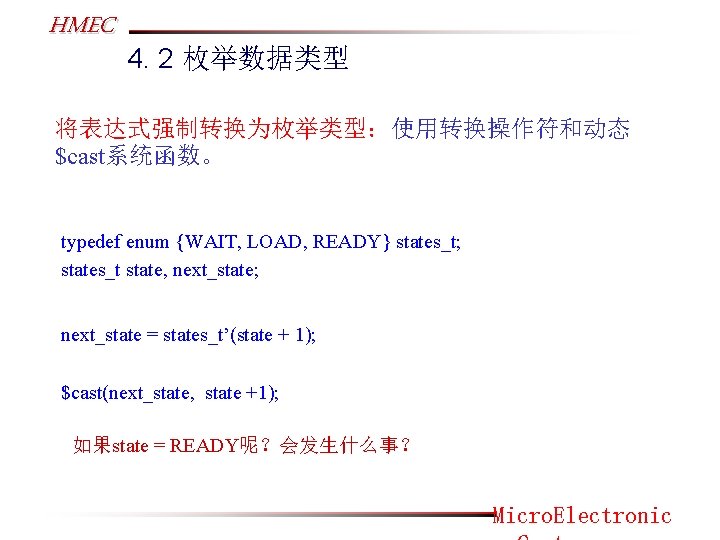

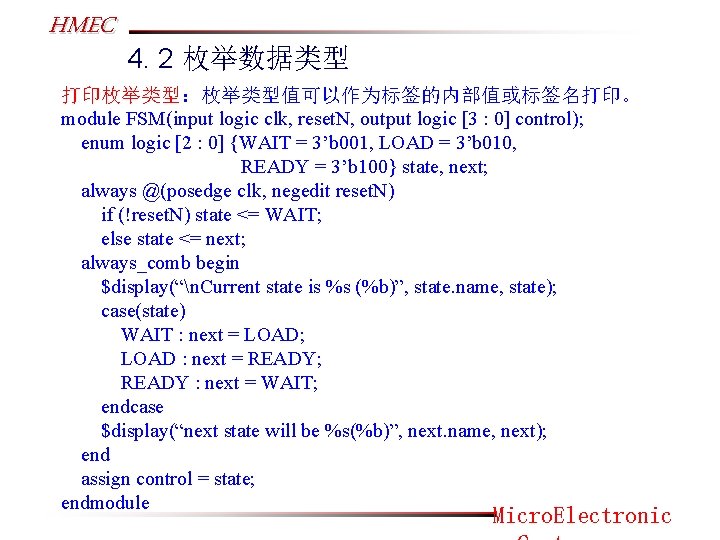

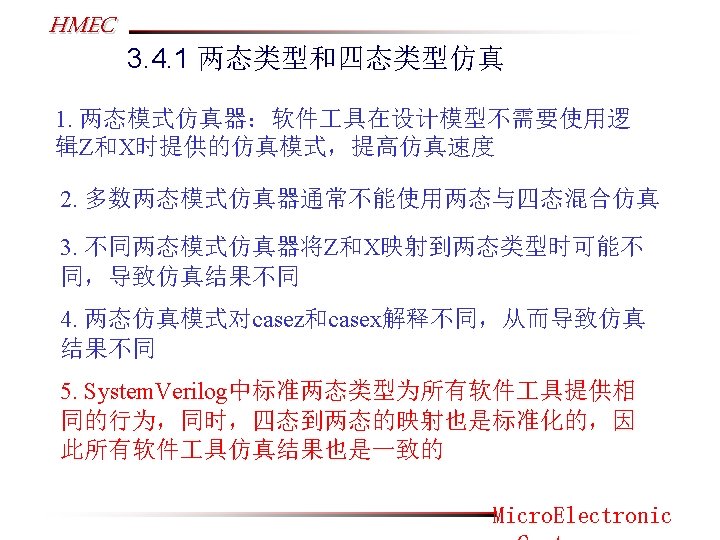

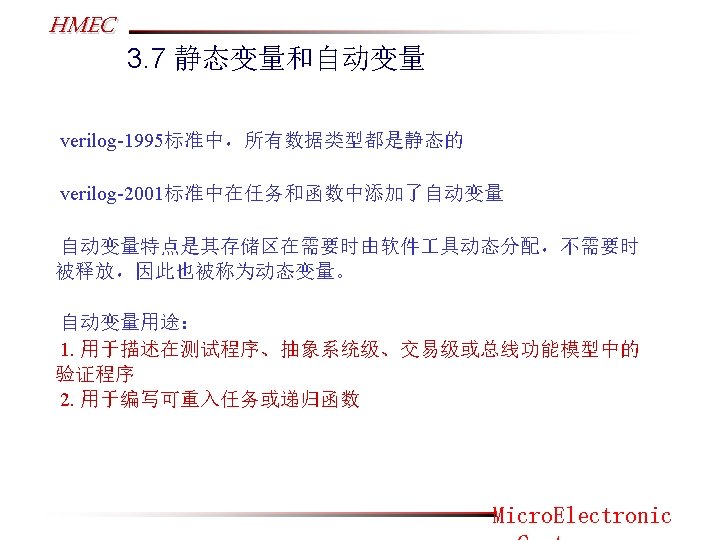

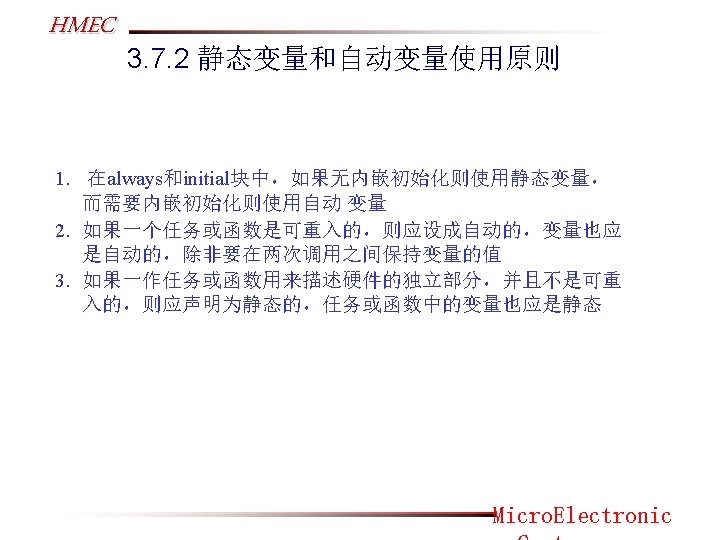

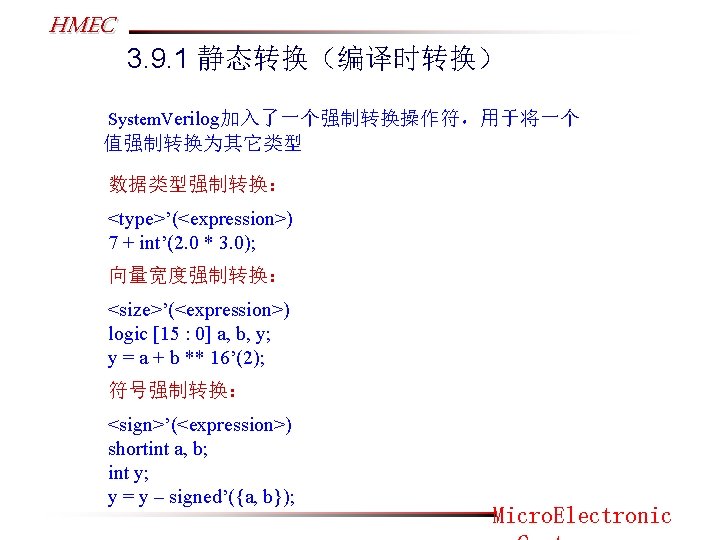

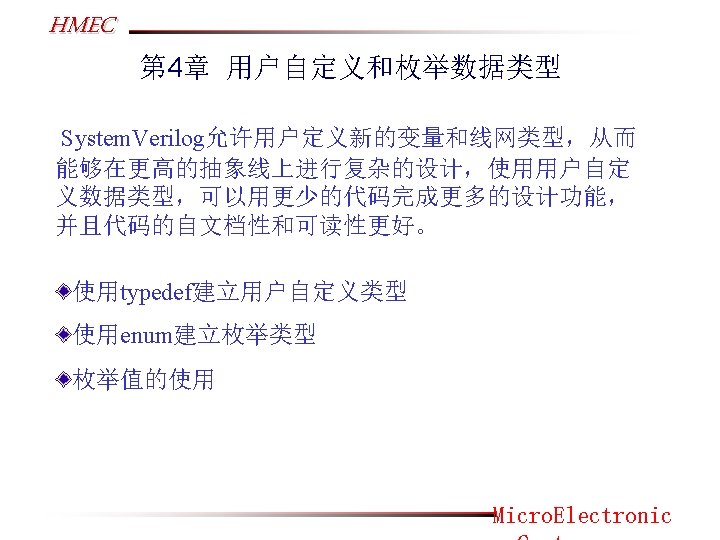

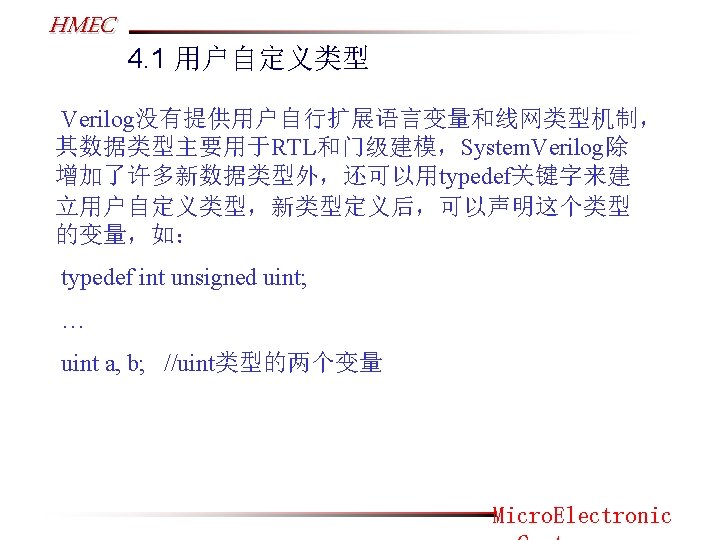

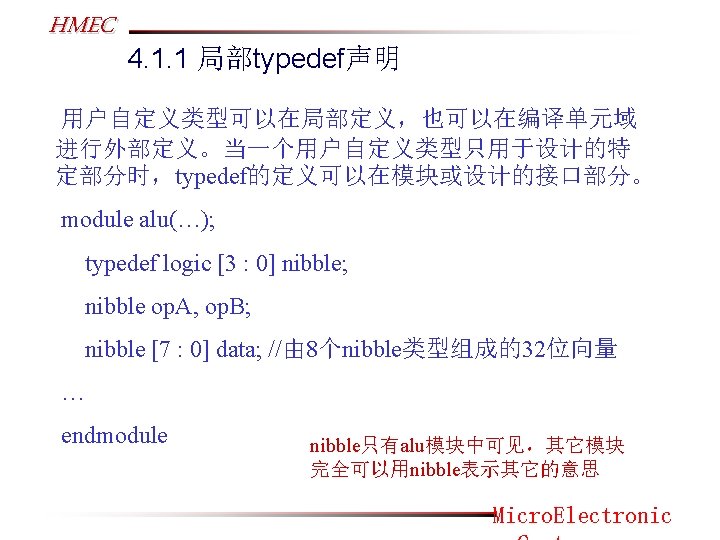

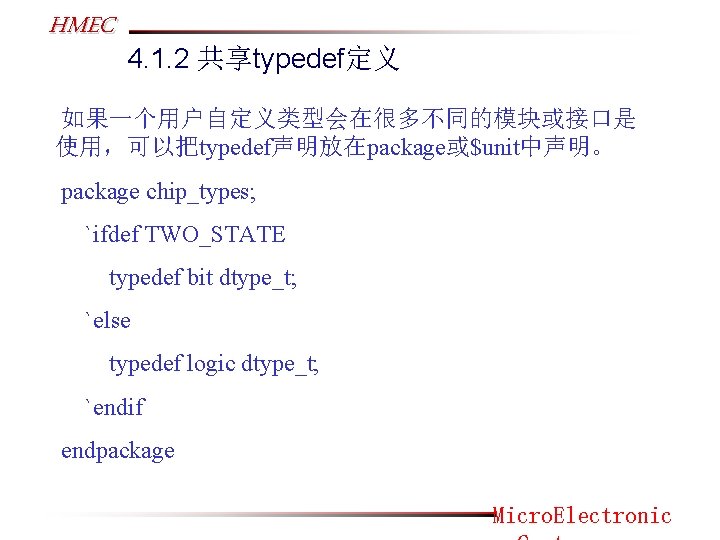

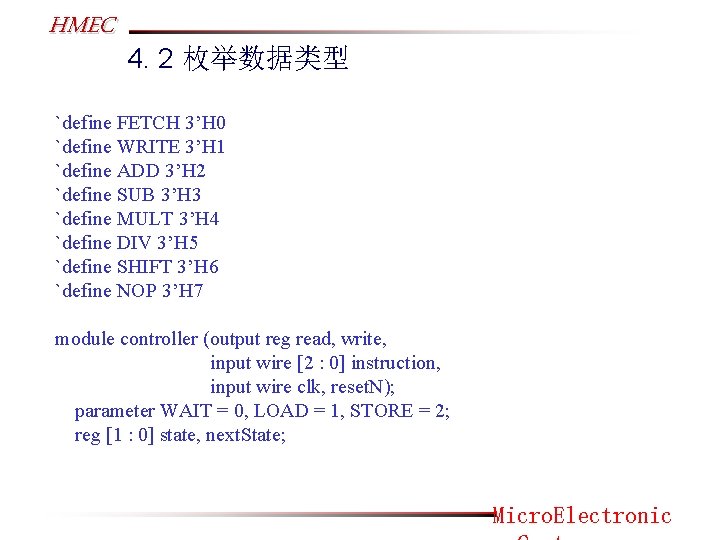

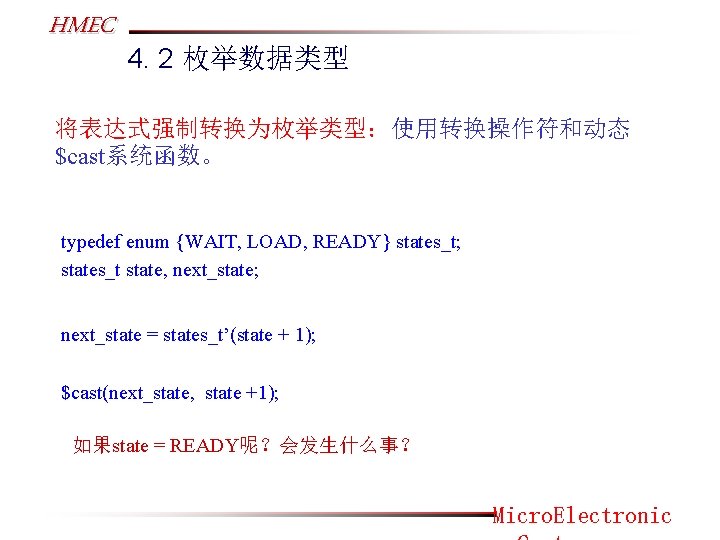

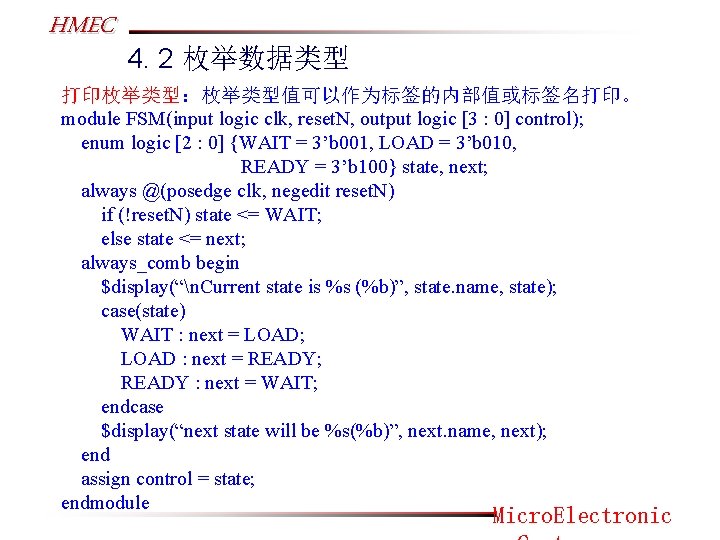

HMEC 4. 1. 2 共享typedef定义 如果一个用户自定义类型会在很多不同的模块或接口是 使用,可以把typedef声明放在package或$unit中声明。 package chip_types; `ifdef TWO_STATE typedef bit dtype_t; `else typedef logic dtype_t; `endif endpackage Micro. Electronic

![HMEC 4 1 2 共享typedef定义 module counteroutput chiptypes dtypet 15 0 HMEC 4. 1. 2 共享typedef定义 module counter(output chip_types : : dtype_t [15 : 0]](https://slidetodoc.com/presentation_image/de99ea502cf8b0ca289ecae55ccac904/image-37.jpg)

HMEC 4. 1. 2 共享typedef定义 module counter(output chip_types : : dtype_t [15 : 0] count, input chip_types : : clock, reset. N); always @(posedge clock, negedge reset. N) if (! reset. N) count <= 0; else count <= count + 1; endmodule inport chip_types : : *; module counter(output dtype_t [15 : 0] count, input clock, reset. N); always @(posedge clock, negedge reset. N) if (! reset. N) count <= 0; else count <= count + 1; endmodule Micro. Electronic

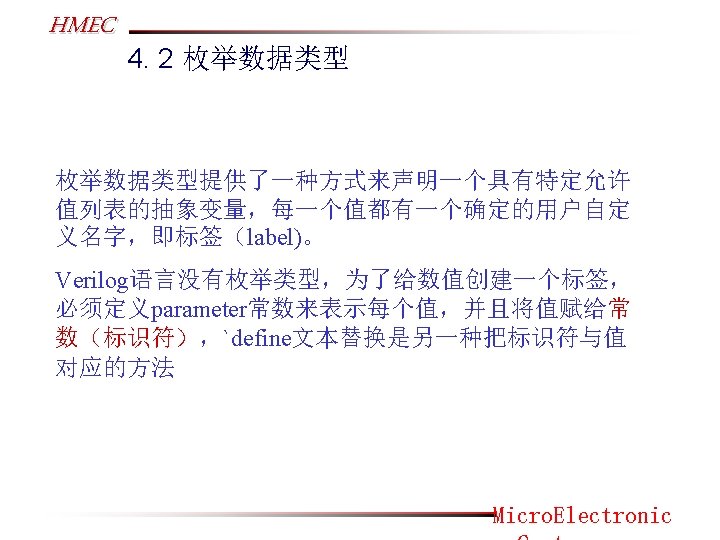

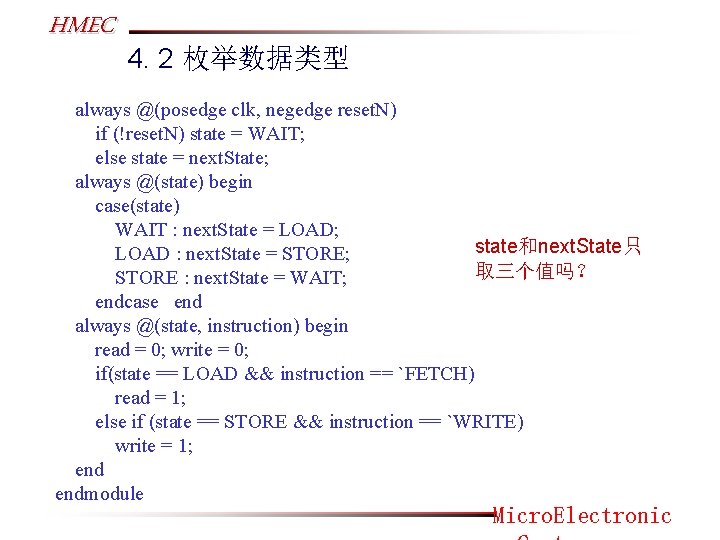

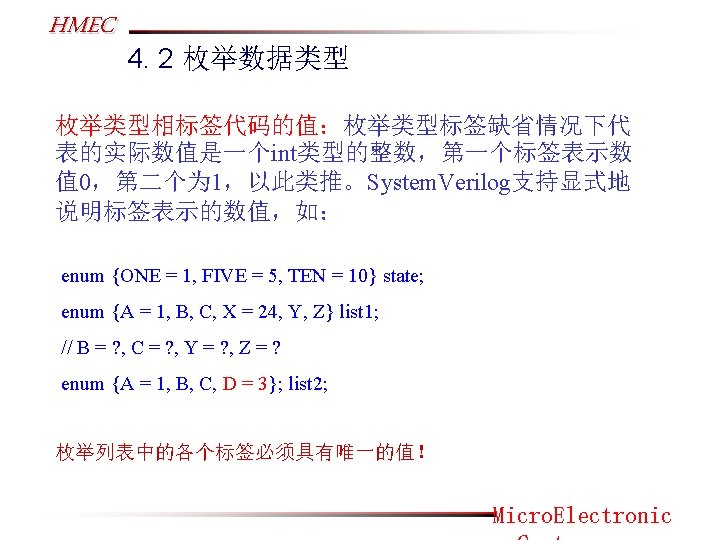

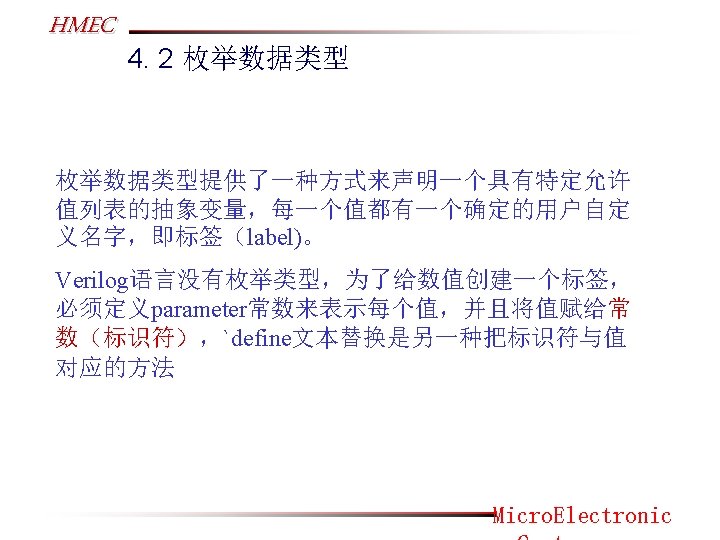

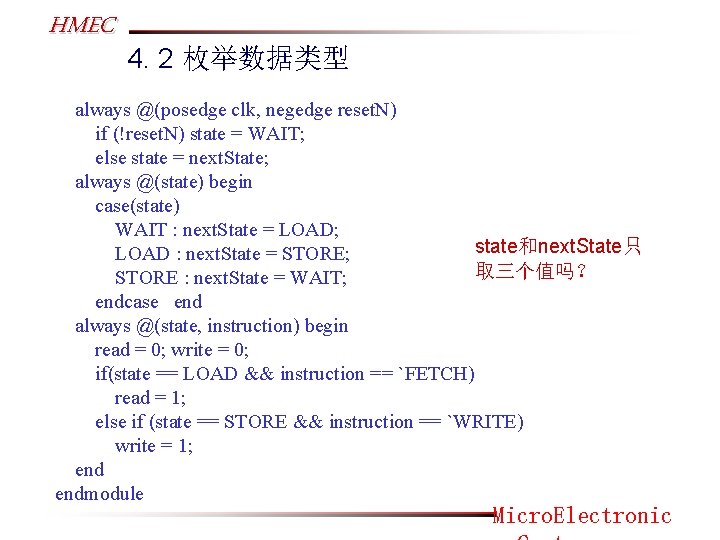

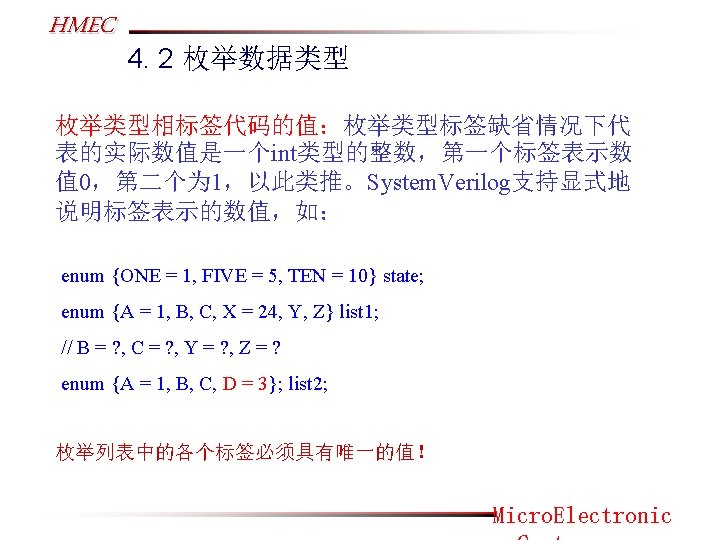

HMEC 4. 2 枚举数据类型 `define FETCH 3’H 0 `define WRITE 3’H 1 `define ADD 3’H 2 `define SUB 3’H 3 `define MULT 3’H 4 `define DIV 3’H 5 `define SHIFT 3’H 6 `define NOP 3’H 7 module controller (output reg read, write, input wire [2 : 0] instruction, input wire clk, reset. N); parameter WAIT = 0, LOAD = 1, STORE = 2; reg [1 : 0] state, next. State; Micro. Electronic

HMEC 4. 2 枚举数据类型 always @(posedge clk, negedge reset. N) if (!reset. N) state = WAIT; else state = next. State; always @(state) begin case(state) WAIT : next. State = LOAD; state和next. State只 LOAD : next. State = STORE; 取三个值吗? STORE : next. State = WAIT; endcase end always @(state, instruction) begin read = 0; write = 0; if(state == LOAD && instruction == `FETCH) read = 1; else if (state == STORE && instruction == `WRITE) write = 1; endmodule Micro. Electronic

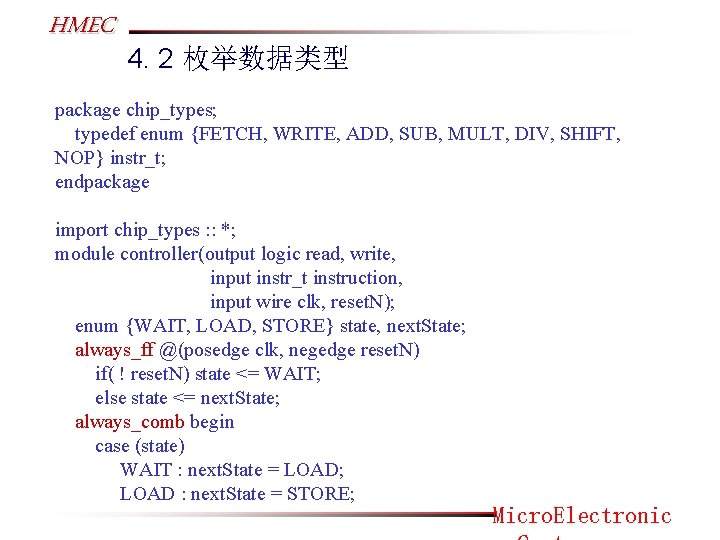

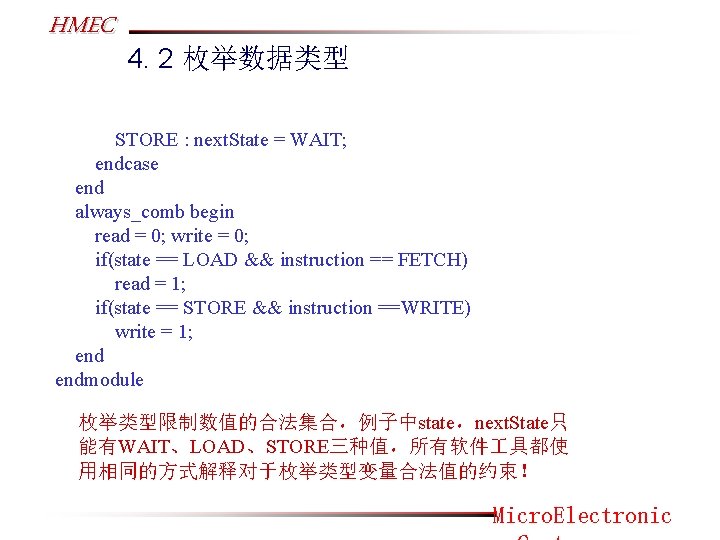

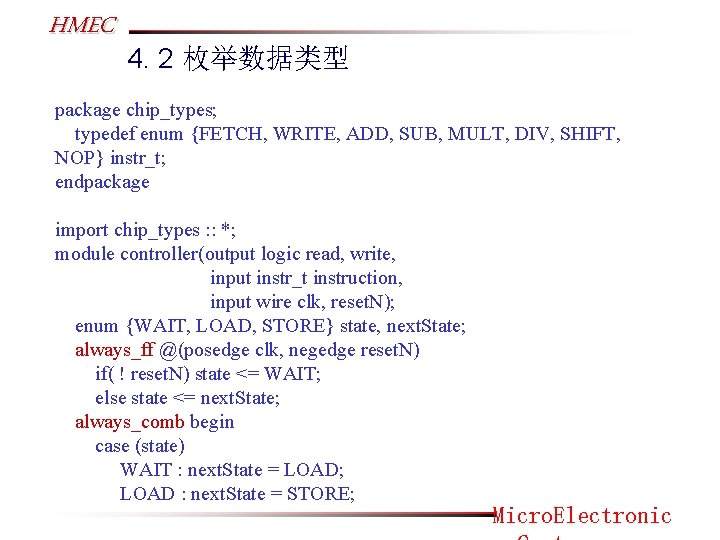

HMEC 4. 2 枚举数据类型 package chip_types; typedef enum {FETCH, WRITE, ADD, SUB, MULT, DIV, SHIFT, NOP} instr_t; endpackage import chip_types : : *; module controller(output logic read, write, input instr_t instruction, input wire clk, reset. N); enum {WAIT, LOAD, STORE} state, next. State; always_ff @(posedge clk, negedge reset. N) if( ! reset. N) state <= WAIT; else state <= next. State; always_comb begin case (state) WAIT : next. State = LOAD; LOAD : next. State = STORE; Micro. Electronic

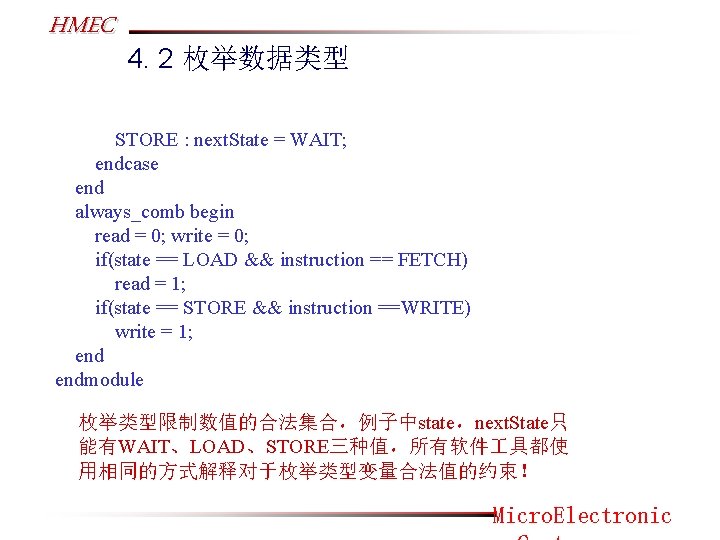

HMEC 4. 2 枚举数据类型 STORE : next. State = WAIT; endcase end always_comb begin read = 0; write = 0; if(state == LOAD && instruction == FETCH) read = 1; if(state == STORE && instruction ==WRITE) write = 1; endmodule 枚举类型限制数值的合法集合,例子中state,next. State只 能有WAIT、LOAD、STORE三种值,所有软件 具都使 用相同的方式解释对于枚举类型变量合法值的约束! Micro. Electronic

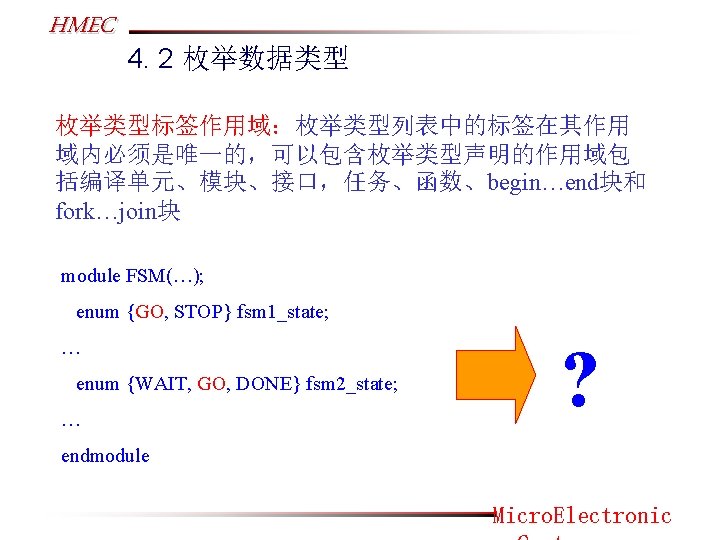

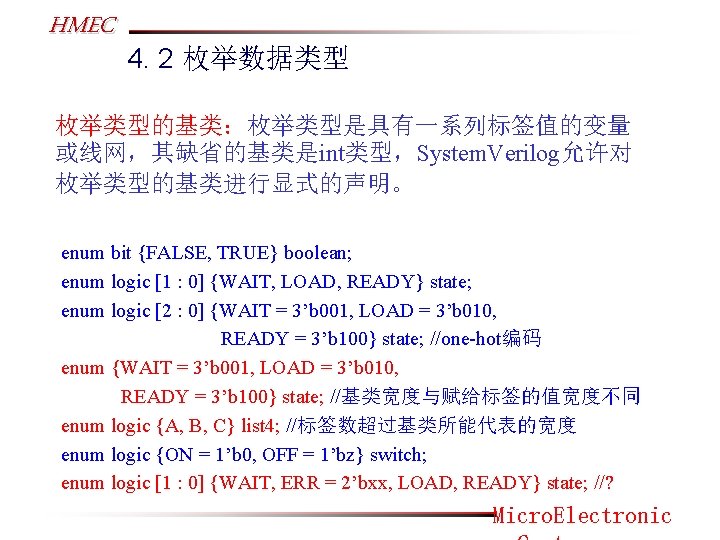

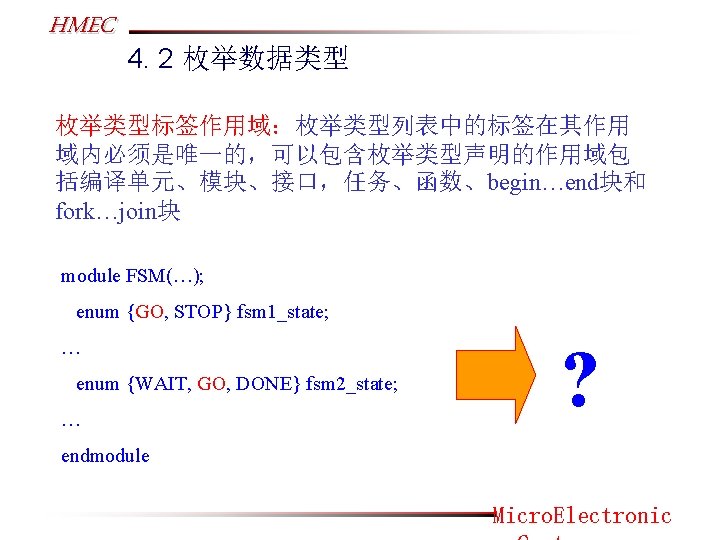

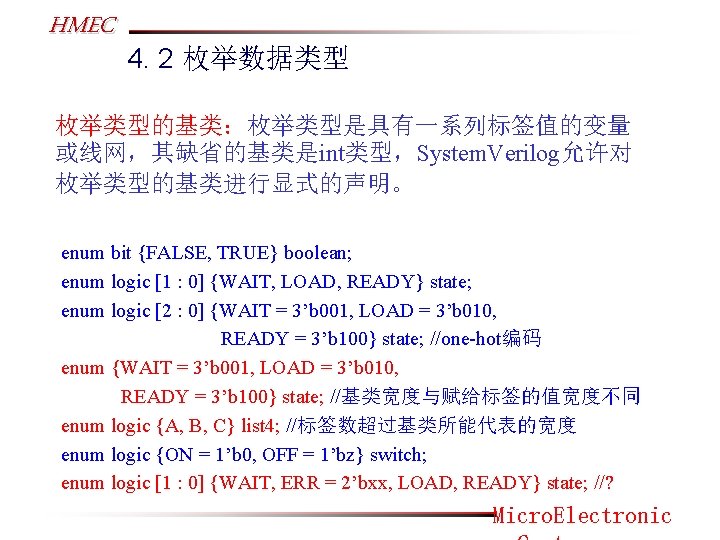

HMEC 4. 2 枚举数据类型 枚举类型的基类:枚举类型是具有一系列标签值的变量 或线网,其缺省的基类是int类型,System. Verilog允许对 枚举类型的基类进行显式的声明。 enum bit {FALSE, TRUE} boolean; enum logic [1 : 0] {WAIT, LOAD, READY} state; enum logic [2 : 0] {WAIT = 3’b 001, LOAD = 3’b 010, READY = 3’b 100} state; //one-hot编码 enum {WAIT = 3’b 001, LOAD = 3’b 010, READY = 3’b 100} state; //基类宽度与赋给标签的值宽度不同 enum logic {A, B, C} list 4; //标签数超过基类所能代表的宽度 enum logic {ON = 1’b 0, OFF = 1’bz} switch; enum logic [1 : 0] {WAIT, ERR = 2’bxx, LOAD, READY} state; //? Micro. Electronic

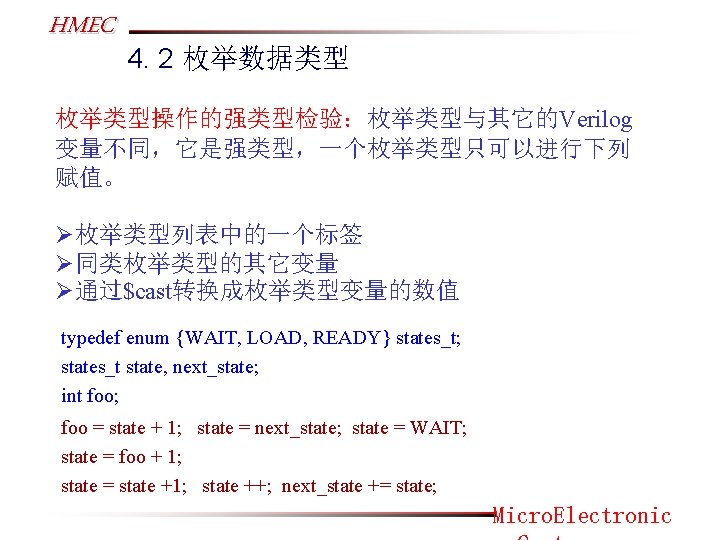

HMEC 4. 2 枚举数据类型 将表达式强制转换为枚举类型:使用转换操作符和动态 $cast系统函数。 typedef enum {WAIT, LOAD, READY} states_t; states_t state, next_state; next_state = states_t’(state + 1); $cast(next_state, state +1); 如果state = READY呢?会发生什么事? Micro. Electronic

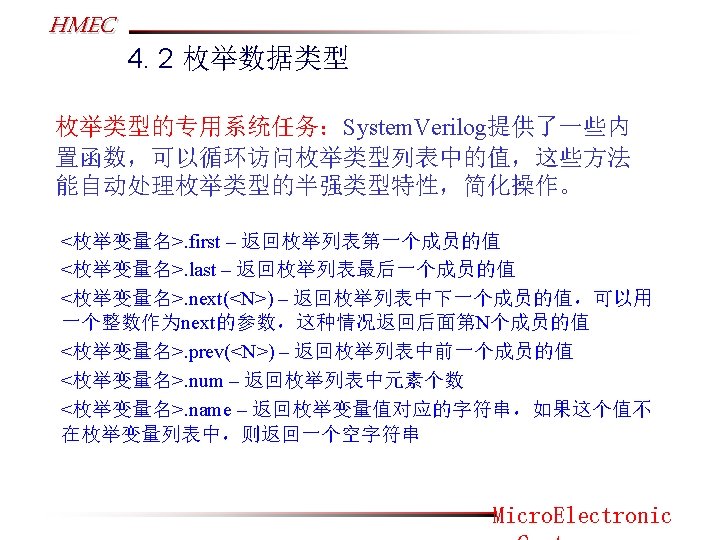

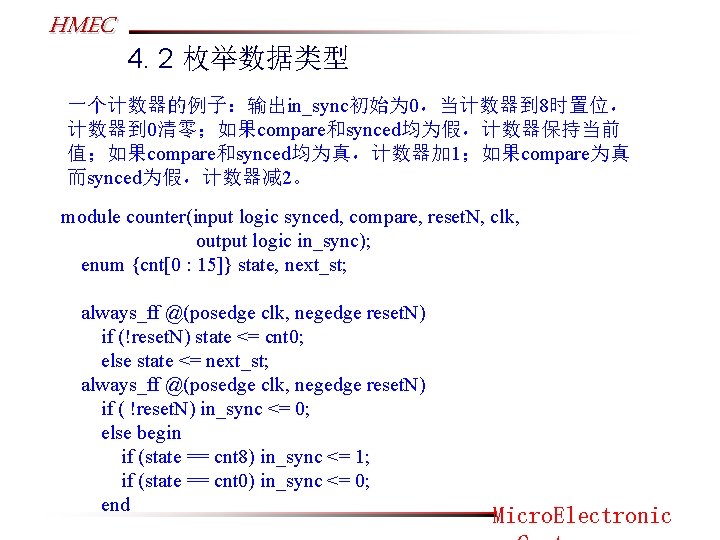

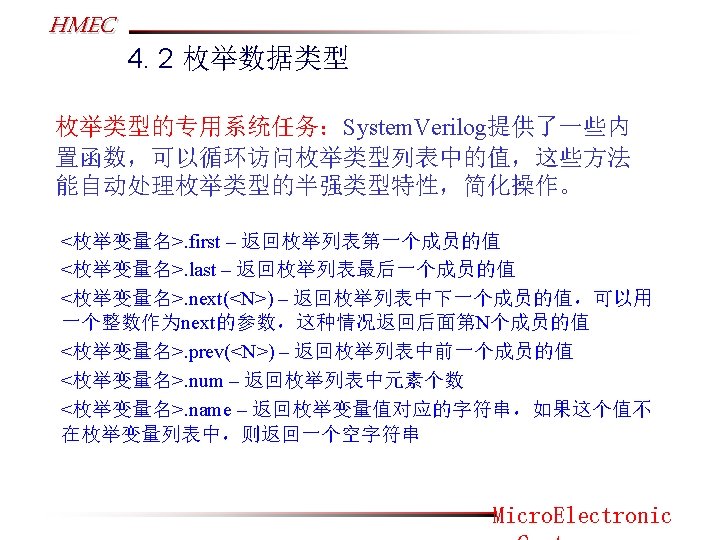

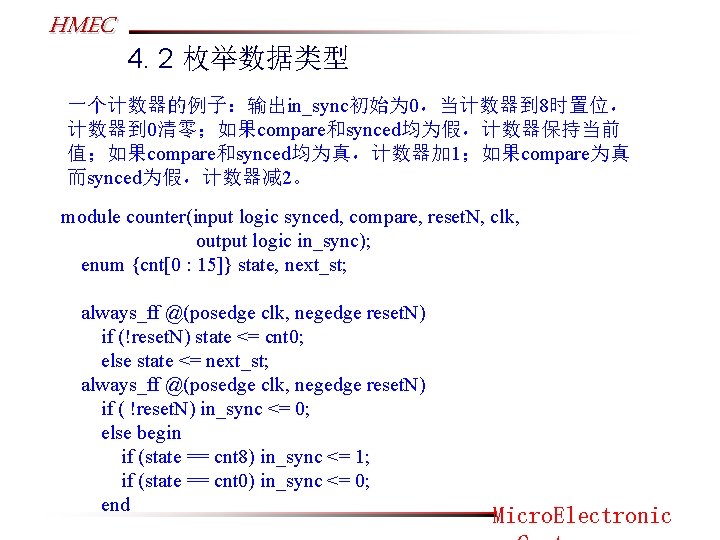

HMEC 4. 2 枚举数据类型 一个计数器的例子:输出in_sync初始为 0,当计数器到 8时置位, 计数器到 0清零;如果compare和synced均为假,计数器保持当前 值;如果compare和synced均为真,计数器加 1;如果compare为真 而synced为假,计数器减 2。 module counter(input logic synced, compare, reset. N, clk, output logic in_sync); enum {cnt[0 : 15]} state, next_st; always_ff @(posedge clk, negedge reset. N) if (!reset. N) state <= cnt 0; else state <= next_st; always_ff @(posedge clk, negedge reset. N) if ( !reset. N) in_sync <= 0; else begin if (state == cnt 8) in_sync <= 1; if (state == cnt 0) in_sync <= 0; end Micro. Electronic

HMEC 4. 2 枚举数据类型 always_comb begin next_st = state; case (state) cnt 0 : if (compare && synced) next_st = state. next; cnt 1 : begin if (compare && synced) next_st = state. next; if (compare && !synced) next_st = state. first; end cnt 15 : if (compare && !synced) next_st = state. prev(2); default : begin if (compare && synced) next_st = state. next; if (compare && !synced) next_st = state. prev(2); endcase endmodule Micro. Electronic

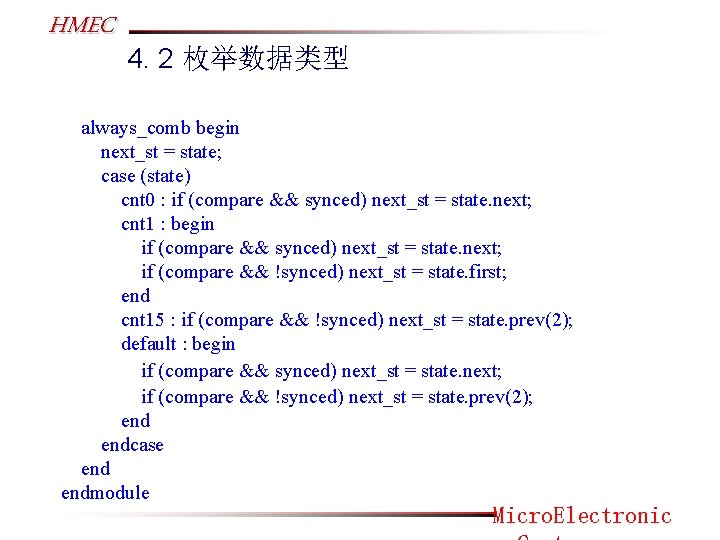

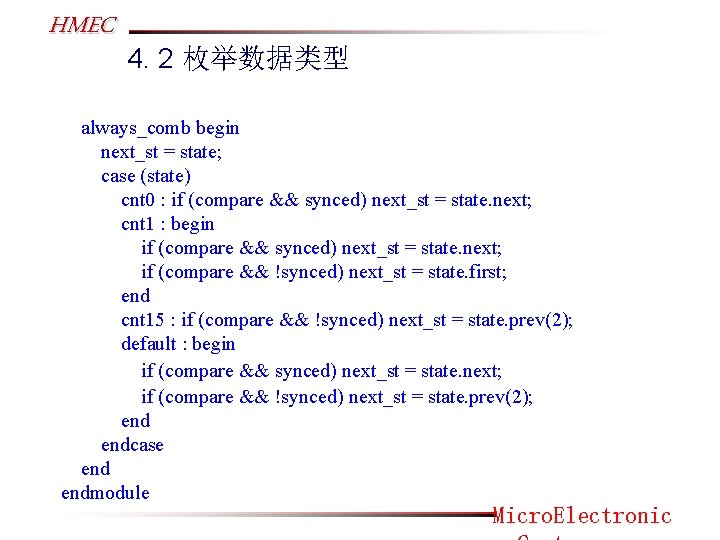

HMEC 4. 2 枚举数据类型 打印枚举类型:枚举类型值可以作为标签的内部值或标签名打印。 module FSM(input logic clk, reset. N, output logic [3 : 0] control); enum logic [2 : 0] {WAIT = 3’b 001, LOAD = 3’b 010, READY = 3’b 100} state, next; always @(posedge clk, negedit reset. N) if (!reset. N) state <= WAIT; else state <= next; always_comb begin $display(“n. Current state is %s (%b)”, state. name, state); case(state) WAIT : next = LOAD; LOAD : next = READY; READY : next = WAIT; endcase $display(“next state will be %s(%b)”, next. name, next); end assign control = state; endmodule Micro. Electronic