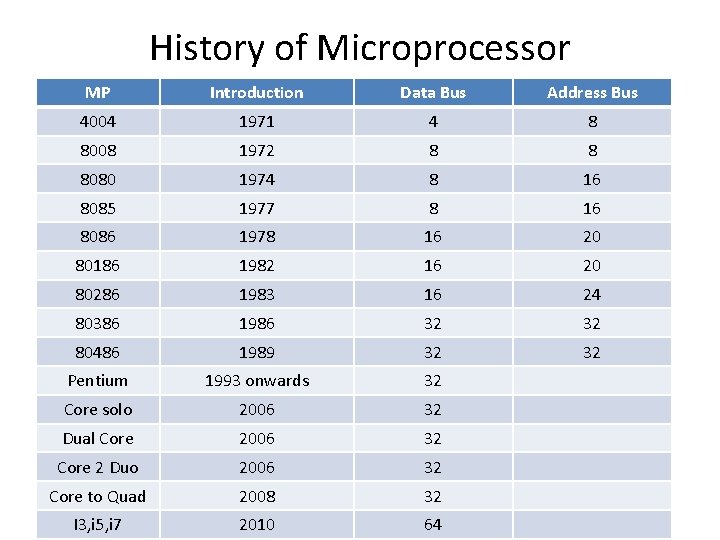

History of Microprocessor MP Introduction Data Bus Address

History of Microprocessor MP Introduction Data Bus Address Bus 4004 1971 4 8 8008 1972 8 8 8080 1974 8 16 8085 1977 8 16 8086 1978 16 20 80186 1982 16 20 80286 1983 16 24 80386 1986 32 32 80486 1989 32 32 Pentium 1993 onwards 32 Core solo 2006 32 Dual Core 2006 32 Core 2 Duo 2006 32 Core to Quad 2008 32 I 3, i 5, i 7 2010 64

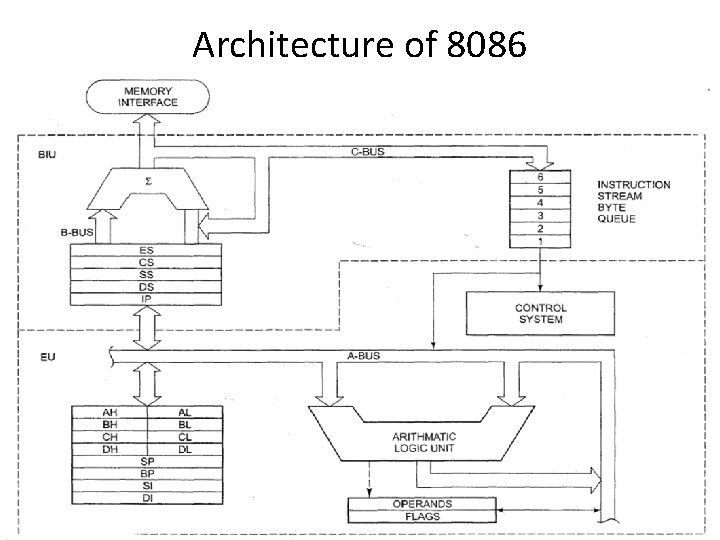

Architecture of 8086

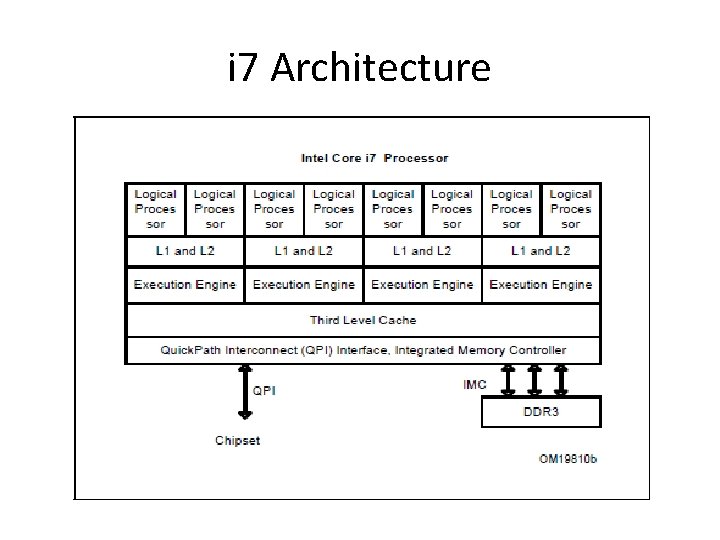

i 7 Architecture

Features of i 7 • Support 64 -bit execution: Having 64 bits data bus and 36 bits address bus. • Quad Core Processor: Integrate 4 Cores (latest Core i 7 processor incorporate 6 cores) • High Speed Computation: Speed ranges from 2. 66 GHz to 3. 33 GHz • Virtualization Technology: Virtualization is a technology that enables running multiple OSs side-by-side on the same processing hardware.

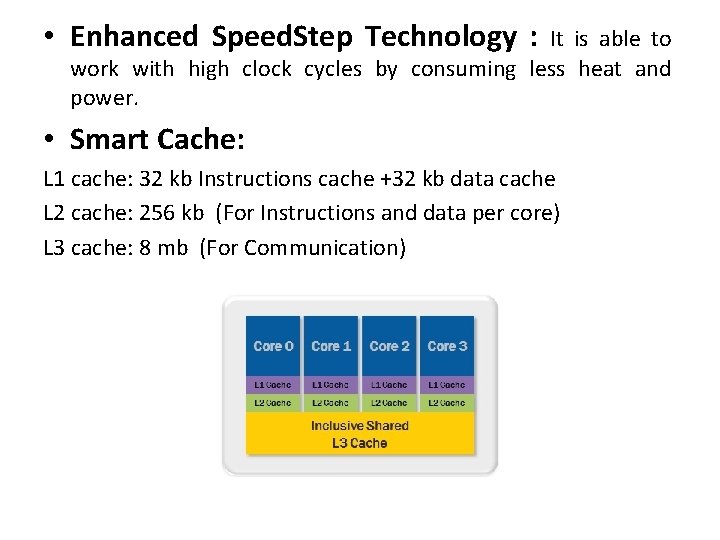

• Enhanced Speed. Step Technology : It is able to work with high clock cycles by consuming less heat and power. • Smart Cache: L 1 cache: 32 kb Instructions cache +32 kb data cache L 2 cache: 256 kb (For Instructions and data per core) L 3 cache: 8 mb (For Communication)

• Supports Intel Turbo Boost technology: Intel Turbo Boost is an innovative feature that automatically allows active processor cores to run faster than the base operating frequency when certain conditions are met. • Support DDR 3 main memory: (Double Data Rate Type Three Random Access Memory) Ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data rates. This leads to faster execution of programs and other functions. • Active Management Technology (AMT) AMT provides system administrators the ability to remotely monitor, maintain, and update systems. This will help to collect or modify data remotely, to recover or update system etc. .

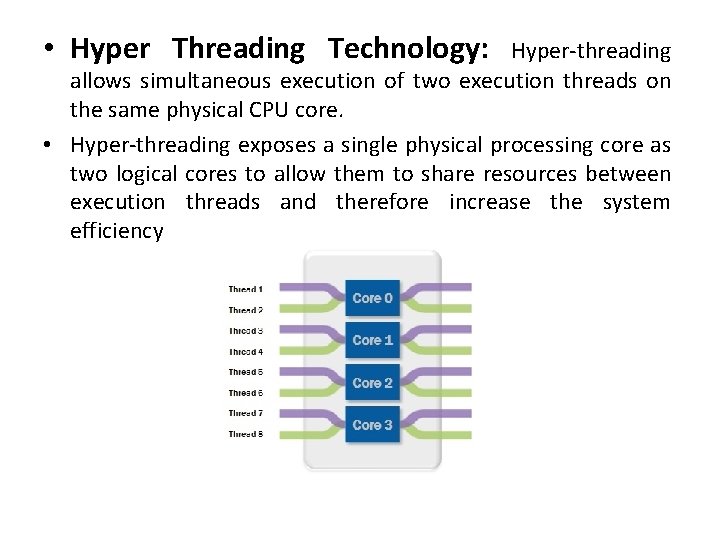

• Hyper Threading Technology: Hyper-threading allows simultaneous execution of two execution threads on the same physical CPU core. • Hyper-threading exposes a single physical processing core as two logical cores to allow them to share resources between execution threads and therefore increase the system efficiency

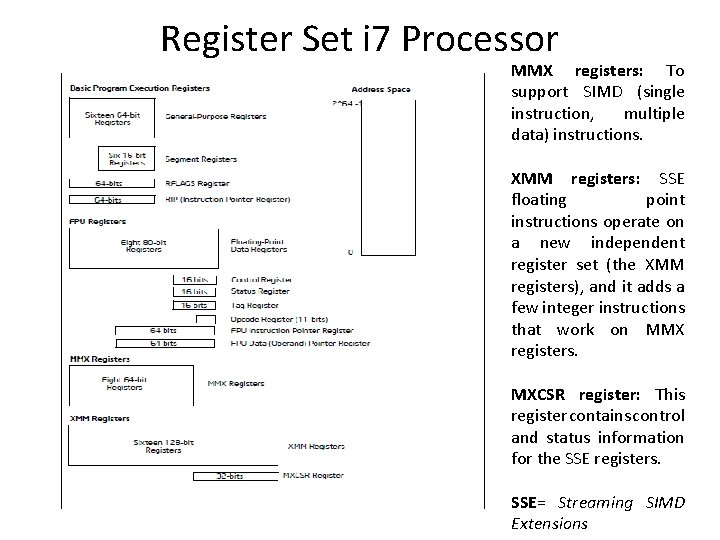

Register Set i 7 Processor MMX registers: To support SIMD (single instruction, multiple data) instructions. XMM registers: SSE floating point instructions operate on a new independent register set (the XMM registers), and it adds a few integer instructions that work on MMX registers. MXCSR register: This register contains control and status information for the SSE registers. SSE= Streaming SIMD Extensions

RFLAG • In 64 -bit mode, EFLAGS is extended to 64 bits and called RFLAGS. The upper 32 bits of RFLAGS register is reserved. The lower 32 bits of RFLAGS is the same as EFLAGS.

- Slides: 9