History of 64 bit Computing AMD 64 and

History of 64 -bit Computing: AMD 64 and Intel Itanium Processors Brett Casbeer, Adam Kenny, Chris Kopek, Nick Snead 1

64 -bit History • “ 640 K ought to be enough for anybody” – Bill Gates • 64 -bit twice as fast as 32 -bits? • Benefits of 64 -bit technology • Applications of 64 -bit technology 2

AMD 64 Outline • • AMD Athlon 64 Specifications Operating Modes Register overview DDR controller and Hypertransport 3

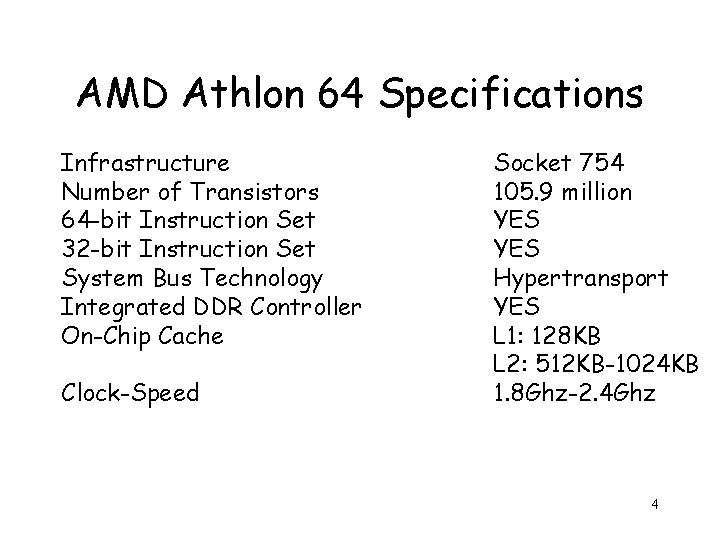

AMD Athlon 64 Specifications Infrastructure Number of Transistors 64 -bit Instruction Set 32 -bit Instruction Set System Bus Technology Integrated DDR Controller On-Chip Cache Clock-Speed Socket 754 105. 9 million YES Hypertransport YES L 1: 128 KB L 2: 512 KB-1024 KB 1. 8 Ghz-2. 4 Ghz 4

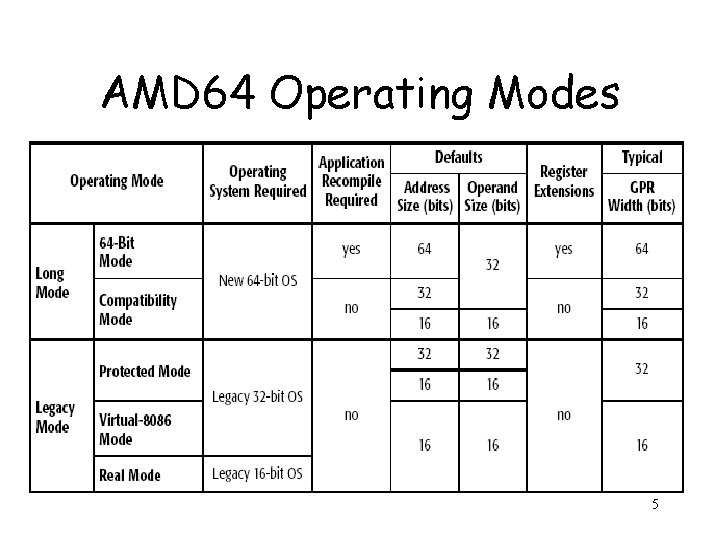

AMD 64 Operating Modes 5

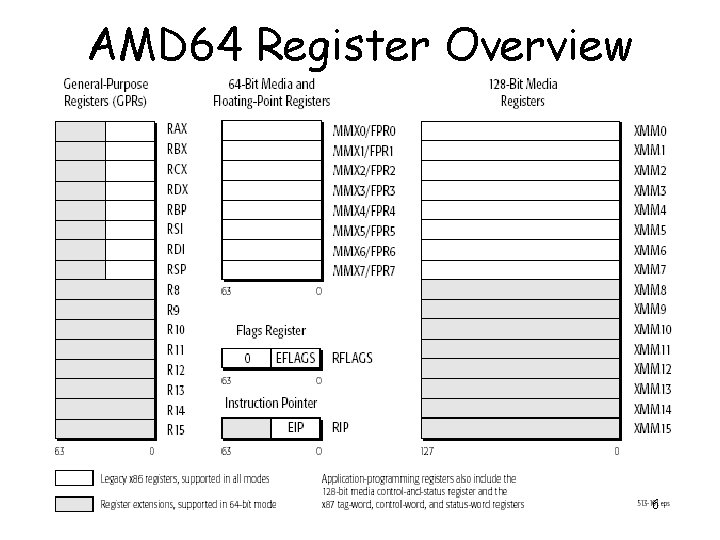

AMD 64 Register Overview 6

Reduce Bottlenecks • DDR Memory Controller – Built into CPU – Saves Time • Hypertransport – Transport Speeds – Data packets 7

Intel Itanium Outline • • • Itanium Processor Specifications Itanium Features Itanium Epic Architecture IA-64 Instruction Set IA-64 vs. IA-32 8

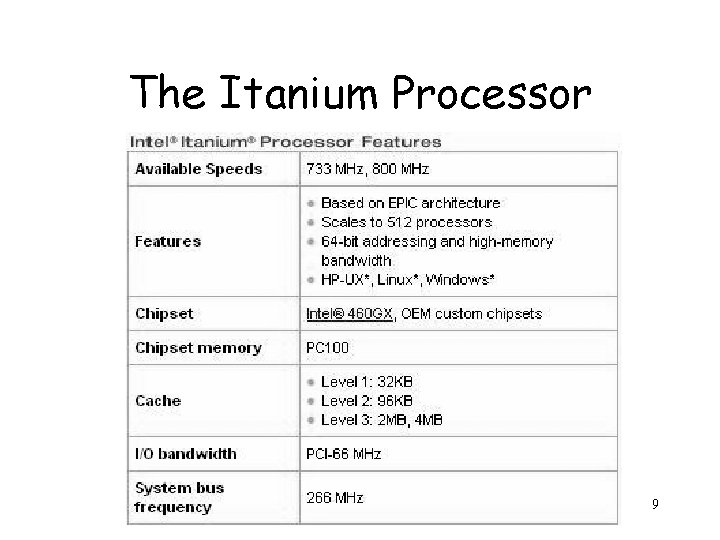

The Itanium Processor 9

The Itanium Processor • Designed for 1 -4000 processor workstations and servers. • Level 3 bus designed for communication between processors • Level 2 cache reduces traffic • Page sizes from 4 KB-256 MB 10

Itanium: EPIC Architecture • Explicitly Parallel Instruction Computing • Allows processor to run instructions parallel to other instructions • Instructions “bundled” during the compiler stage • No size limit for the groups of “bundled” instructions 11

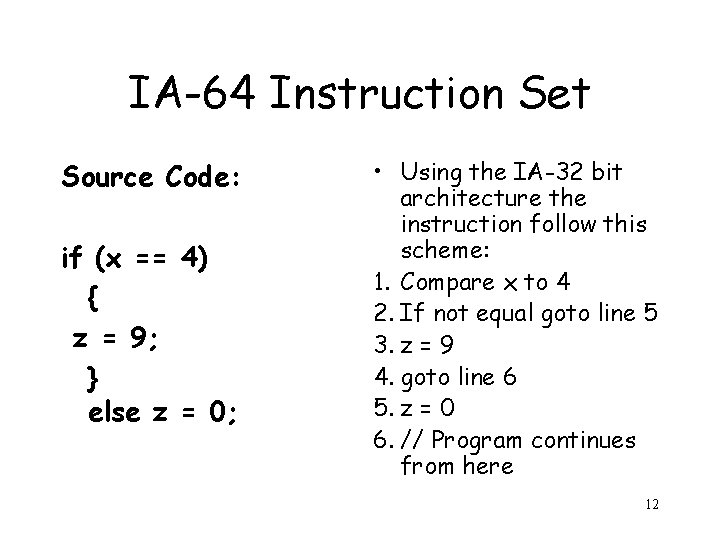

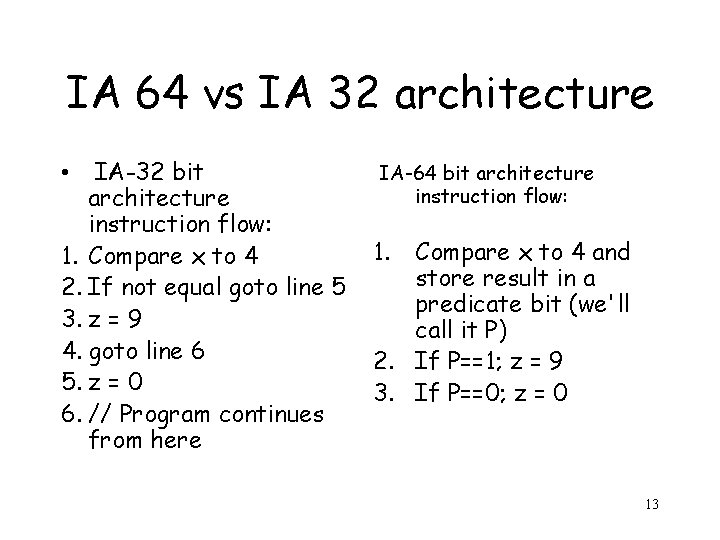

IA-64 Instruction Set Source Code: if (x == 4) { z = 9; } else z = 0; • Using the IA-32 bit architecture the instruction follow this scheme: 1. Compare x to 4 2. If not equal goto line 5 3. z = 9 4. goto line 6 5. z = 0 6. // Program continues from here 12

IA 64 vs IA 32 architecture IA-32 bit architecture instruction flow: 1. Compare x to 4 2. If not equal goto line 5 3. z = 9 4. goto line 6 5. z = 0 6. // Program continues from here • IA-64 bit architecture instruction flow: 1. Compare x to 4 and store result in a predicate bit (we'll call it P) 2. If P==1; z = 9 3. If P==0; z = 0 13

Conclusion • AMD 64 – Operating Modes • Long Mode, Legacy Mode – Registers • GPRs, XMM, RIP – Reduce Bottlenecks • DDR Controller, Hypertransport 14

Conclusion • Intel Specifications and Features • EPIC Architecture – Parallel Computing, Bundled Instructions • IA-64 Instruction Set • IA-64 vs. IA-32 15

- Slides: 15