HighVoltage CMOS Technology Ivan Peric University of Heidelberg

High-Voltage CMOS Technology Ivan Peric University of Heidelberg, Germany Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 1

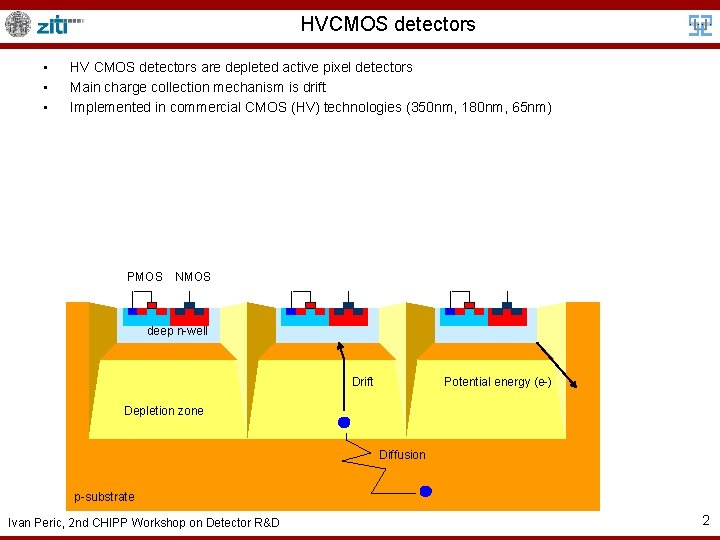

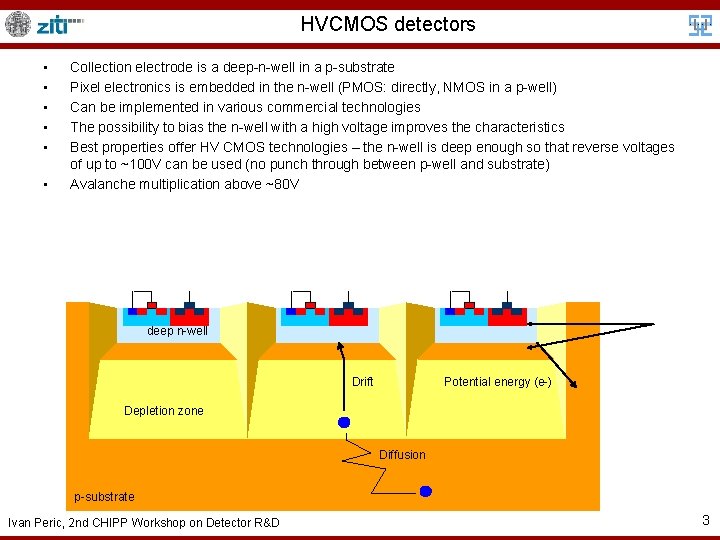

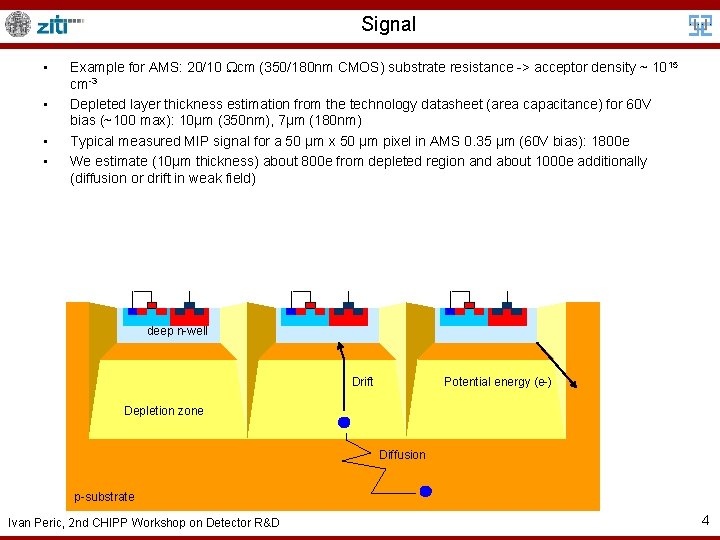

HVCMOS detectors • • • HV CMOS detectors are depleted active pixel detectors Main charge collection mechanism is drift Implemented in commercial CMOS (HV) technologies (350 nm, 180 nm, 65 nm) PMOS NMOS deep n-well Drift Potential energy (e-) Depletion zone Diffusion p-substrate Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 2

HVCMOS detectors • • • Collection electrode is a deep-n-well in a p-substrate Pixel electronics is embedded in the n-well (PMOS: directly, NMOS in a p-well) Can be implemented in various commercial technologies The possibility to bias the n-well with a high voltage improves the characteristics Best properties offer HV CMOS technologies – the n-well is deep enough so that reverse voltages of up to ~100 V can be used (no punch through between p-well and substrate) Avalanche multiplication above ~80 V deep n-well Drift Potential energy (e-) Depletion zone Diffusion p-substrate Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 3

Signal • • Example for AMS: 20/10 cm (350/180 nm CMOS) substrate resistance -> acceptor density ~ 1015 cm-3 Depleted layer thickness estimation from the technology datasheet (area capacitance) for 60 V bias (~100 max): 10µm (350 nm), 7µm (180 nm) Typical measured MIP signal for a 50 µm x 50 µm pixel in AMS 0. 35 µm (60 V bias): 1800 e We estimate (10µm thickness) about 800 e from depleted region and about 1000 e additionally (diffusion or drift in weak field) deep n-well Drift Potential energy (e-) Depletion zone Diffusion p-substrate Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 4

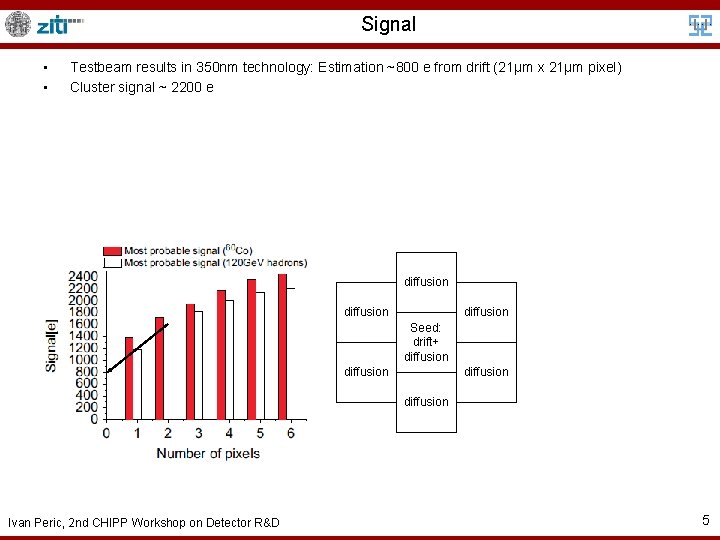

Signal • • Testbeam results in 350 nm technology: Estimation ~800 e from drift (21µm x 21µm pixel) Cluster signal ~ 2200 e diffusion Seed: drift+ diffusion Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 5

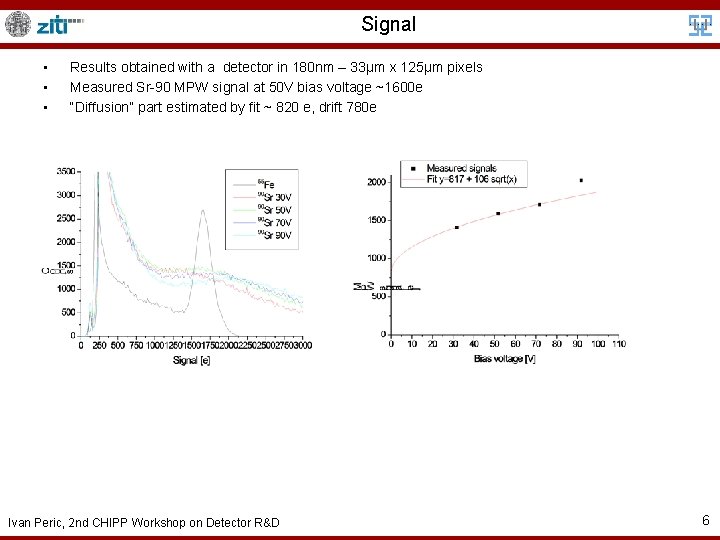

Signal • • • Results obtained with a detector in 180 nm – 33µm x 125µm pixels Measured Sr-90 MPW signal at 50 V bias voltage ~1600 e “Diffusion” part estimated by fit ~ 820 e, drift 780 e Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 6

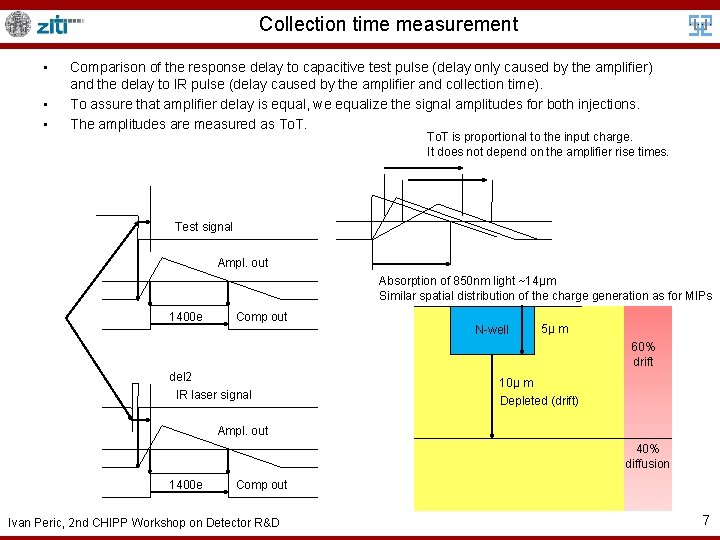

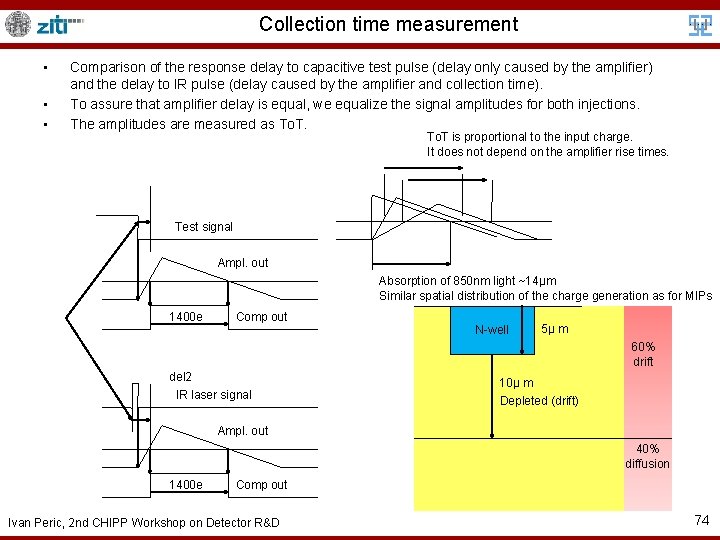

Collection time measurement • • • Comparison of the response delay to capacitive test pulse (delay only caused by the amplifier) and the delay to IR pulse (delay caused by the amplifier and collection time). To assure that amplifier delay is equal, we equalize the signal amplitudes for both injections. The amplitudes are measured as To. T is proportional to the input charge. It does not depend on the amplifier rise times. Test signal Ampl. out Absorption of 850 nm light ~14µm Similar spatial distribution of the charge generation as for MIPs 1400 e Comp out N-well 5µ m 60% drift del 2 IR laser signal 10µ m Depleted (drift) Ampl. out 40% diffusion 1400 e Comp out Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 7

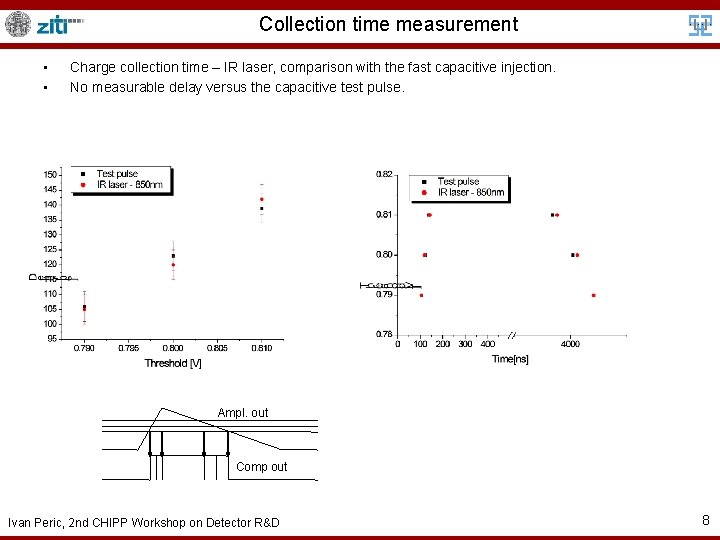

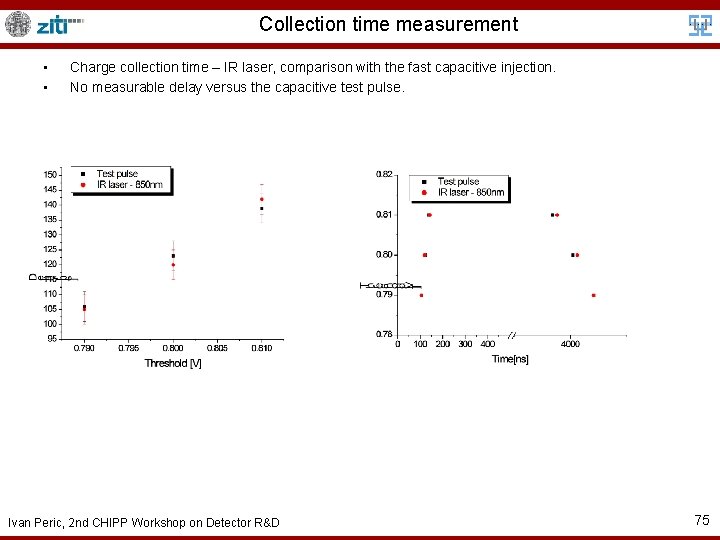

Collection time measurement • • Charge collection time – IR laser, comparison with the fast capacitive injection. No measurable delay versus the capacitive test pulse. Ampl. out Comp out Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 8

General development • • • Two development periods: 1) general development and 2) applications In phase 1) we used (mostly) AMS 0. 35µm technology Several prototypes have been designed Three detector types: A) Monolithic detector with intelligent CMOS pixels Pixel electronic is rather complex – CMOS based charge sensitive amplifier, usually discriminator, threshold tune… B) Monolithic detector with 4 -PMOS-transistor pixel and rolling shutter RO C) Capacitively coupled hybrid detectors Good results, >98% efficiency in test-beam, high radiation tolerance Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 9

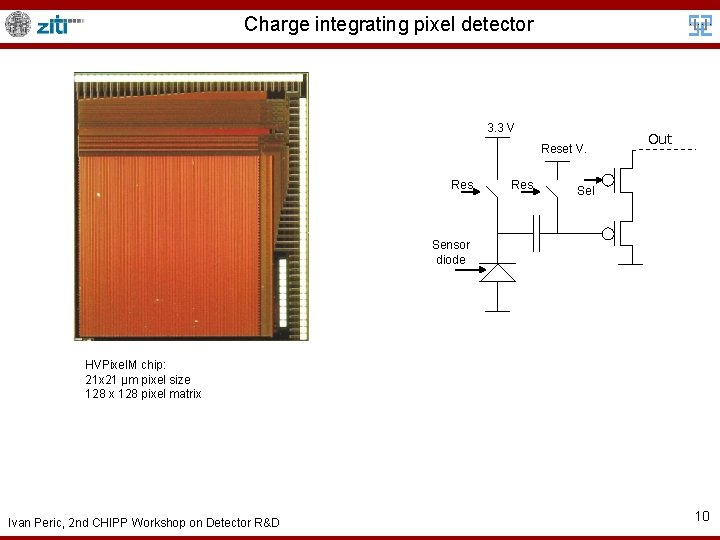

Charge integrating pixel detector 3. 3 V Reset V. Res Out Sel Sensor diode HVPixel. M chip: 21 x 21 µm pixel size 128 x 128 pixel matrix Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 10

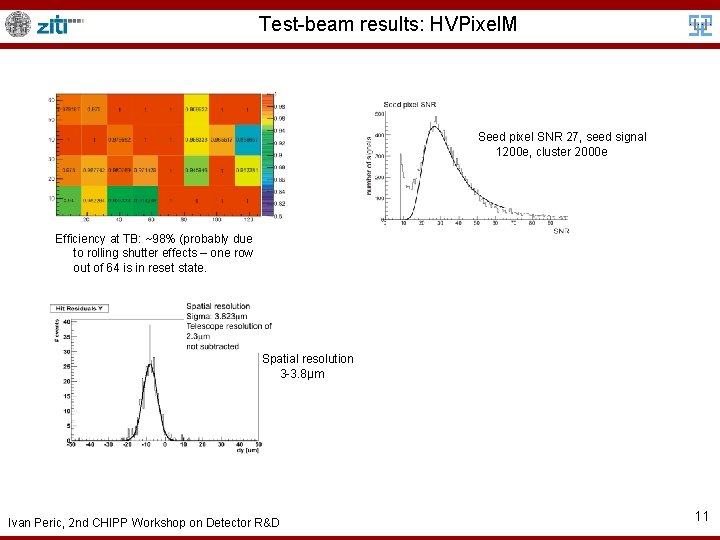

Test-beam results: HVPixel. M Seed pixel SNR 27, seed signal 1200 e, cluster 2000 e Efficiency at TB: ~98% (probably due to rolling shutter effects – one row out of 64 is in reset state. Spatial resolution 3 -3. 8µm Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 11

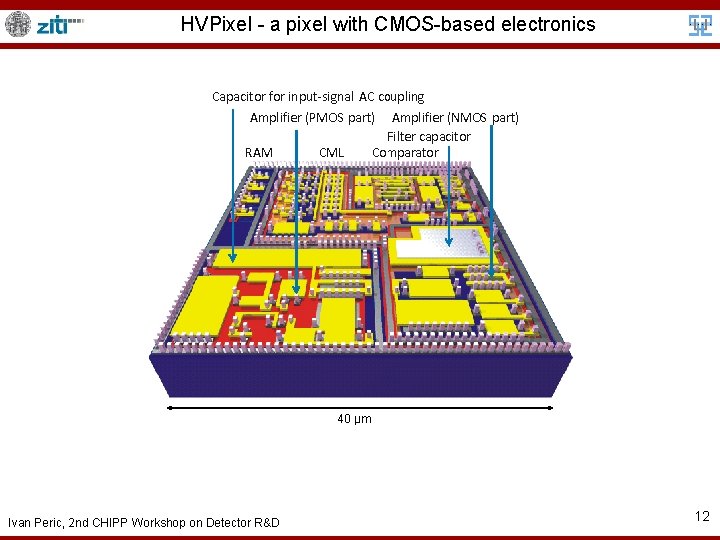

HVPixel - a pixel with CMOS-based electronics 40 µm Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 12

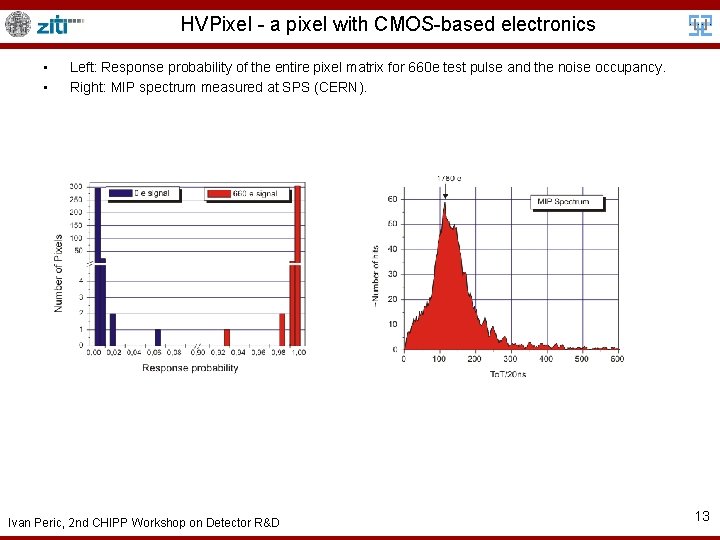

HVPixel - a pixel with CMOS-based electronics • • Left: Response probability of the entire pixel matrix for 660 e test pulse and the noise occupancy. Right: MIP spectrum measured at SPS (CERN). Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 13

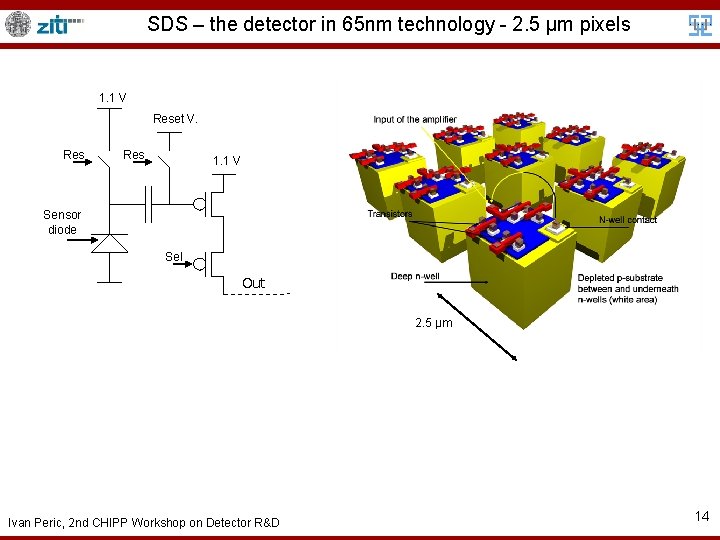

SDS – the detector in 65 nm technology - 2. 5 µm pixels 1. 1 V Reset V. Res 1. 1 V Sensor diode Sel Out 2. 5 µm Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 14

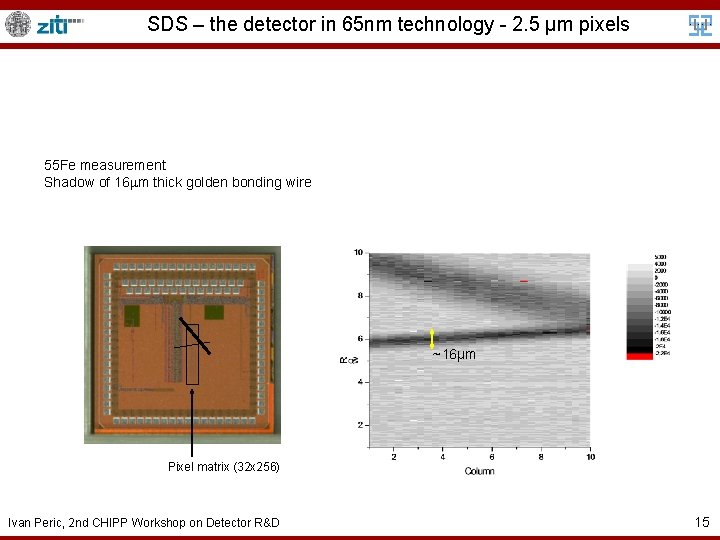

SDS – the detector in 65 nm technology - 2. 5 µm pixels 55 Fe measurement Shadow of 16 m thick golden bonding wire ~16µm Pixel matrix (32 x 256) Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 15

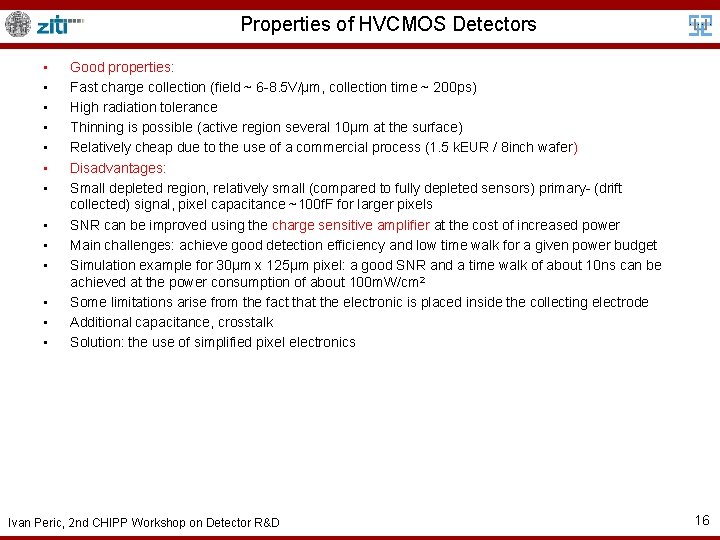

Properties of HVCMOS Detectors • • • • Good properties: Fast charge collection (field ~ 6 -8. 5 V/µm, collection time ~ 200 ps) High radiation tolerance Thinning is possible (active region several 10µm at the surface) Relatively cheap due to the use of a commercial process (1. 5 k. EUR / 8 inch wafer) Disadvantages: Small depleted region, relatively small (compared to fully depleted sensors) primary- (drift collected) signal, pixel capacitance ~100 f. F for larger pixels SNR can be improved using the charge sensitive amplifier at the cost of increased power Main challenges: achieve good detection efficiency and low time walk for a given power budget Simulation example for 30µm x 125µm pixel: a good SNR and a time walk of about 10 ns can be achieved at the power consumption of about 100 m. W/cm 2 Some limitations arise from the fact that the electronic is placed inside the collecting electrode Additional capacitance, crosstalk Solution: the use of simplified pixel electronics Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 16

Planned applications • • • Mu 3 e and PANDA (GSI) HLLHC e. g. ATLAS CLIC Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 17

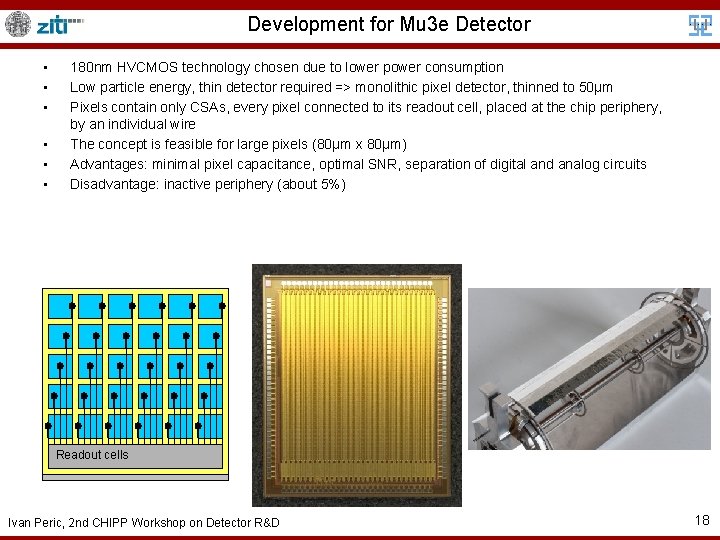

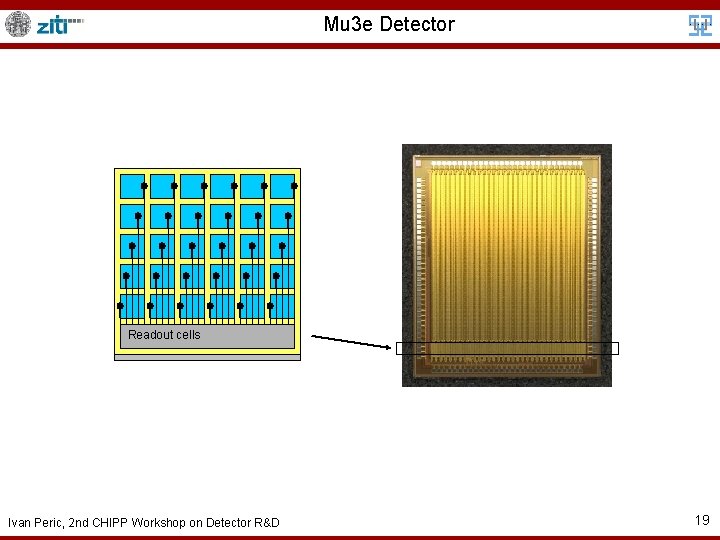

Development for Mu 3 e Detector • • • 180 nm HVCMOS technology chosen due to lower power consumption Low particle energy, thin detector required => monolithic pixel detector, thinned to 50µm Pixels contain only CSAs, every pixel connected to its readout cell, placed at the chip periphery, by an individual wire The concept is feasible for large pixels (80µm x 80µm) Advantages: minimal pixel capacitance, optimal SNR, separation of digital and analog circuits Disadvantage: inactive periphery (about 5%) Readout cells Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 18

Mu 3 e Detector Readout cells Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 19

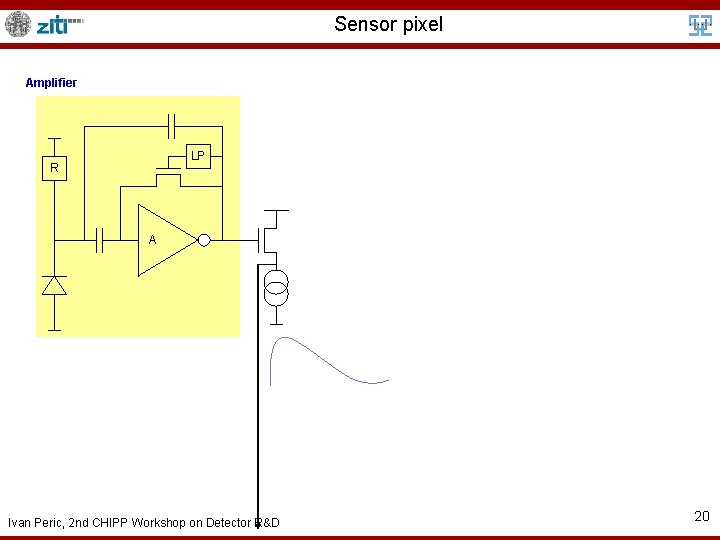

Sensor pixel Amplifier LP R A Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 20

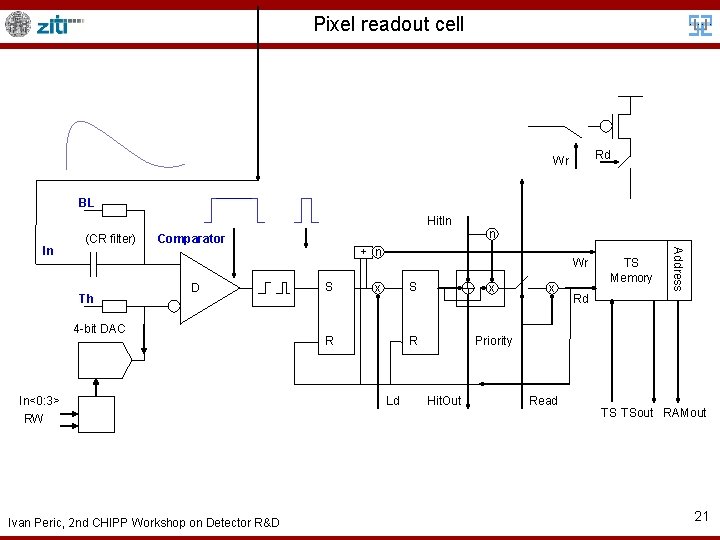

Pixel readout cell Rd Wr BL Hit. In Th Comparator D 4 -bit DAC In<0: 3> RW Ivan Peric, 2 nd CHIPP Workshop on Detector R&D n + n S Wr x R Ld S x R Priority Hit. Out x Read TS Memory Address In (CR filter) Rd TS TSout RAMout 21

Column readout cell Hit. Out. Pix TS/Row. Addr Rd. Pix Hit. In x x Ld S x R Priority Hit. Out Ivan Peric, 2 nd CHIPP Workshop on Detector R&D x Rd Wr Rd Col. Addr Rd. Pix n PD Read 22

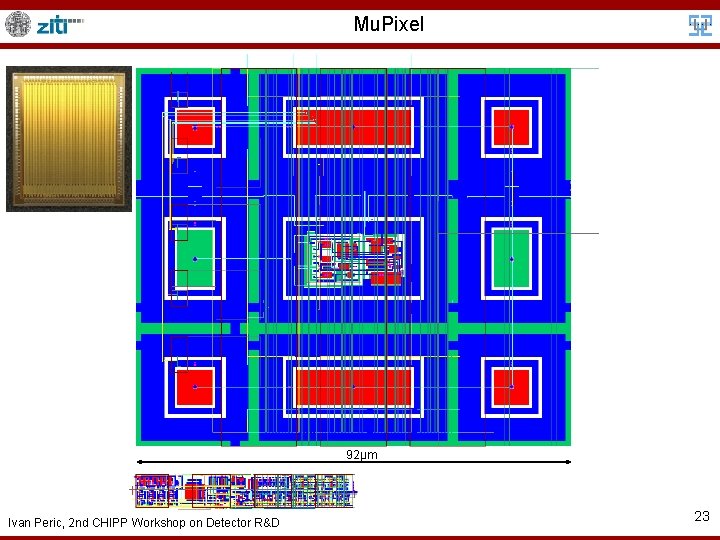

Mu. Pixel 92µm Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 23

Mu. Pixel 92µm Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 24

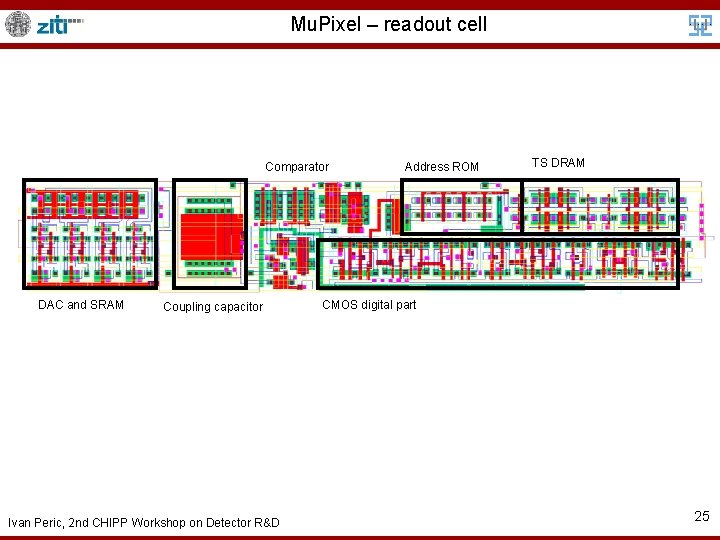

Mu. Pixel – readout cell Comparator DAC and SRAM Coupling capacitor Ivan Peric, 2 nd CHIPP Workshop on Detector R&D Address ROM TS DRAM CMOS digital part 25

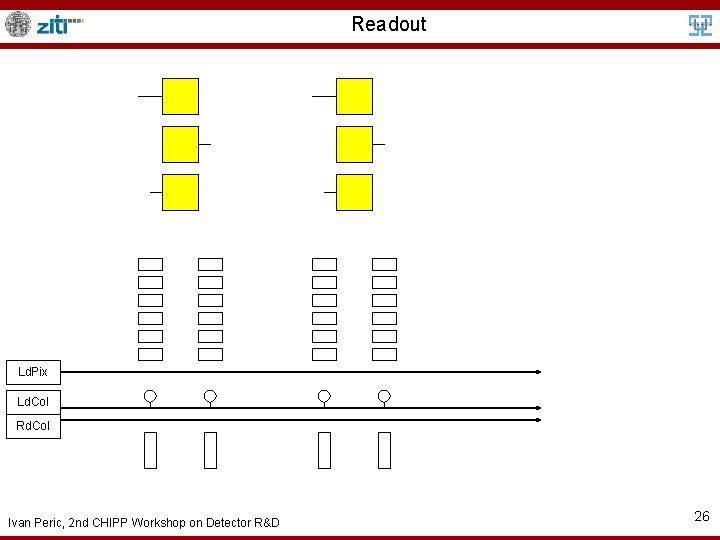

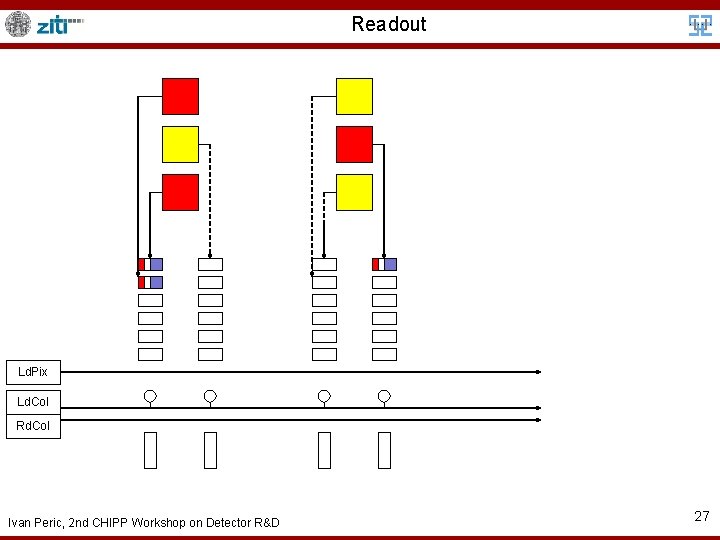

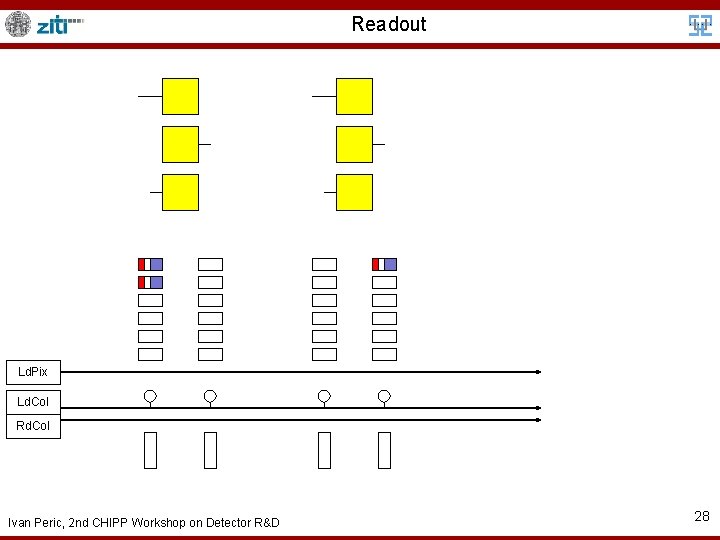

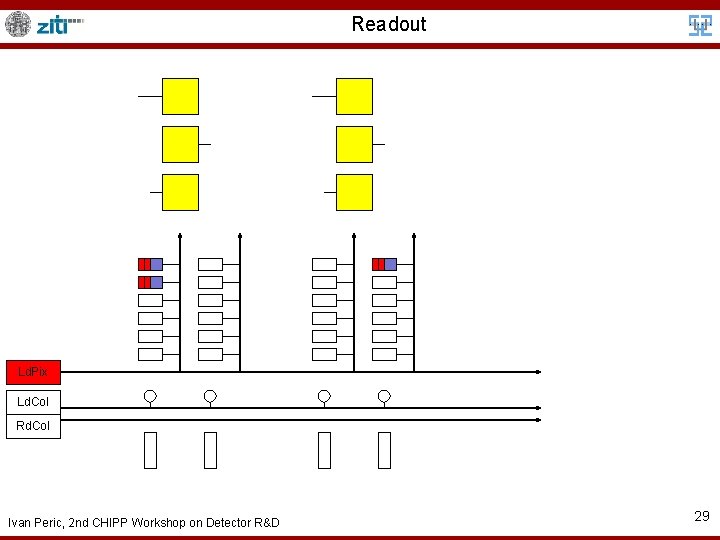

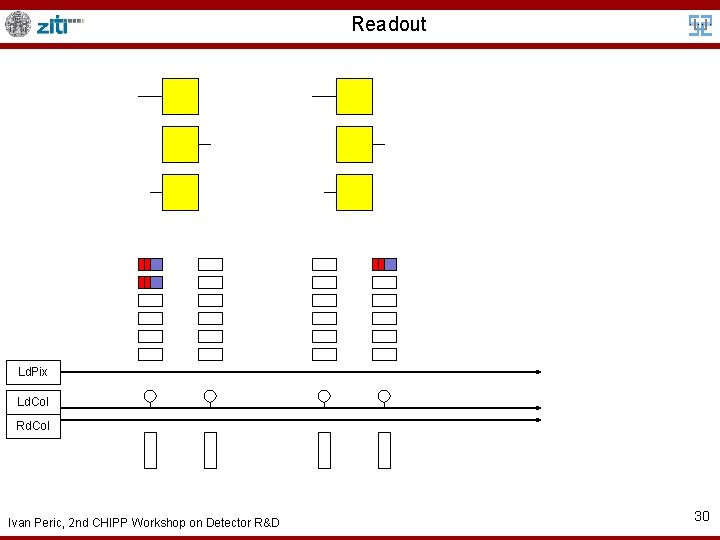

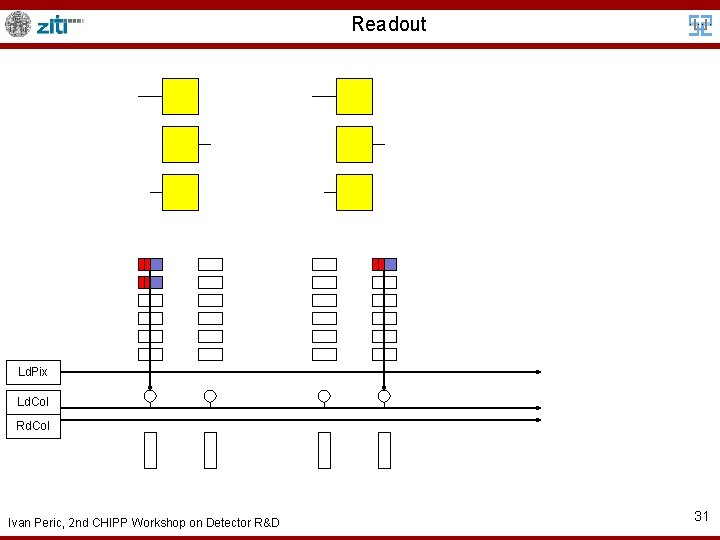

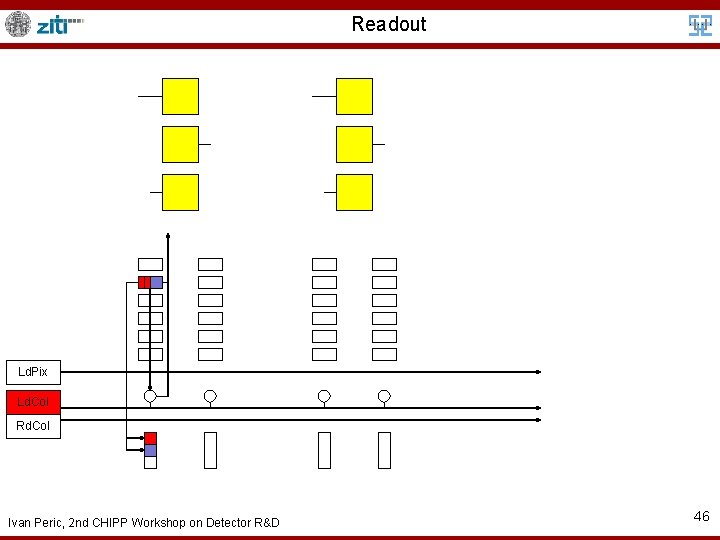

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 26

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 27

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 28

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 29

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 30

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 31

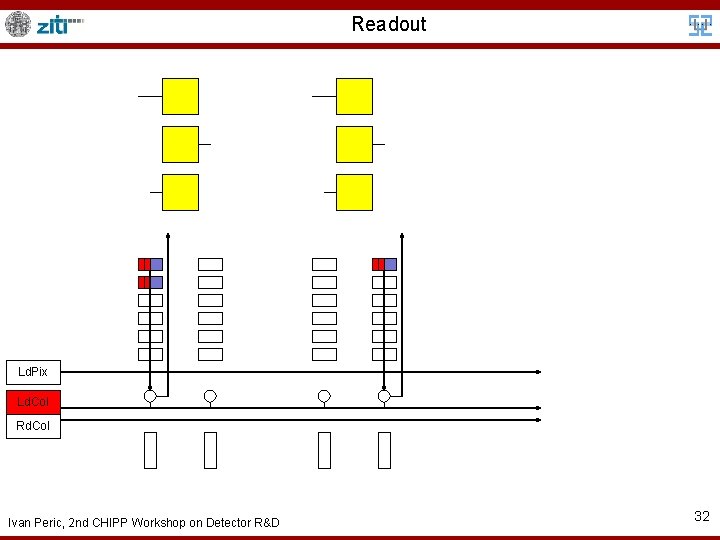

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 32

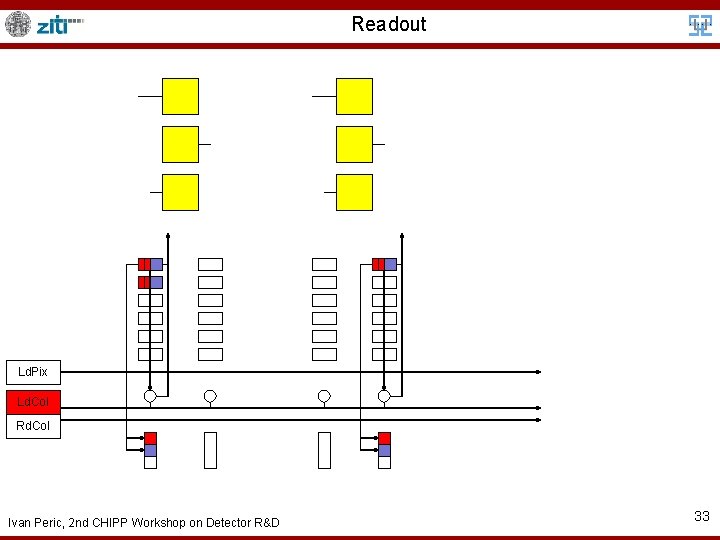

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 33

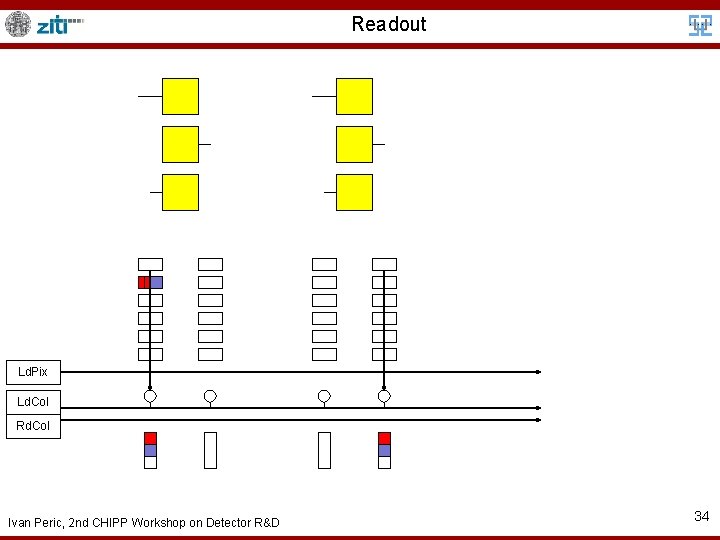

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 34

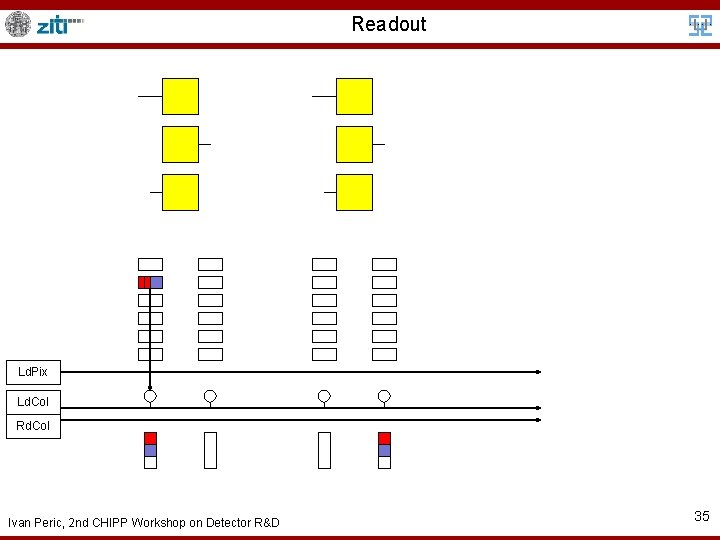

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 35

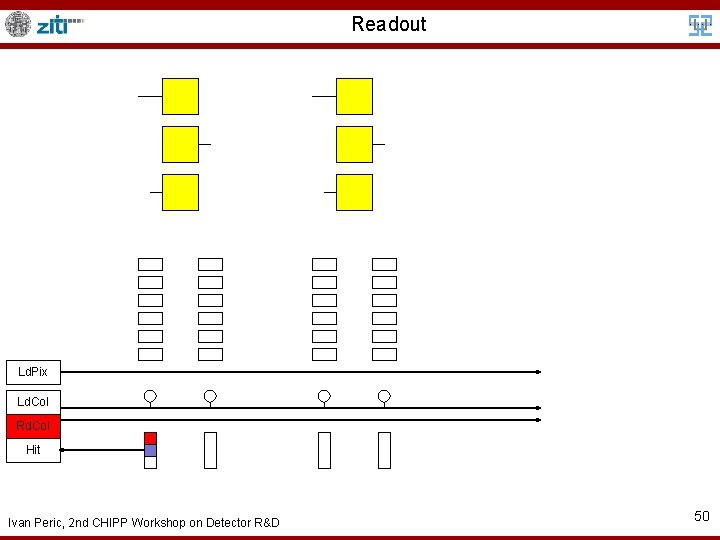

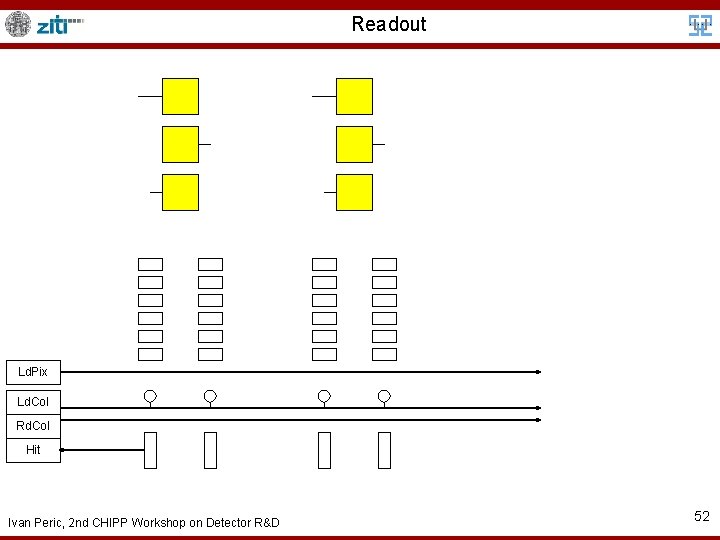

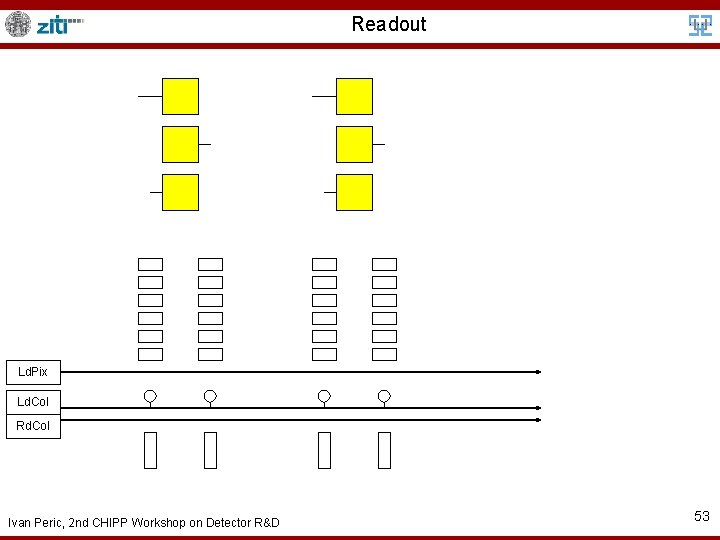

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 36

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 37

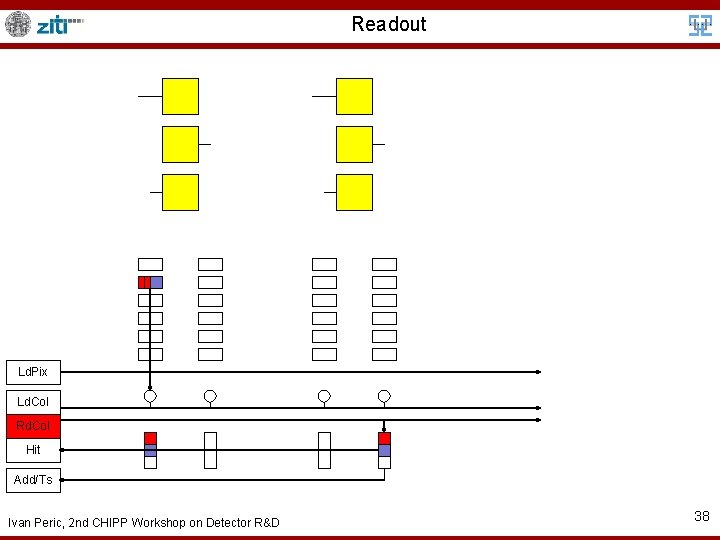

Readout Ld. Pix Ld. Col Rd. Col Hit Add/Ts Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 38

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 39

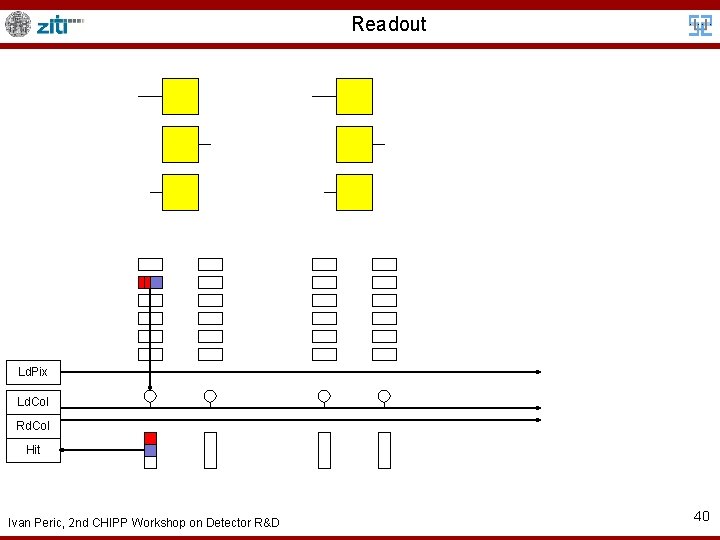

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 40

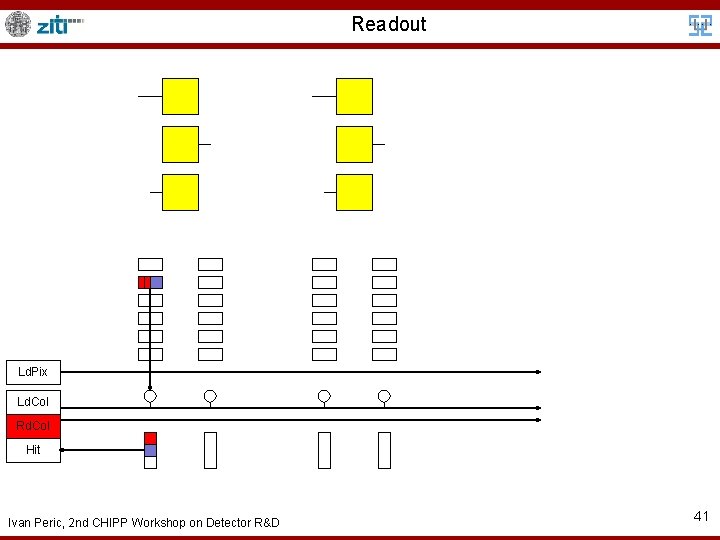

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 41

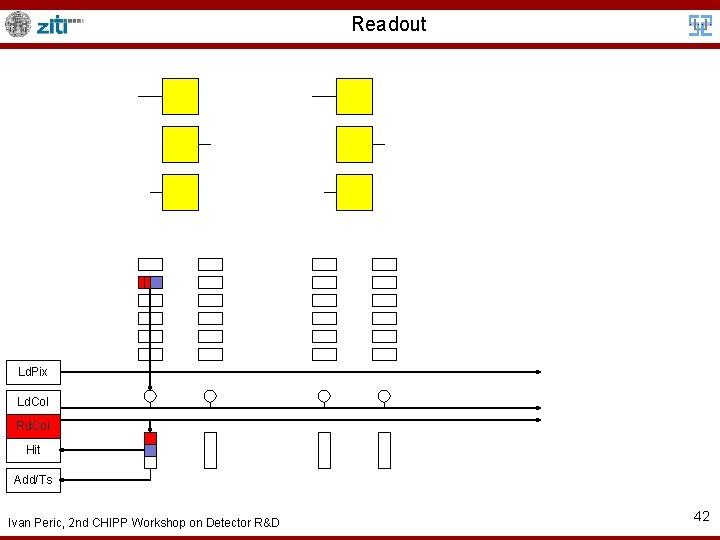

Readout Ld. Pix Ld. Col Rd. Col Hit Add/Ts Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 42

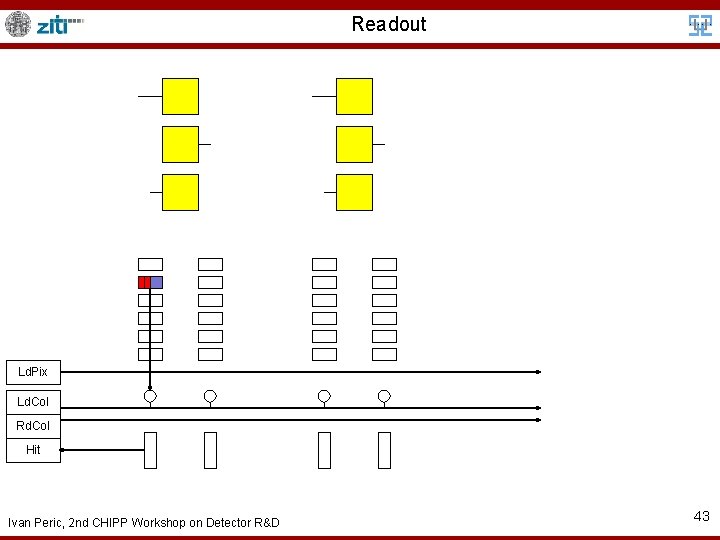

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 43

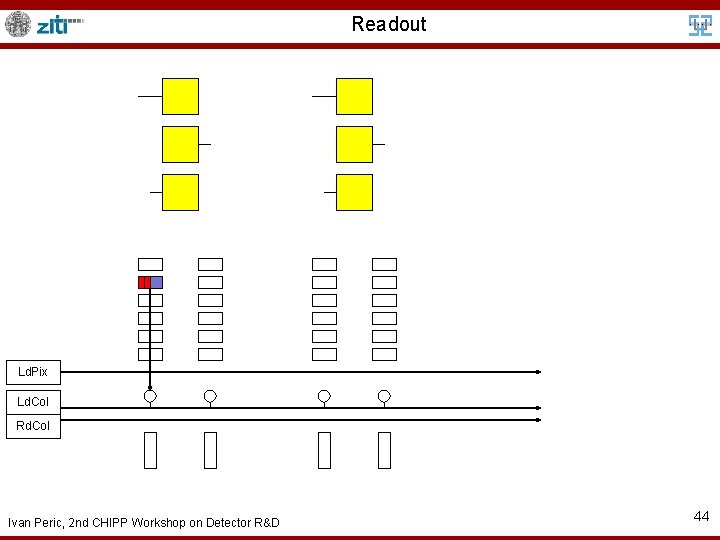

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 44

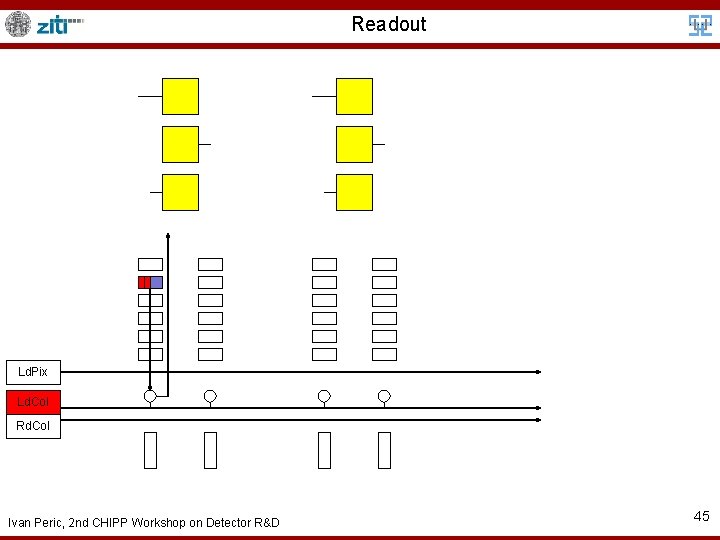

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 45

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 46

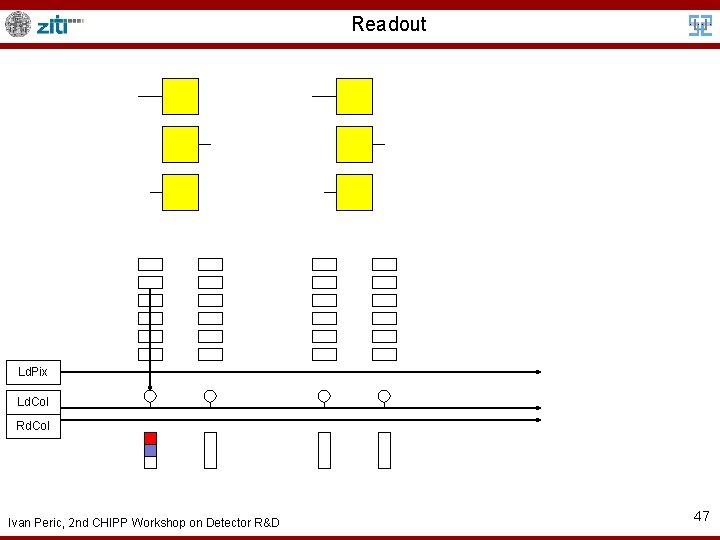

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 47

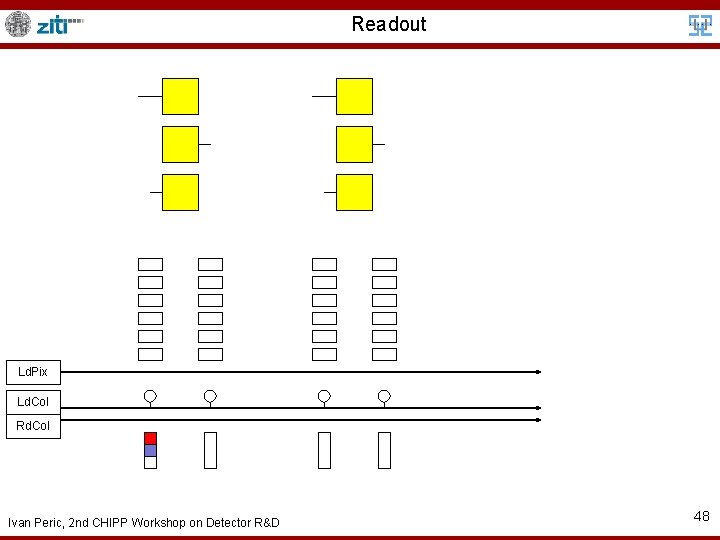

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 48

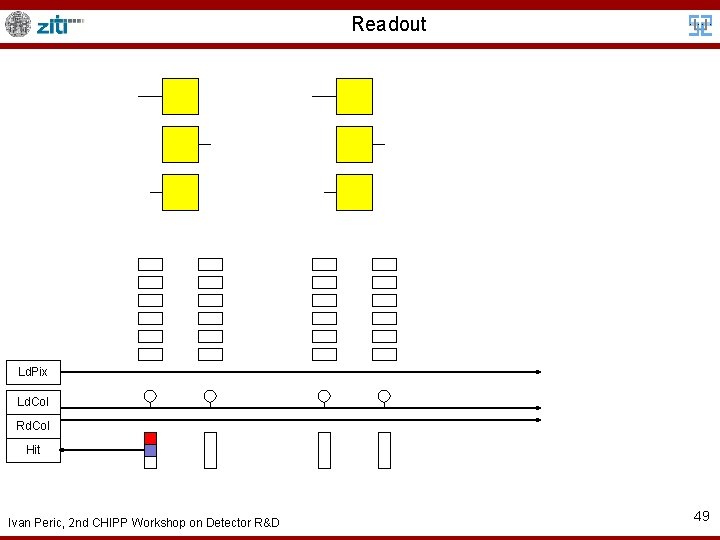

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 49

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 50

Readout Ld. Pix Ld. Col Rd. Col Hit Add/Ts Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 51

Readout Ld. Pix Ld. Col Rd. Col Hit Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 52

Readout Ld. Pix Ld. Col Rd. Col Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 53

Noise measurement Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 54

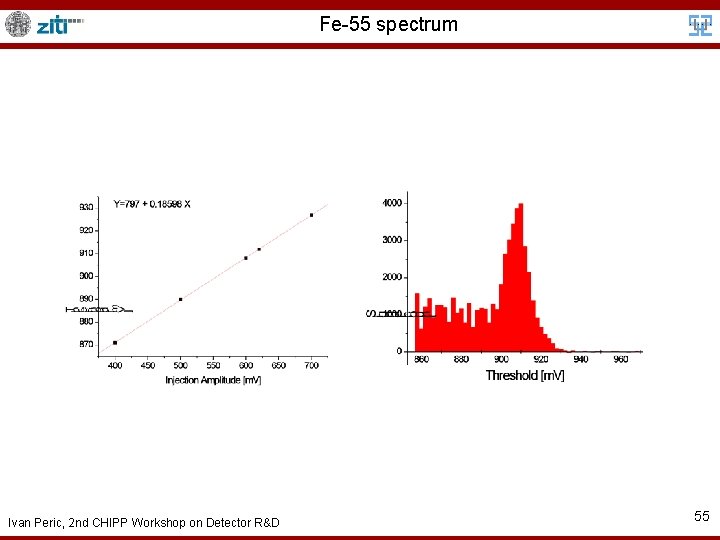

Fe-55 spectrum Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 55

X-ray image Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 56

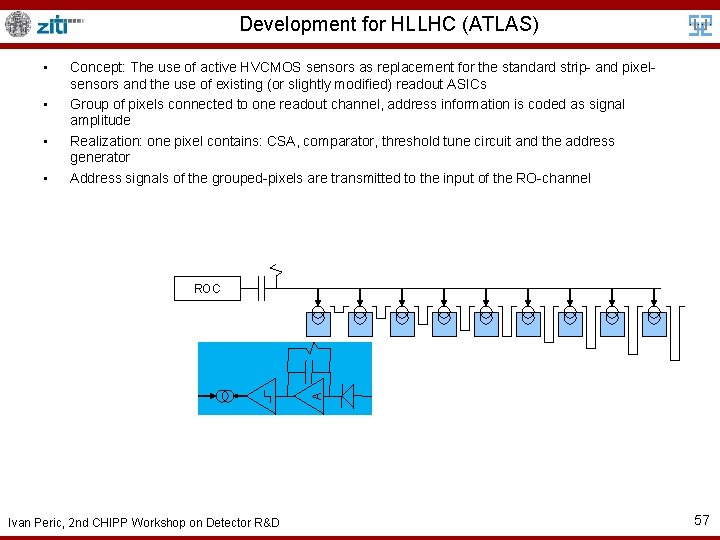

Development for HLLHC (ATLAS) • • Concept: The use of active HVCMOS sensors as replacement for the standard strip- and pixelsensors and the use of existing (or slightly modified) readout ASICs Group of pixels connected to one readout channel, address information is coded as signal amplitude Realization: one pixel contains: CSA, comparator, threshold tune circuit and the address generator Address signals of the grouped-pixels are transmitted to the input of the RO-channel A ROC Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 57

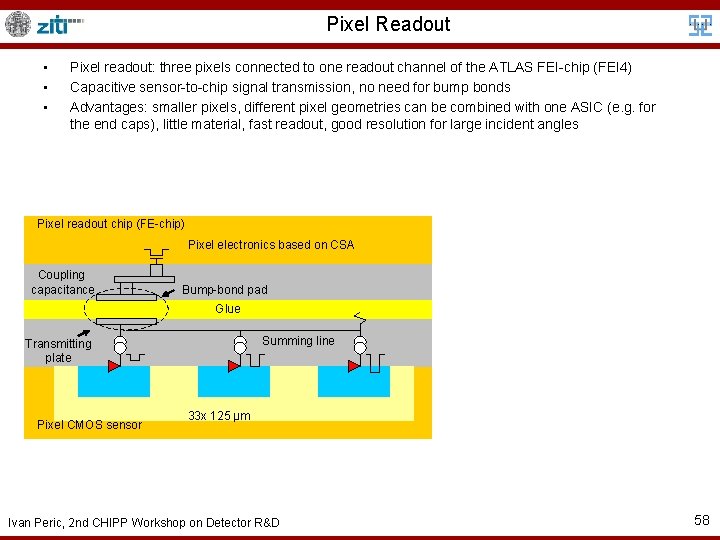

Pixel Readout • • • Pixel readout: three pixels connected to one readout channel of the ATLAS FEI-chip (FEI 4) Capacitive sensor-to-chip signal transmission, no need for bump bonds Advantages: smaller pixels, different pixel geometries can be combined with one ASIC (e. g. for the end caps), little material, fast readout, good resolution for large incident angles Pixel readout chip (FE-chip) Pixel electronics based on CSA Coupling capacitance Bump-bond pad Glue Summing line Transmitting plate Pixel CMOS sensor 33 x 125 μm Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 58

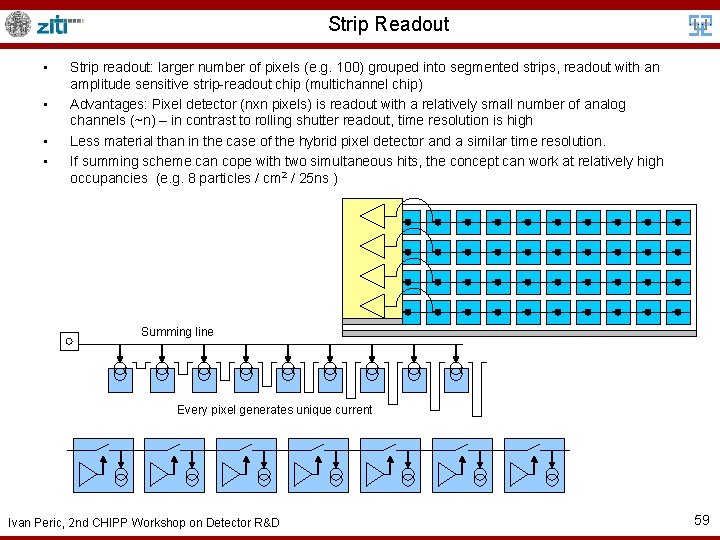

Strip Readout • • Strip readout: larger number of pixels (e. g. 100) grouped into segmented strips, readout with an amplitude sensitive strip-readout chip (multichannel chip) Advantages: Pixel detector (nxn pixels) is readout with a relatively small number of analog channels (~n) – in contrast to rolling shutter readout, time resolution is high Less material than in the case of the hybrid pixel detector and a similar time resolution. If summing scheme can cope with two simultaneous hits, the concept can work at relatively high occupancies (e. g. 8 particles / cm 2 / 25 ns ) Summing line Every pixel generates unique current Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 59

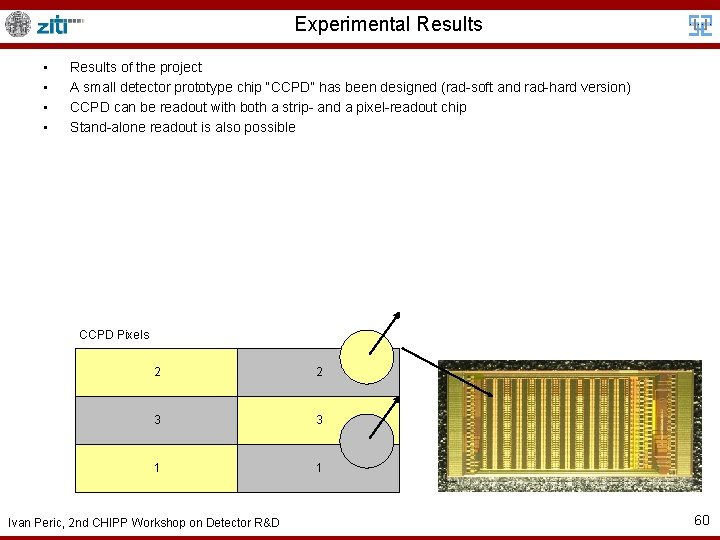

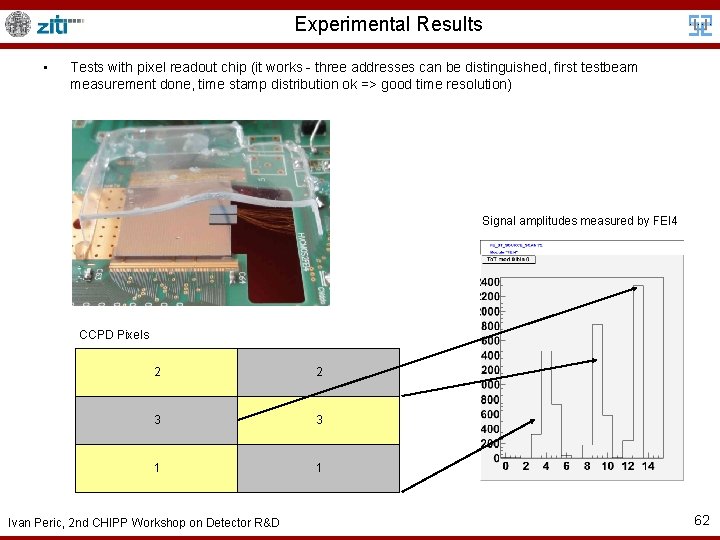

Experimental Results • • Results of the project A small detector prototype chip “CCPD” has been designed (rad-soft and rad-hard version) CCPD can be readout with both a strip- and a pixel-readout chip Stand-alone readout is also possible CCPD Pixels 2 2 3 3 1 1 Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 60

Experimental Results • • Results of the project A small detector prototype chip “CCPD” has been designed (rad-soft and rad-hard version) CCPD can be readout with both a strip- and a pixel-readout chip Stand-alone readout is also possible Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 61

Experimental Results • Tests with pixel readout chip (it works - three addresses can be distinguished, first testbeam measurement done, time stamp distribution ok => good time resolution) Signal amplitudes measured by FEI 4 CCPD Pixels 2 2 3 3 1 1 Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 62

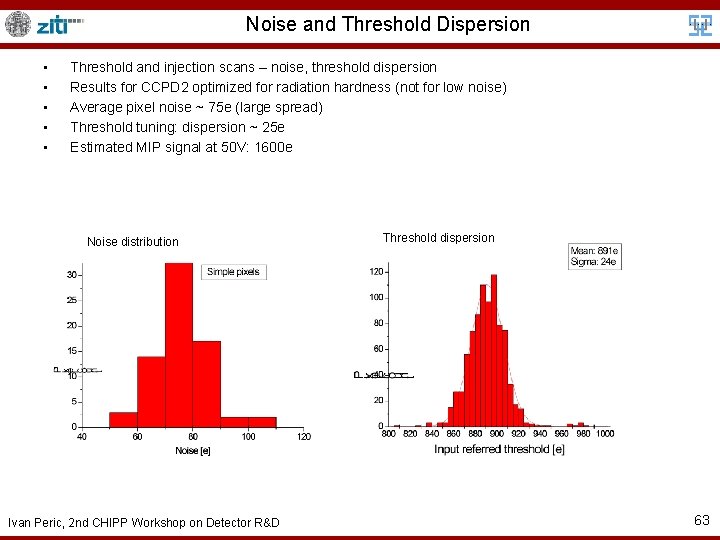

Noise and Threshold Dispersion • • • Threshold and injection scans – noise, threshold dispersion Results for CCPD 2 optimized for radiation hardness (not for low noise) Average pixel noise ~ 75 e (large spread) Threshold tuning: dispersion ~ 25 e Estimated MIP signal at 50 V: 1600 e Noise distribution Ivan Peric, 2 nd CHIPP Workshop on Detector R&D Threshold dispersion 63

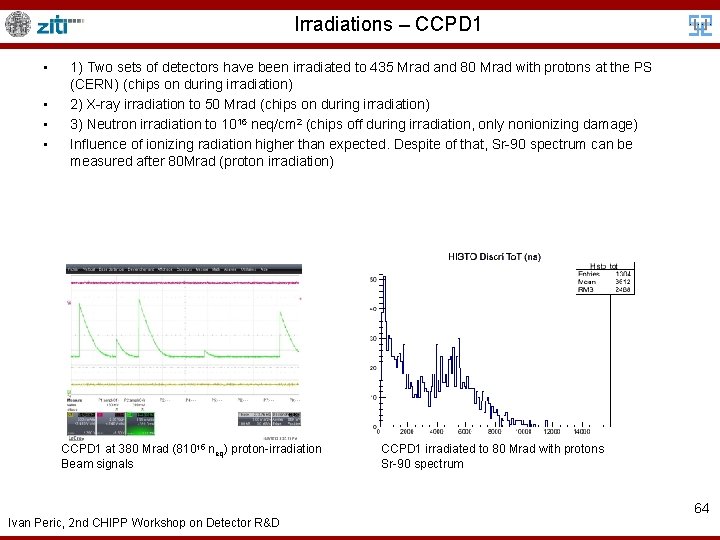

Irradiations – CCPD 1 • • 1) Two sets of detectors have been irradiated to 435 Mrad and 80 Mrad with protons at the PS (CERN) (chips on during irradiation) 2) X-ray irradiation to 50 Mrad (chips on during irradiation) 3) Neutron irradiation to 1016 neq/cm 2 (chips off during irradiation, only nonionizing damage) Influence of ionizing radiation higher than expected. Despite of that, Sr-90 spectrum can be measured after 80 Mrad (proton irradiation) CCPD 1 at 380 Mrad (81015 neq) proton-irradiation Beam signals CCPD 1 irradiated to 80 Mrad with protons Sr-90 spectrum 64 Ivan Peric, 2 nd CHIPP Workshop on Detector R&D

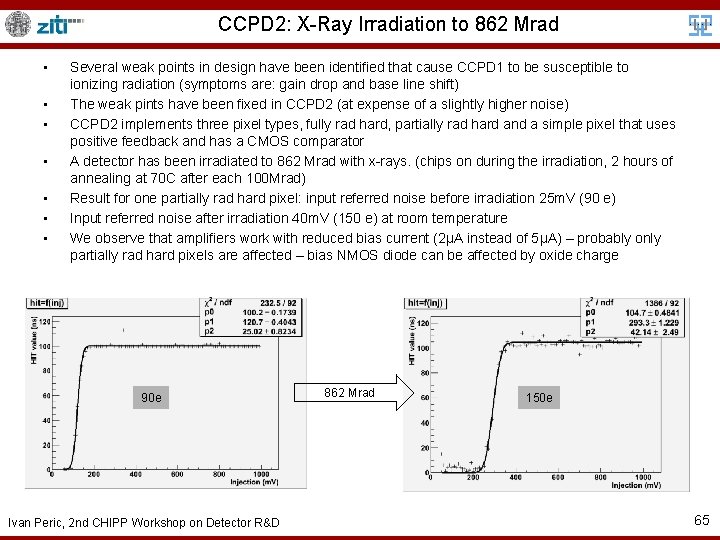

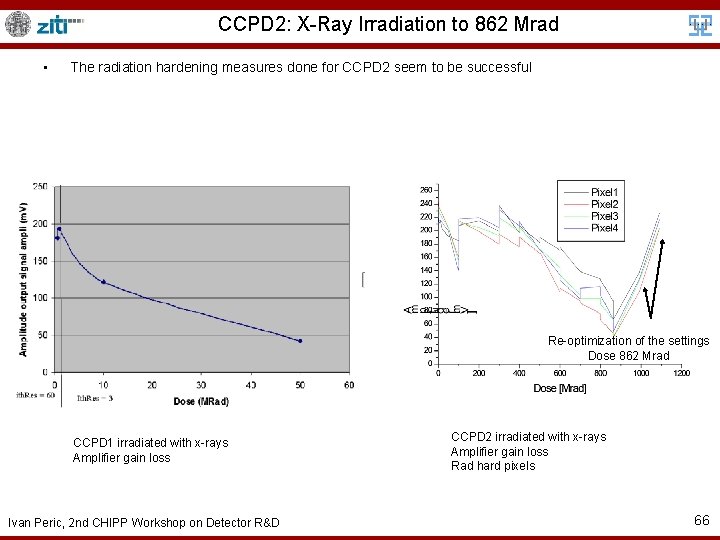

CCPD 2: X-Ray Irradiation to 862 Mrad • • Several weak points in design have been identified that cause CCPD 1 to be susceptible to ionizing radiation (symptoms are: gain drop and base line shift) The weak pints have been fixed in CCPD 2 (at expense of a slightly higher noise) CCPD 2 implements three pixel types, fully rad hard, partially rad hard and a simple pixel that uses positive feedback and has a CMOS comparator A detector has been irradiated to 862 Mrad with x-rays. (chips on during the irradiation, 2 hours of annealing at 70 C after each 100 Mrad) Result for one partially rad hard pixel: input referred noise before irradiation 25 m. V (90 e) Input referred noise after irradiation 40 m. V (150 e) at room temperature We observe that amplifiers work with reduced bias current (2µA instead of 5µA) – probably only partially rad hard pixels are affected – bias NMOS diode can be affected by oxide charge 90 e Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 862 Mrad 150 e 65

CCPD 2: X-Ray Irradiation to 862 Mrad • The radiation hardening measures done for CCPD 2 seem to be successful Re-optimization of the settings Dose 862 Mrad CCPD 1 irradiated with x-rays Amplifier gain loss Ivan Peric, 2 nd CHIPP Workshop on Detector R&D CCPD 2 irradiated with x-rays Amplifier gain loss Rad hard pixels 66

Segmented Strip Measurements • Setup Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 67

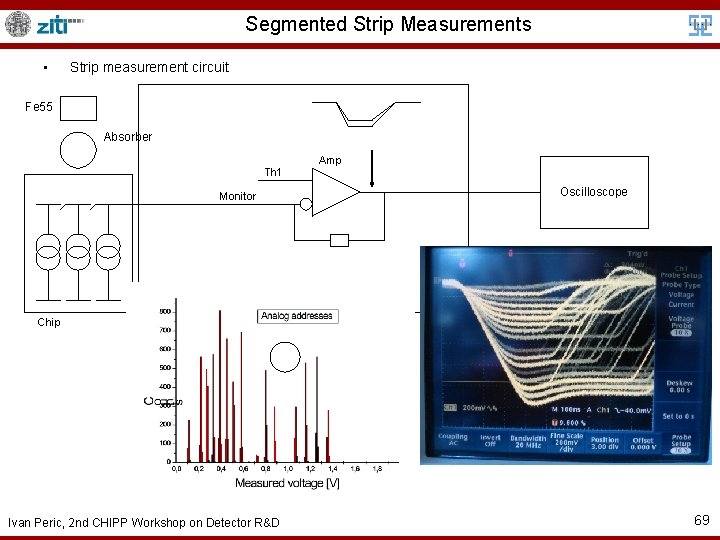

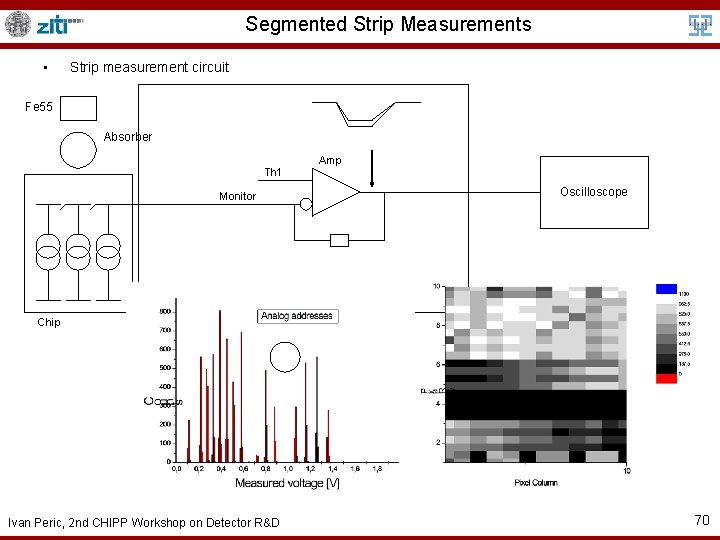

Segmented Strip Measurements • Strip measurement circuit Fe 55 Absorber Th 1 Monitor Amp Oscilloscope Chip Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 68

Segmented Strip Measurements • Strip measurement circuit Fe 55 Absorber Th 1 Monitor Amp Oscilloscope Chip Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 69

Segmented Strip Measurements • Strip measurement circuit Fe 55 Absorber Th 1 Monitor Amp Oscilloscope Chip Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 70

Conclusion and Outlook • • HVCMOS detectors are depleted monolithic detectors Good time resolution, high radiation tolerance, little material, low cost Planned applications: Mu 3 e, HLLHC and CLIC Results: Signal and noise should allow a good detection efficiency Detectors work after 1016 neq/cm 2 and 860 Mrad – efficiency should still to be measured Time resolution seems ok Synergy between projects: engineering run planned in 2014 Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 71

Thank you! Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 72

Backup Slides Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 73

Collection time measurement • • • Comparison of the response delay to capacitive test pulse (delay only caused by the amplifier) and the delay to IR pulse (delay caused by the amplifier and collection time). To assure that amplifier delay is equal, we equalize the signal amplitudes for both injections. The amplitudes are measured as To. T is proportional to the input charge. It does not depend on the amplifier rise times. Test signal Ampl. out Absorption of 850 nm light ~14µm Similar spatial distribution of the charge generation as for MIPs 1400 e Comp out N-well 5µ m 60% drift del 2 IR laser signal 10µ m Depleted (drift) Ampl. out 40% diffusion 1400 e Comp out Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 74

Collection time measurement • • Charge collection time – IR laser, comparison with the fast capacitive injection. No measurable delay versus the capacitive test pulse. Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 75

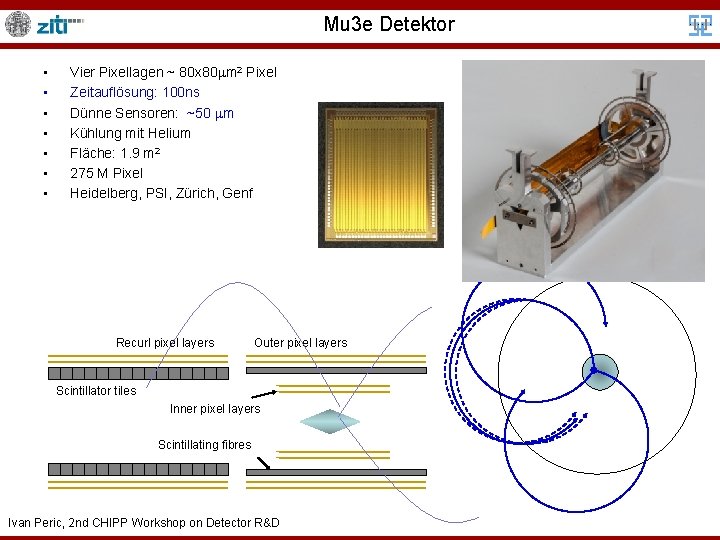

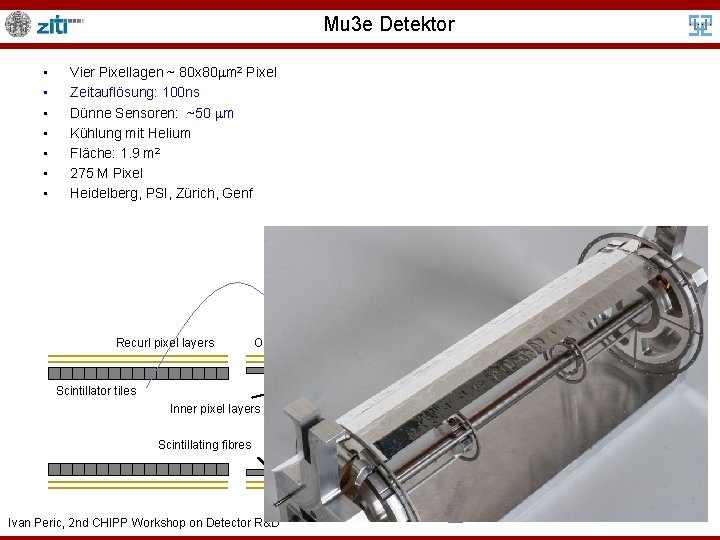

Mu 3 e Detektor • • Vier Pixellagen ~ 80 x 80 m 2 Pixel Zeitauflösung: 100 ns Dünne Sensoren: ~50 m Kühlung mit Helium Fläche: 1. 9 m 2 275 M Pixel Heidelberg, PSI, Zürich, Genf Recurl pixel layers Outer pixel layers Scintillator tiles Inner pixel layers Scintillating fibres Ivan Peric, 2 nd CHIPP Workshop on Detector R&D

Mu 3 e Detektor • • Vier Pixellagen ~ 80 x 80 m 2 Pixel Zeitauflösung: 100 ns Dünne Sensoren: ~50 m Kühlung mit Helium Fläche: 1. 9 m 2 275 M Pixel Heidelberg, PSI, Zürich, Genf Recurl pixel layers Outer pixel layers Scintillator tiles Inner pixel layers Scintillating fibres Ivan Peric, 2 nd CHIPP Workshop on Detector R&D

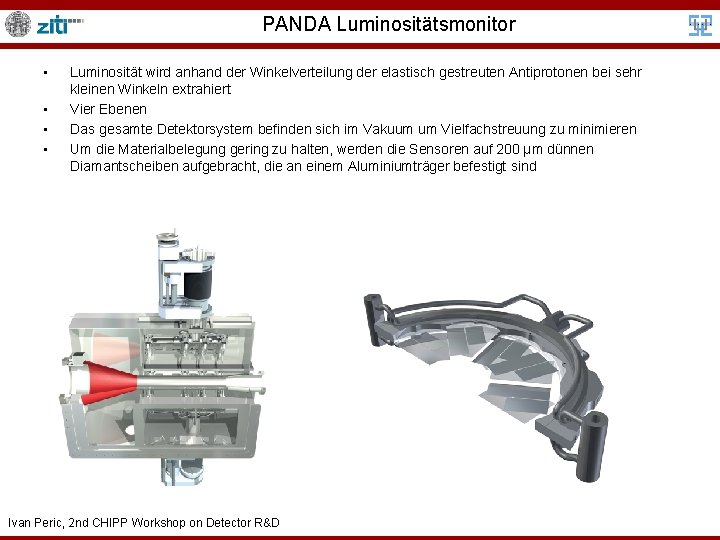

PANDA Luminositätsmonitor • • Luminosität wird anhand der Winkelverteilung der elastisch gestreuten Antiprotonen bei sehr kleinen Winkeln extrahiert Vier Ebenen Das gesamte Detektorsystem befinden sich im Vakuum um Vielfachstreuung zu minimieren Um die Materialbelegung gering zu halten, werden die Sensoren auf 200 µm dünnen Diamantscheiben aufgebracht, die an einem Aluminiumträger befestigt sind Ivan Peric, 2 nd CHIPP Workshop on Detector R&D

Signal-generation and amplification Ivan Peric, 2 nd CHIPP Workshop on Detector R&D

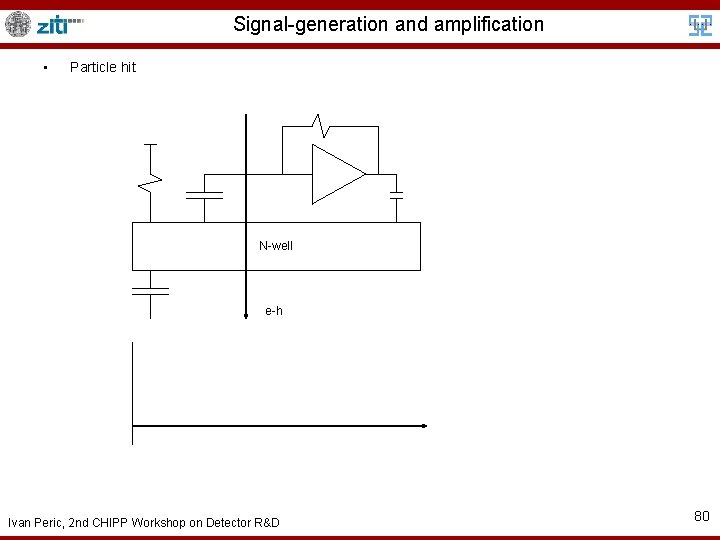

Signal-generation and amplification • Particle hit N-well e-h Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 80

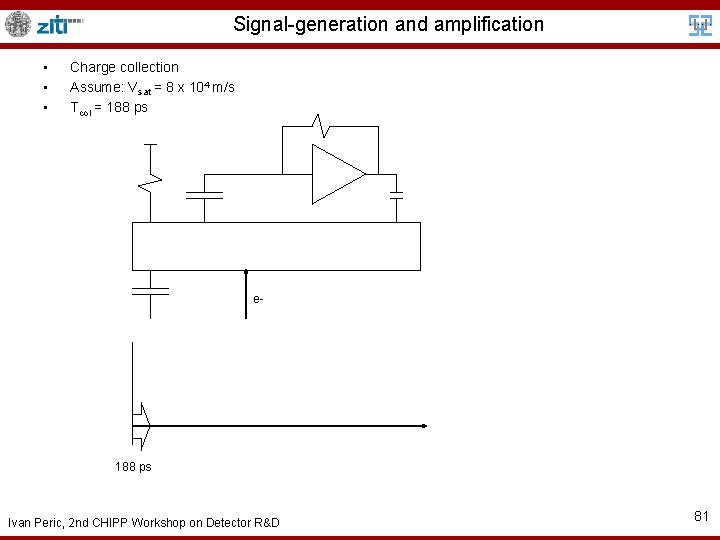

Signal-generation and amplification • • • Charge collection Assume: Vsat = 8 x 104 m/s Tcol = 188 ps e- 188 ps Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 81

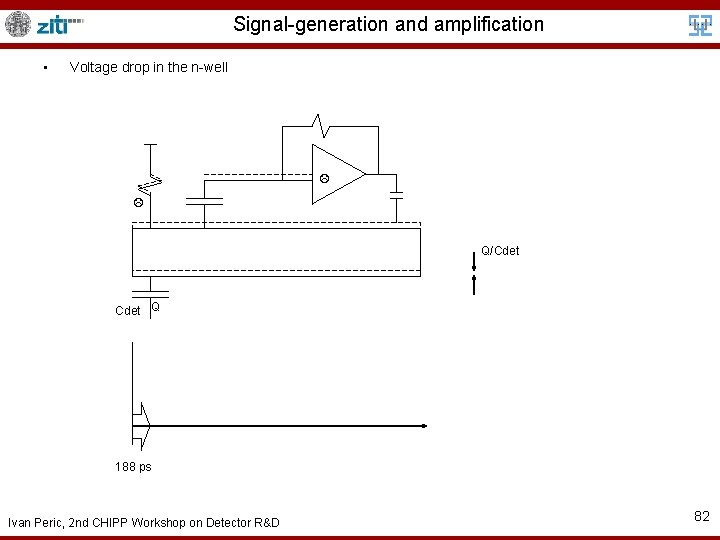

Signal-generation and amplification • Voltage drop in the n-well Q/Cdet Q 188 ps Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 82

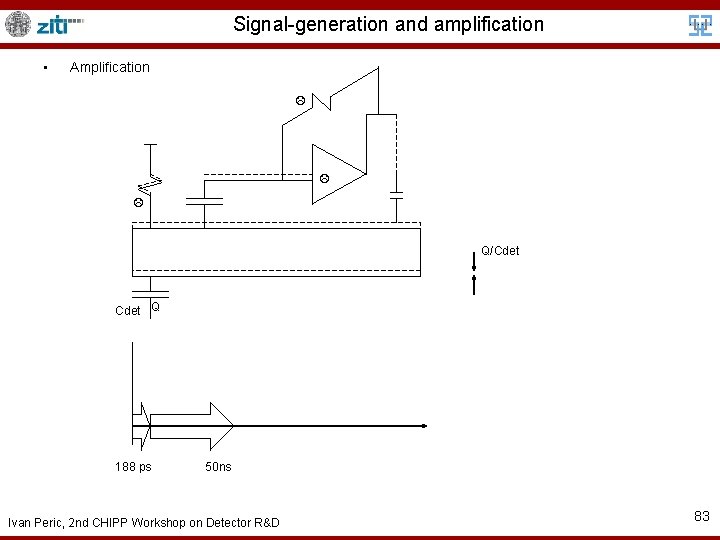

Signal-generation and amplification • Amplification Q/Cdet Q 188 ps 50 ns Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 83

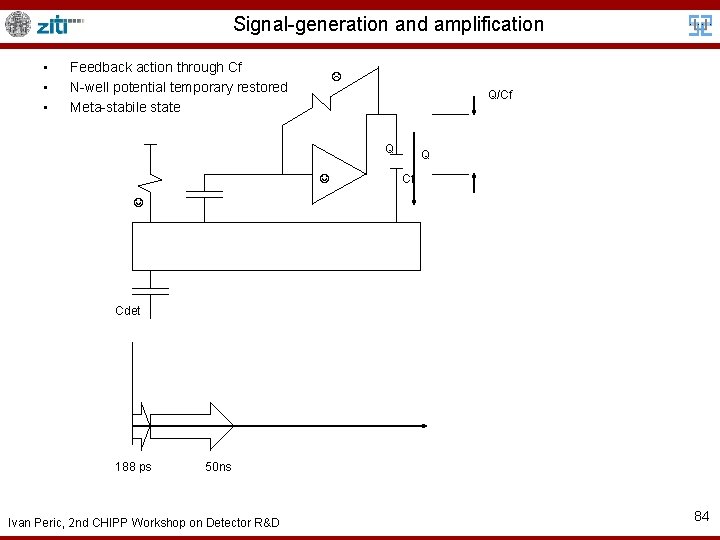

Signal-generation and amplification • • • Feedback action through Cf N-well potential temporary restored Meta-stabile state Q/Cf Q Q Cf Cdet 188 ps 50 ns Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 84

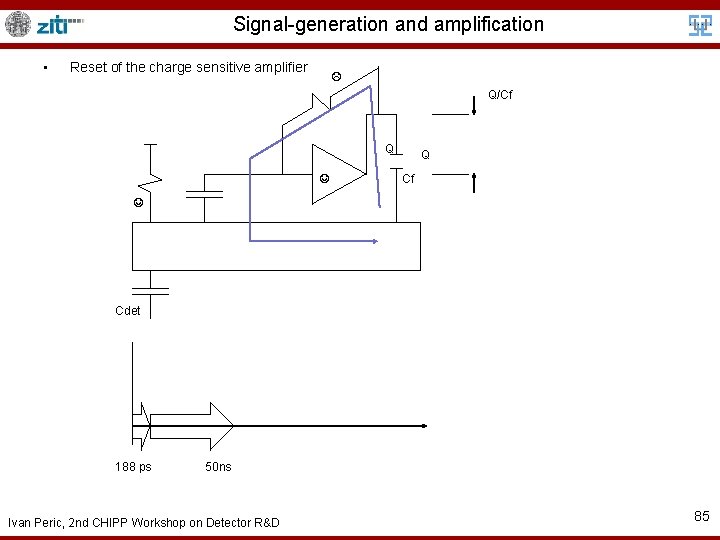

Signal-generation and amplification • Reset of the charge sensitive amplifier Q/Cf Q Q Cf Cdet 188 ps 50 ns Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 85

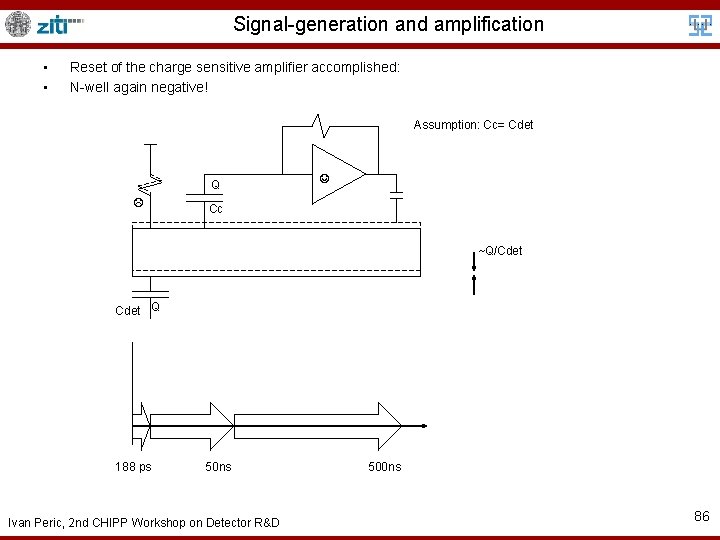

Signal-generation and amplification • • Reset of the charge sensitive amplifier accomplished: N-well again negative! Assumption: Cc= Cdet Q Cc ~Q/Cdet Q 188 ps 50 ns Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 500 ns 86

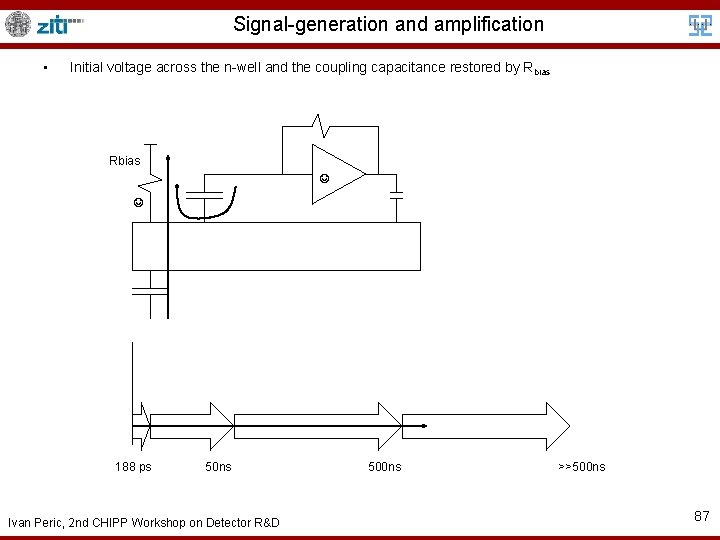

Signal-generation and amplification • Initial voltage across the n-well and the coupling capacitance restored by Rbias 188 ps 50 ns Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 500 ns >>500 ns 87

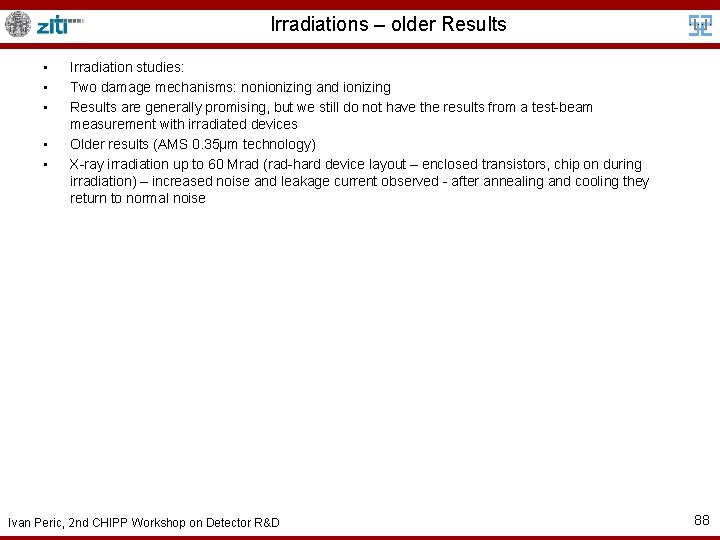

Irradiations – older Results • • • Irradiation studies: Two damage mechanisms: nonionizing and ionizing Results are generally promising, but we still do not have the results from a test-beam measurement with irradiated devices Older results (AMS 0. 35µm technology) X-ray irradiation up to 60 Mrad (rad-hard device layout – enclosed transistors, chip on during irradiation) – increased noise and leakage current observed - after annealing and cooling they return to normal noise Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 88

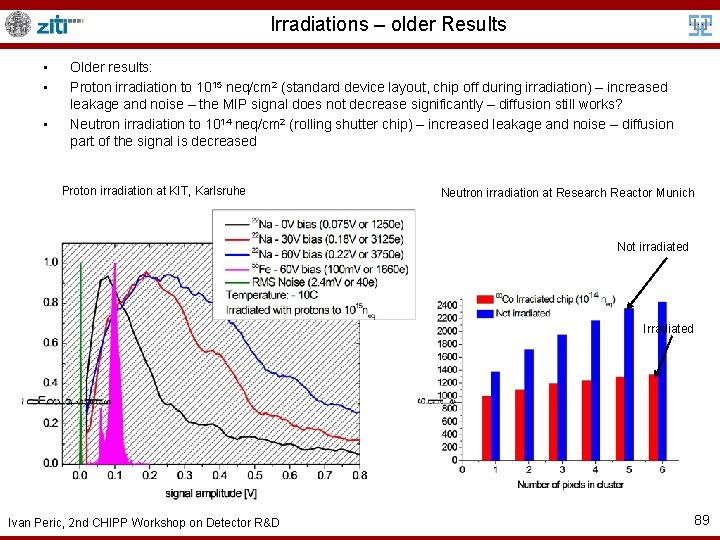

Irradiations – older Results • • • Older results: Proton irradiation to 1015 neq/cm 2 (standard device layout, chip off during irradiation) – increased leakage and noise – the MIP signal does not decrease significantly – diffusion still works? Neutron irradiation to 1014 neq/cm 2 (rolling shutter chip) – increased leakage and noise – diffusion part of the signal is decreased Proton irradiation at KIT, Karlsruhe Neutron irradiation at Research Reactor Munich Not irradiated Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 89

Standard CCPD Monolithic matrix CCPD matrix (sensor) wire bonds Electrodes chips Chip A Sensor pixels Signal transmission CCPD matrix (readout) Standard CCPD 55 x 70 µm pixel size Ivan Peric, 2 nd CHIPP Workshop on Detector R&D Chip B Readout pixels 90

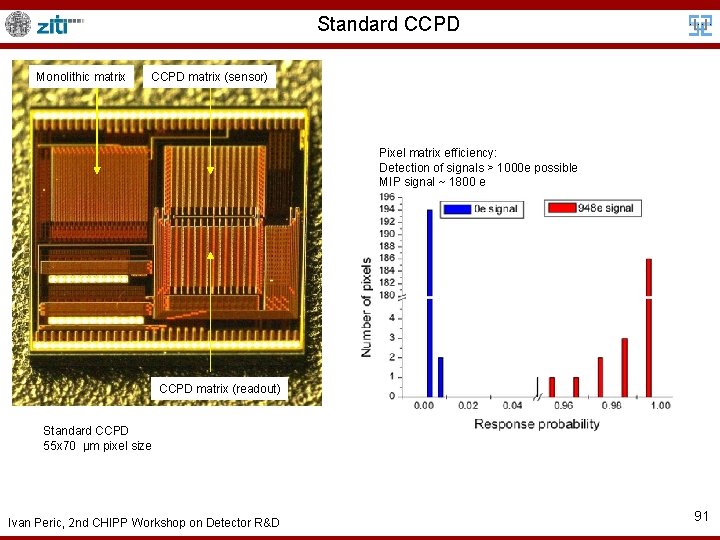

Standard CCPD Monolithic matrix CCPD matrix (sensor) Pixel matrix efficiency: Detection of signals > 1000 e possible MIP signal ~ 1800 e CCPD matrix (readout) Standard CCPD 55 x 70 µm pixel size Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 91

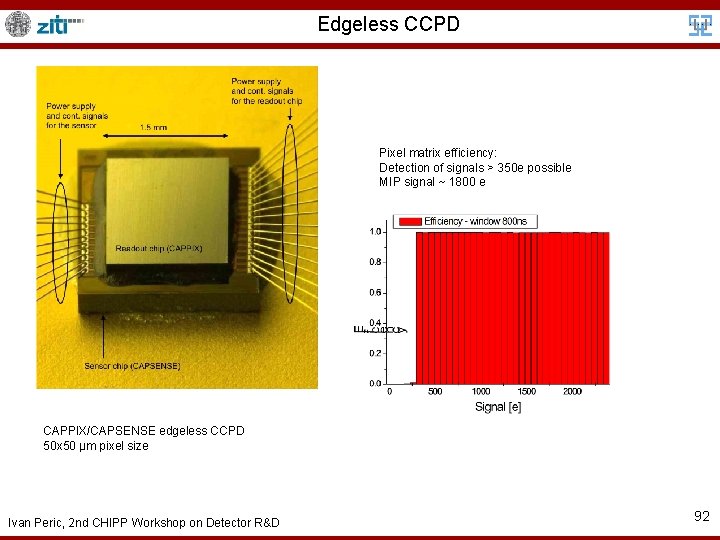

Edgeless CCPD Pixel matrix efficiency: Detection of signals > 350 e possible MIP signal ~ 1800 e CAPPIX/CAPSENSE edgeless CCPD 50 x 50 µm pixel size Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 92

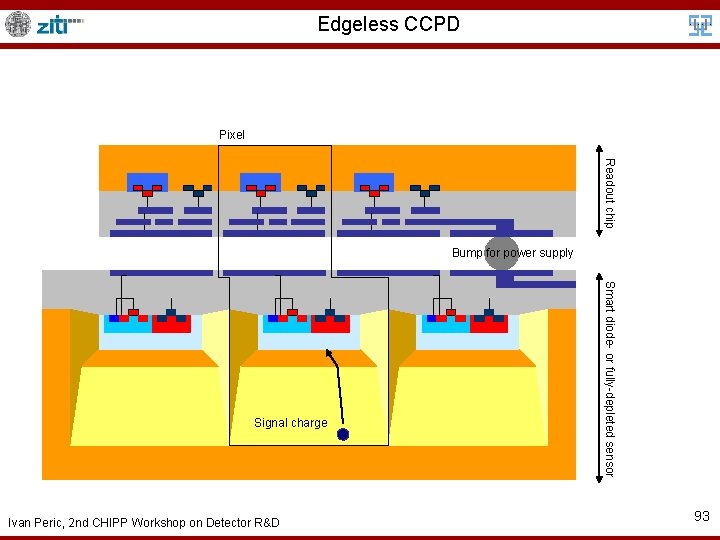

Edgeless CCPD Pixel Readout chip Bump for power supply Ivan Peric, 2 nd CHIPP Workshop on Detector R&D Smart diode- or fully-depleted sensor Signal charge 93

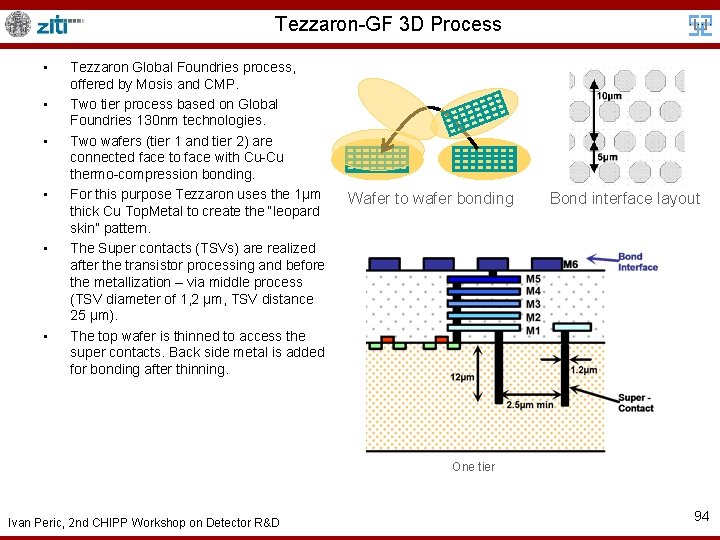

Tezzaron-GF 3 D Process • • • Tezzaron Global Foundries process, offered by Mosis and CMP. Two tier process based on Global Foundries 130 nm technologies. Two wafers (tier 1 and tier 2) are connected face to face with Cu-Cu thermo-compression bonding. For this purpose Tezzaron uses the 1µm thick Cu Top. Metal to create the “leopard skin” pattern. The Super contacts (TSVs) are realized after the transistor processing and before the metallization – via middle process (TSV diameter of 1, 2 µm, TSV distance 25 µm). The top wafer is thinned to access the super contacts. Back side metal is added for bonding after thinning. Wafer to wafer bonding Bond interface layout One tier Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 94

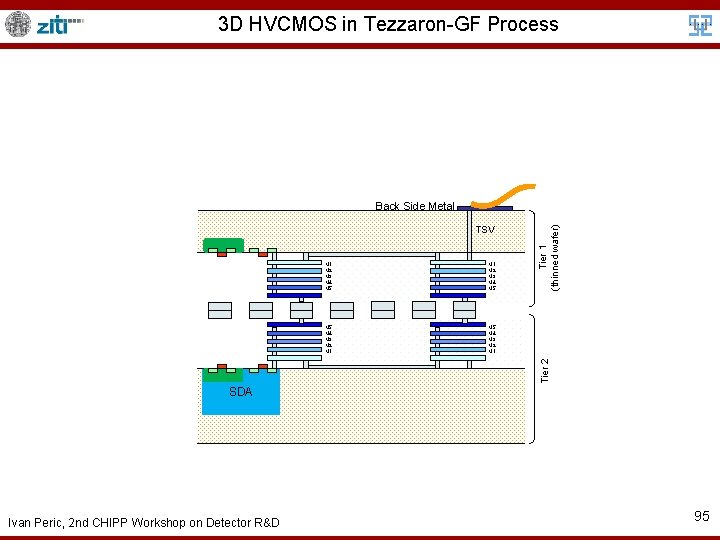

3 D HVCMOS in Tezzaron-GF Process TSV M 1 M 2 M 3 M 4 M 5 M 4 M 3 M 2 M 1 Tier 2 M 1 M 2 M 3 M 4 M 5 Tier 1 (thinned wafer) Back Side Metal SDA Ivan Peric, 2 nd CHIPP Workshop on Detector R&D 95

- Slides: 95