HighSpeed CircuitTuning Techniques Based on Lagrangian Relaxation Charlie

High-Speed Circuit-Tuning Techniques Based on Lagrangian Relaxation Charlie Chung-Ping Chen ICCAD 99’ Embedded Tutorial Session 12 A chen@engr. wisc. edu (608)2651145

People Involved • Joint work Charlie Chen, University of Wisconsin at Madison Chris Chu, Iowa State University D. F. Wong, University of Texas at Austin • Publication “Fast and Exact Simultaneous Gate and Wire Sizing by Lagrangian Relaxation”, IEEE Transactions on Computer-Aided Design, July 1999 High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Acknowledgement • Strategic CAD Labs, Intel Corp. Steve Burns, Prashant Sawkar, N. Sherwani, and Noel Menezes • IBM T. J. Watson Center Chandu Visweswariah • C. Kime, L. He (UWisc-Madison) High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Outline • Motivation • Overview of Circuit Tuning Techniques • Lagrangian Relaxation Based Circuit Tuning High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Motivation • Double the work load and design complexity every 18 months High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Motivation • Trends – – – Increased custom design Aggressive tuning for performance improvement Shorter time to market Interconnect effects severe Signal integrity issues emerging • Circuit Tuning – Can significantly improve circuit performance and signal integrity without major modification High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

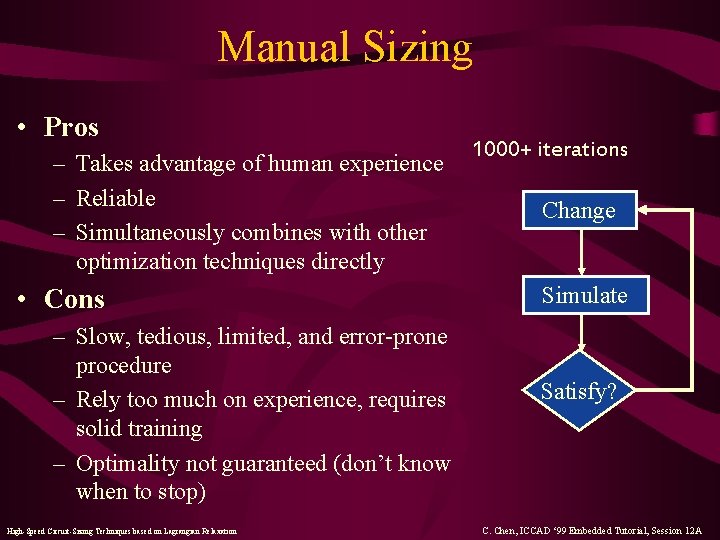

Manual Sizing • Pros – Takes advantage of human experience – Reliable – Simultaneously combines with other optimization techniques directly • Cons – Slow, tedious, limited, and error-prone procedure – Rely too much on experience, requires solid training – Optimality not guaranteed (don’t know when to stop) High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation 1000+ iterations Change Simulate Satisfy? C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Automatic Circuit Tuning • Pros – Fast – Achieves the best performance with interconnect considerations – Explores alternatives (power/delay/noise tradeoff) – Boosts productivity – Optimality guaranty (for convex problems) – Insures timing and reliability • Cons – Complicated tool development and support ($$) – Tool testing, integration, and training High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Good Tuning Algorithm • • • Fast Optimality guaranteed (for convex problem) Versatile Easy to use Solution quality index (error bound to the optimal solution) • Simple (Easy to develop and maintain) High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Static vs. Dynamic Sizing • Static Sizing – – – Stage Based Nature circuit decomposition, large scale tuning capability Very reasonable accuracy (when using good model) No need for sensitization vectors Solves for all critical paths in a polynomial formulation False paths; Potentially inaccurate modeling of slopes of input excitation • Dynamic Sizing – – Simulation based More accurate No false path problems Need good input vectors; good for circuits for which critical paths are known and limited – Takes care of a few scenario only – Relatively slower High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

A Simple Sizing Problem • Minimize the maximum delay Dmax by changing w 1, …, wn a w 9 w 7 w 4 w 11 High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation D 1<Dmax w 5 w 10 b w 1 w 8 w 6 w 3 w 2 D 2<Dmax C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Existing Sizing Works • Algorithm: fast, non-optimal for general problem formulation – TILOS (J. Fishburn, A. Dunlop, ICCAD 85’) – Weight Delay Optimization (J. Cong et al. , ICCAD 95’) • Mathematical Programming: slower, optimal – – – Geometrical Programming (TILOS) Augmented Lagrangian (D. P. Marple et al. , 86’) Sequential Linear Programming (S. Sapatnekar et al. ) Interior Point Method (S. Sapatnekar et al. , TCAD 93’) Sequential Quadratic Programming (N. Menezes et al. , DAC 95’) Augmented Lagrangian + Adjoin Sensitivity (C. Visweswariah et al. , ICCAD 96’, ICCAD 97’) • Is there any method that is fast and optimal? High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Converge? ? Weighted Delay Augmented Lagrangian SQP TILOS Fast Optimal SLP Algorithm High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation Mathematical Programming C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Heuristic Approach • TILOS: (J. Fishburn etc ICCAD 85’) – Find all the sensitivities associated with each gate – Up-Size one gate only with the maximum sensitivity – To minimize the object function w 1 a Minimize Dmax w 2 w 3 w 5 b w 4 w 6 w 7 High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation w 8 w 9 w 10 w 11 D 1<Dmax D 2<Dmax C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Weighted Delay Optimization • J. Cong ICCAD 95’ – Size one wire at a time in DFS order – To minimize the weighted delay – best weight? Drivers Minimize l 1 D 1 +l 2 D 2 w 1 w 2 w 4 High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation Loads w 3 w 5 l 1 D 1 l 2 D 2 C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Mathematical Programming • Problem Formulation: • Lagrangian: • Optimality (Necessary) Condition: (Kuhn-Tucker Condition) High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

PSLP v. s. SQP • Penalty Sequential Linear Programming • Sequential Quadratic Programming High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Lagrangian Methods • Augmented Lagrangian • Lagrangian Relaxation High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Lagrangian Relaxation Theory • LRS (Lagrangian Relaxation Subproblem) • There exist Lagrangian multipliers will lead LRS to find the optimal solution for convex programming problem • The optimal solution for any LRS is a lower bound of the original problem for any type of problem High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Lagrangian Relaxation High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Lagrangian Relaxation Weighted Delay Augmented Lagrangian SQP TILOS SLP Algorithm High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation Mathematical Programming C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Lagrangian Relaxation Framework Update Multipliers Weighted Delay Optimization Converge? High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Lagrangian Relaxation Framework More Critical -> More Resource -> More Weight D 1 D 2 l 1 l 2 Dmax D 1 D 2 High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation Dmax D 1 D 2 C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Weighted Minimization • Traverse the circuit in topological order • Resize each component to minimize Lagrangian during visit Minimize l 1 D 1 +l 2 D 2 w 1 a D 1 D 2 b w 2 High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation w 3 C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Multipliers Adjustment a subgradient approach • Subgradient: An extension definition of gradient for nonsmooth function • Experience: Simple heuristic implementation can achieve very good convergence rate • Reference: Non-smooth function optimization: N. Z. Shor High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Path Delay Formulation d 1 Aa Ab Ac d 2 D 1 d 3 D 2 • Exponential growing • More accurate • Can exclude false paths High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Stage Delay Formulation d 1 Aa Ab Ac Ae d 2 D 1 d 3 D 2 • Polynomial size • Less accurate • Contains false paths High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Compatible? ? Stage Based High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation Path Based C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Both Multipliers Satisfy KCL (Flow Conservation) Path Based Stage Based l 43 4 3 l 31 1 4 2 l 53 5 l 32 l 43 +l 53=l 31 +l 32 High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation l 41 l 1 51 3 5 l 3, in =l 3, out 2 l 42 l 52 C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Mixed Delay Formulation Stage Based High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation Path Based Stage Based C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Compatible? Lagrangian Relaxation Stage Based High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation Path Based C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Hierarchical Objective Function Decomposition • Divide the Lagrangian into who terms (containing or not containing variable wi ) • Hierarchically update the Lagrangian during resizing High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Intermediate Variables Cancellation Aa Ab Ae D 2 Ac lae lbe + D 1 lae + lbe = le 1 + le 2 le 1 le 2 lae (Aa + d 1 ) + lbe (Ab + dl + le 1 (d 2 - D 1 ) + le 2 (d 3 - D 2 ) 1 )c 2 High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Decomposition and Pruning • Flow Decomposition • Prune out all the gates with zero multipliers High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Complimentary Condition Implications • li (Di-Dmax )= 0 • Optimal Solution – Critical Path, weight l i >= 0. 0, path delay=Dmax – Non-critical path, weight l i = 0. 0, path delay < Dmax High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Convergence Sequence Max Delay Any Feasible Maximum Delay= Upper Bound Optimal Solution Lagrangian=Lower Bound Weighted Delay<=Maximum Delay # Iteration High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Transistor Sizing Extension High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Runtime and Storage Requirement High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Runtime versus Circuit Size High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Storage versus Circuit Size High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Convergence of Subgradient Optimization High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Area vs. Delay Tradeoff Curve High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

Conclusion • Lagrangian Relaxation – – – General mathematical programming algorithm Optimality guarantee for convex programming problem Versatile No extra complication (no quadratic penalty function) Lagrangian multiplier provides connections between mathematical programming and algorithmic approaches – Multipliers satisfy KCL (flow conservation) – Hierarchical update objective function provides extreme efficiency – Solution quality guaranteed (by providing lower bound) High-Speed Circuit-Sizing Techniques based on Lagrangian Relaxation C. Chen, ICCAD ‘ 99 Embedded Tutorial, Session 12 A

- Slides: 43