HighLevel Test Generation SATBased Diagnosis Test Generation by

High-Level Test Generation SAT-Based Diagnosis

Test Generation by Enhancing Validation Test Sets* * L. Lingappan, et al. , VLSI Design, 2007 (Paper available on the class website) SAT-Based Diagnosis

Basic Idea Reuse validation test sequences Fixed control sequence, only data path values need to be determined Precomputed module tests are used If validation sequences are instructionlevel, so are the generated tests RTL level analysis means faster times SAT-Based Diagnosis 3

Details Basis for analysis: RTL circuit and controller FSM CDFG and state transition sequence for a given validation test sequence Not all test sequences are analyzed for all precomputed test vectors because this could be computationally expensive. Instead, heuristics are used to determine compatibility. SAT-Based Diagnosis 4

Process Fault simulate validation test sequences and determine the activation time cycle for each detected fault. If a detected fault falls within a module, the sequence is a candidate for applying precomputed test vectors Determine compatibility of each test vector with the sequence If compatible, then justify and propagate SAT-Based Diagnosis 5

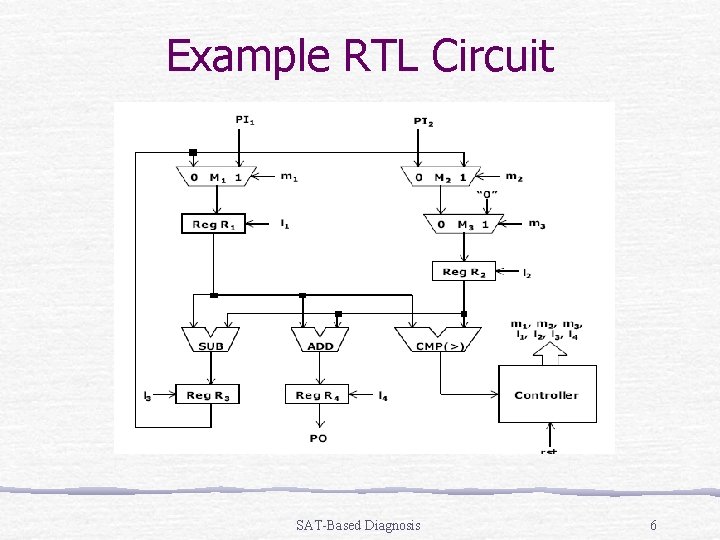

Example RTL Circuit SAT-Based Diagnosis 6

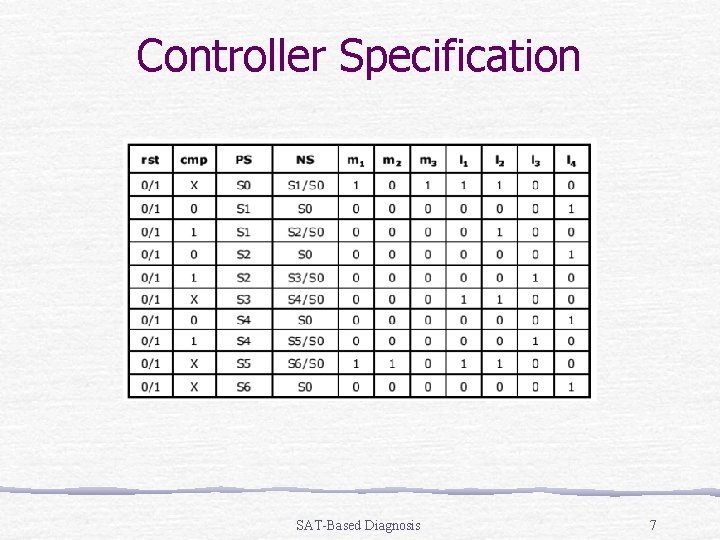

Controller Specification SAT-Based Diagnosis 7

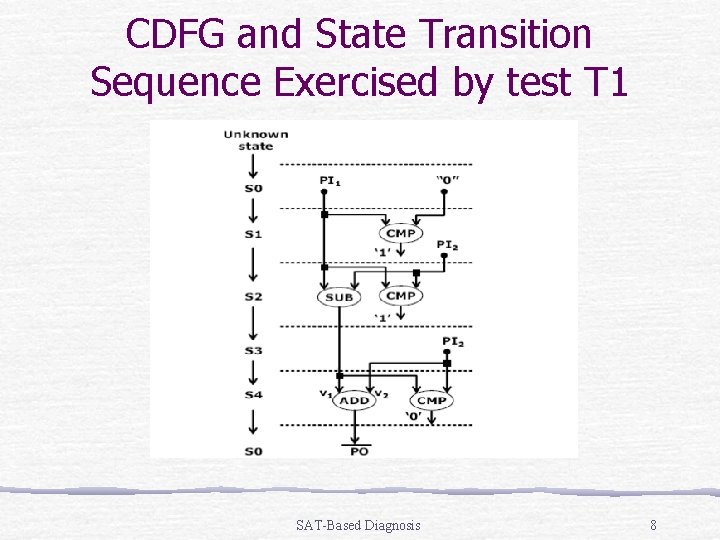

CDFG and State Transition Sequence Exercised by test T 1 SAT-Based Diagnosis 8

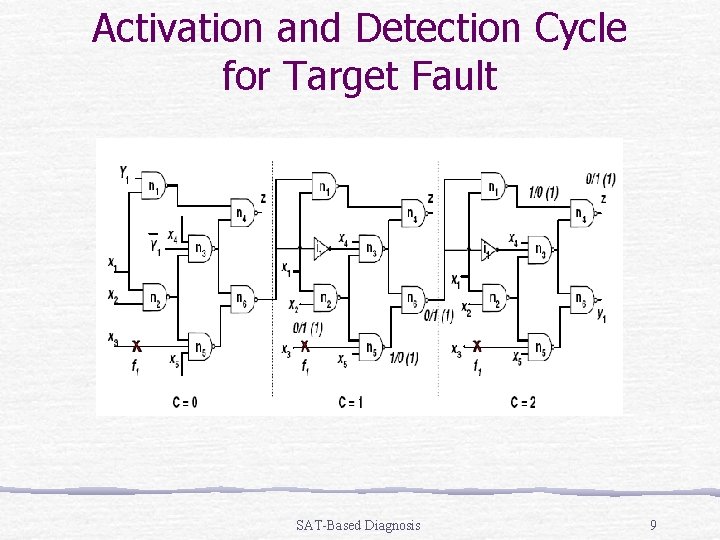

Activation and Detection Cycle for Target Fault SAT-Based Diagnosis 9

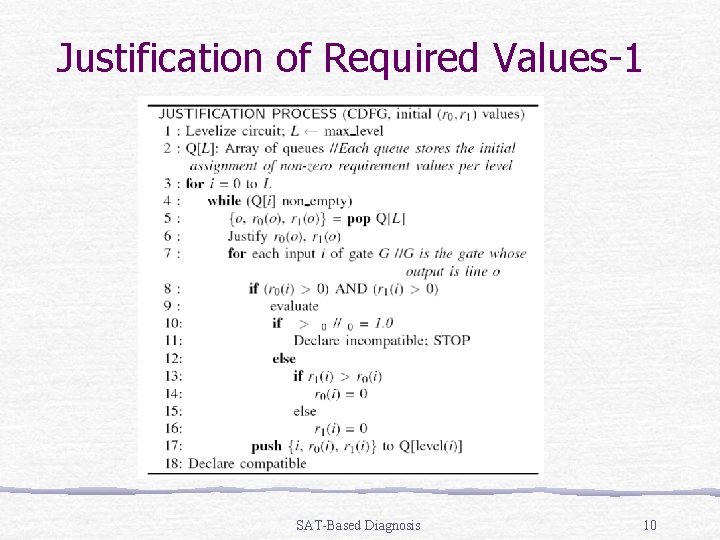

Justification of Required Values-1 SAT-Based Diagnosis 10

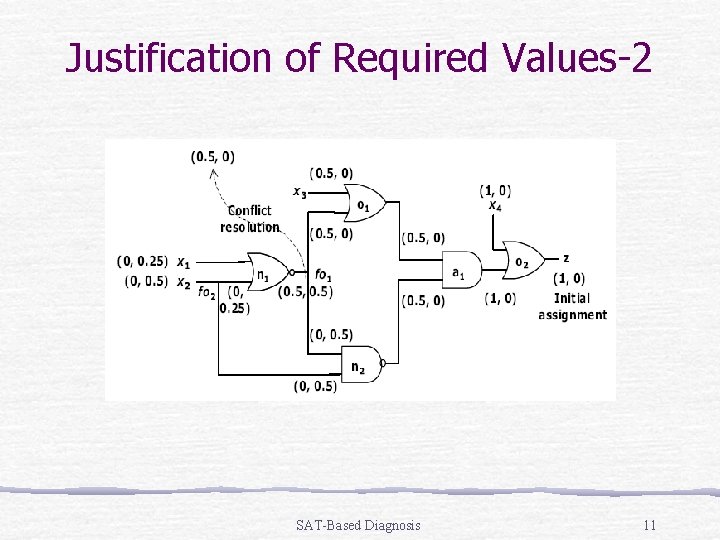

Justification of Required Values-2 SAT-Based Diagnosis 11

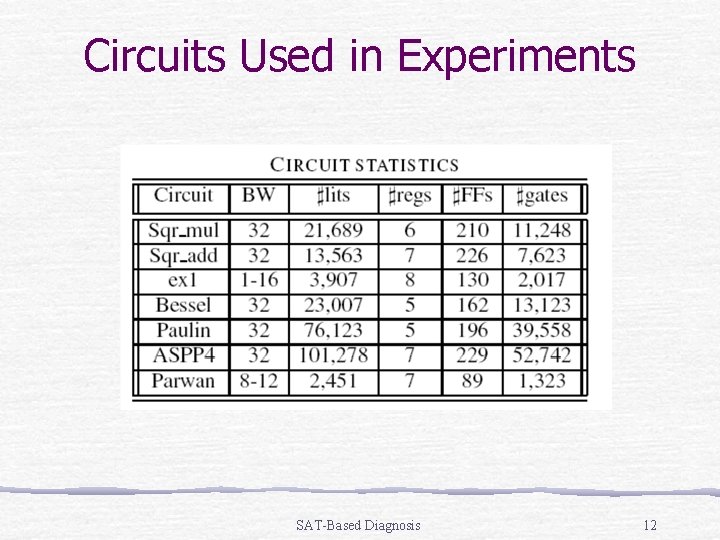

Circuits Used in Experiments SAT-Based Diagnosis 12

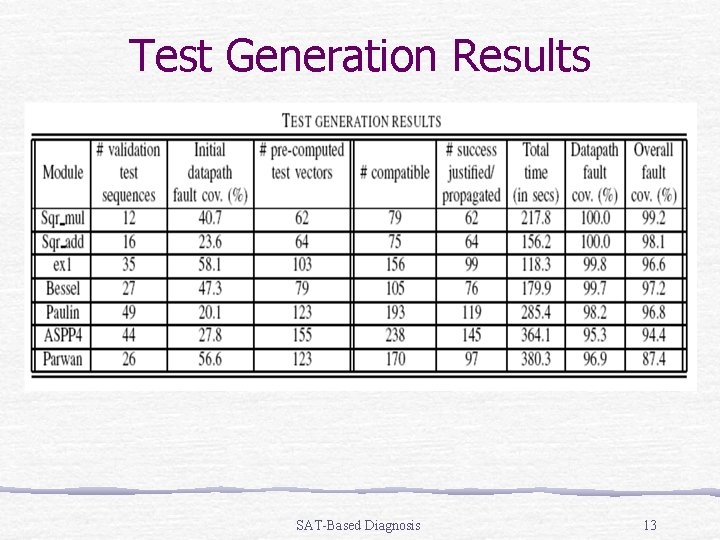

Test Generation Results SAT-Based Diagnosis 13

Test Generation with Functional Fault Modleing* * Hansen and Hayes, VLSI Test Symposium, 1995, pp. 20 -28. SAT-Based Diagnosis

Summary High-level fault modeling ensuring coverage of low-level (physical or single -stuck-line) faults. Fault effects induced from low (gate) to high (RTL or functional) level Allows discovery of minimum test sets at the high level that are hard to find by low (gate-level) techniques SAT-Based Diagnosis 15

Functional Fault Models General Faults (Universal) Pin Faults Both of the above are implementation and technology independent Induced faults: Physically Induced Faults (PIFs) Derived from an implementation by the induction process, hence implementation dependent and may be technology dependent. PIFs derived from single stuck-at faults are denoted as SIFs in the paper. SAT-Based Diagnosis 16

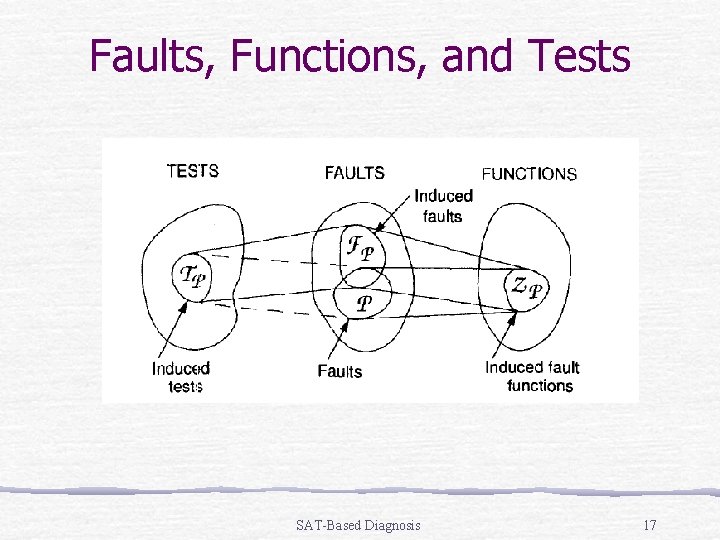

Faults, Functions, and Tests SAT-Based Diagnosis 17

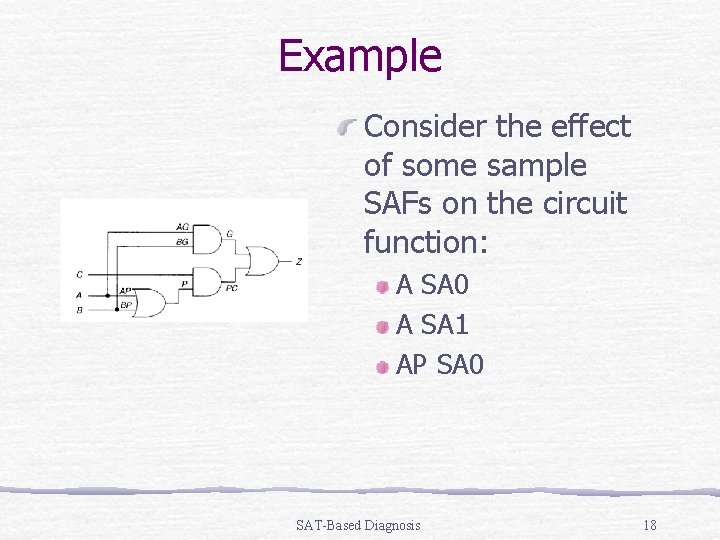

Example Consider the effect of some sample SAFs on the circuit function: A SA 0 A SA 1 AP SA 0 SAT-Based Diagnosis 18

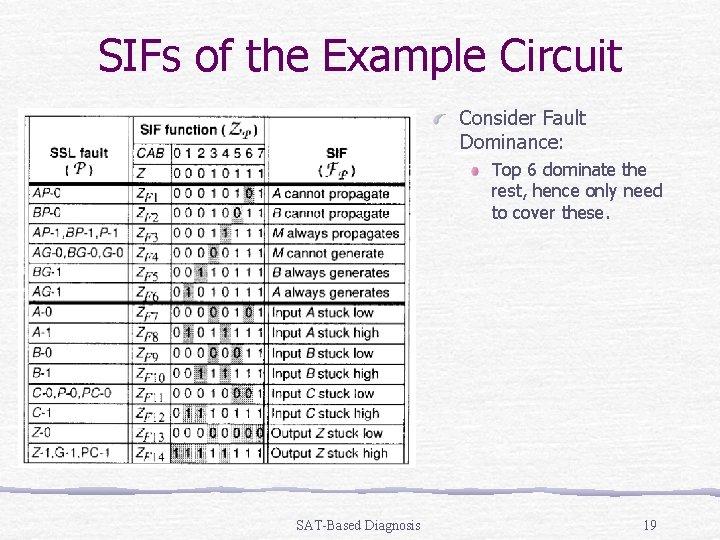

SIFs of the Example Circuit Consider Fault Dominance: Top 6 dominate the rest, hence only need to cover these. SAT-Based Diagnosis 19

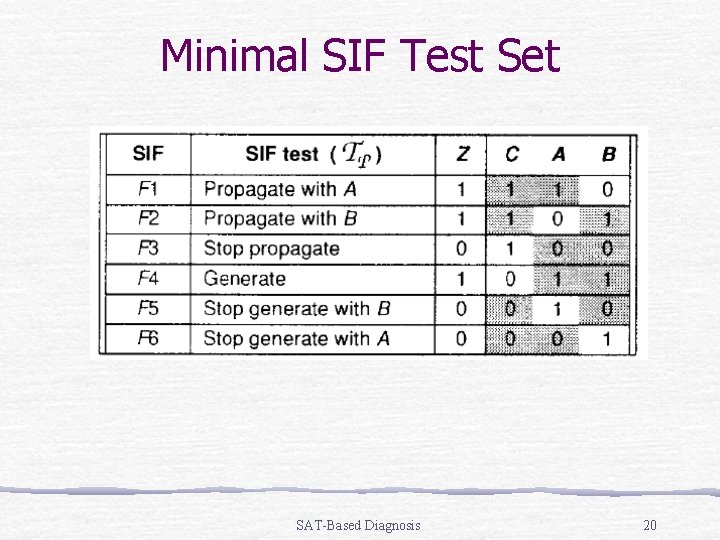

Minimal SIF Test Set SAT-Based Diagnosis 20

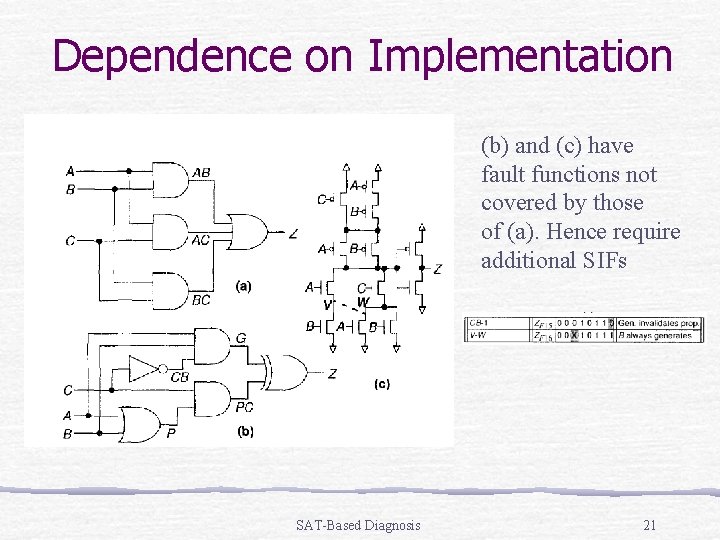

Dependence on Implementation (b) and (c) have fault functions not covered by those of (a). Hence require additional SIFs SAT-Based Diagnosis 21

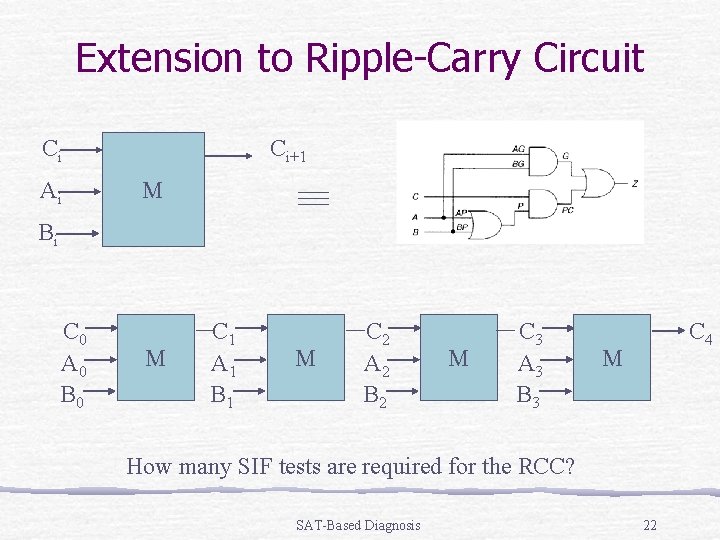

Extension to Ripple-Carry Circuit Ci Ai Ci+1 M Bi C 0 A 0 B 0 M C 1 A 1 B 1 M C 2 A 2 B 2 M C 3 A 3 B 3 C 4 M How many SIF tests are required for the RCC? SAT-Based Diagnosis 22

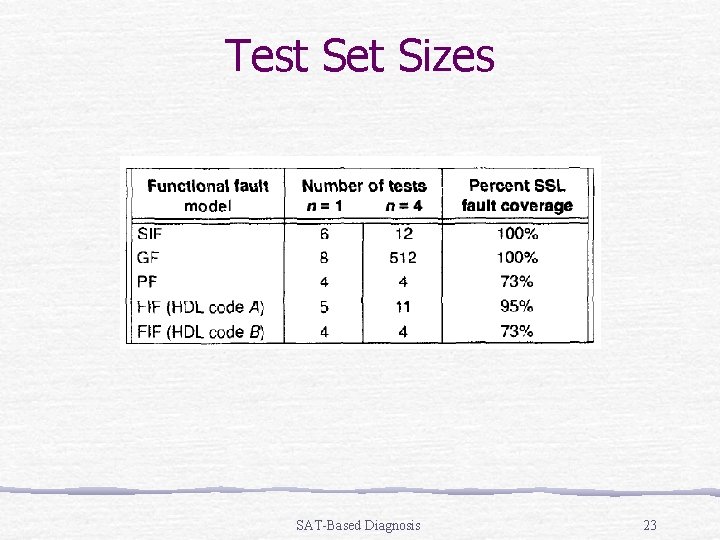

Test Set Sizes SAT-Based Diagnosis 23

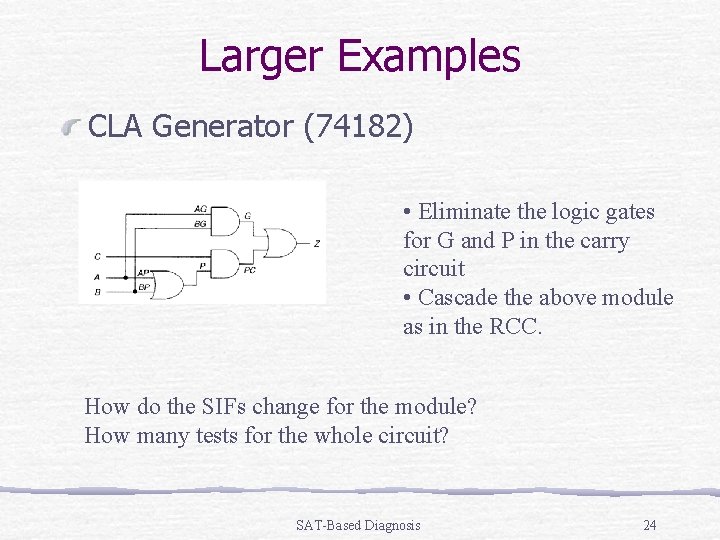

Larger Examples CLA Generator (74182) • Eliminate the logic gates for G and P in the carry circuit • Cascade the above module as in the RCC. How do the SIFs change for the module? How many tests for the whole circuit? SAT-Based Diagnosis 24

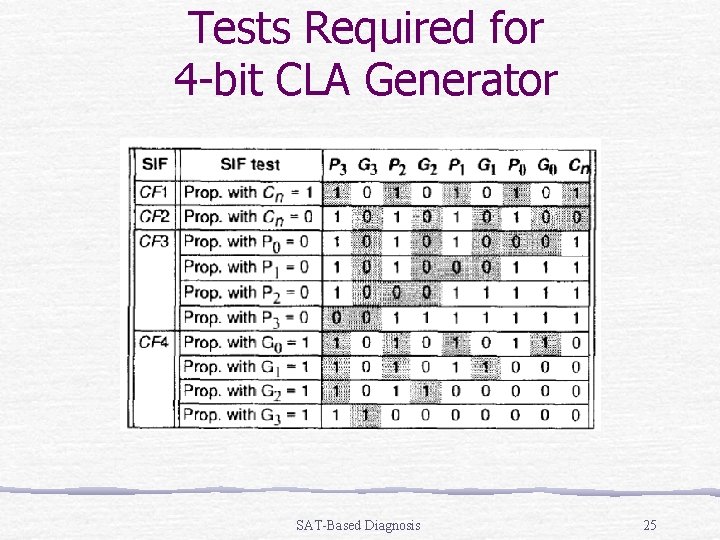

Tests Required for 4 -bit CLA Generator SAT-Based Diagnosis 25

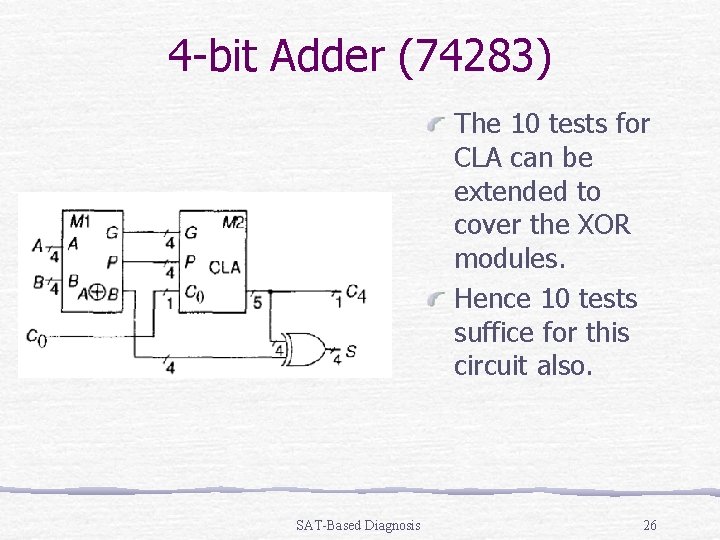

4 -bit Adder (74283) The 10 tests for CLA can be extended to cover the XOR modules. Hence 10 tests suffice for this circuit also. SAT-Based Diagnosis 26

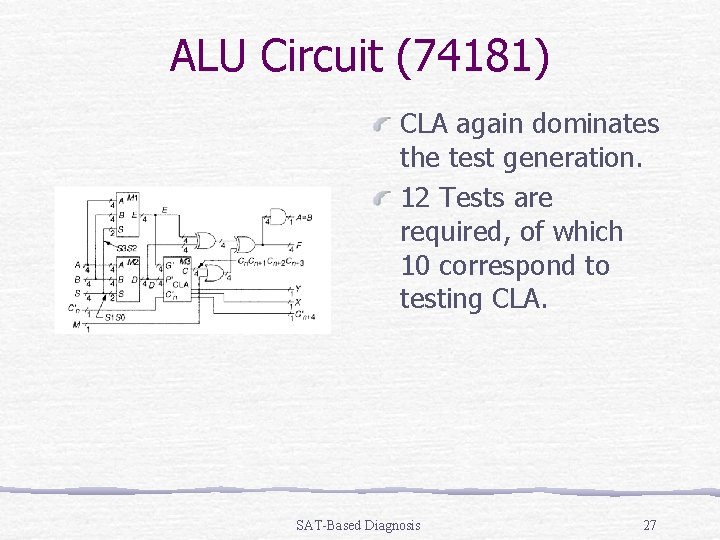

ALU Circuit (74181) CLA again dominates the test generation. 12 Tests are required, of which 10 correspond to testing CLA. SAT-Based Diagnosis 27

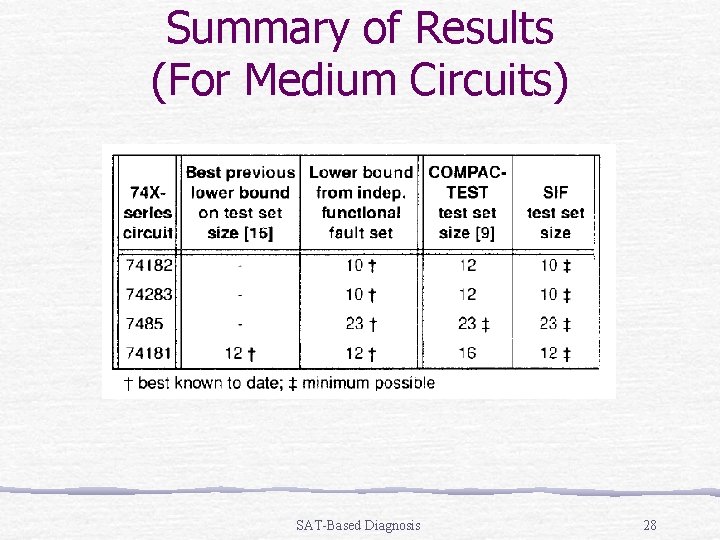

Summary of Results (For Medium Circuits) SAT-Based Diagnosis 28

The paper goes on to apply the technique to ISCAS 85 circuits. They needed to extract high-level models for these circuits by painstaking reverse-engineering. These models are available from Prof. Hayes’ website at U. Michigan. SAT-Based Diagnosis 29

Conclusion Physical fault effects induced at the functional level Unlike prior high-level models, PIFs allow complete low-level coverage. However, the analysis is not automatic and the results do depend on the implementation The technique allowed obtaining provably minimum test sets for various common known implementations. SAT-Based Diagnosis 30

- Slides: 30