High Speed Equalizer Circuits ECE 1352 Jenkin Wong

- Slides: 15

High Speed Equalizer Circuits ECE 1352 Jenkin Wong November 28, 2003 Jenkin Wong

Agenda Background • Why Equalize? Equalization for 100 Base-TX Ethernet • Introduction • Define Problem • Proposed Solution Jenkin Wong 2

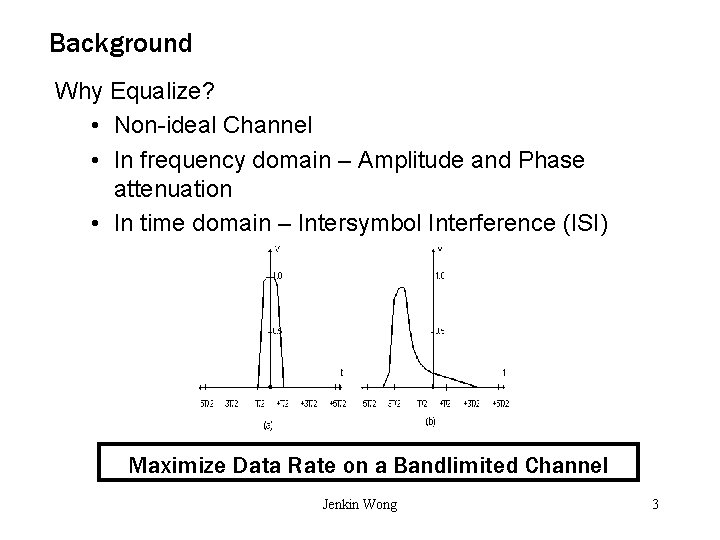

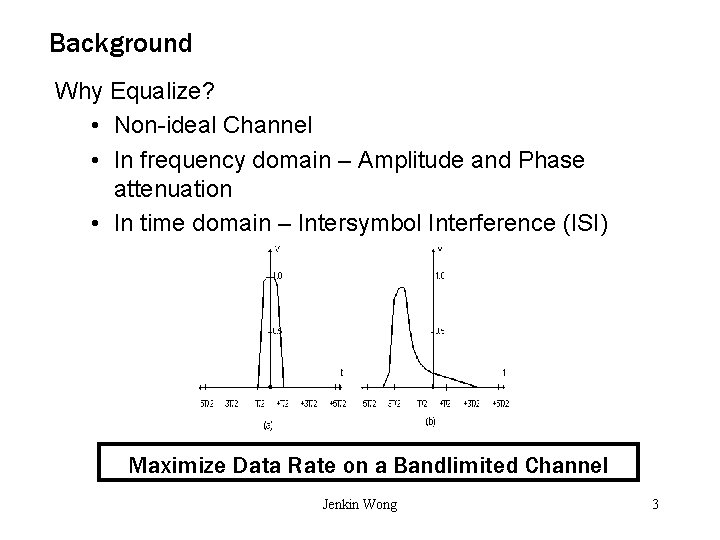

Background Why Equalize? • Non-ideal Channel • In frequency domain – Amplitude and Phase attenuation • In time domain – Intersymbol Interference (ISI) Maximize Data Rate on a Bandlimited Channel Jenkin Wong 3

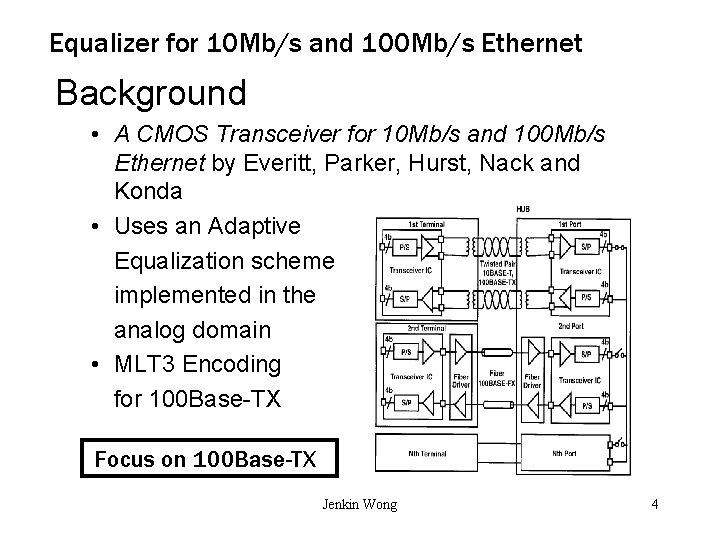

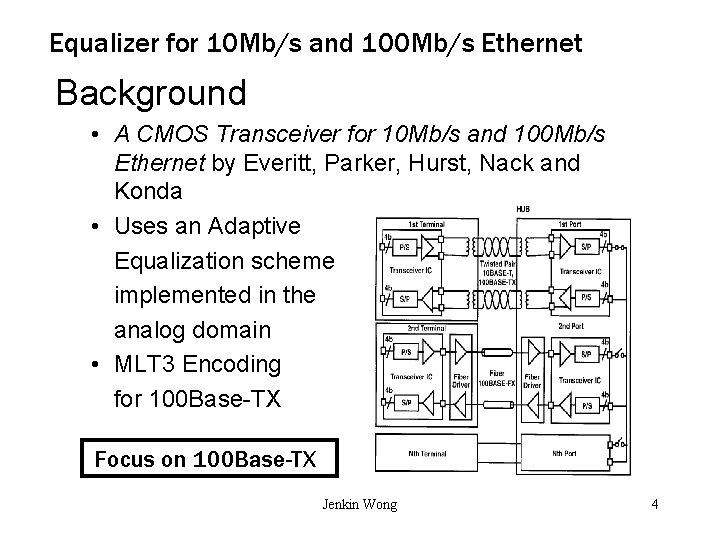

Equalizer for 10 Mb/s and 100 Mb/s Ethernet Background • A CMOS Transceiver for 10 Mb/s and 100 Mb/s Ethernet by Everitt, Parker, Hurst, Nack and Konda • Uses an Adaptive Equalization scheme implemented in the analog domain • MLT 3 Encoding for 100 Base-TX Focus on 100 Base-TX Jenkin Wong 4

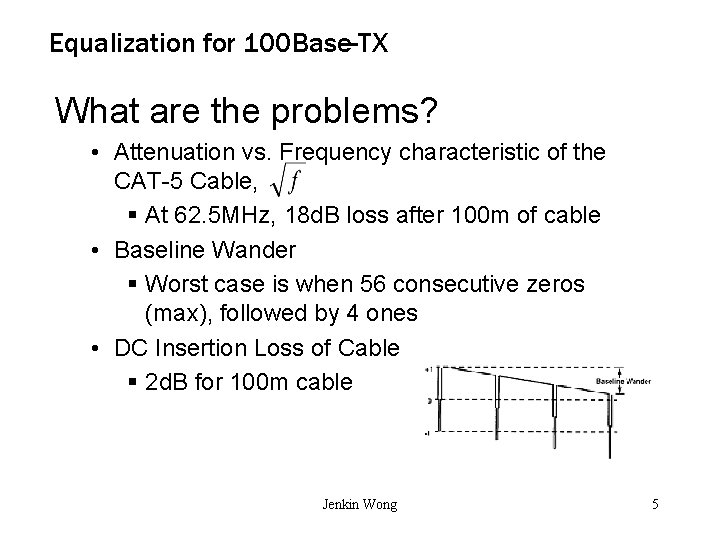

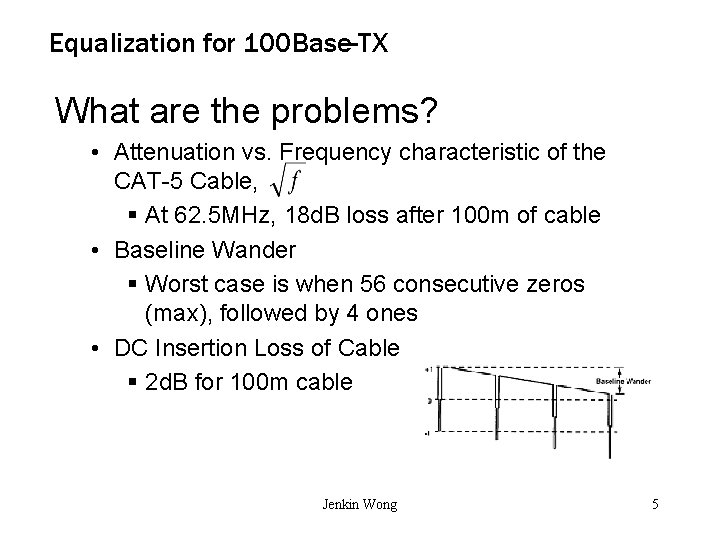

Equalization for 100 Base-TX What are the problems? • Attenuation vs. Frequency characteristic of the CAT-5 Cable, § At 62. 5 MHz, 18 d. B loss after 100 m of cable • Baseline Wander § Worst case is when 56 consecutive zeros (max), followed by 4 ones • DC Insertion Loss of Cable § 2 d. B for 100 m cable Jenkin Wong 5

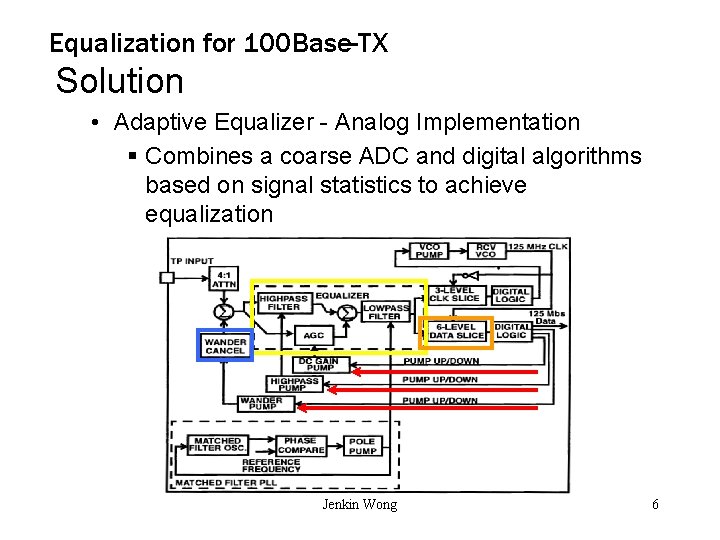

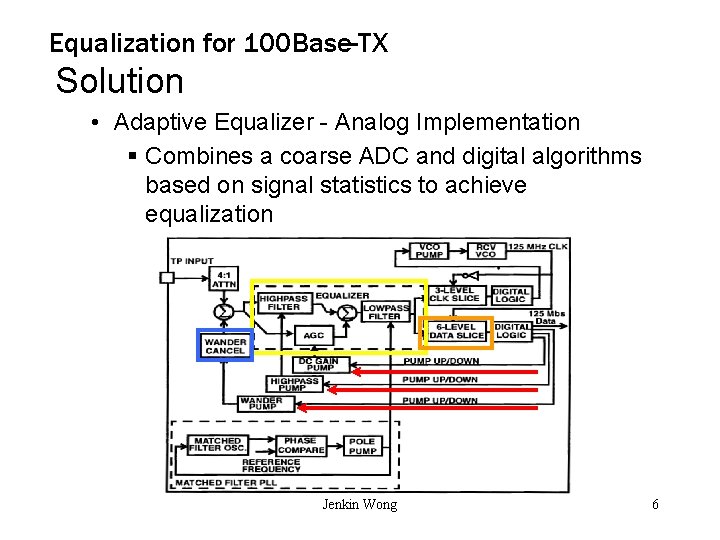

Equalization for 100 Base-TX Solution • Adaptive Equalizer - Analog Implementation § Combines a coarse ADC and digital algorithms based on signal statistics to achieve equalization Jenkin Wong 6

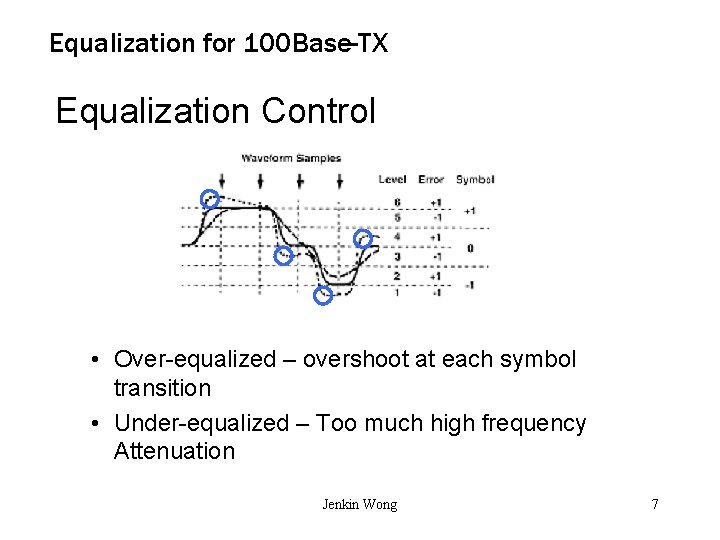

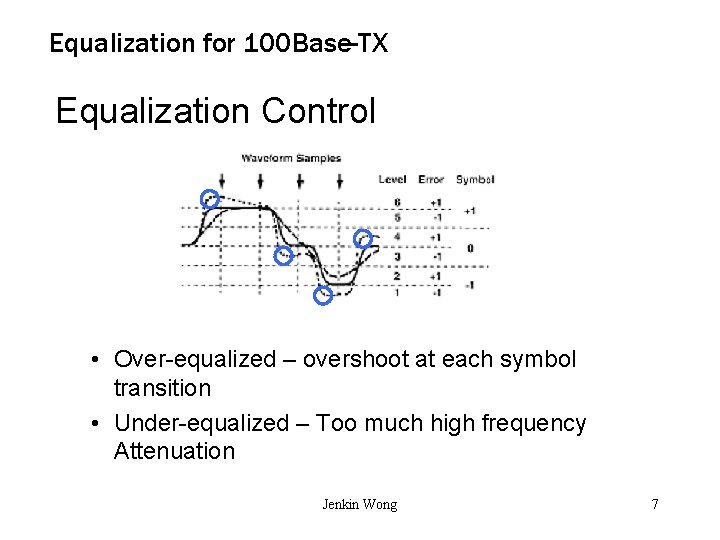

Equalization for 100 Base-TX Equalization Control • Over-equalized – overshoot at each symbol transition • Under-equalized – Too much high frequency Attenuation Jenkin Wong 7

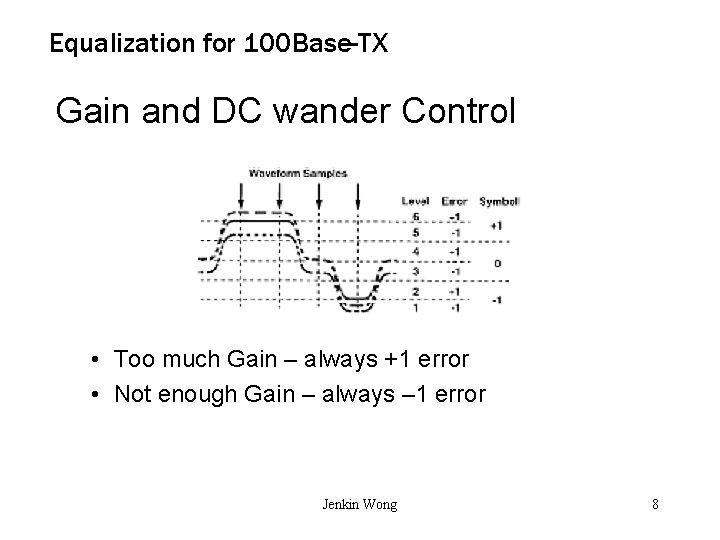

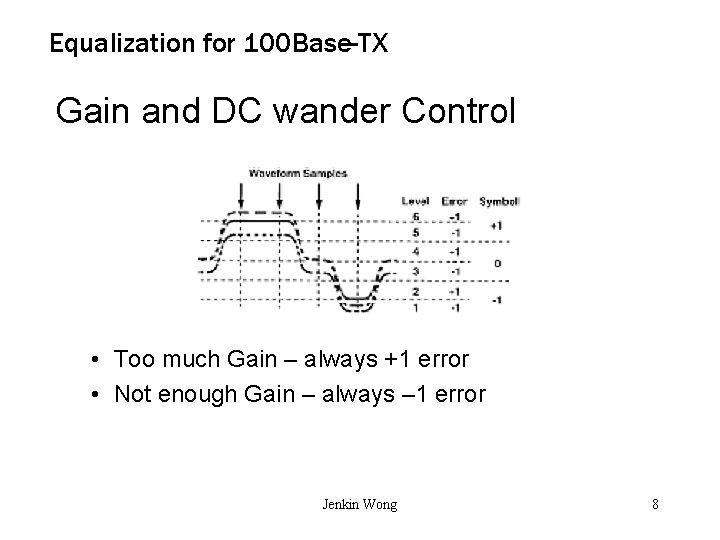

Equalization for 100 Base-TX Gain and DC wander Control • Too much Gain – always +1 error • Not enough Gain – always – 1 error Jenkin Wong 8

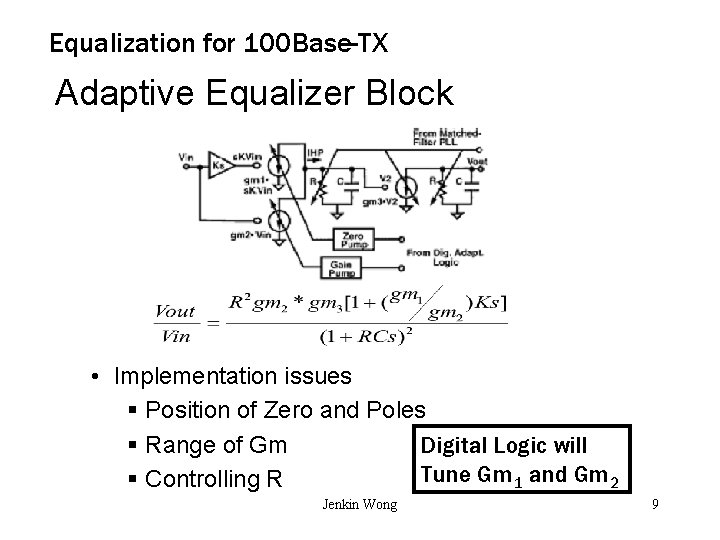

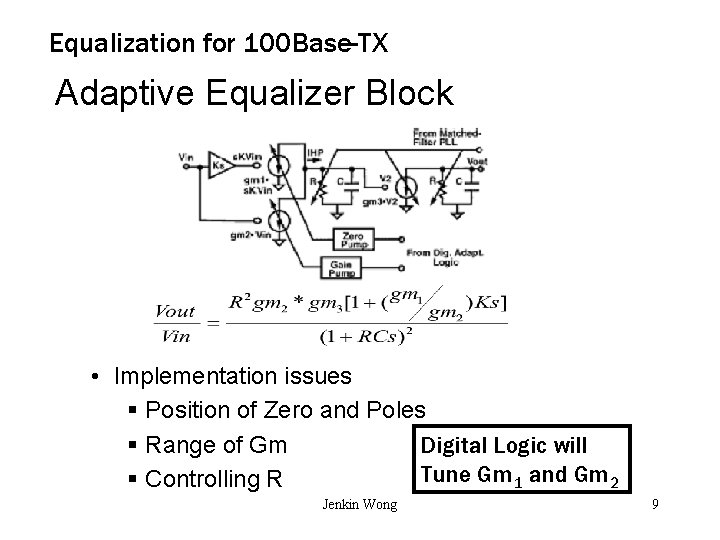

Equalization for 100 Base-TX Adaptive Equalizer Block • Implementation issues § Position of Zero and Poles Digital Logic will § Range of Gm Tune Gm 1 and Gm 2 § Controlling R Jenkin Wong 9

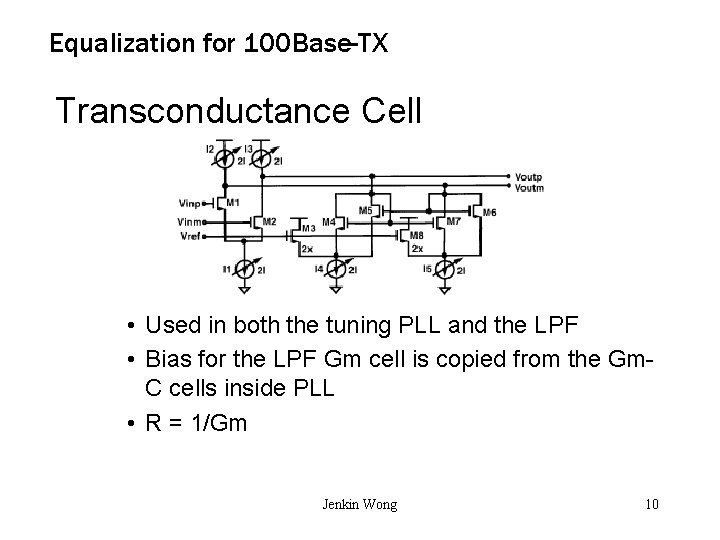

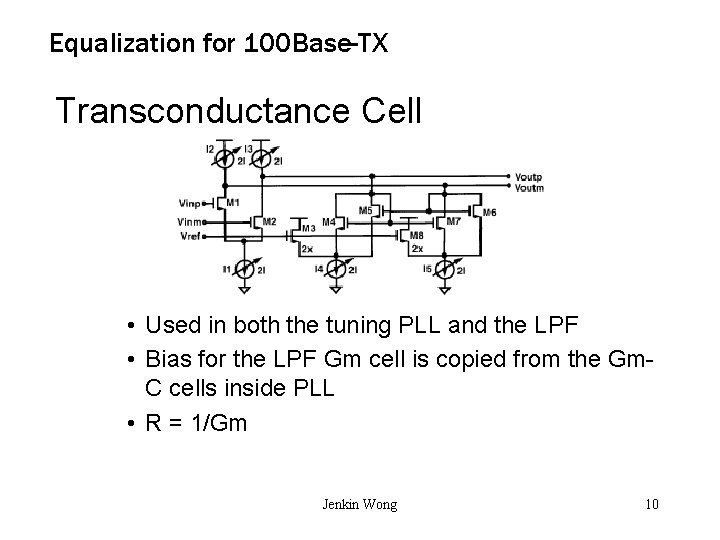

Equalization for 100 Base-TX Transconductance Cell • Used in both the tuning PLL and the LPF • Bias for the LPF Gm cell is copied from the Gm. C cells inside PLL • R = 1/Gm Jenkin Wong 10

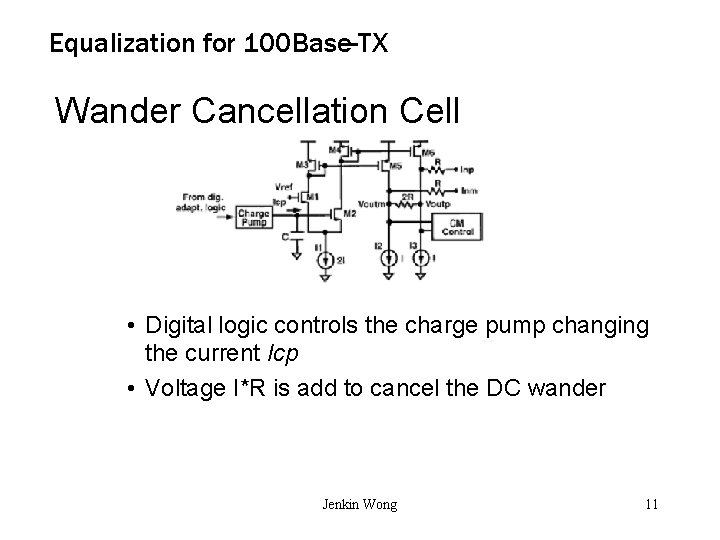

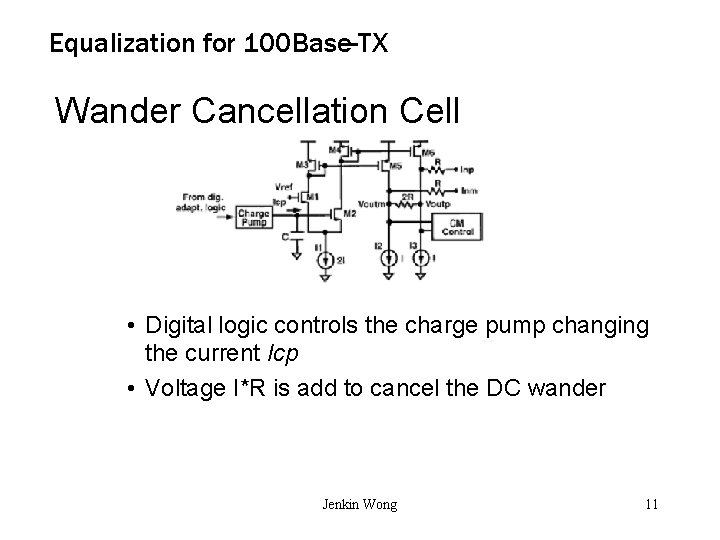

Equalization for 100 Base-TX Wander Cancellation Cell • Digital logic controls the charge pump changing the current Icp • Voltage I*R is add to cancel the DC wander Jenkin Wong 11

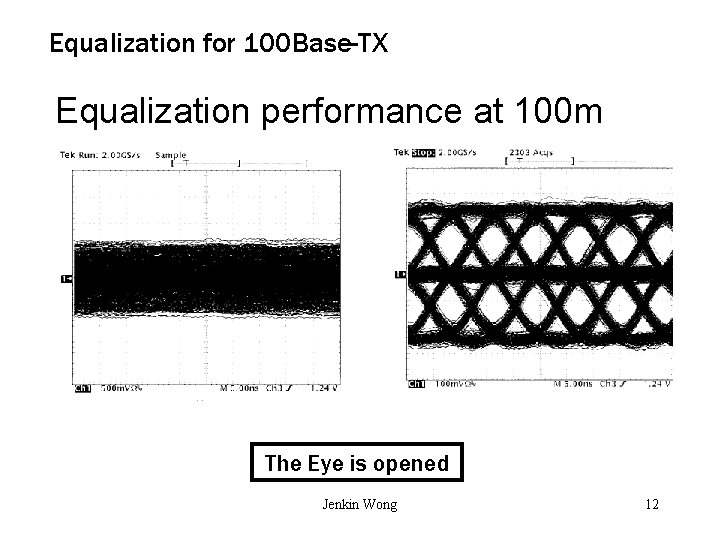

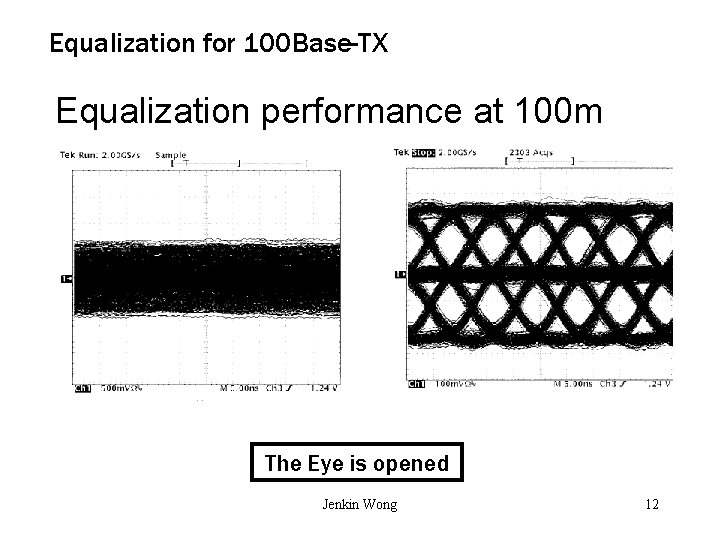

Equalization for 100 Base-TX Equalization performance at 100 m The Eye is opened Jenkin Wong 12

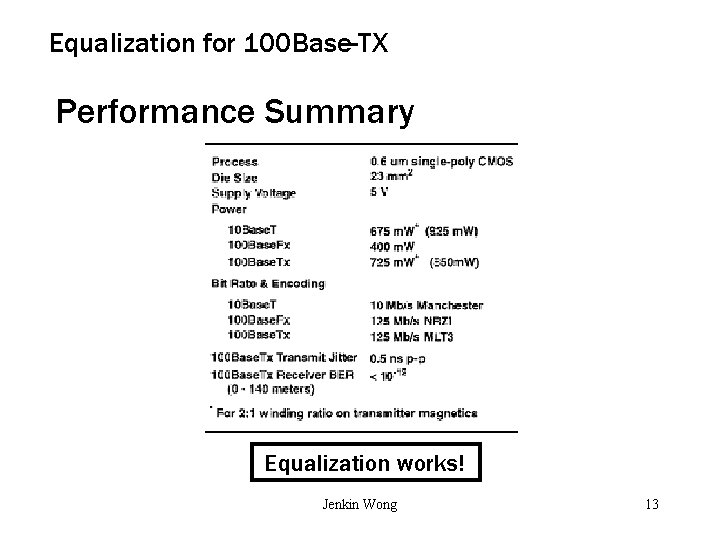

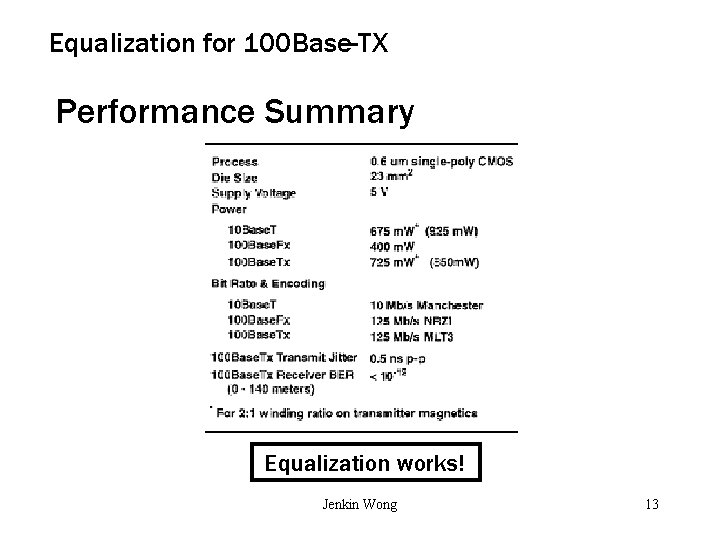

Equalization for 100 Base-TX Performance Summary Equalization works! Jenkin Wong 13

Equalization for 100 Base-TX Conclusion • Crash course on Equalization • Analog Implementation of a High Speed adaptive equalization scheme for 100 Base-TX • Equalization is one of the many keys to reliable high speed digital data communication • ECE 1392 – IC for Digital Communication • Q&A Jenkin Wong 14

Equalization for 100 Base-TX References • A CMOS Transceiver for 10 Mb/s and 100 Mb/s Ethernet by Everitt, Parker, Hurst, Nack and Konda • A Mixed-Signal Tuning Loop for Variable Bandpass Filter, A Final Report by Wee-Guan Ben Tan, EE, University of California • Slides from Research Overview in Analog IC Design by Prof. Phillip E. Allen, ECE Georgia Institute of Technology • Notes from Analog versus DSP for Disk Drive by Prof. Richard Spencer, University of California Jenkin Wong 15